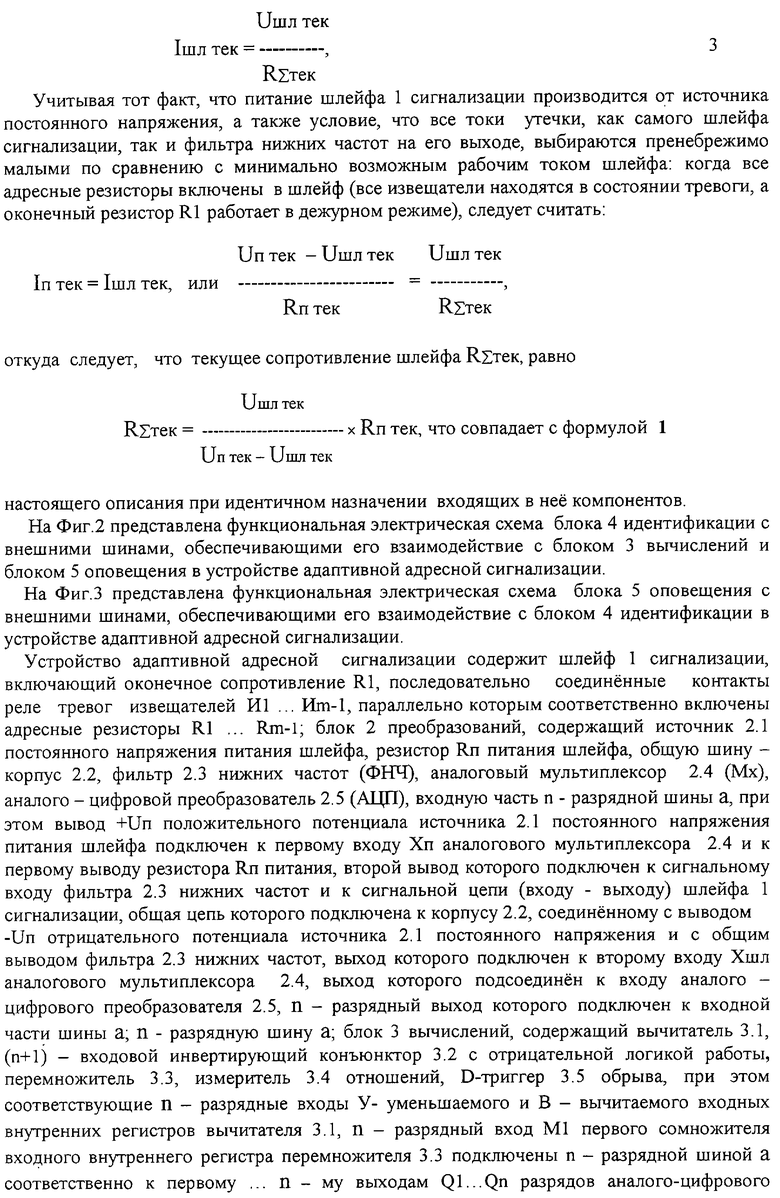

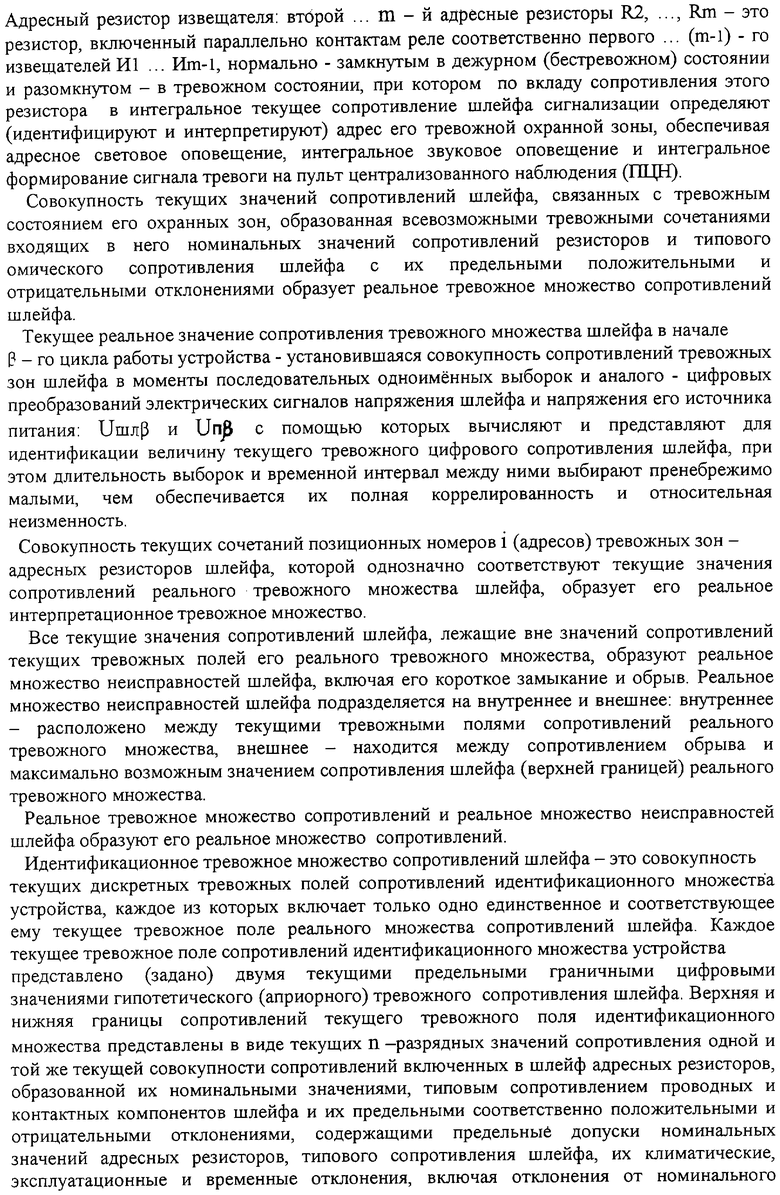

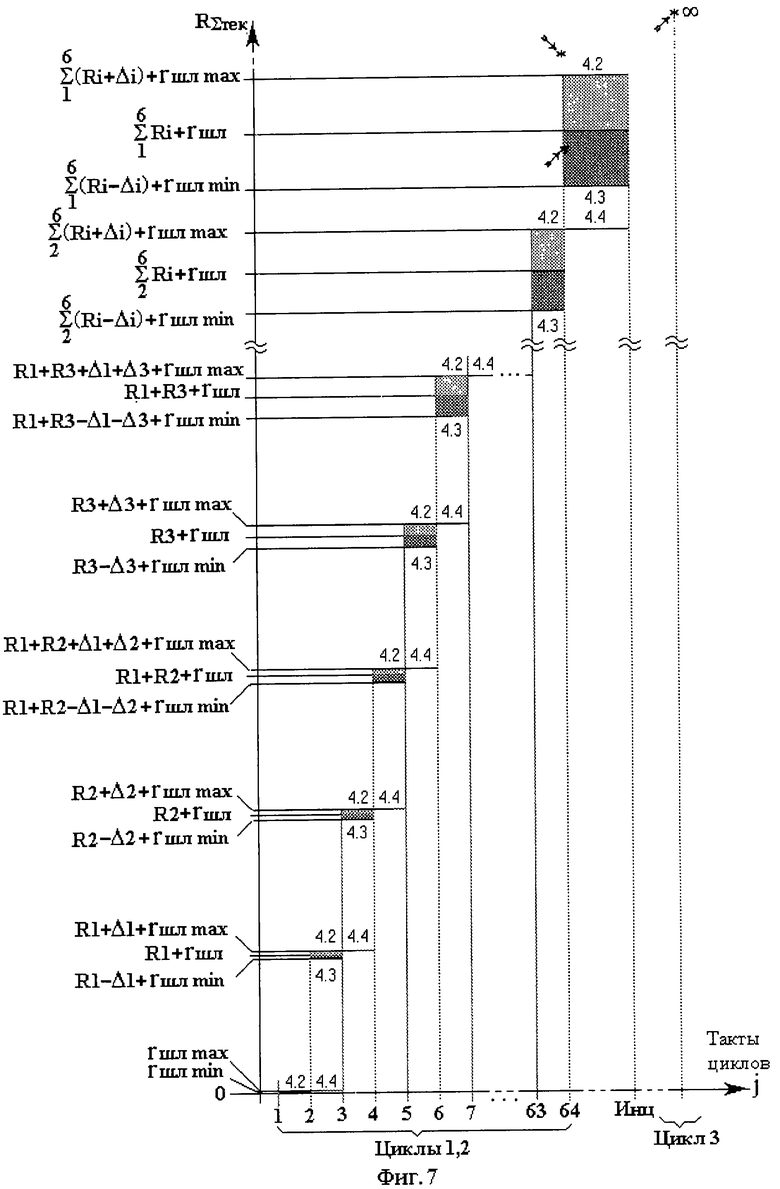

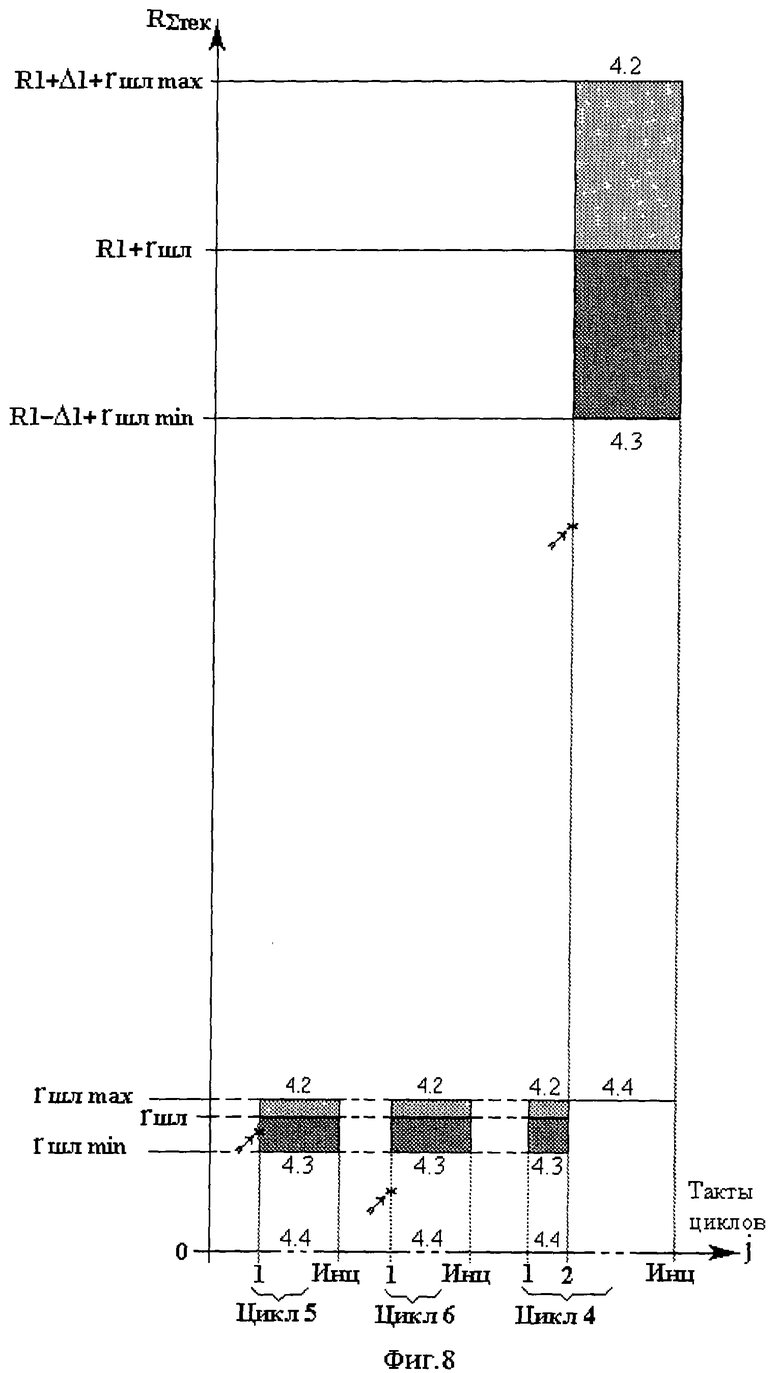

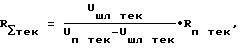

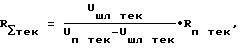

1. Способ адаптивной адресной сигнализации, заключающийся в определении адресов тревожных зон шлейфа сигнализации независимо от их текущего множества сочетаний, содержащего последовательно включенные в него нормально замкнутые в дежурном состоянии релейные выходы извещателей, параллельно которым включены соответствующие им адресные резисторы, имеющие индивидуально различимые друг от друга сопротивления, содержащий питание шлейфа сигнализации, аналого-цифровое преобразование выходного напряжения шлейфа сигнализации, извещение и оповещение о тревожном состоянии шлейфа сигнализации, отличающийся тем, что используют оконечный элемент шлейфа в виде адресного резистора, выбирают сопротивления адресных резисторов шлейфа из условия их индивидуальной достоверной различимости при всевозможных сочетаниях тревожных охранных зон и при действии всего комплекса эксплуатационных, производственных факторов и погрешностей преобразований и вычислений способа и устройства, при этом производят питание шлейфа сигнализации от источника постоянного напряжения через сопротивление резистора Rптек питания шлейфа и осуществляют следующие действия: производят фильтрацию помех фильтром нижних частот; производят выборку текущего напряжения Uптек источника питания шлейфа сигнализации и ее аналого-цифровое преобразование в n-разрядный код; производят выборку текущего напряжения Uшлтек шлейфа сигнализации после его низкочастотной фильтрации и ее аналого-цифровое преобразование, число n разрядов которого выбирают из условий достоверного различения включения (или выключения) минимального сопротивления адресного резистора шлейфа сигнализации на фоне его максимально возможного сопротивления с учетом погрешностей, отклонений за счет дестабилизирующих факторов; вычисляют цифровой аналог текущего сопротивления шлейфа по формуле

где RΣтек - суммарное цифровое значение сопротивления текущей совокупности адресных резисторов и омического сопротивления проводов и контактных соединений, включенных в шлейф сигнализации, - аналог его реального текущего сопротивления в начале текущего цикла работы устройства;

Uшлтек - падение напряжения в шлейфе сигнализации в текущий момент времени;

Uптек - постоянное напряжение источника питания шлейфа сигнализации в текущий момент времени;

Rптек - текущее сопротивление резистора (питания шлейфа), последовательно включенного между источником питания и шлейфом сигнализации внутри устройства;

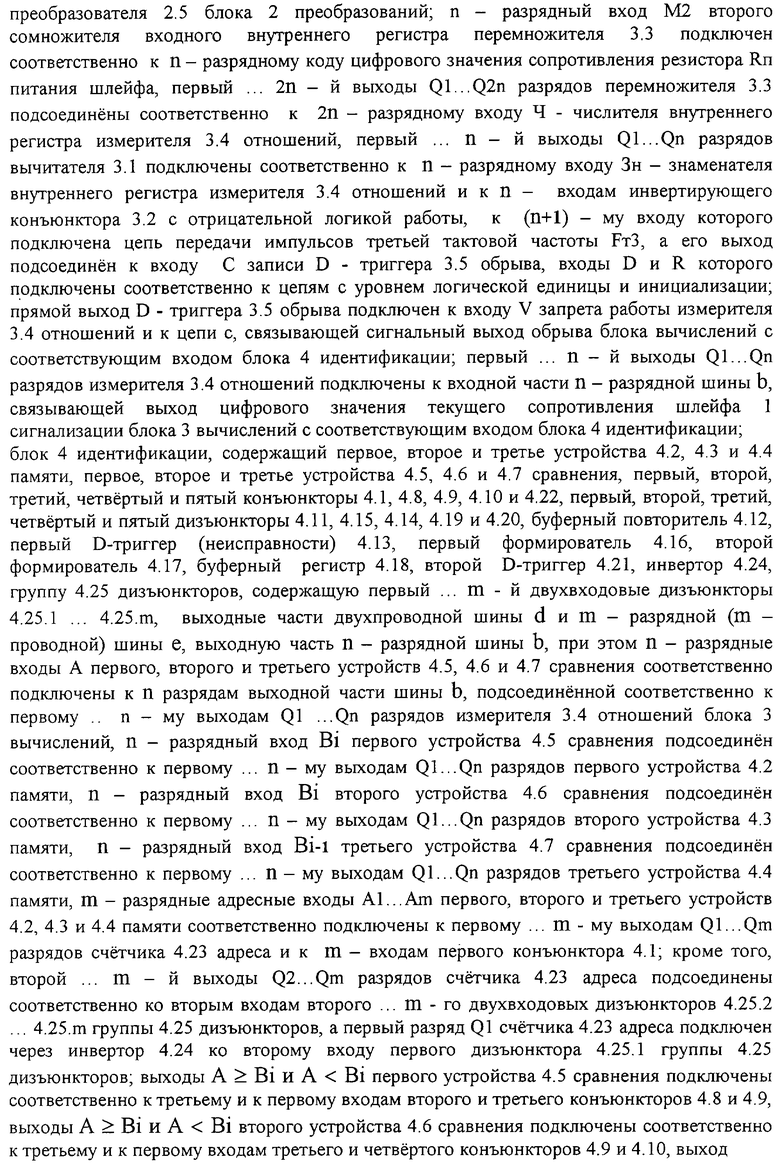

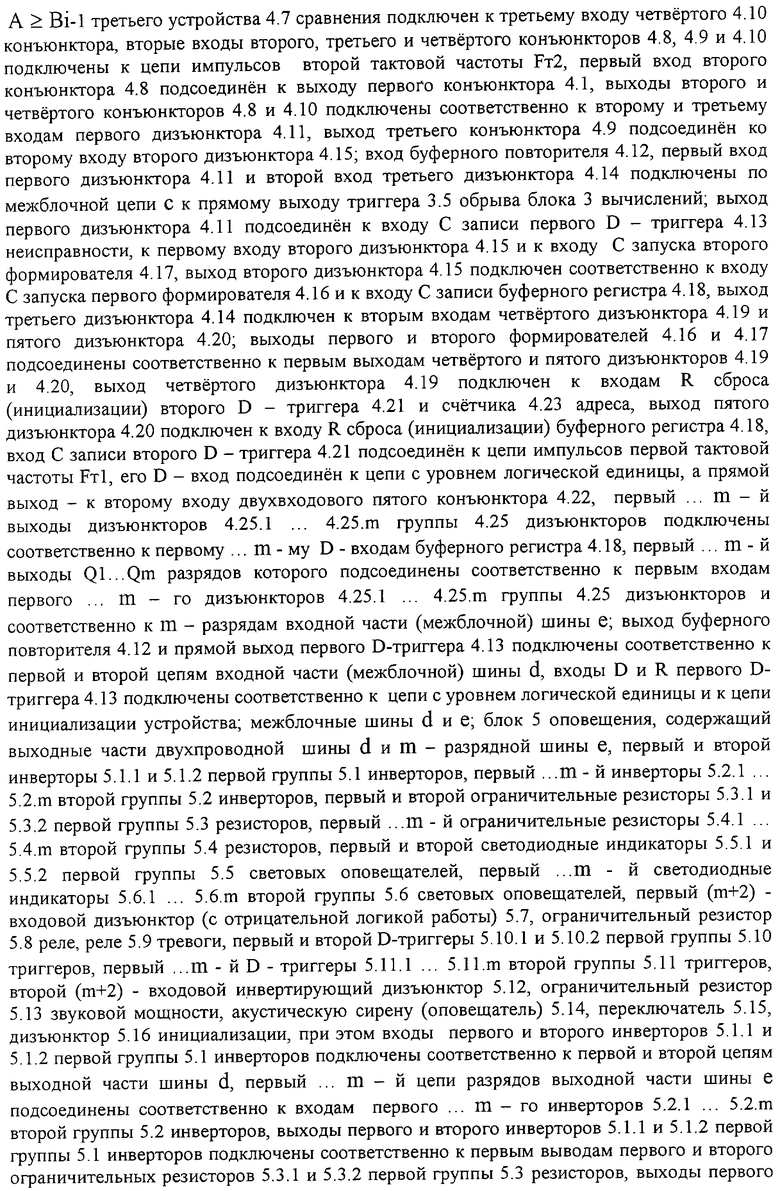

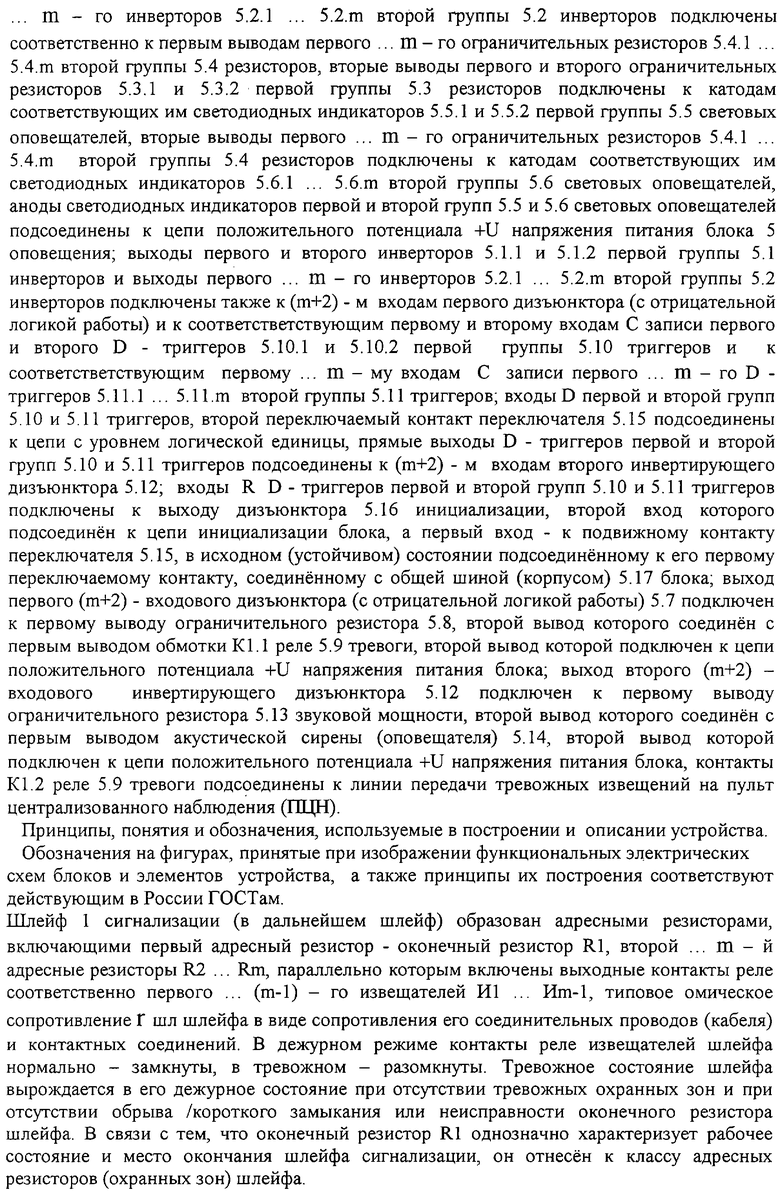

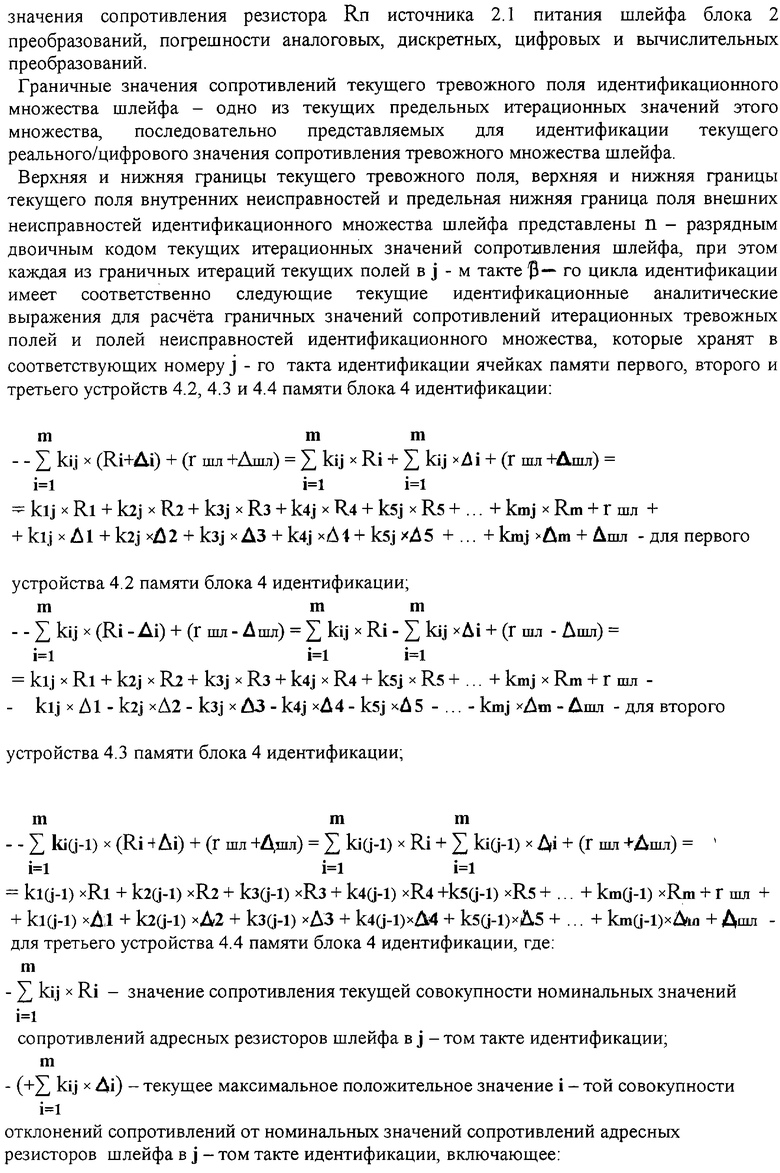

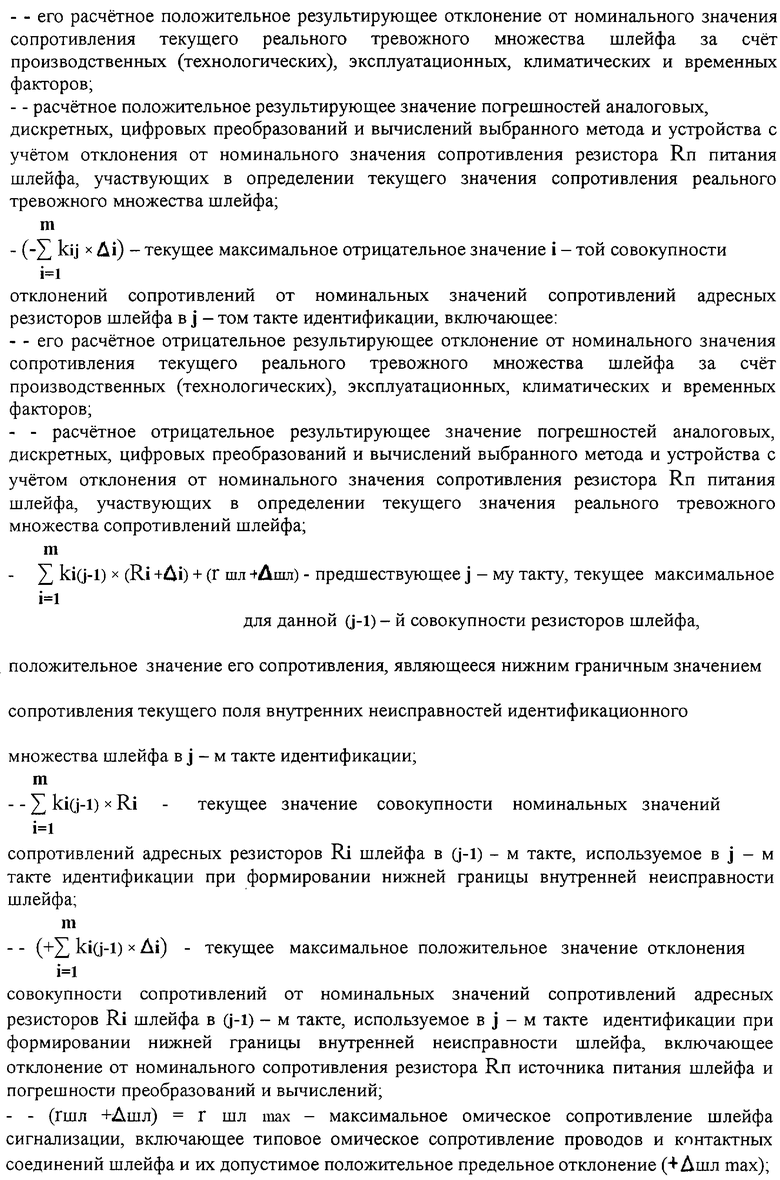

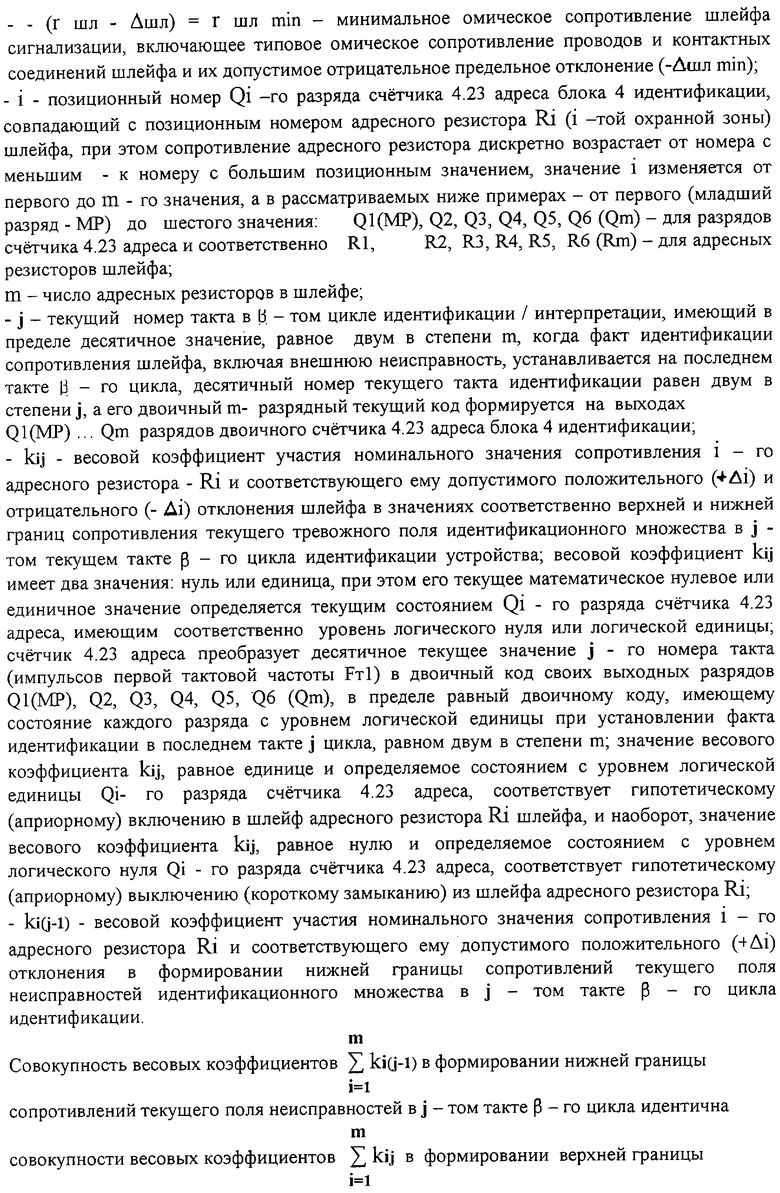

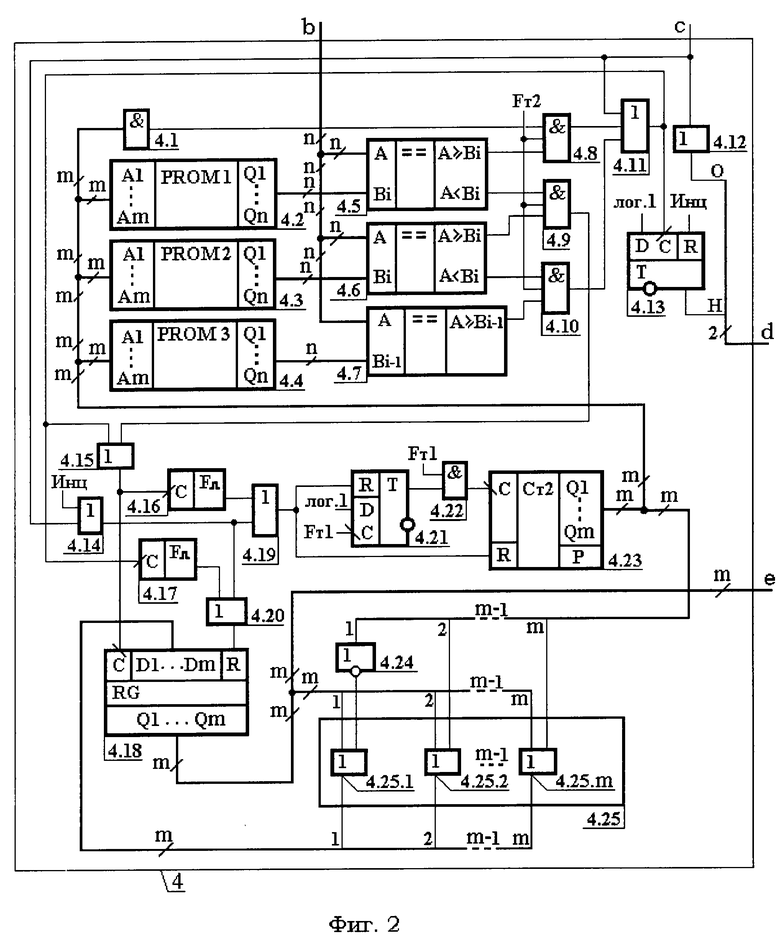

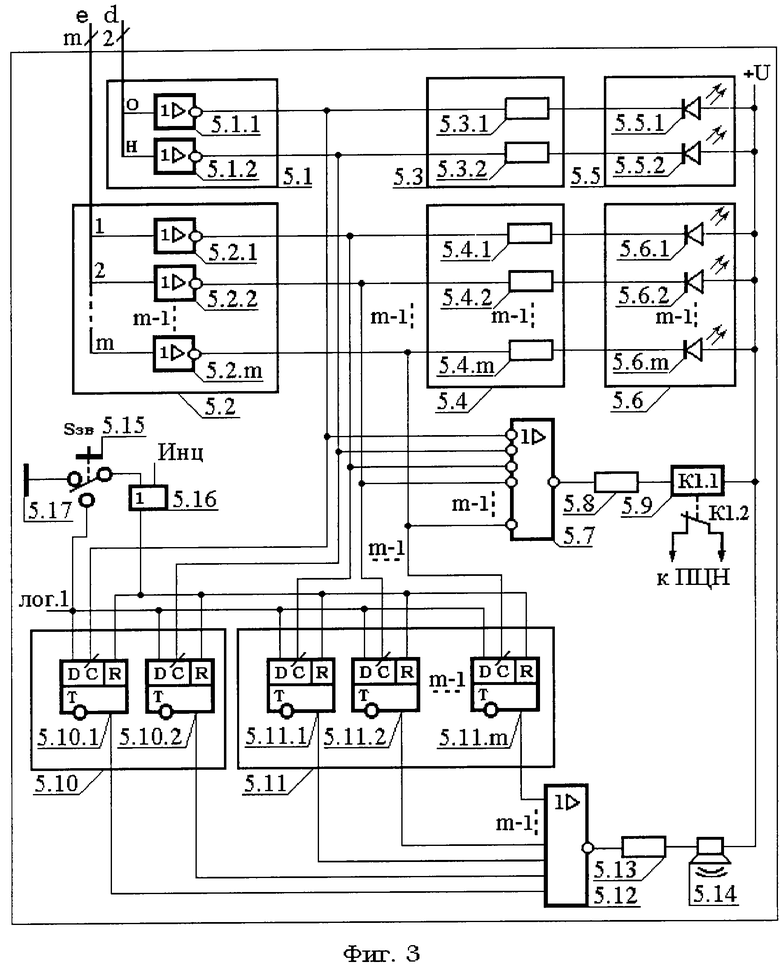

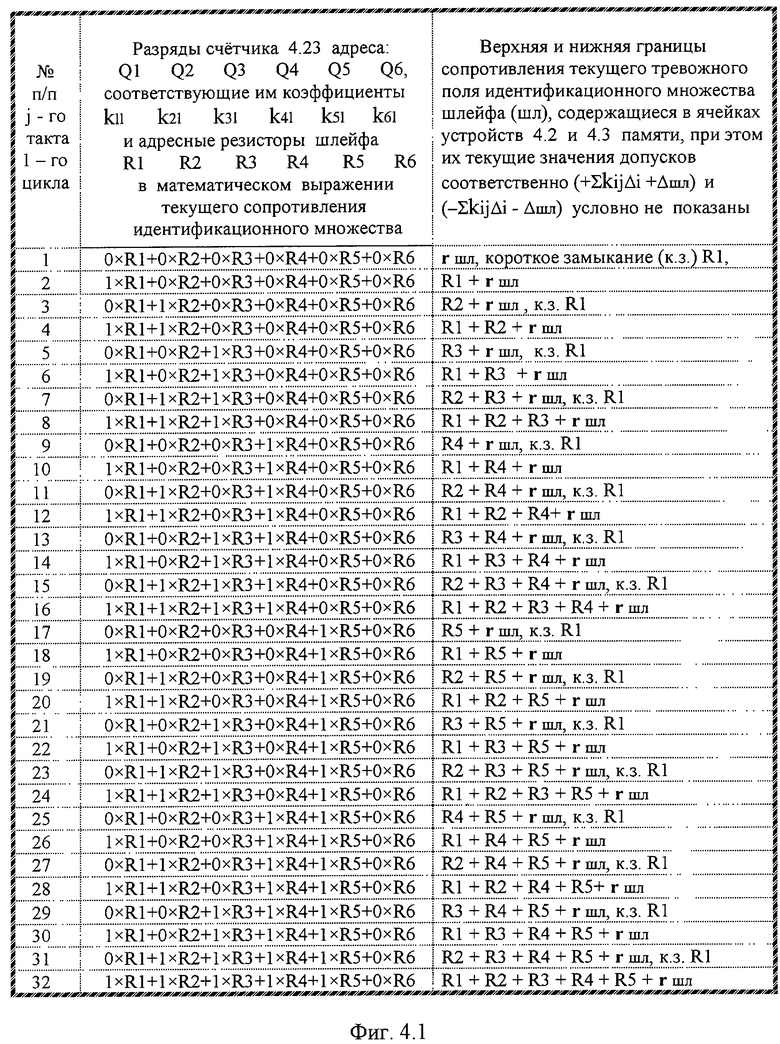

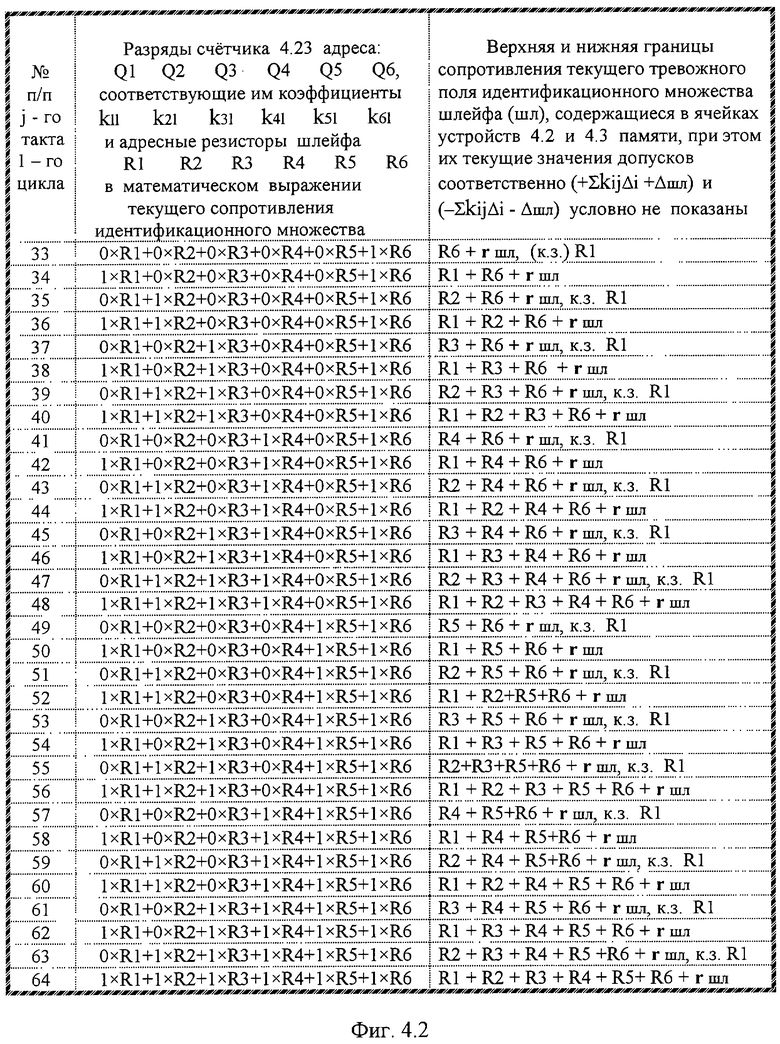

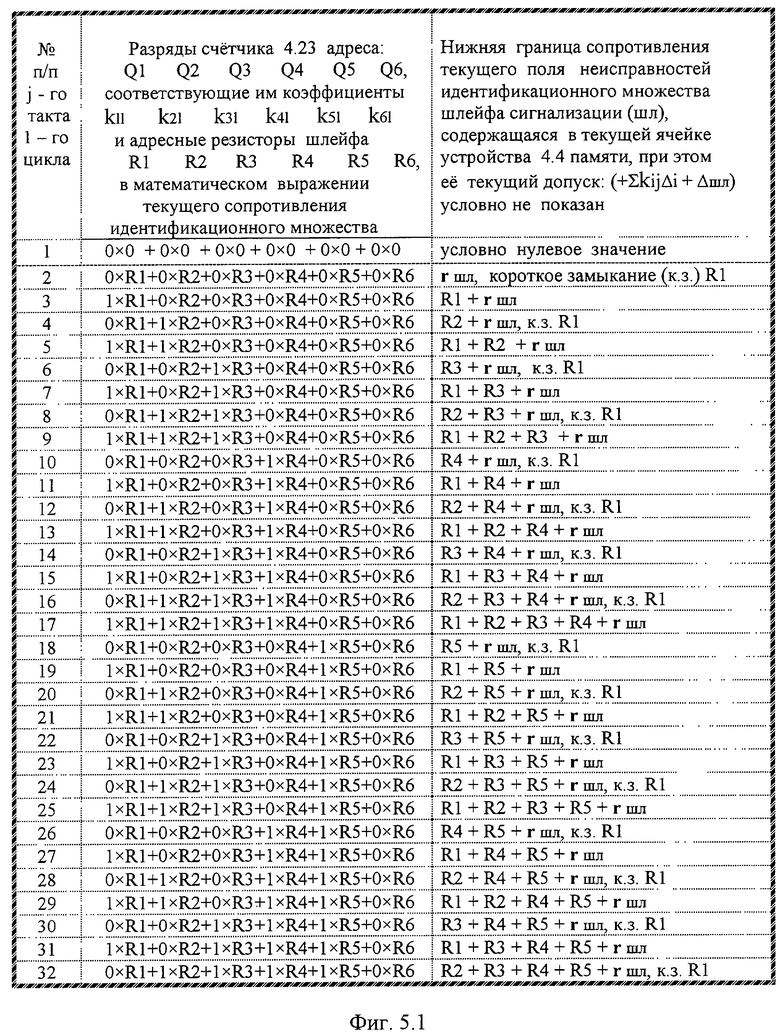

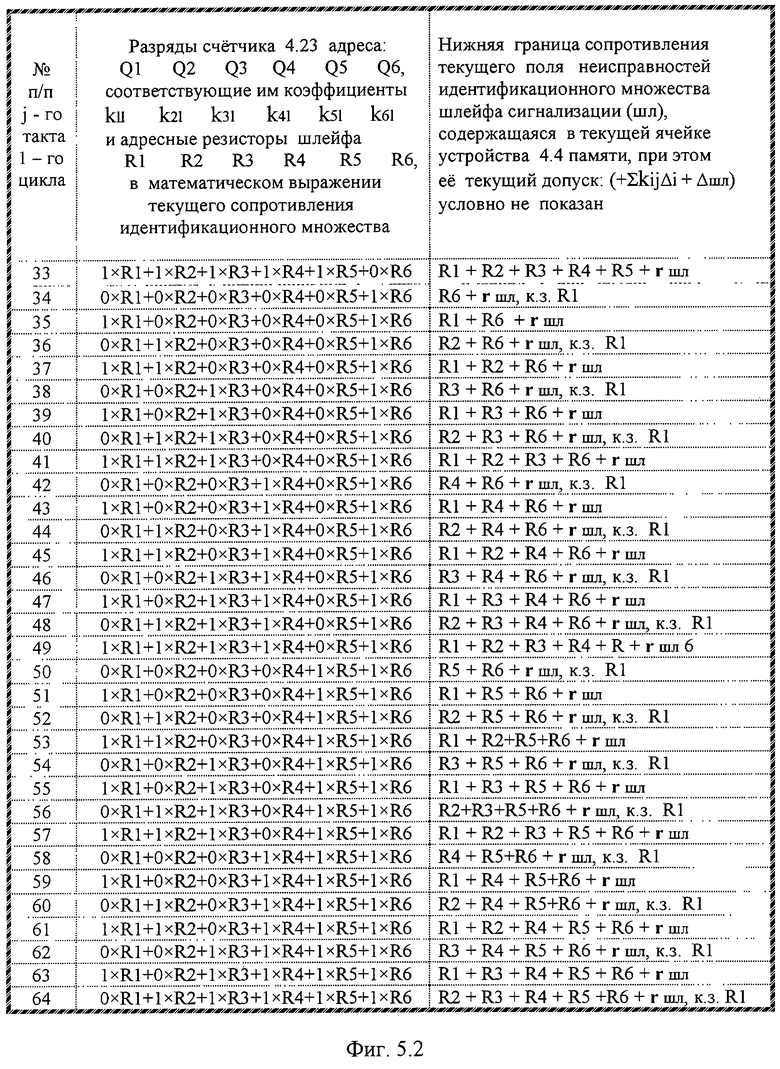

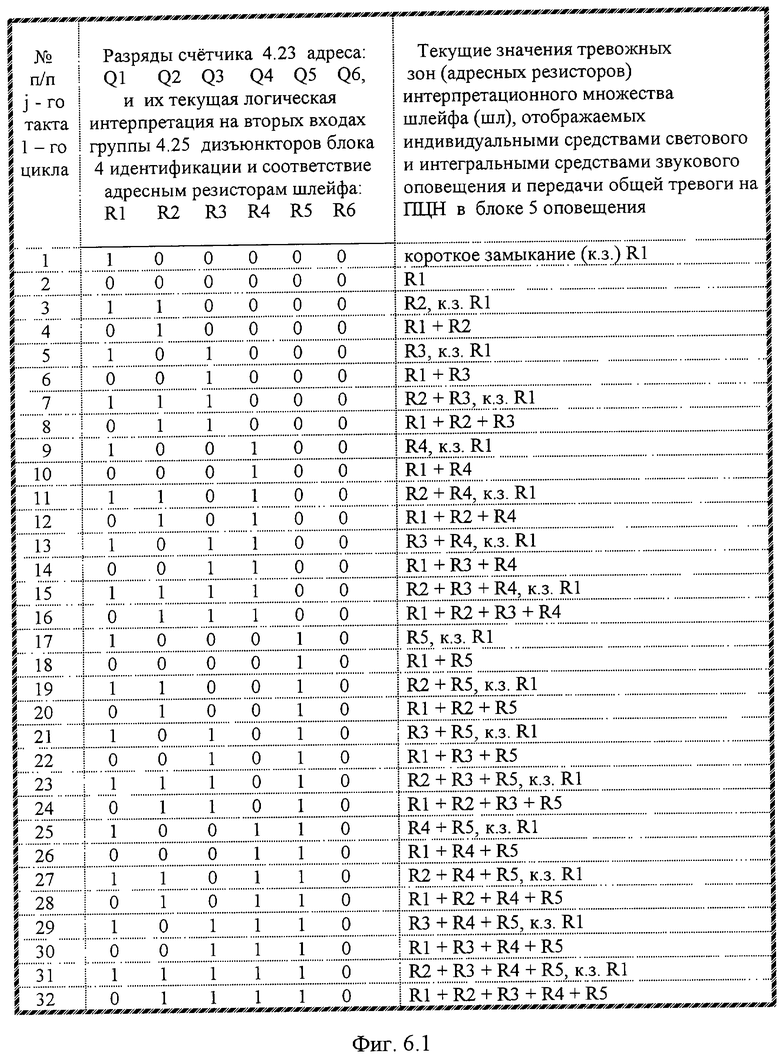

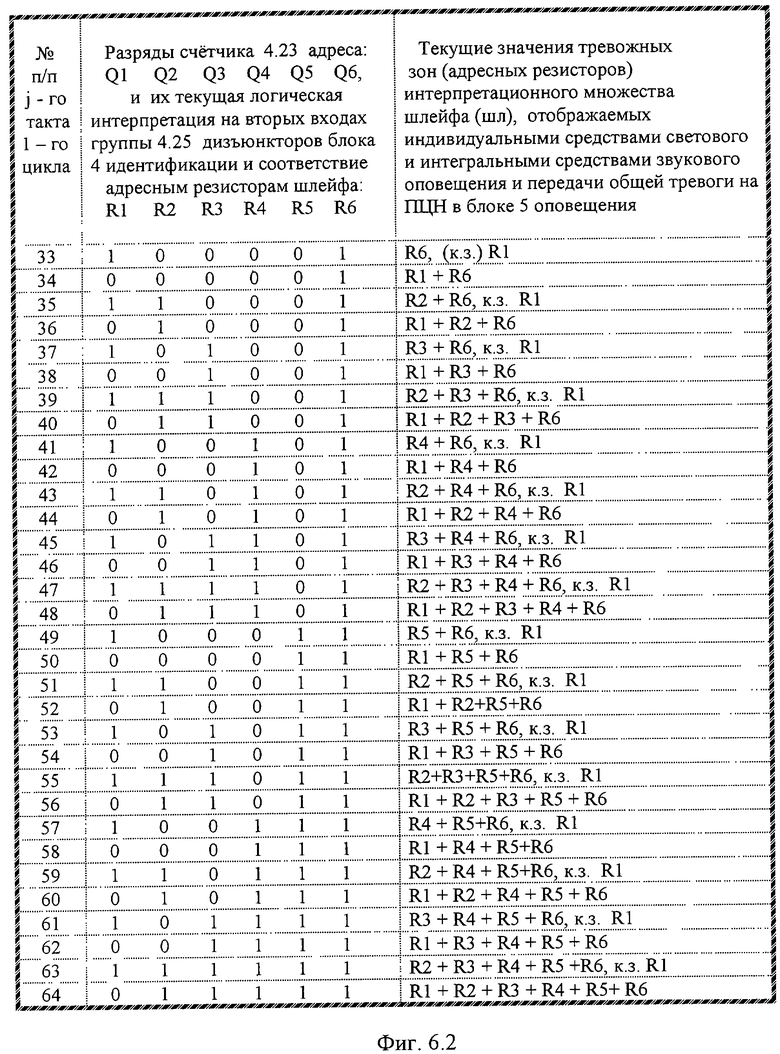

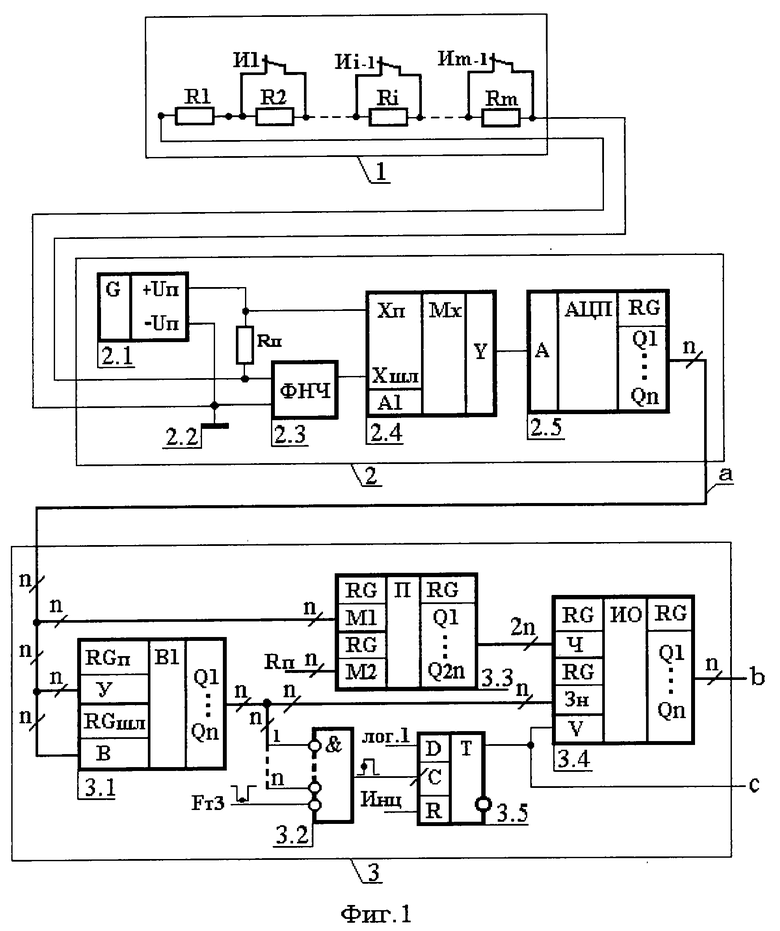

формируют цифровую идентификационную модель реального тревожного множества сопротивлений шлейфа сигнализации следующим образом: каждому единственно возможному текущему сочетанию тревожных адресных резисторов (тревожных охранных зон) шлейфа ставят в соответствие два единственных предельно возможных рабочих значения текущего сопротивления шлейфа - верхнее и нижнее, имеющих общее текущее номинальное значение сопротивления шлейфа в виде суммы номинальных значений сопротивлений рассматриваемой текущей совокупности тревожных адресных резисторов, оконечного резистора и типового омического сопротивления шлейфа, причем для образования верхнего и нижнего значений текущего сопротивления шлейфа его текущее номинальное значение сопротивления соответственно увеличивают и уменьшают на максимальные соответственно положительные и отрицательные отклонения сопротивлений тревожных адресных резисторов, оконечного резистора и типового омического сопротивления шлейфа за счет производственных и эксплуатационных факторов, учитывают отклонения от номинального значения сопротивления резистора питания шлейфа, учитывают погрешности аналоговых, дискретных и аналого-цифровых преобразований сигналов напряжения источника питания, напряжения шлейфа и погрешности вычислений цифрового значения текущего сопротивления шлейфа, при этом сформированные верхнее и нижнее значения текущего сопротивления шлейфа являются границами его текущего тревожного поля, внутрь которого попадают все текущие возможные рабочие значения сопротивлений рассматриваемой тревожной совокупности адресных резисторов шлейфа с одной и той же номинальной основой его сопротивления, при этом число возможных текущих тревожных полей сопротивления шлейфа равно числу возможных сочетаний тревожных адресных резисторов шлейфа сигнализации и образует его тревожное идентификационное множество, обеспеченное физической памятью, в/из которой хранят/считывают одноименные (равноадресные) значения сопротивлений границ текущих тревожных полей: от минимального значения, когда оконечный резистор шлейфа закорочен (саботажной перемычкой), а адресные резисторы извещателей шлейфа закорочены контактами их реле (соответствующие им извещатели находятся в бестревожном состоянии), до максимального значения, когда все адресные резисторы, включая оконечный резистор, включены в шлейф (все его извещатели находятся в состоянии тревоги); формируют цифровую идентификационную модель реального множества неисправностей шлейфа, расположенную вне полей сопротивлений идентификационного тревожного множества шлейфа; формируют текущие группы смежных (одноименных) текущих идентификационных полей: тревожного поля и поля неисправностей идентификационного множества сопротивлений шлейфа, в одно из которых обязательно и единственным образом попадает вычисленное текущее значение Rтек тревожного или неисправного сопротивления шлейфа сигнализации, при этом регистрируют факт установления идентификации значения сопротивления шлейфа и в случае его тревожного состояния ставят в соответствие единственно возможное сочетание суммы номинальных значений сопротивлений его тревожных адресных резисторов, которое однозначно интерпретируют в адреса тревожных охранных зон (тревожных состояний извещателей и/или оконечного резистора, активных состояний пультов, станций, другого оборудования) шлейфа сигнализации в текущем временном цикле идентификации/интерпретации; по факту установления текущей идентификации/интерпретации тревожных и неисправных состояний сопротивления шлейфа сигнализации формируют адресные сигналы соответствующих им тревожных извещений, включая короткое замыкание, световых оповещений и интегрального сигнала звукового оповещения. 2. Устройство адаптивной адресной сигнализации, содержащее шлейф сигнализации, включающий последовательно соединенные релейные выходы первого ... (m-1)-го извещателей (датчиков) И1 ... Иm-1, параллельно которым подключены бинарно отличающиеся по величине сопротивлений соответственно второй ... m-й адресные резисторы R2 . .. Rm, узлы блока преобразований в виде источника питания и аналого-цифрового преобразователя, мультиплексор, двоичный счетчик, отличающееся тем, что в него введены: в шлейф сигнализации - оконечный элемент в виде первого адресного резистора R1, при этом выход шлейфа подключен к блоку преобразований; в блок преобразований - источник питания шлейфа в виде источника постоянного напряжения питания, резистор Rп питания шлейфа, общая шина (корпус устройства), фильтр нижних частот, мультиплексор (аналоговый), входная часть n-разрядной шины а, при этом сигнальный выход шлейфа подключен к сигнальному входу фильтра нижних частот и ко второму выводу резистора Rп питания шлейфа, первый вывод которого подключен к выводу положительного потенциала +Uп напряжения источника питания шлейфа и к первому сигнальному аналоговому входу Хп мультиплексора, вывод отрицательного потенциала -Uп напряжения источника питания шлейфа и общий вывод фильтра нижних частот подключены к корпусу (общей шине) блока, выход фильтра нижних частот подсоединен ко второму сигнальному аналоговому входу Хшл мультиплексора, выход Y которого подключен к входу аналого-цифрового преобразователя, первый ... n-й выходы Q1 ... Qn разрядов которого подсоединены соответственно к входной части n-разрядной шины а; n-разрядная шина а, подключающая информационный выход блока преобразований к информационному входу блока вычислений; блок вычислений, содержащий вычитатель, (n+1) - входовой инвертирующий конъюнктор с отрицательной логикой работы, перемножитель, вычислитель текущего сопротивления шлейфа, D-триггер обрыва, выходная часть n-разрядной шины a, входная часть n-разрядной шины b, вход цепи с обрыва, при этом соответствующие n-разрядные входы У - уменьшаемого и В - вычитаемого входных внутренних регистров вычитателя и n-разрядный вход M1 входного внутреннего регистра первого сомножителя перемножителя поразрядно объединены и через n-разрядную шину а между блоком вычислений и блоком преобразований соответственно подсоединены к первому ... n-му выходам Q1...Qn разрядов его аналого-цифрового преобразователя; n-разрядный вход М2 входного внутреннего регистра второго сомножителя перемножителя поразрядно подключен к n-разрядному коду цифрового значения номинального сопротивления резистора Rп питания шлейфа, 2n-разрядный выход Q1...Q2n перемножителя подсоединен соответственно к 2n-разрядному входу Ч - числителя внутреннего регистра вычислителя текущего сопротивления шлейфа; первый ... n-й выходы Q1...Qn разрядов вычитателя поразрядно подключены к n-разрядному входу Зн - знаменателя внутреннего регистра вычислителя текущего сопротивления шлейфа и к n-входам инвертирующего конъюнктора с отрицательной логикой работы, к (n+1)-му входу которого подключена цепь передачи импульсов третьей тактовой частоты Fт3, а его выход подсоединен к входу С записи D-триггера обрыва, входы D и R которого подключены соответственно к цепям с уровнем логической единицы и инициализации; прямой выход D-триггера обрыва подключен к входу V запрета работы измерителя отношений и к входу цепи с обрыва; первый ... n-й выходы Q1...Qn вычислителя текущего сопротивления шлейфа поразрядно подключены к входной части n-разрядной шины b; n-разрядная шина b, подключающая информационный выход блока вычислений к информационному входу блока идентификации; цепь с обрыва между выходом блока вычислений и входом блока идентификации; блок идентификации, содержащий первый m-входовой конъюнктор; первое, второе и третье устройства памяти; первое, второе и третье устройства сравнения; второй, третий, четвертый и пятый конъюнкторы; первый, второй, третий, четвертый и пятый дизъюнкторы; буферный повторитель, первый D-триггер, второй D-триггер, двоичный счетчик (адреса), первый формирователь импульса, второй формирователь импульса, буферный регистр, инвертор, первый ... m-й дизъюнкторы группы дизъюнкторов, выходная часть n-разрядной шины b, выход цепи с обрыва, входная часть двухпроводной шины d и входная часть m-разрядной шины е, при этом n-разрядная шина b подключает выходы Q1...Qn измерителя отношений блока вычислений соответственно к n-разрядным входам А первого, второго и третьего устройств сравнения блока идентификации, n-разрядный вход Bi первого устройства сравнения соответственно подсоединен к n-разрядному выходу Q1...Qn первого устройства памяти, n-разрядный вход Bi второго устройства сравнения соответственно подсоединен к n-разрядному выходу Q1...Qn второго устройства памяти, n-разрядный вход Bi-1 третьего устройства сравнения соответственно подсоединен к n-разрядному выходу Q1...Qn третьего устройства памяти, первый . .. m-й адресные входы A1...Am первого, второго и третьего устройств памяти соответственно подключены к первому ... m-му выходам Q1...Qm двоичного счетчика адреса и к m-входам первого конъюнктора; второй ... m-й выходы Q2...Qm двоичного счетчика адреса подсоединены соответственно ко вторым входам второго ... m-го дизъюнкторов группы дизъюнкторов, первый разряд Q1 счетчика адреса подключен к инвертору, выход которого подсоединен к второму входу первого дизъюнктора группы дизъюнкторов, выходы первого ... m-го дизъюнкторов группы дизъюнкторов подсоединены соответственно к первому ... m-му входам D1. ..Dm буферного регистра, выходы A≥Bi и А<Bi первого устройства сравнения подключены соответственно к третьему и к первому входам второго и третьего конъюнкторов, выходы A≥Bi и А<Bi второго устройства сравнения подключены соответственно к третьему и к первому входам третьего и четвертого конъюнкторов, выход А≥Bi-1 третьего устройства сравнения подключен к третьему входу четвертого конъюнктора, вторые входы второго, третьего и четвертого конъюнкторов подключены к цепи импульсов второй тактовой частоты Fт2, первый вход второго конъюнктора подсоединен к выходу первого m-входового конъюнктора, выходы второго и четвертого конъюнкторов подключены соответственно к второму и третьему входам первого дизъюнктора, выход третьего конъюнктора подсоединен к второму входу второго дизъюнктора; прямой выход триггера обрыва блока вычислений по цепи с подключен к устройствам блока идентификации: к входу буферного повторителя, к первому входу первого дизъюнктора, к второму входу третьего дизъюнктора; выход первого дизъюнктора блока идентификации подсоединен к входу С записи первого D-триггера неисправности, к первому входу второго дизъюнктора и к входу С запуска второго формирователя импульса, выход второго дизъюнктора подключен соответственно к входу С запуска первого формирователя импульса и к входу С записи буферного регистра, выход третьего дизъюнктора подключен к вторым входам четвертого и пятого дизъюнкторов; выходы первого формирователя импульса и второго формирователя импульса подсоединены соответственно к первым входам четвертого и пятого дизъюнкторов, выход четвертого дизъюнктора подключен к входам R сброса (инициализации) второго D-триггера и (двоичного) счетчика адреса, выход пятого конъюнктора предназначен для подачи тактовой частоты Fт1 на счетный вход двоичного счетчика адреса; выход пятого дизъюнктора подключен к входу R сброса (инициализации) буферного регистра, вход С записи второго D-триггера подсоединен к цепи импульсов первой тактовой частоты Fт1, его D-вход подключен к цепи с уровнем логической единицы, а прямой выход - к второму входу пятого конъюнктора, первый вход которого подсоединен к цепи импульсов первой тактовой частоты Fт1; первый ... m-й выходы Q1...Qm разрядов буферного регистра подсоединены соответственно к выходной части m-разрядной шины е и к первым входам соответственно первого ... m-го дизъюнкторов группы дизъюнкторов, выход буферного повторителя и прямой выход первого D-триггера подключены соответственно к входной части двухпроводной шины d, входы D и R первого D-триггера подключены соответственно к цепи с уровнем логической единицы и к цепи инициализации устройства; двухпроводная шина d и m-разрядная шина е, которыми подключены (интерпретационные) выходы блока идентификации к входам блока оповещения; в блок оповещения - выходная часть двухпроводной шины d, выходная часть m-разрядной шины е, первый и второй инверторы первой группы инверторов, первый ... m-й инверторы второй группы инверторов, первый и второй ограничительные резисторы первой группы резисторов, первый ... m-й ограничительные резисторы второй группы резисторов, первый и второй светодиодные индикаторы первой группы световых оповещателей, первый ... m-й светодиодные индикаторы второй группы световых оповещателей, первый (m+2)-входовый дизъюнктор с отрицательной логикой работы, ограничительный резистор (обмотки) реле, реле, состоящее из обмотки К 1.1 и нормально замкнутых в бестревожном состоянии контактов К 1.2 тревоги, первый и второй D-триггеры первой группы триггеров, первый . . . m-й D-триггеры второй группы триггеров, второй (m+2)-входовой инвертирующий дизъюнктор, ограничительный резистор звуковой мощности, акустическая сирена (оповещатель), переключатель, дизъюнктор инициализации, при этом выход буферного повторителя обрыва и прямой выход первого D-триггера блока идентификации двухпроводной шиной d подключены соответственно к входам первого и второго инверторов первой группы инверторов блока оповещения, первый . . . m-й выходы Q1...Qm разрядов буферного регистра блока идентификации m-разрядной шиной е подсоединены соответственно к входам первого . .. m-го инверторов второй группы инверторов блока оповещения; выходы инверторов первой и второй групп блока оповещения подключены к первым выводам соответствующих ограничительных резисторов первой и второй групп резисторов, вторые выводы которых подключены к катодам соответствующих светодиодных индикаторов первой и второй групп световых оповещателей, аноды которых подсоединены к цепи положительного потенциала: +U напряжения питания блока; выходы инверторов соответственно первой и второй групп подключены также к (m+2)-м входам первого дизъюнктора (с отрицательной логикой работы) и к входам С записи соответственно первого и второго D-триггеров первой группы и к входам С записи соответственно первого ... m-го D-триггеров второй группы триггеров, соответствующих инверторам обеих групп; входы D триггеров первой и второй групп и второй переключаемый контакт переключателя Sзв сброса подсоединены к цепи с уровнем логической единицы, прямые выходы D-триггеров первой и второй групп подсоединены к (m+2)-м входам второго инвертирующего дизъюнктора; входы R D-триггеров первой и второй групп подключены к выходу дизъюнктора инициализации (сброса), второй вход которого подсоединен к цепи инициализации устройства, а первый вход - к подвижному контакту переключателя Sзв сброса, в исходном (устойчивом) состоянии подсоединенному к его первому переключаемому контакту, соединенному с общей шиной (корпусом) блока; выход первого (m+2)-входового дизъюнктора с отрицательной логикой работы подключен к выводу ограничительного резистора реле, последовательно соединенного с его обмоткой К 1.1, подключенной к цепи положительного потенциала +U напряжения питания блока; выход второго (m+2)-входового инвертирующего дизъюнктора подключен к выводу ограничительного резистора звуковой мощности, последовательно соединенного с акустической сиреной (оповещателем), подключенной к цепи положительного потенциала +U напряжения питания блока, контакты К 1.2 тревоги реле подсоединены к линии передачи тревожных извещений на пульт централизованного наблюдения.