Изобретение относится к области автоматики управления и связи, в том числе к электронной пожарно-охранной сигнализации, и может быть использовано при построении систем обнаружения пожара, несанкционированного вскрытия объекта охраны.

Известно устройство пожарной сигнализации по патенту №2024062, МКИ G 08 B 17/00, которое содержит блок питания (БП), блок сопряжения (БС), датчик (Д), шлейф (Ш), триггеры (ТР), формирователи импульса (ФИ), генератор импульсов (ГИ), усилитель (У), селектор импульса (СИ), дешифратор (ДШ), схемы 2И, 2И-НЕ, 2ИЛИ-НЕ, два интегрирующих звена, две кнопки начальной установки (КН), регистр (Р) блоки световой и звуковой индикации (Св.И) и (Зв.И). Данное устройство исключает одновременное появление в Ш адресных сигналов от двух и более абонентов, не вырабатывает сигнал тревоги на импульс помехи, возникающий на входе контрольного пульта (КП), при отсутствии адресного сигнала от абонента вследствие применения СИ, на выходе которого формируется импульс напряжения только в случае наличия на его входе импульса напряжения, величина длительности которого больше заранее определенной величины, большей величины максимальной длительности помехи.

С целью повышения помехоустойчивости устройства было сделано следующее: первый вход схемы 2И-НЕ блока сопряжения соединен с датчиком (Д), а второй вход схемы 2И-НЕ через первое интегрирующее звено объединен с одной клеммой электронного ключа и сигнальным проводом Ш. Выход схемы 2И-НЕ соединен с R-входом RS-триггера, S-вход которого подключен к первой клемме первой КН и через второе интегрирующее звено подключен через общий провод Ш к общей клемме БП. Вход первого интегрирующего звена и одна клемма электронного ключа БС через сигнальный провод Ш подключены к одной входной клемме оптронной связи, другая входная клемма которого через токоограничивающий резистор соединена с клеммой питания БП. Другая клемма электронного ключа объединена с общим выводом первого и второго интегрирующих звеньев, со второй клеммой КН и через общий провод Ш соединена с общей клеммой БП. Выход RS-триггера соединен с управляющим входом электронного ключа через одновибратор. При этом все микросхемы БС запитываются от этого же БП. Фотоприемник оптрона соединен с выходом У, выход которого соединен с запускающим входом ГИ, с первым входом первого ФИ, первым входом схемы ИЛИ, второй вход которой соединен с выходом первого ФИ, а второй вход первого ФИ соединен с клеммой второй КН. Выход ГИ соединен с входом СИ, обнуляющий вход которого соединен с выходом второго ФИ, вход которого соединен с выходом схемы ИЛИ. Клемма второй КН также соединена со сбрасывающим входом блока Зв.И., запускающий вход которого объединен с выходом СИ и входом СЧ. Выходы СЧ соединены с информационными входами Р, синхронизирующий вход которого соединен с выходом третьего ФИ. Второй выход третьего ФИ соединен с входом четвертого ФИ, выход которого соединен с обнуляющим входом СЧ, а вход третьего ФИ соединен с выходом второго ФИ. Выход Р через ДШ соединен с входом Св.И.

Основным недостатком изобретения по патенту №2024062 является недостаточная достоверность вызова конкретного абонента из-за отсутствия способности устройства определять появившуюся помеху в период вырабатывания адресного сигнала и поэтому не реагировать на нее, вследствие этого устройство-аналог может вырабатывать искаженный сигнал, приводящий к неадекватным действиям оператора относительно истинной ситуации на охраняемом объекте.

Известно также избирательное устройство идентификации вызова от абонента по патенту РФ №2136050, МПК G 08 В 25/00, Н 04 Q 3/74, принятое авторами в качестве ближайшего аналога, который содержит ряд абонентских Д, каждый из которых снабжен БС, при этом к каждому БС подключен БП через первый R и сигнальный провод Ш, последовательно соединенные между собой ГИ, СИ, СЧ, Р и ДШ с блоком Св.И, а также избирательное устройство идентификации вызова от абонента содержит блок Зв.И, ФИ, схемы 2И-НЕ, 2ИЛИ, 2И-НЕ, 4ИЛИ, ТР, КН, при этом к выходу каждого БС через сигнальный провод Ш присоединены запускающий вход ГИ через первый ТР, тактовый вход Р через первый ФИ, ФМД, инвертор НЕ и первый вход схемы 4И-НЕ, к выходу ФМД и к выходу инвертора НЕ подсоединена соответствующими входами первая схема 2И-НЕ, ко второму входу схемы 4И-НЕ подключен через второй ФИ выход ФМД, к третьему входу схемы 4И-НЕ подсоединен выход второго ТР, обнуляющий вход которого связан с выходом первой схемы 2И-НЕ через схему 2ИЛИ, а к установочному входу второго ТР подсоединены выход первого ФИ и тактовый вход Р, к выходу схемы 4И-НЕ присоединены установочный вход третьего ТР и первый вход схемы 4ИЛИ, к выходу третьего ТР подключен первый вход схемы 2И, ко второму входу которой подсоединен выход четвертого ТР, к установочному входу которого подключен выход второй схемы 2И-НЕ, первый вход которой соединен с инверсным выходом схемы первого ФИ, ко второму входу второй схемы 2И-НЕ подсоединен выход схемы N-ИЛИ, входы которой связаны с соответствующими выходами СЧ, выход схемы 2И соединен с разрешающим входом ДШ, обнуляющий вход третьего и четвертого ТР соединен со вторым контактом КН, со вторым входом схемы 4ИЛИ и со вторым R, который в свою очередь подключен к БП, в то же время к третьему входу схемы 4ИЛИ подключены третий R, связанный с БП, и С, связанный с общим проводом, при этом выход схемы 4ИЛИ через третий ФИ соединен с обнуляющим входом СЧ, СИ и первого ТР, к четвертому входу схемы 4ИЛИ подключен выход третьей схемы 2И-НЕ, первый вход которой соединен с инверсным выходом схемы N-ИЛИ, а второй вход соединен с инверсным выходом первого ФИ, кроме этого инверсный выход ФМД соединен с четвертым входом схемы 4И-НЕ, второй вход схемы 2ИЛИ соединен со вторым контактом КН и выходы ДШ соединены с запускающим входом блока 3И через схему ИЛИ.

Основным недостатком изобретения по патенту РФ №2136050 является низкая надежность устройства из-за отсутствия средств проверки работоспособности Д с БС, т.е. извещателей.

Задачей изобретения является повышение надежности работы системы пожарно-охранной сигнализации за счет обеспечения регулярного контроля работоспособности извещателей [датчик - блок сопряжения], осуществляемого по единому запросу для всех извещателей при обязательной однозначной очередности их ответов, что повышает надежность работы системы.

Указанная задача решается в изобретении за счет того, что система пожарно-охранной сигнализации, содержащая контрольный пульт (КП), к которому через провода шлейфа (Ш) подключен ряд абонентских датчиков (Д), каждый через свой блок сопряжения (БС), блок питания (БП), генератор импульсов (ГИ), счетчик (СЧ), регистр (Р), дешифратор (ДШ), световая и звуковая индикации (Св.И) и (Зв.И), формирователи импульса (ФИ), схемы 2И, 2И-НЕ, 4И-НЕ, 2ИЛИ, триггеры (ТР), формирователь импульса максимальной длительности помехи (ФМД), селектор импульса (СИ), резисторы (R), конденсатор (С) и кнопку обнуления (КН), по предложению авторов в системе пожарно-охранной сигнализации связь всех БС с КП выполнена в виде Ш из двух проводов, при этом все БС подключены к проводам Ш параллельно, в каждом БС первый вход первой схемы 2И/2ИЛИ объединен с инверсным входом первой схемы 2И, инверсный выход первой схемы 2И соединен с входом первого ФИ, первый вход второй схемы 2И соединен с выходом соответствующего Д, второй вход второй схемы 2И соединен с выходом первой схемы 2И/2ИЛИ, второй вход первой схемы 2И/2ИЛИ объединен с инверсным выходом  второго разряда первого СЧ, инверсный выход второй схемы 2И соединен с S-входом первого ТР, к выходу Q которого подсоединена первым входом первая схема 3И, R-вход первого ТР соединен с выходом первой схемы 2ИЛИ, выход первого интегрирующего звена [R1-Cl] соединен с первым входом первой схемы 2ИЛИ, а выход первой схемы 2ИЛИ также соединен с первым входом второй схемы 2И/2ИЛИ, к входу первого интегрирующего звена [R1-C1] подсоединен катодом диод (D), анод которого в свою очередь объединен с инверсным входом первой схемы 2И, причем к месту объединения входа первого интегрирующего звена [R1-Cl] и катода D также подсоединен С2, при этом второй вход первой схемы 2ИЛИ соединен с первой клеммой первой КН и через R2 соединен с катодом D, вторая клемма первой КН соединена с общим проводом (землей), к выходу первой схемы 2И подсоединена первым входом схема 5ИЛИ, к выходу которой подсоединен входом первый формирователь задержки (ФЗ) и вход второго ФИ, к выходу первого ФЗ подсоединен разрешающим счет входом второй СЧ, счетный вход которого соединен с выходом первого ГИ, обнуляющий вход R второго СЧ соединен с выходом второй схемы 2ИЛИ, первый вход которой соединен с выходом второго ФИ, а второй вход второй схемы 2ИЛИ объединен с выходом первой схемы 2ИЛИ, выход второй схемы 2ИЛИ также соединен с R-входом второго ТР, выходы второго СЧ соединены с соответствующими входами первого ДШ, инверсный выход которого соединен с первым входом третьей схемы 2И, второй вход которой объединен с выходом первого ФИ и со вторым входом схемы 5ИЛИ, инверсный выход

второго разряда первого СЧ, инверсный выход второй схемы 2И соединен с S-входом первого ТР, к выходу Q которого подсоединена первым входом первая схема 3И, R-вход первого ТР соединен с выходом первой схемы 2ИЛИ, выход первого интегрирующего звена [R1-Cl] соединен с первым входом первой схемы 2ИЛИ, а выход первой схемы 2ИЛИ также соединен с первым входом второй схемы 2И/2ИЛИ, к входу первого интегрирующего звена [R1-C1] подсоединен катодом диод (D), анод которого в свою очередь объединен с инверсным входом первой схемы 2И, причем к месту объединения входа первого интегрирующего звена [R1-Cl] и катода D также подсоединен С2, при этом второй вход первой схемы 2ИЛИ соединен с первой клеммой первой КН и через R2 соединен с катодом D, вторая клемма первой КН соединена с общим проводом (землей), к выходу первой схемы 2И подсоединена первым входом схема 5ИЛИ, к выходу которой подсоединен входом первый формирователь задержки (ФЗ) и вход второго ФИ, к выходу первого ФЗ подсоединен разрешающим счет входом второй СЧ, счетный вход которого соединен с выходом первого ГИ, обнуляющий вход R второго СЧ соединен с выходом второй схемы 2ИЛИ, первый вход которой соединен с выходом второго ФИ, а второй вход второй схемы 2ИЛИ объединен с выходом первой схемы 2ИЛИ, выход второй схемы 2ИЛИ также соединен с R-входом второго ТР, выходы второго СЧ соединены с соответствующими входами первого ДШ, инверсный выход которого соединен с первым входом третьей схемы 2И, второй вход которой объединен с выходом первого ФИ и со вторым входом схемы 5ИЛИ, инверсный выход  второго ТР соединен со вторым входом первой схемы 3И, инверсный выход

второго ТР соединен со вторым входом первой схемы 3И, инверсный выход  третьего ТР объединен с третьим входом схемы 5ИЛИ, выход

третьего ТР объединен с третьим входом схемы 5ИЛИ, выход  третьего ТР соединен с третьим входом первой схемы 3И, R-вход третьего ТР соединен с инверсным выходом третьей схемы 2И, а S-вход третьего ТР соединен с выходом третьей схемы 2ИЛИ, к первому входу которой подсоединены вторым (инверсным) входом четвертая схема 2И и выход однополюсного многопозиционного переключателя П1, первый вход четвертой схемы 2И соединен с третьим входом схемы 5ИЛИ, а второй вход третьей схемы 2ИЛИ соединен с выходом первой схемы 2ИЛИ, инверсный выход первой схемы 3И соединен с S-входом четвертого ТР, R вход которого соединен с выходом четвертой схемы 2ИЛИ, а выход

третьего ТР соединен с третьим входом первой схемы 3И, R-вход третьего ТР соединен с инверсным выходом третьей схемы 2И, а S-вход третьего ТР соединен с выходом третьей схемы 2ИЛИ, к первому входу которой подсоединены вторым (инверсным) входом четвертая схема 2И и выход однополюсного многопозиционного переключателя П1, первый вход четвертой схемы 2И соединен с третьим входом схемы 5ИЛИ, а второй вход третьей схемы 2ИЛИ соединен с выходом первой схемы 2ИЛИ, инверсный выход первой схемы 3И соединен с S-входом четвертого ТР, R вход которого соединен с выходом четвертой схемы 2ИЛИ, а выход  четвертого ТР соединен со счетным входом первого СЧ и вторым входом второй схемы 2И/2ИЛИ, третий вход которой соединен с инверсным выходом

четвертого ТР соединен со счетным входом первого СЧ и вторым входом второй схемы 2И/2ИЛИ, третий вход которой соединен с инверсным выходом  пятого ТР.

пятого ТР.

К первому входу четвертой схемы 2ИЛИ присоединен выходом второй однополюсный многопозиционный переключатель П2, а второй вход четвертой схемы 2ИЛИ объединен с первым входом пятой схемы 2ИЛИ и с выходом первой схемы 2ИЛИ, ко второму входу пятой схемы 2ИЛИ присоединены выходом третий однополюсный многопозиционный переключатель ПЗ и четвертый (инверсный) вход схемы 5ИЛИ, выход пятой схемы 2ИЛИ соединен с R-входом пятого ТР, S-вход которого объединен с выходом четвертой схемы 2И, пятый вход схемы 5ИЛИ соединен с выходом Q пятого ТР, четвертый однополюсный многопозиционный переключатель П4 выходом соединен с R входом шестого ТР, S вход которого соединен с Q выходом третьего ТР, инверсный выход  пятого ТР соединен с первым входом шестой схемы 2ИЛИ, а второй вход шестой схемы 2ИЛИ соединен с инверсным выходом

пятого ТР соединен с первым входом шестой схемы 2ИЛИ, а второй вход шестой схемы 2ИЛИ соединен с инверсным выходом  шестого ТР, выход шестой схемы 2ИЛИ соединен со вторым входом первой схемы 2И и третьим входом первой схемы 2И/2ИЛИ.

шестого ТР, выход шестой схемы 2ИЛИ соединен со вторым входом первой схемы 2И и третьим входом первой схемы 2И/2ИЛИ.

К выходам первого ДШ соответственно подсоединены входы однополюсных многопозиционных переключателей П1, П2, П3 П4, а также входы дополнительно введенного П5, выход последнего соединен с S-входом второго ТР, к выходу второй схемы 2И/2ИЛИ присоединен входом первый передатчик (ПЕР), выход которого соединен с инверсным входом первой схемы 2И, при этом в КП выходом второй ПЕР и входом приемник (ГТР) соединены с сигнальным проводом Ш, который также присоединен через R3 к выходу БП, вход второго ПЕР объединен с выходом Q седьмого ТР, с входом четвертого ФИ и с первым (инверсным) входом пятой схемы 2И, S-вход седьмого ТР соединен с инверсным выходом пятой схемы 2И и с входом пятого ФИ, схема 2И/К-ИЛИ первым входом соединена с сигнальным проводом Ш, а инверсные входы схемы 2И/К-ИЛИ соединены с соответствующими выходами второго ДШ, входы которого в свою очередь также соединены с соответствующими выходами третьего СЧ, счетный вход которого соединен с первым выходом второго ГИ, обнуляющий вход R третьего СЧ соединен с выходом седьмой схемы 2ИЛИ, первый вход которой объединен с выходом четвертого ФИ, выход второго интегрирующего звена [R4-С3] соединен с первым входом восьмой схемы 2ИЛИ, а вход второго интегрирующего звена [R4-С3] соединен с выходом БП, к которому также подключены выводы питания микросхем КП, первая клемма второй КН объединена с выводом R5 и первым инверсным входом шестой схемы 2И, второй вход которой соединен с сигнальным проводом Ш, другой вывод R5 объединен с выходом БП, вторая клемма второй КН соединена с общим проводом, к которому также присоединен общий выход БП, второй вход восьмой схемы 2ИЛИ соединен через шестой ФИ с инверсным выходом шестой схемы 2И.

Инверсный выход ПР соединен с первым входом седьмой схемы 2И, второй вход которой соединен с инверсным выходом пятого ФИ, а прямой выход пятого ФИ соединен с первым входом восьмой схемы 2И, второй вход восьмой схемы 2И соединен со вторым выходом второго ГИ, выход восьмой схемы 2И объединен со счетным входом четвертого СЧ и первым входом девятой схемы 2И, второй вход которой соединен с выходом Q1 первого разряда пятого СЧ, выход девятой схемы 2И соединен с устанавливающим режим записи входом Р1, к Q-выходу восьмого ТР присоединена первым входом вторая схема 3И, второй вход которой соединен с третьим выходом второго ГИ, третий вход второй схемы 3И соединен с инверсным выходом пятого ФИ, к выходу второй схемы 3И присоединен Р2 входом, устанавливающим режим чтения ячеек, а также к выходу второй схемы 3И присоединен счетный вход шестого СЧ, первым (инверсным) входом схема 5И соединена с инверсным выходом ПР, выход Р1 соединен со вторым (инверсным) входом схемы 5И, а третий вход схемы 5И соединен с выходом Q2 второго разряда пятого СЧ и с входом, устанавливающим режим чтения Р1, четвертый вход схемы 5И соединен с инверсным выходом схемы 4И-НЕ, а пятый вход схемы 5И соединен с выходом восьмой схемы 2И, инверсный выход схемы 5И объединен с S-входом девятого ТР, со счетным входом седьмого СЧ, с S-входом восьмого ТР и входом дополнительно введенного второго ФЗ, выходы шестого и седьмого СЧ соединены с соответствующими входами дополнительно введенного мультиплексора (М), адресный вход А которого соединен с инверсным выходом пятого ФИ.

Выходы М соединены с адресными входами Р2, информационные входы которого объединены с соответствующими выходами четвертого СЧ и с соответствующими адресными входами Р1, вход, управляющий режимом записи Р2, соединен с выходом второго ФЗ, выходы Р2 через четвертый ДШ соединены с соответствующими входами первого блока Св.И, выходы седьмого СЧ также соединены с соответствующими входами схемы 4И-НЕ, выход Q девятого ТР соединен через первый вход девятой схемы 2ИЛИ с запускающим входом Зв.И, выход Q десятого ТР соединен со вторым входом девятой схемы 2ИЛИ, первым входом дополнительно введенная третья схема 3И соединена с инверсным выходом седьмой схемы 2И и входом седьмого ФИ, выход которого соединен с первым входом девятой схемы 2И, выход третьей схемы 3И соединен через первый вход десятой схемы 2ИЛИ с входом восьмого ФИ, выход которого соединен с первым входом одиннадцатой схемы 2ИЛИ, выход Q десятого ТР также объединен с входом, устанавливающим режим чтения пятого ДШ, и вторым входом десятой схемы 2ИЛИ, выходы пятого ДШ соединены с входами второго блока Св.И, инверсный выход девятой схемы 2И соединен с входом, устанавливающим режим записи РЗ, выходы которого соединены с соответствующими информационными входами пятого ДШ.

S-вход десятого ТР соединен с инверсным выходом дополнительно введенной четвертой схемы 3И, первый вход которой объединен с инверсным выходом седьмой схемы 2И, а второй вход четвертой схемы 3И объединен с выходом девятого ФИ и с третьим входом третьей схемы 3И, вход девятого ФИ объединен с выходом седьмой схемы 2И и со вторым входом СИ, первый вход которого соединен с выходом третьего ГИ, запускающий вход которого соединен с выходом Q одиннадцатого ТР, S-вход которого соединен с инверсным выходом седьмой схемы 2И, младший разряд восьмого СЧ соединен с инверсным S-входом двенадцатого ТР, выход Q которого соединен со вторым входом девятой схемы 2И, выход СИ соединен со счетным входом восьмого СЧ, выходы которого соединены с соответствующими информационными входами РЗ, выход Q двенадцатого ТР также соединен со вторым (инверсным) входом третьей схемы 3И и третьим входом четвертой схемы 3И, второй вход седьмой схемы 2ИЛИ объединен с R-входом седьмого ТР и выходом двенадцатой схемы 2ИЛИ, R-вход одиннадцатого ТР объединен с R-входом восьмого СЧ, с R-входом двенадцатого ТР, входом обнуления СИ и выходом одиннадцатой схемы 2ИЛИ, второй вход одиннадцатой схемы 2ИЛИ соединен с выходом восьмой схемы 2ИЛИ, обнуляющим входом P1, P2, Р3, вторым входом двенадцатой схемы 2ИЛИ, входом R обнуления СЧ4, СЧ5, СЧ6, СЧ7, ТР8, ТР9, ТР10, при этом первый вход двенадцатой схемы 2ИЛИ соединен с инверсным выходом схемы 2И/К-ИЛИ.

Техническим результатом системы пожарно-охранной сигнализации является обеспечение регулярного контроля работоспособности извещателей, осуществляемого по единому запросу для всех извещателей при обязательной однозначной очередности их ответов, благодаря чему повышена надежность работы системы пожарно-охранной системы.

Дополнительным техническим результатом является сокращение количества проводов шлейфа до двух, что способствует снижению стоимости пожарно-охранной сигнализации.

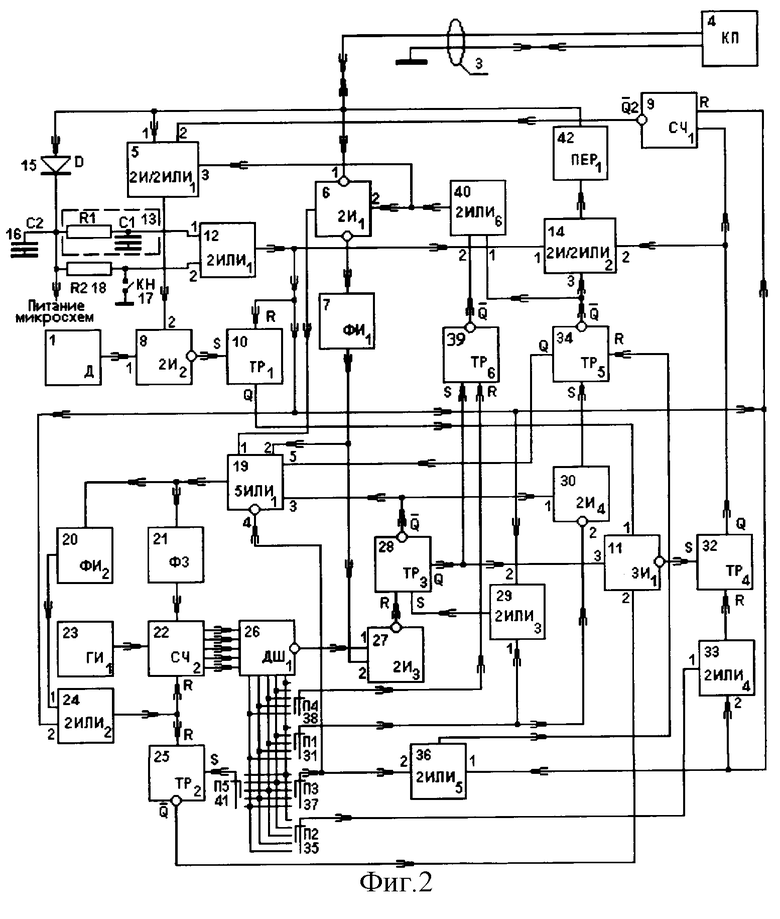

На фиг.1 приведена блок-схема приемопередающего контрольного пульта системы пожарно-охранной сигнализации;

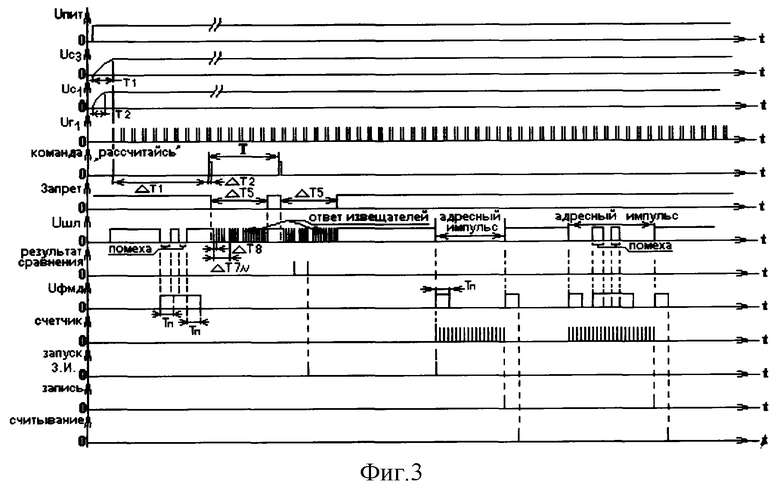

на фиг.2 приведена блок-схема блока сопряжения системы пожарно-охранной сигнализации;

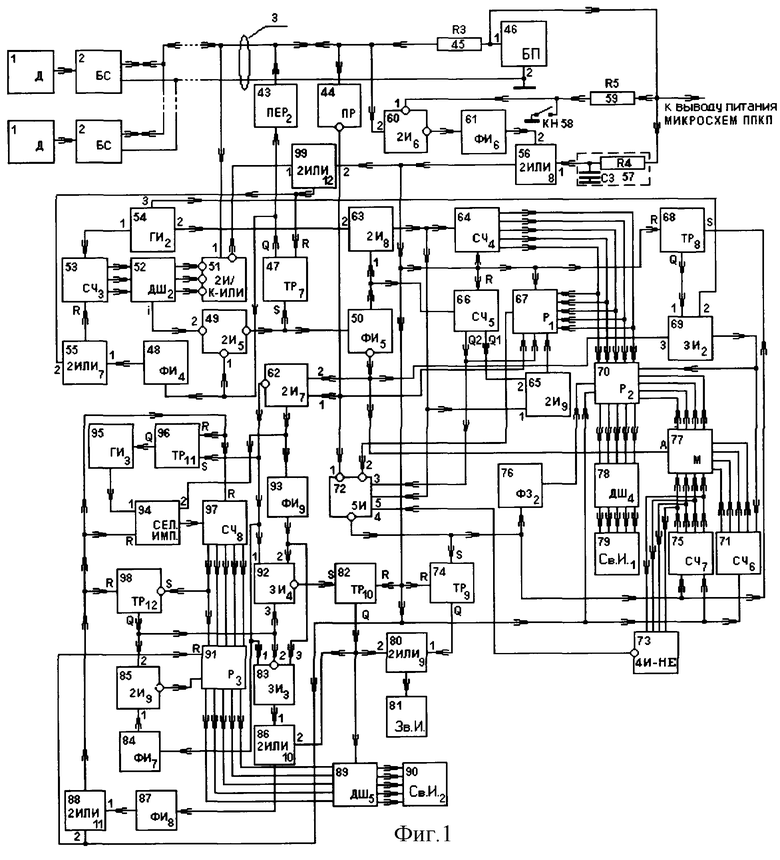

на фиг.3 - эпюра напряжений на выходе блоков системы.

Система пожарно-охранной сигнализации содержит ряд абонентских датчиков (Д) 1 (фиг.1, 2), каждый из которых соединен через свой блок сопряжения (БС) 2 посредством двух проводов шлейфа (Ш) 3 с входом контрольного пульта (КП) 4. Все БС 2 подключены к проводам шлейфа параллельно. В каждом БС 2 (фиг.2) первый вход первой схемы 2И/2ИЛИ 5 объединен с инверсным входом первой схемы 2И 6, инверсный выход первой схемы 2И 6 соединен со входом первого формирователя импульса (ФИ) 7, первый вход второй схемы 2И 8 соединен с выходом соответствующего Д 1, второй вход второй схемы 2И 8 соединен с выходом первой схемы 2И/2ИЛИ 5, второй вход первой схемы 2И/2ИЛИ 5 объединен с инверсным выходом  2 второго разряда первого счетчика (СЧ) 9, инверсный выход второй схемы 2И 8 соединен с S-входом первого триггера (ТР) 10, к выходу Q которого подсоединена первым входом первая схема 3И 11, R-вход первого ТР 10 соединен с выходом первой схемы 2ИЛИ 12, выход первого интегрирующего звена (ИЗ) 13 [R1-C1] соединен с первым входом первой схемы 2ИЛИ 12, выход первой схемы 2ИЛИ 12 также соединен с первым входом второй схемы 2И/2ИЛИ 14, к входу первого ИЗ 13 подсоединен катодом диод (D) 15, анод которого в свою очередь объединен с инверсным входом первой схемы 2И 6, причем к месту объединения входа ИЗ 13 и D 15 также подсоединен второй конденсатор (С) 16, при этом второй вход первой схемы 2ИЛИ 12 соединен с первой клеммой первой кнопки начальной установки (КН) 17 и через второй резистор (R) 18 соединен с катодом D 15.

2 второго разряда первого счетчика (СЧ) 9, инверсный выход второй схемы 2И 8 соединен с S-входом первого триггера (ТР) 10, к выходу Q которого подсоединена первым входом первая схема 3И 11, R-вход первого ТР 10 соединен с выходом первой схемы 2ИЛИ 12, выход первого интегрирующего звена (ИЗ) 13 [R1-C1] соединен с первым входом первой схемы 2ИЛИ 12, выход первой схемы 2ИЛИ 12 также соединен с первым входом второй схемы 2И/2ИЛИ 14, к входу первого ИЗ 13 подсоединен катодом диод (D) 15, анод которого в свою очередь объединен с инверсным входом первой схемы 2И 6, причем к месту объединения входа ИЗ 13 и D 15 также подсоединен второй конденсатор (С) 16, при этом второй вход первой схемы 2ИЛИ 12 соединен с первой клеммой первой кнопки начальной установки (КН) 17 и через второй резистор (R) 18 соединен с катодом D 15.

Вторая клемма первой КН 17 соединена с общим проводом (землей), к выходу первой схемы 2И 6 подсоединена первым входом схема 5ИЛИ 19, к выходу которой подсоединен входом второй ФИ 20 и входом первый формирователь задержки (ФЗ) 21, к выходу первого ФЗ 21 в свою очередь соединен с входом второго СЧ 22, разрешающим ему счет, счетный вход этого счетчика соединен с выходом первого генератора импульсов (ГИ) 23, обнуляющий вход R второго СЧ 22 соединен с выходом второй схемы 2ИЛИ 24, первый вход которой соединен с выходом второго ФИ 20, а второй вход второй схемы 2ИЛИ 24 объединен с выходом первой схемы 2ИЛИ 12, выход второй схемы 2ИЛИ 24 также соединен с R-входом второго ТР 25, выходы второго СЧ 22 соединены с соответствующими входами первого дешифратора (ДШ) 26, инверсный выход которого соединен с первым входом третьей схемы 2И 27, второй вход которой объединен с выходом первого ФИ 8 и со вторым входом схемы 5ИЛИ 19, инверсный выход  второго ТР 25 соединен со вторым входом первой схемы 3И 11, инверсный выход

второго ТР 25 соединен со вторым входом первой схемы 3И 11, инверсный выход  третьего ТР 28 объединен с третьим входом схемы 5ИЛИ 19, выход Q третьего ТР 28 соединен с третьим входом первой схемы 3И 11, R-вход третьего ТР 28 соединен с инверсным выходом третьей схемы 2И 27, a S-вход третьего ТР 28 соединен с выходом третьей схемы 2ИЛИ 29, инверсный выход Q третьего ТР 28 объединен с первым входом четвертой схемы 2И 30 и третьим входом схемы 5ИЛИ, при этом второй (инверсный) вход четвертой схемы 2И 30 объединен с первым входом третьей схемы 2ИЛИ 29 и выходом однополюсного многопозиционного переключателя П1 31, второй вход третьей схемы 2ИЛИ 29 соединен с выходом первой схемы 2ИЛИ 12, инверсный выход первой схемы 3И 11 соединен с S-входом четвертого ТР 32, R-вход которого соединен с выходом четвертой схемы 2ИЛИ 33, а выход Q четвертого ТР 32 соединен со счетным входом первого СЧ 9 и вторым входом второй схемы 2И/2ИЛИ 14, третий вход которой соединен с инверсным выходом

третьего ТР 28 объединен с третьим входом схемы 5ИЛИ 19, выход Q третьего ТР 28 соединен с третьим входом первой схемы 3И 11, R-вход третьего ТР 28 соединен с инверсным выходом третьей схемы 2И 27, a S-вход третьего ТР 28 соединен с выходом третьей схемы 2ИЛИ 29, инверсный выход Q третьего ТР 28 объединен с первым входом четвертой схемы 2И 30 и третьим входом схемы 5ИЛИ, при этом второй (инверсный) вход четвертой схемы 2И 30 объединен с первым входом третьей схемы 2ИЛИ 29 и выходом однополюсного многопозиционного переключателя П1 31, второй вход третьей схемы 2ИЛИ 29 соединен с выходом первой схемы 2ИЛИ 12, инверсный выход первой схемы 3И 11 соединен с S-входом четвертого ТР 32, R-вход которого соединен с выходом четвертой схемы 2ИЛИ 33, а выход Q четвертого ТР 32 соединен со счетным входом первого СЧ 9 и вторым входом второй схемы 2И/2ИЛИ 14, третий вход которой соединен с инверсным выходом  пятого ТР 34, к первому входу четвертой схемы 2ИЛИ 33 присоединен выходом второй однополюсной многопозиционный переключатель П2 35, а второй вход четвертой схемы 2ИЛИ 33 объединен первым входом пятой схемы 2ИЛИ 36 и с выходом первой схемы 2ИЛИ 12, ко второму входу пятой схемы 2ИЛИ 36 присоединены выходом третий однополюсный многопозиционный переключатель ПЗ 37 и четвертый (инверсный) вход схемы 5ИЛИ 19, выход пятой схемы 2ИЛИ 36 соединен с R-входом пятого ТР 34, S-вход которого объединен с выходом четвертой схемы 2ИЛИ 30, пятый вход схемы 5ИЛИ 19 соединен с выходом Q пятого ТР 34, четвертый однополюсный многопозиционный переключатель П4 38 выходом соединен с R-входом шестого ТР 39, S вход которого соединен выходом Q третьего ТР 28, инверсный выход Q пятого ТР 34 соединен с первым входом шестой схемы 2ИЛИ 40, а второй вход шестой схемы 2ИЛИ 40 соединен с инверсный выходом

пятого ТР 34, к первому входу четвертой схемы 2ИЛИ 33 присоединен выходом второй однополюсной многопозиционный переключатель П2 35, а второй вход четвертой схемы 2ИЛИ 33 объединен первым входом пятой схемы 2ИЛИ 36 и с выходом первой схемы 2ИЛИ 12, ко второму входу пятой схемы 2ИЛИ 36 присоединены выходом третий однополюсный многопозиционный переключатель ПЗ 37 и четвертый (инверсный) вход схемы 5ИЛИ 19, выход пятой схемы 2ИЛИ 36 соединен с R-входом пятого ТР 34, S-вход которого объединен с выходом четвертой схемы 2ИЛИ 30, пятый вход схемы 5ИЛИ 19 соединен с выходом Q пятого ТР 34, четвертый однополюсный многопозиционный переключатель П4 38 выходом соединен с R-входом шестого ТР 39, S вход которого соединен выходом Q третьего ТР 28, инверсный выход Q пятого ТР 34 соединен с первым входом шестой схемы 2ИЛИ 40, а второй вход шестой схемы 2ИЛИ 40 соединен с инверсный выходом  шестого ТР 39, выход шестой схемы 2ИЛИ 40 соединен со вторым входом первой схемы 2И 6 и третьим входом первой схемы 2И/2ИЛИ 5.

шестого ТР 39, выход шестой схемы 2ИЛИ 40 соединен со вторым входом первой схемы 2И 6 и третьим входом первой схемы 2И/2ИЛИ 5.

К выходам первого ДШ 26 соответственно подсоединены входы однополюсных многопозиционных переключателей П1 31, П2 35, П3 37, П4 38, а также входы дополнительно введенного однополюсного многопозиционного переключателя П5 41, выход последнего соединен с S-входом второго ТР 25, к выходу второй схемы 2И/2ИЛИ 14 присоединен входом первый ПЕР 42, выход которого соединен с инверсным входом первой схемы 2И 6 и сигнальным проводом Ш 3, при этом в КП 4 выходом второй ПЕР 43 и входом ПР 44 соединены с сигнальным проводом Ш 3, который также присоединен через третий R 45 к выходу БП 46, вход второго ПЕР 43 объединен с выходом Q седьмого ТР 47, с входом четвертого ФИ 48 и с первым (инверсным) входом пятой схемы 2 И 49, S-вход седьмого ТР 47 соединен с инверсным выходом пятой схемы 2И 49 и входом пятого ФИ 50, схема 2И/К-ИЛИ 51 первым входом соединена с сигнальным проводом Ш 3, а инверсные входы этой схемы соединены с соответствующими выходами второго ДШ 52, входы которого в свою очередь также соединены с соответствующими выходами третьего СЧ 53, счетный вход которого соединен с первым выходом второго ГИ 54, обнуляющий вход R третьего СЧ 53 соединен с выходом седьмой схемы 2ИЛИ 55, первый вход которой объединен с выходом четвертого ФИ 48, выход второго ИЗ 57 [R4-С3] соединен с первым входом восьмой схемы 2ИЛИ 56, а вход второго ИЗ 57 [R4-С3] соединен с выходом БП 46, к которому также подключены выводы питания микросхем КП 4, первая клемма второй КН 58 объединена с выводом пятого R 59 и первым (инверсным) входом шестой схемы 2И 60, второй вход которой соединен с сигнальным проводом Ш 3, другой вывод пятого R 59 объединен с выходом БП 46, вторая клемма второй КН 58 соединена с общим проводом, к которому также присоединен общий выход БП 46, второй вход восьмой схемы 2ИЛИ 56 соединен через шестой ФИ 61 с инверсным выходом шестой схемы 2И 60.

Инверсный выход ПР 44 соединен с первым входом седьмой схемы 2И 62, второй вход которой соединен с инверсным выходом пятого ФИ 50, а прямой выход пятого ФИ 50 соединен с первым входом восьмой схемы 2И 63, второй вход восьмой схемы 2И 63 соединен со вторым выходом второго ГИ 54, выход восьмой схемы 2И 63 объединен со счетным входом четвертого СЧ 64 и первым входом девятой схемы 2И 65, второй вход которой соединен с выходом первого разряда Q1 пятого СЧ 66, выход девятой схемы 2И 65 соединен с устанавливающим режим записи входом первого Р 67, к Q выходу восьмого ТР 68 присоединена первым входом вторая схема 3И 69, второй вход которой соединен с третьим выходом второго ГИ 54, третий вход второй схемы 3И 69 соединен с инверсным выходом пятого ФИ 50, к выходу второй схемы 3И 69 присоединен второй Р 70 входом, устанавливающим режим чтения ячеек, а также к выходу второй схемы 3И 69 присоединен счетный вход шестого СЧ 71, первым (инверсным) входом схема 5И 72 соединена с инверсным выходом ПР 44, выход первого Р 67 соединен со вторым (инверсным) входом схемы 5И 72, а третий вход схемы 5И 72 соединен с выходом Q2 второго разряда пятого СЧ 66 и с входом, устанавливающим режим чтения первого Р 67, четвертый вход схемы 5И 72 соединен с инверсным выходом схемы 4И-НЕ 73, а пятый вход схемы 5И 72 соединен с выходом восьмой 2И 63, инверсный выход схемы 5И 72 объединен с S-входом девятого ТР 74, со счетным входом седьмого СЧ 75, с S-входом восьмого ТР 68, входом дополнительно введенного второго ФЗ 76, выходы шестого и седьмого СЧ 71, СЧ 75 соединены с соответствующими входами дополнительно введенного мультиплексора М 77, адресный вход А которого соединен с инверсным выходом пятого ФИ 50, выходы М 77 соединены с адресными входами второго Р 70, информационные входы которого объединены с соответствующими выходами четвертого СЧ 64 и с соответствующими адресными входами первого Р 67, вход, управляющий режимом записи второго Р 70, соединен с выходом второго ФЗ 76, выходы второго Р 70 через четвертый ДШ 78 соединены с соответствующими входами первого блока Св.И 79.

Выходы седьмого СЧ 75 также соединены с соответствующими входами второй схемы 4И-НЕ 73, Q-выход девятого ТР 74 соединен через первый вход девятой схемы 2ИЛИ 80 с запускающим входом Зв.И 81, выход Q десятого ТР 82 объединен со вторым входом девятой схемы 2ИЛИ 80.

Первым входом дополнительно введенная третья схема 3И 83 соединена с инверсным выходом седьмой схемы 2И 62 и входом седьмого ФИ 84, выход которого соединен с первым входом девятой схемы 2И 85, выход третьей схемы 3И 83 соединен через первый вход десятой схемы 2ИЛИ 86 с входом восьмого ФИ 87, выход которого соединен с первым входом одиннадцатой схемы 2ИЛИ 88.

Выход Q десятого ТР 82 также объединен с входом, устанавливающим режим чтения пятого ДШ 89, вторым входом девятой схемы 2ИЛИ 80 и вторым входом десятой схемы 2ИЛИ 86, выходы пятого ДШ 89 соединены с входами второго блока Св.И 90, инверсный выход девятой схемы 2И 85 соединен с входом, устанавливающим режим записи третьему Р 91, выходы третьего Р 91 соединены с соответствующими информационными входами пятого ДШ 89, S-вход десятого ТР 82 соединен с инверсным выходом дополнительно введенной четвертой схемы 3И 92, первый вход которой объединен с инверсным выходом седьмой схемы 2И 62, а второй вход четвертой схемы 3И 92 объединен с выходом девятого ФИ 93 и с третьим входом третьей схемы 3И 83, вход девятого ФИ 93 объединен с выходом седьмой схемы 2И 62 и со вторым входом СИ 94, первый вход которого соединен с выходом третьего ГИ 95, запускающий вход которого соединен с выходом Q одиннадцатого ТР 96, S-вход которого соединен с инверсным выходом седьмой схемы 2И 62, младший разряд восьмого СЧ 97 соединен с инверсным S-входом двенадцатого ТР 98, выход Q которого соединен со вторым входом девятой схемы 2И 85, выход СИ 94 соединен со счетным входом восьмого СЧ 97, выходы которого соединены с соответствующими информационными входами третьего Р 91, выход Q двенадцатого ТР 98 также соединен с третьим входом четвертой схемы 3И 92 и вторым (инверсным) входом третьей схемы 3И 83, второй вход седьмой схемы 2ИЛИ 55 объединен с R-входом седьмого ТР 47 и выходом двенадцатой схемы 2ИЛИ 99, R-вход одиннадцатого ТР 96 объединен с R-входом восьмого СЧ 97, R-входом двенадцатого ТР 98, входом обнуления СИ 94 и с выходом одиннадцатой схемы 2ИЛИ 88, второй вход одиннадцатой схемы 2ИЛИ 88 соединен с выходом восьмой схемы 2ИЛИ 56, обнуляющим входом первого Р 67, второго Р 70, третьего Р 91, вторым входом двенадцатой схемы 2ИЛИ 99, входом R обнуления СЧ 64, СЧ 66, СЧ 71, СЧ 75, ТР 68, ТР 74, ТР 82, при этом первый вход двенадцатой схемы 2ИЛИ 99 соединен с инверсным выходом схемы 2И/К-ИЛИ 51.

Работает система пожарно-охранной сигнализации (фиг.1 и 2) следующим образом.

При включении БП 46 на выходе восьмой схемы 2ИЛИ 56 формируется низкий уровень напряжения длительностью Т1 (фиг.3). Величина длительности Т1 определяется постоянной времени второго ИЗ 57, см. фиг.3. Этим уровнем напряжения осуществляются обнуление и удержание в этом состоянии выходов четвертого, пятого, шестого, седьмого СЧ 64, 66, 71, 75, первого, второго и третьего Р 67, 70, 91, выходов Q восьмого, девятого, десятого ТР 68, 74, 82, а обнуление восьмого СЧ 97, СИ 94, одиннадцатого, двенадцатого ТР 96, 97 осуществляется при помощи одиннадцатой схемы 2ИЛИ 88, формирование нулевого уровня напряжения на выходе Q седьмого ТР 47 и обнуление третьего СЧ 53 осуществляются посредством двенадцатой схемы 2ИЛИ 99.

Аналогично в каждом блоке сопряжения БС 2 первой схемой 2ИЛИ 12 осуществляется обнуление и удержание в этом состоянии выхода первого ТР 10 и выходов первого СЧ 9 в течение интервала времени Т2, равного величине постоянной времени первого ИЗ 13, (фиг.3), а посредством второй схемы 2ИЛИ 24, третьей схемы 2ИЛИ 29, четвертой схемы 2ИЛИ 33, пятой схемы 2ИЛИ 36, шестой схемы 2ИЛИ 40 происходит обнуление и удержание в этом состоянии выходов Q также в течение интервала времени Т2 второго, третьего, четвертого, пятого и шестого ТР 25, 28, 32, 34, 39, второго СЧ 22.

По окончании интервала времени Т1 на входах питания микросхем всех БС 2 и КП 4 установится номинальная величина напряжения и третий СЧ 53 начинает считать импульсы напряжения UГ1, которые вырабатывает на первом выходе второй ГИ 54 (кварцевый) с частотой F1, см. фиг.3. Через интервал времени AT 1 последовательно во времени на выходах второго ДШ 52 формируются импульсы напряжения, поступающие на инверсные входы микросхемы 2И/К-ИЛИ 51. При отсутствии низкого уровня напряжения в сигнальном проводе Ш 3 на момент окончания интервала времени ΔT 1 на инверсном выходе микросхемы 2И/К-ИЛИ 51 формируется низкий уровень напряжения, устанавливающий низкий уровень напряжения на выходе Q седьмого ТР 47 через двенадцатую схему 2ИЛИ 99.

С этого момента времени в сигнальном проводе Ш 3 второй ПЕР 43 устанавливает низкий уровень напряжения и запускается четвертый ФИ 48, формирующий короткий импульс напряжения, которым обнуляется третий СЧ 53 через первый вход седьмой схемой 2ИЛИ 55. Одновременно низкий уровень напряжения на выходе Q седьмого триггера 47 поступает на первый (инверсный) вход пятой схемы 2И 49. После обнуления третий СЧ 53 снова начинает считать импульсы напряжения, поступающие с первого выхода второго ГИ 54. Через интервал времени ΔТ2 на i-том выходе второго ДШ 52 формируется напряжение низкого уровня, которое через второй (инверсный) вход пятой схемы 2И 49 устанавливает высокий уровень напряжения на выходе Q седьмого ТР 47 и на выходе второго передатчика ПЕР 43.

Таким образом происходит формирование и передача всем БС 2 при помощи проводов Ш 3 импульса запроса "рассчитайсь", длительностью ΔТ2, см. фиг.3. Момент начала формирования импульса запроса "рассчитайсь" может начинаться, когда в сигнальном проводе Ш 3, а следовательно, на первом входе микросхемы 2И/К-ИЛИ 51 присутствует высокий уровень напряжения. Если в сигнальном проводе Ш 3 и на первом входе микросхемы 2И/К-ИЛИ 51 до момента начала формирования импульса запроса "рассчитайсь" зафиксирован низкий уровень напряжения, то формирование импульса запроса "рассчитайсь" сдвигается во времени до момента появления в сигнальном проводе высокого уровня напряжения.

Для этого К выходов второго ДШ 52 присоединяется к соответствующим инверсным К входам схемы 2И/К-ИЛИ 51, что дает возможность начать формирование импульса запроса "рассчитайсь" в течение интервала времени ΔТЗ, величина которого больше максимальной длительности адресного импульса.

Момент формирования низкого уровня напряжения в сигнальном проводе Ш 3 регистрируется всеми БС 2 для определения величины длительности низкого уровня напряжения. Для этого всегда в момент формирования низкого уровня напряжения в сигнальном проводе Ш 3 на выходе первой схемы 2И 6 формируется высокий уровень напряжения, который производит через первый вход схемы 5ИЛИ 19 запуск второго ФИ 20, который в свою очередь через первый вход второй схемы 2ИЛИ 24 производит обнуление выходов второго СЧ 22, и после временной задержки на выходе первого ФЗ 21 формируется высокий уровень напряжения, разрешающий второму СЧ 22 считать импульсы напряжения, вырабатываемые первым ГИ 23. Если во время фиксирования высокого уровня напряжения на инверсном выходе первого ДШ 26 в сигнальном проводе Ш 3 также зафиксирован высокий уровень напряжения, то это означает, что длительность измеренного интервала времени соответствует длительности импульса ΔТ2.

В момент формирования высокого уровня напряжения в сигнальном проводе Ш 3 на втором входе третьей схемы 2И 27 устанавливается высокий уровень напряжения в течение интервала времени ΔТ4 первым ФИ 7. Этот интервал времени ΔТ4 необходим для того, чтобы успел сформироваться на инверсном выходе третьей схемы 2И 27 низкий уровень напряжения, устанавливающий на инверсном выходе Q третьего ТР 28 высокий уровень напряжения, которым через третий вход схемы 5ИЛИ 19 осуществляется обнуление второго СЧ 22 посредством второго ФИ 20. В этот же момент времени низкий уровень напряжения на выходе Q третьего ТР 28 устанавливает на инверсном выходе  шестого ТР 39 низкий уровень напряжения, который через второй вход шестой схемой 2ИЛИ 40 запрещает всем БС 2 реагировать на появление в сигнальном проводе Ш 3 низкого уровня напряжения в течение интервала времени ΔТ5, длительность которого определяется интервалом времени, в течение которого должны выработать импульс ответа все БС 2.

шестого ТР 39 низкий уровень напряжения, который через второй вход шестой схемой 2ИЛИ 40 запрещает всем БС 2 реагировать на появление в сигнальном проводе Ш 3 низкого уровня напряжения в течение интервала времени ΔТ5, длительность которого определяется интервалом времени, в течение которого должны выработать импульс ответа все БС 2.

Величина интервала времени ΔТ5 устанавливается коммутацией одного из входов четвертого однополюсного многопозиционного переключателя П4 38 с его выходом. По окончании интервала времени ΔТ5 на выходе четвертого однополюсного многопозиционного переключателя П4 38 формируется импульс нулевого уровня напряжения, поступающий на R-вход шестого ТР 39, вследствие чего на инверсном выходе  шестого ТР 39 устанавливается высокий уровень напряжения, поступающий на второй вход шестой схемы 2ИЛИ 40, тем самым разрешая первой схеме 2И 6 регистрацию низкого уровня напряжения, появляющегося в сигнальном проводе Ш 3, и выработать адресный импульс в случае срабатывания Д1. В ответ на импульс "запроса" каждый БС 2 вырабатывает импульс ответа длительностью ΔТ6 через фиксированную для каждого БС 2 величину задержки ответа ΔТ7, длительность которой измеряется интервалом времени с момента времени определения импульса "запрос" до момента формирования нулевого уровня напряжения на выходе первого однополюсного многопозиционного переключателя П1 31, причем величина длительности задержки ответа ΔТ7 для каждого БС 2 выбирается такой, чтобы совокупность импульсов ответа от всех БС 2 представляла последовательность импульсов напряжения одной и той же длительности ΔТ6 следующих друг за другом через равный промежуток времени ΔТ8, т.е. для N-го БС 2 величина длительности задержки ΔТ7 определяется выражением ΔТ7N=N·ΔT8+(N-1)·ΔT6.

шестого ТР 39 устанавливается высокий уровень напряжения, поступающий на второй вход шестой схемы 2ИЛИ 40, тем самым разрешая первой схеме 2И 6 регистрацию низкого уровня напряжения, появляющегося в сигнальном проводе Ш 3, и выработать адресный импульс в случае срабатывания Д1. В ответ на импульс "запроса" каждый БС 2 вырабатывает импульс ответа длительностью ΔТ6 через фиксированную для каждого БС 2 величину задержки ответа ΔТ7, длительность которой измеряется интервалом времени с момента времени определения импульса "запрос" до момента формирования нулевого уровня напряжения на выходе первого однополюсного многопозиционного переключателя П1 31, причем величина длительности задержки ответа ΔТ7 для каждого БС 2 выбирается такой, чтобы совокупность импульсов ответа от всех БС 2 представляла последовательность импульсов напряжения одной и той же длительности ΔТ6 следующих друг за другом через равный промежуток времени ΔТ8, т.е. для N-го БС 2 величина длительности задержки ΔТ7 определяется выражением ΔТ7N=N·ΔT8+(N-1)·ΔT6.

В момент окончания задержки ответа ΔТ7 БС 2 на выходе первого однополюсного многопозиционного переключателя П1 31 каждого БС 2 формируется амплитуда напряжения нулевого уровня, которая устанавливает на инверсном выходе  пятого триггера ТР 34 через второй вход четвертой схемы 2И 30 низкий уровень напряжения, при этом на выходе Q третьего ТР 28 формируется высокий уровень напряжения, вследствие чего на четвертом входе схемы 5ИЛИ 19 формируется напряжение высокого уровня. Так как после окончания переходного периода на первом входе второй схемы 2И/2ИЛИ 14 установлен высокий уровень напряжения, то появление на втором или третьем входе схемы 2И/2ИЛИ 14 низкого уровня напряжения вызовет формирование низкого уровня напряжения на выходе первого ПЕР 42.

пятого триггера ТР 34 через второй вход четвертой схемы 2И 30 низкий уровень напряжения, при этом на выходе Q третьего ТР 28 формируется высокий уровень напряжения, вследствие чего на четвертом входе схемы 5ИЛИ 19 формируется напряжение высокого уровня. Так как после окончания переходного периода на первом входе второй схемы 2И/2ИЛИ 14 установлен высокий уровень напряжения, то появление на втором или третьем входе схемы 2И/2ИЛИ 14 низкого уровня напряжения вызовет формирование низкого уровня напряжения на выходе первого ПЕР 42.

Формирование на третьем входе низкого уровня напряжения приводит к формированию переднего фронта импульса ответа и одновременно высоким уровнем напряжения с Q выхода пятого ТР 34 осуществляется обнуление второго СЧ 22, а затем разрешение ему счета импульсов напряжения, вырабатываемых первым ГИ 23. Величина длительности импульса ответа ΔТ6 устанавливается коммутацией одного из входов третьего однополюсного многопозиционного переключателя ПЗ 37 с его выходом, так как только через интервал времени ΔТ6 на выходе этого переключателя сформируется нулевой уровень напряжения, который установит через второй вход пятой схемы 2ИЛИ 36 на инверсном выходе  пятого ТР 34 напряжение высокого уровня.

пятого ТР 34 напряжение высокого уровня.

Таким образом, в сигнальном проводе Ш 3 при помощи второй схемы 2И/2ИЛИ 14 всех БС 2 формируется последовательность импульсов "ответа", следующих друг за другом через равный промежуток времени АТ8, см. фиг.3. В момент формирования заднего фронта импульса запроса "рассчитайсь" на инверсном выходе седьмого ТР 47 формируется высокий уровень напряжения, запускающий четвертый ФИ 48, который через первый вход седьмой схемы 2ИЛИ 55 обнуляет выходы третьего СЧ 53, который снова начинает считать импульсы напряжения, вырабатываемые на первом выходе вторым ГИ 54, а также одновременно запускается пятый ФИ 50, высокий уровень напряжения на выходе которого разрешает счет четвертому СЧ 64 через восьмую схему 2И 63 импульсов, вырабатываемых на втором выходе вторым ГИ 54, одновременно на инверсном выходе пятого ФИ 50 формируется низкий уровень напряжения, запрещающий седьмой схеме 2И 62 в течение интервала времени ΔТ5 реагировать на сигналы, принимаемые ПР 44, см. фиг.3.

Частота и длительность импульсов напряжения, вырабатываемых на втором выходе второго ГИ 54 и импульсов "ответа", вырабатываемых БС 2, таковы, что их появление на инверсном выходе ПР 44 и на счетном входе четвертого СЧ 64 возможно только одновременно. Количество импульсов, сосчитанное четвертым СЧ 64, на конкретный момент времени означает номер Д1 (адрес датчика) БС 2, который должен выработать в этот момент времени импульс "ответа" в виде низкого уровня напряжения, если этот извещатель находится в работоспособном состоянии, в противном случае в этот интервал времени в сигнальном проводе Ш 3 будет присутствовать высокий уровень напряжения.

Информация о работоспособности или неработоспособности Д 1 соответственно в виде высокого или низкого уровня напряжения записывается в ячейки первого Р 67 при первом опросе по команде "запись" с выхода ПР 44. После вырабатывания второй раз команды "рассчитайсь" на выходе второго разряда Q1 пятого СЧ 66 устанавливается высокий уровень напряжения и первый Р 67 переведется в режим чтения содержимого ячейки, адрес которой определяется количеством импульсов, сосчитанных четвертым СЧ 64 на данный момент времени.

На третьем и четвертом входах схемы 5И 72 с этого момента времени присутствует высокий уровень напряжения, а на пятом ее входе периодически формируется импульс высокого уровня напряжения, вырабатываемый восьмой схемой 2И 63, в течение длительности которого схемой 5И 72 осуществляется сравнение информации, содержащейся на первом и втором ее входах. На четвертом входе схемы 5И 72 будет сохраняться высокий уровень напряжения, вырабатываемый схемой 4И-НЕ 73, до тех пор, пока не произойдет регистрация числа двойного отсутствия ответных импульсов, равного максимальному числу, которое способен сосчитать седьмой СЧ 75.

Если после двух опросов одного и того же Д1 на первом и втором входах схемы 5И 72 присутствует низкий уровень напряжения, что означает неработоспособность этого Д1, то в этом случае на инверсном выходе этой схемы формируется низкий уровень напряжения, устанавливающий высокий уровень напряжения на Q-выходе девятого ТР 74, которым запускается Зв.И 81 через первый вход девятой схемы 2ИЛИ 80, и на выходах седьмого СЧ 75 формируется адрес ячейки второго Р 70, определяемый количеством регистрации неисправных Д1, в которую записывается номер неисправного Д1. Команда записи адреса неисправного Д1 вырабатывается после окончания временной задержки, вносимой вторым ФЗ 76, необходимой для формирования на адресных входах второго Р 70 адреса ячейки, см. фиг.3.

После окончания интервала времени ΔТ5, в течение которого должны ответить все подключенные к проводам Ш 3 извещатели, на инверсном выходе пятого ФИ 50 установится высокий уровень напряжения, вследствие этого М 77 будет коммутировать адреса ячеек второго Р 70 с выходов шестого СЧ 71 на адресные входы второго Р 70. Этот адрес будет отличен от нулевого значения, если была зафиксирована неработоспособность даже одного Д1, так как только в этом случае на Q-выходе восьмого ТР 68 установится высокий уровень напряжения.

Также после окончания интервала времени ΔТ5 приема импульсов "ответа" на третьем входе второй схемы 3И 69 устанавливается высокий уровень напряжения, и на выходе этой схемы будут формироваться импульсы высокого уровня напряжения идентичные импульсам, генерируемые на третьем выходе второго ГИ 54. Эти импульсы поступают на счетный вход шестого СЧ 71, на выходах которого формируется адрес ячейки второго Р 70, в которой записан адрес неработоспособного Д1, и также поступают на вход второго Р 70, управляющего режимом чтения. Вследствие этого адрес неработоспособного Д1 в двоичном коде поступает на входы четвертого ДШ 78, который преобразует этот код в десятичный и отображается первым блоком Св.И 79.

По окончании интервала времени ΔТ5 на втором входе седьмой схемы 2И 62 установятся высокий уровень напряжения и фиксирование низкого уровня напряжения в сигнальном проводе Ш 3 приведет к формированию высокого уровня на выходе ПР 44, что вызовет появление высокого уровня напряжения на первом входе седьмой схемы 2И 62. Это приведет к тому, что на S-входе одиннадцатого ТР 96 установится низкий уровень напряжения, а на его Q-выходе установится высокий уровень напряжения, вследствие чего третий ГИ 95 с этого момента начнет вырабатывать импульсы напряжения фиксированной частоты, которые поступают на первый вход СИ 94. В СИ 94 время непрерывного поступления импульсов с третьего ГИ 95 сравнивается с заранее заданной величиной максимальной длительности ожидаемой помехи (ТП), и в случае превышения времени непрерывного поступления импульсов от третьего ГИ 95 величины максимальной длительности ожидаемой помехи на выходе СИ 94 появляются импульсы напряжения, вырабатываемые третьим ГИ 95, при этом на втором входе СИ 94 обязательно присутствует высокий уровень напряжения. В момент формирования высокого уровня напряжения в сигнальном проводе Ш 3 фронтом сигнала, вырабатываемого на инверсном выходе седьмой схемы совпадения 2И 62, запускается седьмой ФИ 84, выходным сигналом которого через девятую схему 2И 85 осуществляется запись числа импульсов в третий Р 91, сосчитанных восьмым СЧ 97 на данный момент времени. В этот же момент времени седьмой схемой 2И 62 запускается девятый ФИ 93, который вырабатывает напряжение нулевого уровня, длительностью, равной максимальной длительности помехи. Если задний фронт принадлежит адресному импульсу, то после окончания интервала времени, равного максимальной длительности помехи, на всех входах четвертой схемы 3И 92 установится высокий уровень напряжения, вследствие этого низкий уровень напряжения на инверсном выходе четвертой схемы 3И 92 установит на Q-выходе десятого ТР 82 высокий уровень напряжения. Этот высокий уровень напряжения разрешает пятому ДШ 89 выдачу адреса сработавшего Д1, хранящегося в третьем Р 91, второму блоку Св.И 90 и через второй вход девятой схемы 2ИЛИ 80 запускает блок Зв.И 81, см. фиг.3.

Если низкий уровень напряжения в сигнальном проводе Ш 3 был вызван импульсом помехи, длительность которой заведомо меньше максимальной длительности помехи, то не выработается команда на выходе двенадцатого ТР 98 в виде высокого уровня напряжения на запись данных с выхода восьмого СЧ 97 в третий Р 91. После окончания импульса напряжения, вырабатываемого девятым ФИ 93, через первый вход десятой схемы 2ИЛИ 86 запускается восьмой ФИ 87, который через первый вход одиннадцатой схемы 2ИЛИ 88 осуществляет обнуление восьмого СЧ 97, одиннадцатого ТР 96, СИ 94, двенадцатого ТР 98, обнуление содержимого первого, второго и третьего Р 67, Р 70, Р 91, третьего, четвертого, пятого, шестого, седьмого СЧ 53, СЧ 64, СЧ 66, СЧ 71, СЧ 75, седьмого, восьмого, девятого, десятого ТР 47, ТР 68, ТР 74, ТР 82 осуществляется коммутацией второго входа шестой схемы 2И 60 при помощи КН 58 на общий провод, если в это время в сигнальном проводе Ш 3 присутствует высокий уровень напряжения. После этого система пожарно-охранной сигнализации вновь готова к приему и анализу информации от абонентов.

Изобретение позволило получить технический результат, а именно достигнута возможность регулярного контроля работоспособности извещателей [датчик - блок сопряжения], осуществляемого по единому запросу для всех извещателей при обязательно однозначной очередности их ответов, что повысило надежность работы системы пожарно-охранной сигнализации. Дополнительным техническим результатом является сокращение количества проводов шлейфа до двух, что способствует снижению стоимости системы пожарно-охранной сигнализации.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КООРДИНАТ МЕСТА ВЫСТРЕЛА ИЗ ОГНЕСТРЕЛЬНОГО ОРУЖИЯ (ВАРИАНТЫ) | 2008 |

|

RU2406964C2 |

| УСТРОЙСТВО ПОЖАРНОЙ СИГНАЛИЗАЦИИ | 2005 |

|

RU2293373C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ УГЛОВЫХ КООРДИНАТ МЕСТА ВЫСТРЕЛА ИЗ ОГНЕСТРЕЛЬНОГО ОРУЖИЯ | 2007 |

|

RU2366888C2 |

| УСТРОЙСТВО, ОПРЕДЕЛЯЮЩЕЕ УГЛОВЫЕ КООРДИНАТЫ МЕСТА ВЫСТРЕЛА ИЗ ОГНЕСТРЕЛЬНОГО ОРУЖИЯ | 2007 |

|

RU2359207C2 |

| СПОСОБ ЗАЩИТЫ ОТ СБОЕВ И ОТКАЗОВ ЭЛЕКТРОННОГО БЛОКА КОСМИЧЕСКОГО АППАРАТА, ВЫЗЫВАЕМЫХ ВНЕШНИМИ ВОЗДЕЙСТВУЮЩИМИ ФАКТОРАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2018 |

|

RU2693296C1 |

| Система записи и воспроизведения видеосигнала | 1990 |

|

SU1783635A1 |

| Многоканальное устройство тестового контроля логических узлов | 1990 |

|

SU1837295A1 |

| Цифровой интегрирующий вольтметр | 1983 |

|

SU1093984A2 |

| ЦВЕТОИЗЛУЧАЮЩЕЕ УСТРОЙСТВО СВЕТОФОРА | 2009 |

|

RU2390105C1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

Изобретение относится к области автоматики управления и связи, в том числе к электронной пожарно-охранной сигнализации. Технический результат - повышение надежности работы пожарно-охранной сигнализации. Результат достигается введением технических средств, которые позволяют обеспечивать регулярный контроль работоспособности извещателей [датчик-блок сопряжения], осуществляемый по единому импульсу запроса для всех извещателей при обязательно однозначной очередности их ответов. Связь контрольного пульта с извещателями осуществляется через два провода шлейфа, причем все извещатели подключены параллельно к проводам шлейфа, что стало возможным из-за малого (микроамперного) потребления тока микросхем извещателей. Каждый датчик соединен с проводами шлейфа через свой блок сопряжения. Блоки сопряжения анализируют длительность нулевого уровня напряжения в сигнальном проводе шлейфа и по определенной величине длительности импульса определяют его как импульс “запрос”, после чего все блоки сопряжения вырабатывают ответ в виде импульса напряжения нулевой амплитуды в сигнальный провод шлейфа одинаковой длительности извещателей после временной задержки, определенной величины для каждого извещателя, если извещатель исправен. Анализ импульсов ответа извещателей позволяет выработать соответствующее суждение. 3 ил.

Система пожарно-охранной сигнализации, содержащая ряд абонентских датчиков, каждый из которых через свой блок сопряжения соединен посредством проводов шлейфа с контрольным пультом, в который входят блок питания, генератор импульсов, счетчик, регистр, дешифратор, световая и звуковая индикация, формирователи импульса, схемы 2И, 2И-НЕ, 4И-НЕ, 2ИЛИ, триггеры, формирователь импульса максимальной длительности помехи, селектор импульса, ре3Исторы, конденсатор, и кнопку обнуления, отличающаяся тем, что в каждом блоке сопряжения первый вход первой схемы 2И/2ИЛИ объединен с инверсным входом первой схемы 2И, инверсный выход первой схемы 2И соединен с входом первого формирователя импульса, первый вход второй схемы 2И соединен с выходом соответствующего датчика, второй вход второй схемы 2И соединен с выходом первой схемы 2И/2ИЛИ, второй вход первой схемы 2И/2ИЛИ объединен с инверсным выходом  2 второго разряда первого счетчика, инверсный выход второй схемы 2И соединен с S входом первого триггера, к выходу Qкоторого подсоединена первым входом первая схема 3И, R вход первого триггера соединен с выходом первой схемы 2ИЛИ, выход первого интегрирующего звена [R1-C1] соединен с первым входом первой схемы 2ИЛИ, а выход первой схемы 2ИЛИ также соединен с первым входом второй схемы 2И/2ИЛИ, к входу первого интегрирующего звена [R1-C1] подсоединен катодом диод, анод которого, в свою очередь, объединен с инверсным входом первой схемы 2И, причем к месту объединения входа первого интегрирующего звена [R1-C1] и катода диода также подсоединен второй конденсатор, при этом второй вход первой схемы 2ИЛИ соединен с первой клеммой первой кнопки обнуления и через второй резистор соединен с катодом диода, вторая клемма первой кнопки обнуления соединена с общим проводом (землей), к выходу первой схемы 2И подсоединена первым входом схема 5ИЛИ, к выходу которой подсоединен входом первый формирователь задержки и вход второго формирователя импульса, к выходу первого формирователя задержки подсоединен разрешающим счет входом второй счетчик, счетный вход которого соединен с выходом первого генератора импульсов, обнуляющий вход R второго счетчика соединен с выходом второй схемы 2ИЛИ, первый вход которой соединен с выходом второго формирователя импульса, а второй вход второй схемы 2ИЛИ объединен с выходом первой схемы 2ИЛИ, выход второй схемы 2ИЛИ также соединен с R входом второго триггера, выходы второго счетчика соединены с соответствующими входами первого дешифратора, инверсный выход которого соединен с первым входом третьей схемы 2И, второй вход которой объединен с выходом первого формирователя импульса и со вторым входом схемы 5ИЛИ, инверсный выход

2 второго разряда первого счетчика, инверсный выход второй схемы 2И соединен с S входом первого триггера, к выходу Qкоторого подсоединена первым входом первая схема 3И, R вход первого триггера соединен с выходом первой схемы 2ИЛИ, выход первого интегрирующего звена [R1-C1] соединен с первым входом первой схемы 2ИЛИ, а выход первой схемы 2ИЛИ также соединен с первым входом второй схемы 2И/2ИЛИ, к входу первого интегрирующего звена [R1-C1] подсоединен катодом диод, анод которого, в свою очередь, объединен с инверсным входом первой схемы 2И, причем к месту объединения входа первого интегрирующего звена [R1-C1] и катода диода также подсоединен второй конденсатор, при этом второй вход первой схемы 2ИЛИ соединен с первой клеммой первой кнопки обнуления и через второй резистор соединен с катодом диода, вторая клемма первой кнопки обнуления соединена с общим проводом (землей), к выходу первой схемы 2И подсоединена первым входом схема 5ИЛИ, к выходу которой подсоединен входом первый формирователь задержки и вход второго формирователя импульса, к выходу первого формирователя задержки подсоединен разрешающим счет входом второй счетчик, счетный вход которого соединен с выходом первого генератора импульсов, обнуляющий вход R второго счетчика соединен с выходом второй схемы 2ИЛИ, первый вход которой соединен с выходом второго формирователя импульса, а второй вход второй схемы 2ИЛИ объединен с выходом первой схемы 2ИЛИ, выход второй схемы 2ИЛИ также соединен с R входом второго триггера, выходы второго счетчика соединены с соответствующими входами первого дешифратора, инверсный выход которого соединен с первым входом третьей схемы 2И, второй вход которой объединен с выходом первого формирователя импульса и со вторым входом схемы 5ИЛИ, инверсный выход  второго триггера соединен со вторым входом первой схемы 3И, инверсный выход

второго триггера соединен со вторым входом первой схемы 3И, инверсный выход  третьего триггера объединен с третьим входом схемы 5ИЛИ, выход Q

третьего триггера объединен с третьим входом схемы 5ИЛИ, выход Q третьего триггера соединен с третьим входом первой схемы 3И, R вход третьего триггера соединен с инверсным выходом третьей схемы 2И, a S вход третьего триггера соединен с выходом третьей схемы 2ИЛИ, к первому входу которой подсоединены вторым (инверсным) входом четвертая схема 2И и выход однополюсного многопозиционного переключателя, первый вход четвертой схемы 2И соединен с третьим входом схемы 5ИЛИ, а второй вход третьей схемы 2ИЛИ соединен с выходом первой схемы 2ИЛИ, инверсный выход первой схемы 3И соединен с S входом четвертого триггера, R вход которого соединен с выходом четвертой схемы 2ИЛИ, а выход Qчетвертого триггера соединен со счетным входом первого счетчика и вторым входом второй схемы 2И/2ИЛИ, третий вход которой соединен с инверсным выходом

третьего триггера соединен с третьим входом первой схемы 3И, R вход третьего триггера соединен с инверсным выходом третьей схемы 2И, a S вход третьего триггера соединен с выходом третьей схемы 2ИЛИ, к первому входу которой подсоединены вторым (инверсным) входом четвертая схема 2И и выход однополюсного многопозиционного переключателя, первый вход четвертой схемы 2И соединен с третьим входом схемы 5ИЛИ, а второй вход третьей схемы 2ИЛИ соединен с выходом первой схемы 2ИЛИ, инверсный выход первой схемы 3И соединен с S входом четвертого триггера, R вход которого соединен с выходом четвертой схемы 2ИЛИ, а выход Qчетвертого триггера соединен со счетным входом первого счетчика и вторым входом второй схемы 2И/2ИЛИ, третий вход которой соединен с инверсным выходом  пятого триггера, к первому входу четвертой схемы 2ИЛИ присоединен выходом второй однополюсный многопозиционный переключатель, а второй вход четвертой схемы 2ИЛИ объединен с первым входом пятой схемы 2ИЛИ и с выходом первой схемы 2ИЛИ, ко второму входу пятой схемы 2ИЛИ присоединены выходом третий однополюсный многопозиционный переключатель и четвертый (инверсный) вход схемы 5ИЛИ, выход пятой схемы 2ИЛИ соединен с R входом пятого триггера, S вход которого объединен с выходом четвертой схемы 2И, пятый вход схемы 5ИЛИ соединен с выходом Qпятого триггера, четвертый однополюсный многопозиционный переключатель выходом соединен с R входом шестого триггера, S вход которого соединен с Qвыходом третьего триггера, инверсный выход

пятого триггера, к первому входу четвертой схемы 2ИЛИ присоединен выходом второй однополюсный многопозиционный переключатель, а второй вход четвертой схемы 2ИЛИ объединен с первым входом пятой схемы 2ИЛИ и с выходом первой схемы 2ИЛИ, ко второму входу пятой схемы 2ИЛИ присоединены выходом третий однополюсный многопозиционный переключатель и четвертый (инверсный) вход схемы 5ИЛИ, выход пятой схемы 2ИЛИ соединен с R входом пятого триггера, S вход которого объединен с выходом четвертой схемы 2И, пятый вход схемы 5ИЛИ соединен с выходом Qпятого триггера, четвертый однополюсный многопозиционный переключатель выходом соединен с R входом шестого триггера, S вход которого соединен с Qвыходом третьего триггера, инверсный выход  пятого триггера соединен с первым входом шестой схемы 2ИЛИ, а второй вход шестой схемы 2ИЛИ соединен с инверсным выходом

пятого триггера соединен с первым входом шестой схемы 2ИЛИ, а второй вход шестой схемы 2ИЛИ соединен с инверсным выходом  шестого триггера, выход шестой схемы 2ИЛИ соединен со вторым входом первой схемы 2И и третьим входом первой схемы 2И/2ИЛИ, к выходам первого дешифратора соответственно подсоединены входы первого, второго, третьего, четвертого однополюсных многопозиционных переключателей, а также входы дополнительно введенного пятого многопозиционного переключателя, выход последнего соединен с S входом второго триггера, к выходу второй схемы 2И/2ИЛИ присоединен входом первый передатчик, выход которого соединен с инверсным входом первой схемы 2И, при этом в контрольном пульте выходом второй передатчик и входом приемник соединены с сигнальным проводом шлейфа, который также присоединен через третий резистор к выходу блока питания, вход второго передатчика объединен с выходом Qседьмого триггера, с входом четвертого формирователя импульса и с первым (инверсным) входом пятой схемы 2И, S вход седьмого триггера соединен с инверсным выходом пятой схемы 2И и с входом пятого формирователя импульса, схема 2И/К-ИЛИ первым входом соединена с сигнальным проводом шлейфа, а инверсные входы схемы 2И/К-ИЛИ соединены с соответствующими выходами второго дешифратора, входы которого, в свою очередь, также соединены с соответствующими выходами третьего счетчика, счетный вход которого соединен с первым выходом второго генератора импульсов, обнуляющий вход R третьего счетчика соединен с выходом седьмой схемы 2ИЛИ, первый вход которой объединен с выходом четвертого формирователя импульса, выход второго интегрирующего звена [R4 - С3]соединен с первым входом восьмой схемы 2ИЛИ, а вход второго интегрирующего звена [R4 - C3] соединен с выходом блока питания, к которому также подключены выводы питания микросхем контрольного пульта, первая клемма второй кнопки обнуления объединена с выводом пятого резистора и первым инверсным входом шестой схемы 2И, второй вход которой соединен с сигнальным проводом шлейфа, другой вывод пятого резистора объединен с выходом блока питания, вторая клемма второй кнопки обнуления соединена с общим проводом, к которому также присоединен общий выход блока питания, второй вход восьмой схемы 2ИЛИ соединен через шестой формирователь импульса с инверсным выходом шестой схемы 2И, инверсный выход приемника соединен с первым входом седьмой схемы 2И, второй вход которой соединен с инверсным выходом пятого формирователя импульса, а прямой выход пятого формирователя импульса соединен с первым входом восьмой схемы 2И, второй вход восьмой схемы 2И соединен со вторым выходом второго генератора импульсов, выход восьмой схемы 2И объединен со счетным входом четвертого счетчика и первым входом девятой схемы 2И, второй вход которой соединен с выходом Q1первого разряда пятого счeтчика, выход девятой схемы 2И соединен с устанавливающим режим записи входом первого регистра, к Qвыходу восьмого триггера присоединена первым входом вторая схема 3И, второй вход которой соединен с третьим выходом второго генератора импульсов, третий вход второй схемы 3И соединен с инверсным выходом пятого формирователя импульса, к выходу второй схемы 3И присоединен второй регистр входом, устанавливающим режим чтения ячеек, а также к выходу второй схемы 3И присоединен счетный вход шестого счетчика, первым (инверсным) входом схема 5И соединена с инверсным выходом приемника, выход первого регистра соединен со вторым (инверсным) входом схемы 5И, а третий вход схемы 5И соединен с выходом Q2второго разряда пятого счетчика и с входом, устанавливающим режим чтения первому регистру, четвертый вход схемы 5И соединен с инверсным выходом схемы 4И-НЕ, а пятый вход схемы 5И соединен с выходом восьмой схемы 2И, инверсный выход схемы 5И объединен с S входом девятого триггера, со счетным входом седьмого счeтчика, с S входом восьмого триггера и входом дополнительно введенного второго формирователя задержки, выходы шестого и седьмого счeтчиков соединены с соответствующими входами дополнительно введенного мультиплексора, адресный вход которого соединен с инверсным выходом пятого формирователя импульса, выходы мультиплексора соединены с адресными входами второго регистра, информационные входы которого объединены с соответствующими выходами четвертого счeтчика и с соответствующими адресными входами первого регистра, вход, управляющий режимом записи второго регистра, соединен с выходом второго формирователя задержки, выходы второго регистра через четвертый дешифратор соединены с соответствующими входами первого блока световой индикации, выходы седьмого счтчика также соединены с соответствующими входами схемы 4И-НЕ, выход Qдевятого триггера соединен через первый вход девятой схемы 2ИЛИ с запускающим входом звуковой индикации, выход Qдесятого триггера соединен со вторым входом девятой схемы 2ИЛИ, первым входом дополнительно введенная третья схема 3И соединена с инверсным выходом седьмой схемы 2И и входом седьмого формирователя импульса, выход которого соединен с первым входом девятой схемы 2И, выход третьей схемы 3И соединен через первый вход десятой схемы 2ИЛИ с входом восьмого формирователя импульса, выход которого соединен с первым входом одиннадцатой схемы 2ИЛИ, выход Qдесятого триггера также объединен с входом, устанавливающим режим чтения пятого дешифратора, и вторым входом десятой схемы 2ИЛИ, выходы пятого дешифратора соединены с входами второго блока световой индикации, инверсный выход девятой схемы 2И соединен с входом, устанавливающим режим записи третьего регистра, выходы которого соединены с соответствующими информационными входами пятого дешифратора, S вход десятого триггера соединен с инверсным выходом дополнительно введенной четвертой схемы 3И, первый вход которой объединен с инверсным выходом седьмой схемы 2И, а второй вход четвертой схемы 3И объединен с выходом девятого формирователя импульса и третьим входом третьей схемы 3И, вход девятого формирователя импульса объединен с выходом седьмой схемы 2И и со вторым входом селектора импульса, первый вход которого соединен с выходом третьего генератора импульсов, запускающий вход которого соединен с выходом Qодиннадцатого триггера, S вход которого соединен с инверсным выходом седьмой схемы 2И, младший разряд восьмого счетчика соединен с инверсным S входом двенадцатого триггера, выход Q которого соединен со вторым входом девятой схемы 2И, выход селектора импульса соединен со счетным входом восьмого счетчика, выходы которого соединены с соответствующими информационными входами третьего регистра, выход Qдвенадцатого триггера также соединен со вторым (инверсным) входом третьей схемы 3И и третьим входом четвертой схемы 3И, второй вход седьмой схемы 2ИЛИ объединен с R входом седьмого триггера и выходом двенадцатой схемы 2ИЛИ, R вход одиннадцатого триггера объединен с R входом восьмого счетчика, с R входом двенадцатого триггера, входом обнуления селектора импульса и выходом одиннадцатой схемы 2ИЛИ, второй вход одиннадцатой схемы 2ИЛИ соединен с выходом восьмой схемы 2ИЛИ, обнуляющим входом первого, второго, третьего регистров, вторым входом двенадцатой схемы 2ИЛИ, входом R обнуления четвертого, пятого, шестого, седьмого счетчиков, восьмого, девятого и десятого триггеров, при этом первый вход двенадцатой схемы 2ИЛИ соединен с инверсным выходом схемы 2И/К-ИЛИ.

шестого триггера, выход шестой схемы 2ИЛИ соединен со вторым входом первой схемы 2И и третьим входом первой схемы 2И/2ИЛИ, к выходам первого дешифратора соответственно подсоединены входы первого, второго, третьего, четвертого однополюсных многопозиционных переключателей, а также входы дополнительно введенного пятого многопозиционного переключателя, выход последнего соединен с S входом второго триггера, к выходу второй схемы 2И/2ИЛИ присоединен входом первый передатчик, выход которого соединен с инверсным входом первой схемы 2И, при этом в контрольном пульте выходом второй передатчик и входом приемник соединены с сигнальным проводом шлейфа, который также присоединен через третий резистор к выходу блока питания, вход второго передатчика объединен с выходом Qседьмого триггера, с входом четвертого формирователя импульса и с первым (инверсным) входом пятой схемы 2И, S вход седьмого триггера соединен с инверсным выходом пятой схемы 2И и с входом пятого формирователя импульса, схема 2И/К-ИЛИ первым входом соединена с сигнальным проводом шлейфа, а инверсные входы схемы 2И/К-ИЛИ соединены с соответствующими выходами второго дешифратора, входы которого, в свою очередь, также соединены с соответствующими выходами третьего счетчика, счетный вход которого соединен с первым выходом второго генератора импульсов, обнуляющий вход R третьего счетчика соединен с выходом седьмой схемы 2ИЛИ, первый вход которой объединен с выходом четвертого формирователя импульса, выход второго интегрирующего звена [R4 - С3]соединен с первым входом восьмой схемы 2ИЛИ, а вход второго интегрирующего звена [R4 - C3] соединен с выходом блока питания, к которому также подключены выводы питания микросхем контрольного пульта, первая клемма второй кнопки обнуления объединена с выводом пятого резистора и первым инверсным входом шестой схемы 2И, второй вход которой соединен с сигнальным проводом шлейфа, другой вывод пятого резистора объединен с выходом блока питания, вторая клемма второй кнопки обнуления соединена с общим проводом, к которому также присоединен общий выход блока питания, второй вход восьмой схемы 2ИЛИ соединен через шестой формирователь импульса с инверсным выходом шестой схемы 2И, инверсный выход приемника соединен с первым входом седьмой схемы 2И, второй вход которой соединен с инверсным выходом пятого формирователя импульса, а прямой выход пятого формирователя импульса соединен с первым входом восьмой схемы 2И, второй вход восьмой схемы 2И соединен со вторым выходом второго генератора импульсов, выход восьмой схемы 2И объединен со счетным входом четвертого счетчика и первым входом девятой схемы 2И, второй вход которой соединен с выходом Q1первого разряда пятого счeтчика, выход девятой схемы 2И соединен с устанавливающим режим записи входом первого регистра, к Qвыходу восьмого триггера присоединена первым входом вторая схема 3И, второй вход которой соединен с третьим выходом второго генератора импульсов, третий вход второй схемы 3И соединен с инверсным выходом пятого формирователя импульса, к выходу второй схемы 3И присоединен второй регистр входом, устанавливающим режим чтения ячеек, а также к выходу второй схемы 3И присоединен счетный вход шестого счетчика, первым (инверсным) входом схема 5И соединена с инверсным выходом приемника, выход первого регистра соединен со вторым (инверсным) входом схемы 5И, а третий вход схемы 5И соединен с выходом Q2второго разряда пятого счетчика и с входом, устанавливающим режим чтения первому регистру, четвертый вход схемы 5И соединен с инверсным выходом схемы 4И-НЕ, а пятый вход схемы 5И соединен с выходом восьмой схемы 2И, инверсный выход схемы 5И объединен с S входом девятого триггера, со счетным входом седьмого счeтчика, с S входом восьмого триггера и входом дополнительно введенного второго формирователя задержки, выходы шестого и седьмого счeтчиков соединены с соответствующими входами дополнительно введенного мультиплексора, адресный вход которого соединен с инверсным выходом пятого формирователя импульса, выходы мультиплексора соединены с адресными входами второго регистра, информационные входы которого объединены с соответствующими выходами четвертого счeтчика и с соответствующими адресными входами первого регистра, вход, управляющий режимом записи второго регистра, соединен с выходом второго формирователя задержки, выходы второго регистра через четвертый дешифратор соединены с соответствующими входами первого блока световой индикации, выходы седьмого счтчика также соединены с соответствующими входами схемы 4И-НЕ, выход Qдевятого триггера соединен через первый вход девятой схемы 2ИЛИ с запускающим входом звуковой индикации, выход Qдесятого триггера соединен со вторым входом девятой схемы 2ИЛИ, первым входом дополнительно введенная третья схема 3И соединена с инверсным выходом седьмой схемы 2И и входом седьмого формирователя импульса, выход которого соединен с первым входом девятой схемы 2И, выход третьей схемы 3И соединен через первый вход десятой схемы 2ИЛИ с входом восьмого формирователя импульса, выход которого соединен с первым входом одиннадцатой схемы 2ИЛИ, выход Qдесятого триггера также объединен с входом, устанавливающим режим чтения пятого дешифратора, и вторым входом десятой схемы 2ИЛИ, выходы пятого дешифратора соединены с входами второго блока световой индикации, инверсный выход девятой схемы 2И соединен с входом, устанавливающим режим записи третьего регистра, выходы которого соединены с соответствующими информационными входами пятого дешифратора, S вход десятого триггера соединен с инверсным выходом дополнительно введенной четвертой схемы 3И, первый вход которой объединен с инверсным выходом седьмой схемы 2И, а второй вход четвертой схемы 3И объединен с выходом девятого формирователя импульса и третьим входом третьей схемы 3И, вход девятого формирователя импульса объединен с выходом седьмой схемы 2И и со вторым входом селектора импульса, первый вход которого соединен с выходом третьего генератора импульсов, запускающий вход которого соединен с выходом Qодиннадцатого триггера, S вход которого соединен с инверсным выходом седьмой схемы 2И, младший разряд восьмого счетчика соединен с инверсным S входом двенадцатого триггера, выход Q которого соединен со вторым входом девятой схемы 2И, выход селектора импульса соединен со счетным входом восьмого счетчика, выходы которого соединены с соответствующими информационными входами третьего регистра, выход Qдвенадцатого триггера также соединен со вторым (инверсным) входом третьей схемы 3И и третьим входом четвертой схемы 3И, второй вход седьмой схемы 2ИЛИ объединен с R входом седьмого триггера и выходом двенадцатой схемы 2ИЛИ, R вход одиннадцатого триггера объединен с R входом восьмого счетчика, с R входом двенадцатого триггера, входом обнуления селектора импульса и выходом одиннадцатой схемы 2ИЛИ, второй вход одиннадцатой схемы 2ИЛИ соединен с выходом восьмой схемы 2ИЛИ, обнуляющим входом первого, второго, третьего регистров, вторым входом двенадцатой схемы 2ИЛИ, входом R обнуления четвертого, пятого, шестого, седьмого счетчиков, восьмого, девятого и десятого триггеров, при этом первый вход двенадцатой схемы 2ИЛИ соединен с инверсным выходом схемы 2И/К-ИЛИ.

| ИЗБИРАТЕЛЬНОЕ УСТРОЙСТВО ИДЕНТИФИКАЦИИ ВЫЗОВА ОТ АБОНЕНТА | 1998 |

|

RU2136050C1 |

Авторы

Даты

2004-10-20—Публикация

2003-02-18—Подача