Изобретение относится к вычислительной технике и может быть использовано для обеспечения отказоустойчивости оперативных запоминающих устройств.

Известно самокорректирующееся устройство [1], содержащее исходный комбинационный логический блок, избыточный комбинационный логический блок. блок вычисления синдрома, дешифратор ошибки и корректор, входы устройства соединены с входами исходного комбинационного логического блока и входами избыточного комбинационного логического блока, информационные выходы которого подключены к входам блока вычисления синдрома, выходы которого подключены к входам синдрома дешифратора ошибки, выходы которого подключены к входам исходного комбинационного блока, а выход является выходом устройства.

Недостатком устройства является невозможность коррекции кратных ошибок.

Наиболее близким по техническому решению является самокорректирующее устройство [2] , содержащее исходный вычислительный канал (оперативное запоминающее устройство), кодирующее устройство, избыточный вычислительный канал (разряды запоминающего устройства для хранения значений контрольных разрядов), блок вычисления синдрома, дешифратор, корректор, входы устройства подключены к входам исходной схемы и к входам кодирующего устройства, выходы которого подключены к первым входам блока вычисления синдрома, выходы исходного вычислительного канала подключены к вторым входам блока вычисления синдрома и к первым входам корректора, выходы блока вычисления синдрома подключены к входам дешифратора, соединенного своими выходами со вторыми входами корректора, выходы корректора являются выходами устройства.

Недостатком устройства является отсутствие возможности коррекции ошибок произвольной кратности в информационных разрядах.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения коррекции ошибок произвольной кратности, возникающих в информационных разрядах.

Поставленная цель достигается тем, что устройство содержащее, исходный вычислительный канал, избыточный вычислительный канал. первое кодирующее устройство, блок вычисления синдрома, первый дешифратор, корректор, дополнительно содержит второе кодирующее устройство, с первого по десятый элементы ИЛИ, с первого по четвертый элементы задержки, элемент И. блок элементов И, RS-триггер, регистр, с первого по четвертый блоки элементов неравнозначности, второй дешифратор, элемент НЕ, блок хранения поправок, блок вычисления признака поправки, причем адресные входы подключены к первым входам исходного вычислительного канала, информационные входы через первый и второй элементы ИЛИ подключены ко вторым входам исходного вычислительного канала и к первым входам первого кодирующего устройства, подключенного своими выходами через третий и четвертый элементы ИЛИ к первым входам избыточного вычислительного канала, вход установки в исходное состояние через пятый элемент ИЛИ подключен к нулевым входам регистра и RS-триггера, вход "считывание" подключен к входу "запись регистра", через седьмой элемент ИЛИ к третьему входу исходного вычислительного канала, к второму входу избыточного вычислительного канала и через первый элемент задержки к единичному входу RS-триггера, вход "запись" к через шестой элемент ИЛИ подключен к четвертому входу исходного вычислительного канала, третьему входу избыточного вычислительного канала, выходы исходного вычислительного канала подключены ко вторым входам регистра, к первым входам блока вычисления синдрома и к первым входам первого блока элементов неравнозначности, выходы избыточного вычислительного канала подключены к вторым входам блока вычисления синдрома, к третьим входам регистра и к первым входам второго блока элементов неравнозначности, выходы блока вычисления синдрома подключены к четвертым входам регистра, единичный выход RS-триггера подключен к входу "считывание регистра", через второй элемент задержки к первому входу корректора, через третий элемент задержки к второму входу пятого элемента ИЛИ, через четвертый элемент задержки к второму входу седьмого элемента ИЛИ, первая группа выходов регистра подключена к вторым входам с первого по четвертый элементов ИЛИ, вторая группа выходов регистра подключена к вторым входам первого блока элементов неравнозначности и к вторым входам корректора, третья и четвертая группы выходов регистра подключены соответственно к вторым входам второго блока элементов неравнозначности и к первым входам третьего блока элементов неравнозначности, выход первого блока элементов неравнозначности - к входам второго кодирующего устройства, к входам элемента И, к входам девятого элемента ИЛИ, к первым входам четвертого блока элементов неравнозначности и к первым входам блока вычисления признака поправки, выходы восьмого элемента ИЛИ, девятого элемента ИЛИ и элемента И подключены к входам первого дешифратора, первый выход которого через элемент НЕ подключен к первому входу блока элементов И, а вторая группа выходов подключена к входам десятого элемента ИЛИ, выходы третьего блока элементов неравнозначности подключены к входам второго дешифратора, подключенного своими выходами ко входам блока хранения поправок, выходы которого подключены ко вторым входам блока вычисления признака поправки, соединенного своими выходами со вторыми входами четвертого блока элементов неравнозначности, выходы четвертого блока элементов неравнозначности через блок элементов И подключены к третьим входам корректора, выходы которого являются информационными выходами устройства, выход десятого элемента ИЛИ является выходом формирования сигнала "Отказ устройства".

В настоящее время, для исправления ошибок запоминающих устройств, как правило, используются коды, корректирующие одиночные ошибки. В то же время существует необходимость исправления ошибок произвольной кратности, т.е. существует необходимость в разработке методов коррекции кратных ошибок.

Однако осуществление коррекции кратных ошибок на основе линейных кодов приводит к резкому увеличению избыточности кода и большим аппаратурным затратам на кодирование и декодирование информации, что не только не позволяет повысить надежность и достоверность функционирования отказоустойчивого вычислителя, но и снижает данные показатели.

Основная идея устранения указанного противоречия состоит в апостериорной коррекции ошибок, которая заключается в том, что для обнаружения возникающих ошибок используется корректирующий линейный код, исправляющий одиночную ошибку (требующий минимальных аппаратурных затрат), а определение конфигурации (ошибочных разрядов) кратной ошибки и ее коррекция проводятся по результатам анализа ответной реакции, полученной на основе подачи одного тестового воздействия (требующего минимальных временных затрат).

Основные понятия и определения. Пусть исправление ошибок кодового набора обеспечивается на основе корректирующего линейного кода, исправляющего одиночную ошибку.

Каждому рабочему входному набору ХН соответствует кодовый набор

Y={y1,y2, ..., yk,rk+1,rk+2, ..., rn}, (1)

где yi - значения сигналов в информационных разрядах; rj - значения сигналов в контрольных разрядах.

Вектор контрольных разрядов R является функцией информационных разрядов и определяется правилом кодирования информации выбранного кода:

R={rk+1,rk+2, ..., rn-k}=f(y1,y2, ..., yk). (2)

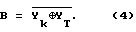

После приема сообщения относительно информационных разрядов повторно формируется вектор контрольных разрядов RП и определяется синдром ошибки

EC = R⊕RП. (3)

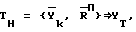

Каждому рабочему входному набору ХН, обеспечивающему определенное значение сигналов в информационных и контрольных разрядах Yk={у1,у2,...,уk,rk+1, rk+2, . . .rn}, поставим в соответствие тестовый набор  порождающий противоположное значение сигналов в информационных и контрольных разрядах.

порождающий противоположное значение сигналов в информационных и контрольных разрядах.

Определение 1. Инверсное значение результата суммирования значений информационных и контрольных разрядов Yk={у1,у2,...,уk,rk+1,rk+2,...rn}, полученных на рабочем входном наборе с информационными и контрольными разрядами YT, полученными на тестовом наборе, будем считать тестовым вектором ошибки:

Если ошибок нет, то тестовый вектор ошибки принимает нулевые значения.

Определение 2. Скрытой будем называть ошибку, которая не проявляется на рассматриваемом входном рабочем наборе.

Пример. Варианту единичных значений в информационных разрядах кода Хемминга (r1, r2, y2, r3, y1) соответствует безошибочный кодовый набор 01111. При наличии ошибки const1 в первом информационном разряде для рассматриваемого входного набора имеем выходной кодовый набор 01111+ (знаком "+" помечен ошибочный разряд), который не отличается от безошибочного кодового набора.

Определение 3. Ошибочный кодовый набор будем называть "правильным", если он не содержит скрытных ошибок и "неправильным" в противном случае.

Утверждение 1. Исправление "неправильного" ошибочного кодового набора на основе тестового вектора ошибки приводит к псевдокоррекции.

Доказательство. При подаче тестового воздействия, обеспечивающего противоположное значение информационных разрядов, обнаруживаются любые ошибки. В этом случае тестовый вектор ошибки указывает номера ошибочных информационных разрядов, в том числе и разрядов, содержащих скрытые ошибки. Так как значения скрытых ошибок соответствуют рабочему входному набору, то их исправление на основе тестового вектора ошибки в свою очередь приведет к ошибке в корректируемом кодовом наборе.

Следствие 1. Апостериорная коррекция кратных ошибок возможна при условии выявления скрытых ошибок (формирования поправки к тестовому вектору ошибки).

На основе приведенных понятий и определений ставится задача выявления конфигурации кратных ошибок по результатам алгебраических операций со значениями синдрома ошибки ЕC и значениями тестового вектора ошибки В, полученным в результате подачи тестового воздействия.

Правила формирования значений вектора ошибки. Процедура определения вектора ошибки основана на следующих теоретических положениях.

Кодирование информационных разрядов тестового вектора ошибки по правилам рассматриваемого кода дает код ошибки тестовых разрядов

Eи=f(Bи). (5)

В результате суммирования синдрома ошибки и кода ошибки тестовых разрядов получим код адреса поправки на скрытую ошибку

EK = EC⊕EИ. (6)

На основе полученных значений ЕС, ЕИ, и ЕК принимается решение на коррекцию ошибок в информационных разрядах при выполнении условия, что количество ошибок в информационных разрядах d≤k-1.

В этом случае стратегия декодирования включает следующие положения:

коррекция возможна если разряды тестового вектора ошибки, соответствующие контрольным разрядам, имеют нулевые значения;

разрешается передача информационных разрядов без коррекции, если тестовый вектор ошибки содержит нулевые значения в информационных разрядах и единичные значения (ошибки) в контрольных разрядах;

коррекция запрещается (формируется сигнал "Отказ устройства") если все разряды тестового вектора ошибки, соответствующие информационным разрядам, имеют единичные значения (k-кратная ошибка) или при наличии единичных значений сигналов одновременно в информационных и контрольных разрядах тестового вектора ошибки;

при возникновении скрытой ошибки вектор ошибки формируется путем добавления поправки к тестовому вектору ошибки.

Правила формирования значений поправки при возникновении скрытой ошибки. Для определения поправки в тестовый вектор ошибки построим таблицу решений (поправок на каждую скрытую ошибку).

В этом случае число поправок образует множество мощностью |SM| = 2k.

Каждой скрытой ошибке поставим в соответствие значение поправки и соответствующий код адреса поправки.

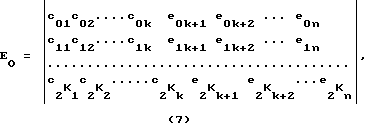

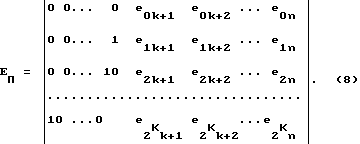

Данную совокупность представим в виде определяющей матрицы

где Cij - значения разрядов вектора поправок 0=0, 1, 2,...,2k -номер строки; j= 0, 1, 2,... k - номер столбца); eij - значения разрядов кода адреса поправки.

Свойство 1. Каждому коду адреса поправок (правой группе элементов определяющей матрицы) соответствует прямое и обратное значение разрядов вектора поправок

где сj - прямое значение разряда вектора ошибки;  - инверсное значение разряда вектора ошибки.

- инверсное значение разряда вектора ошибки.

Данное свойство вытекает из определения двойственного ошибочного кодового набора (противоположным значениям ошибочного кодового набора соответствует одинаковое значение синдрома ошибки).

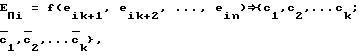

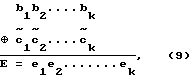

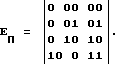

Выберем из определяющей матрицы (7) те строки, у которых номер (двоичный эквивалент) значений вектора поправок соответствует 2i, (i=1, 2,..., k), и построим таблицу поправок:

Свойства таблицы поправок.

Свойство 2. Для выбора значений поправки необходимо формировать признак поправки -V (прямого или обратного значения разрядов поправки относительно рассматриваемого кода адреса поправки).

Таким образом, коррекция кратных ошибок предлагаемым методом осуществляется на основе значений информационных разрядов тестового вектора ошибки и значений поправки на скрытую ошибку, т.е. вектор ошибки равен:

где  - значение разряда вектора поправки (прямого или обратного).

- значение разряда вектора поправки (прямого или обратного).

Свойство 3. Поправка имеет обратное значение, если все значения разрядов вектора поправки совпадают со значениями соответствующих информационных разрядов тестового вектора ошибки и прямое в обратном случае.

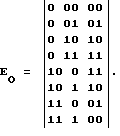

Пример. Рассмотрим процедуру построения корректирующего кода A(n, k) с апостериорной коррекцией кратных ошибок на примере порогового кодирования А(5, 3): (r1 = y1⊕y2; r2 = y1⊕y3).

Построим определяющую матрицу:

По определяющей матрице построим таблицу поправок:

Допустим, необходимо закодировать сообщение

В этом случае проверочные разряды имеют значения r1r2⇒01. Таким образом, кодовый набор передается в виде YK=00101.

Если ошибка не возникла, то синдром ошибки ЕC имеет нулевые значения. В результате подачи тестового воздействия, обеспечивающего противоположное значение информационных разрядов, получим тестовый вектор ошибки В=00000, т. е. код ошибки тестовых разрядов ЕИ=00, ЕК=00 и значения контрольных разрядов тестового вектора Rb П= 00. Так как обратное значение поправки C=111, полученное по коду адреса поправки EК=00, не совпадает со значениями информационных разрядов вектора В, то берется прямое значение поправки С=000. Таким образом вектор ошибки равен: E = B⊕C = 000.

Пусть при передачи сообщения возникла ошибка в первом и втором информационных разрядах: Y*к=1*1*1 01. Используя приведенные выражения, для данного случая имеем:

В=11000; EИ=01; ЕС=01; EK=00; C=000; E=110. Вектор ошибки равен тестовому вектору ошибки, который указывает на ошибку в первом и втором информационных разрядах.

Допустим, в кодовом наборе возникла "правильная" ошибка в первом информационном разряде и скрытая ошибка во втором информационном разряде Y*к=1*0+ 01, тогда:

B=11000: EИ=01; EC=11; EK=10; C=010; E=100.

Так как обратное значение поправки C=101 (полученное из таблицы поправок по коду адреса поправок EK=10) не совпадает с значением третьего информационного разряда тестового вектора ошибки, то берется прямое значение поправки С=010. Тогда Е=100, т.е. корректируется первый информационный разряд.

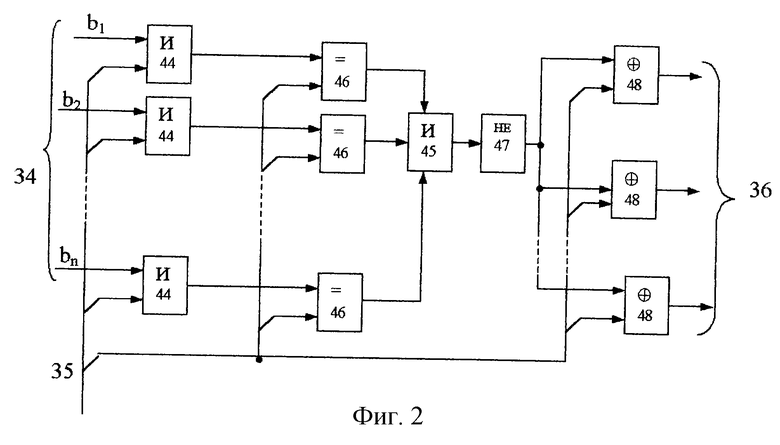

На фиг.1 представлена блок-схема отказоустойчивого запоминающею устройства. Отказоустойчивое запоминающее устройство содержит исходный вычислительный канал 1, избыточный вычислительный канал 2, первое кодирующее устройство 3, второе кодирующее устройство 4, блок вычисления синдрома 5, корректор 6, с первого по десятый 7, 8, 9, 10, 11, 12, 13, 14, 15, 16 элементы ИЛИ, с первого по четвертый 17, 18, 19, 20 элементы задержки, 21-элемент И, блок 22 элементов И, RS-триггер 23, регистр 24, с первого по четвертый 25, 26, 27, 28 блоки элементов неравнозначности, первый 29 и второй 30 дешифраторы, 31-элемент HЕ, блок 32 хранения поправок, блок 33 вычисления признака поправки, входы 34, 35 являются входами блока 33 вычисления признака поправки, выход 36 является выходом блока 33 вычисления признака поправки, вход 37 "Запись", вход 38 "Считывание", вход 39 "Сброс", адресные входы 40, информационные входы 41, информационные выходы 42, выход 43 десятого элемента 16 И является выходом формирования сигнала "Отказ устройства".

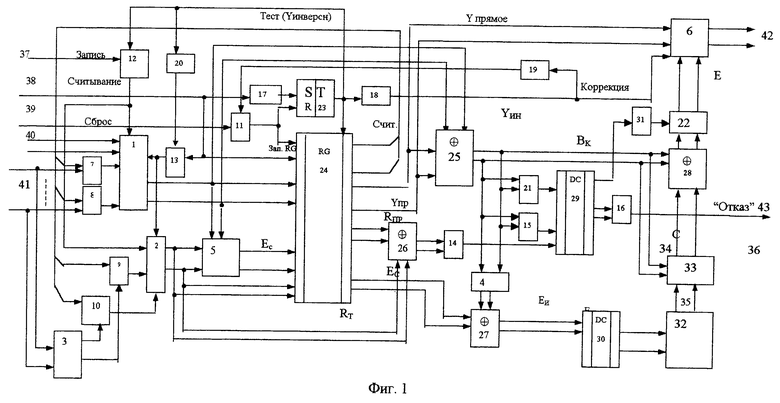

На фиг.2 представлена схема блока 33 вычисления признака поправки Он содержит группу 44-элементов И, 45-элемент И, элементы 46 равнозначности, 47-элeмeнт НЕ, группу элементов 48 неравнозначности.

Адресные входы 40 подключены к первым входам исходного вычислительного канала 1, информационные входы 41 через первый 7 и второй 8 элементы ИЛИ подключены ко вторым входам исходного вычислительного канала 1 и к первым входам первого кодирующего устройства 3, подключенного своими выходами через третий 9 и четвертый 10 элементы ИЛИ к первым входам избыточного вычислительного канала 2, вход 39 "сброс" через пятый 11-элемент ИЛИ подключен к нулевым входам регистра 24 и RS-триггера 23, вход 38 "считывание" подключен к входу "запись" регистра 24, через седьмой 11-элемент ИЛИ к третьему входу исходного вычислительного канала 1, к второму входу избыточного вычислительного канала 2 и через первый элемент 17 задержки к единичному входу RS-триггера 23, вход 37 "запись" через шестой 12-элемент ИЛИ подключен к четвертому входу исходного вычислительного канала 1, третьему входу избыточного вычислительного канала 2, выходы исходного вычислительного канала 1 подключены ко вторым входам регистра 24, к первым входам блока 5 вычисления синдрома и к первым входам первого блока 25 элементов неравнозначности, выходы избыточного вычислительного канала 2 подключены к вторым входам блока 5 вычисления синдрома, к третьим входам регистра 24 и к первым входам второго блока 26 элементов неравнозначности, выходы блока 5 вычисления синдрома подключены к четвертым входам регистра 24, единичный выход RS-триггера 23 подключен к входу "считывание" регистра 24, через второй элемент 18 задержки к первому входу корректора 6, через третий элемент 19 задержки к второму входу пятого 11-элемента ИЛИ, через четвертый элемент 20 задержки к второму входу седьмого 13-элемента ИЛИ, первая группа выходов регистра 24 подключена к вторым входам с первого 7 по четвертый 10 элементов ИЛИ, вторая группа выходов регистра 24 подключена к вторым входам первого блока 25 элементов неравнозначности и к вторым входам корректора 6, третья и четвертая группы выходов регистра 24 подключены соответственно к вторым входам второго блока 26 элементов неравнозначности и к первым входам третьего блока 27 элементов неравнозначности, выход первого блока 25 элементов неравнозначности подключен к входам второго кодирующего устройства 4, к входам 21-элемента И, к входам девятого 15-элемента ИЛИ, к первым входам четвертого блока 28 элементов неравнозначности и к первым входам блока 33 вычисления признака поправки, выходы восьмого 14-элемента ИЛИ, девятого 15-элемента ИЛИ и 21-элемента И подключены к входам первого дешифратора 29, первый выход которого через 31-элемент НЕ подключен к первому входу блока 22 элементов И, а вторая группа выходов подключена к входам десятого 16-элемента ИЛИ, выходы третьего блока 27 элементов неравнозначности подключены к входам второго дешифратора 30, подключенного своими выходами ко входам блока 32 хранения поправок, выходы которого подключены ко вторым входам блока 33 вычисления признака поправки, соединенного своими выходами со вторыми входами четвертого блока 28 элементов неравнозначности, выходы четвертого блока 28 элементов неравнозначности через блок 22 элементов И подключены к третьим входам корректора 6, выходы которого являются информационными выходами 42 устройства, выход десятого 16-элемента ИЛИ является выходом 43 формирования сигнала "Отказ устройства".

Исходный вычислительный канал 1 представляет собой полупроводниковое оперативное ЗУ, содержащее, например, трехразрядный накопитель (каждая ячейка памяти включает три триггера) емкостью М-ячеек памяти.

Избыточный вычислительный канал 2 представляет собой оперативное запоминающее устройство, предназначенное для хранения значений контрольных разрядов.

Первое кодирующее устройство 3 (относительно трех информационных разрядов) имеет два выхода r1, r2, на которых реализуются логические функции соответственно:

r1 = y1⊕y2; r2 = y1⊕y3; (9)

Второе кодирующее устройство 4 выполняет функции, аналогичные первому кодирующему устройству 3, относительно информационных разрядов тестового вектора ошибки В:

d1 = b1⊕b2; d2 = b1⊕b3.

Блок 5 вычисления синдрома выполняет операцию повторного кодирования информации, считываемой с исходного вычислительного канала 1(r

Корректор 6 предназначен для исправления возникающих ошибок путем сложения информационных разрядов с вектором ошибки:

С первого 7 по седьмой 13 элементы ИЛИ предназначены для обеспечения функциональных связей между блоками устройства, восьмой 14-элемент ИЛИ и девятый 15-элемент ИЛИ предназначены соответственно для выявления единичных значений сигналов в контрольных разрядах (отказа элементов избыточного вычислительного канала 2) и информационных разрядах тестового вектора ошибок (отказа элементов исходного вычислительного канала 1). При возникновении ошибки во всех информационных разрядах (появляется сигнал на выходе 21-элемента И) или одновременном возникновении ошибок в информационных и контрольных разрядах (сигналы на выходах восьмого 14 и девятого 15 элементов ИЛИ) на выходе десятого 16-элемента ИЛИ формируется сигнал "Отказ устройства". С первого 17 по четвертый 20 элементы задержки обеспечивают синхронизацию работы блоков устройства.

При возникновении ошибки только в контрольных разрядах (наличие единичного сигнала на выходе восьмого 14-элемента ИЛИ и нулевого значения сигнала на выходе девятого 15-элемента ИЛИ) на выходе первого дешифратора 29 формируется сигнал, который через элемент 31 НЕ, блок 22 элементов И запрещает коррекцию информационных разрядов.

RS-триггер 23 совместно с элементами задержки осуществляет управление блоками устройства.

Регистр 24 предназначен для временного хранения кодового набора:

Yпр - значений сигналов информационных разрядов; Rпр- значений сигналов контрольных разрядов; ЕС-значений сигналов синдрома ошибки; yинв - инверсных (тестовых) значений сигналов информационных и Rинв - контрольных разрядов.

Первый блок 25 элементов неравнозначности предназначен для формирования тестового вектора ошибки В путем сложения прямых значений информационных разрядов Yпр (считываемых с прямых выходов регистра 24) с информационными разрядами YT, считываемыми с исходного вычислительного канала 1 после подачи на него тестового воздействия Yинв (значений сигналов, считываемых с инверсных выходов регистра 24).

Второй блок 26 элементов неравнозначности предназначен для формирования сигналов в контрольных разрядах тестового вектора ошибки В путем сложения прямых значений контрольных разрядов Rпр (считываемых с прямых выходов регистра 24) с значениями контрольных разрядов RT, считываемых с избыточного вычислительного канала 2 после подачи на него тестового воздействия Rинв (значений сигналов, считываемых с инверсных выходов регистра 24).

Третий блок 27 элементов неравнозначности предназначен для формирования кода адреса поправки ЕK путем сложения значений кода ошибки тестовых разрядов ЕИ и значения синдрома ошибки ЕС.

Четвертый блок 28 элементов неравнозначности предназначен для формирования вектора ошибки Е путем сложения информационных разрядов тестового вектора ошибки В с поправкой С.

Второй дешифратор 30 предназначен для выбора поправки из блока 32 хранения поправок по коду адреса поправки ЕК.

Блок 32 хранения поправок предназначен для хранения информации, представленной матрицей поправок (8).

Блок 33 вычисления признака поправки предназначен для выбора прямого или обратного значения поправки и работает следующим образом (см. фиг.2). По значению кода адреса поправки ЕК с блока 32 хранения поправок считывается обратное значение поправки (содержащее для данной ошибки максимальное количество единиц), которое поступает на вход 35 блока вычисления признака поправки и соответственно на входы группы элементов 44 И, группы элементов 46 равнозначности и группы элементов 48 неравнозначности. Значения информационных разрядов тестового вектора ошибки поступают на входы 34 блока 33 вычисления признака поправки.

В этом случае открываются элементы И группы элементов 44 И, имеющие на своих входах единичные значения сигналов поправки и информационных разрядов тестового вектора ошибки. Если значение сигналов, поступающих с выходов элементов И, совпадают с значением поправки, то на выходах всех элементов группы элементов 46 равнозначности появляются единичные значения сигналов (открывается элемент 45 И). В этом случае сигнал на выходе элемента 47 имеет нулевое значение, поэтому с выходов элементов 48 неравнозначности снимается обратное значение поправки. Если значение поправки не совпадает с значениями сигналов тестового вектора ошибки (сигнал на выходе элемента 45 И имеет нулевое значение), то сигнал, поступающий с выхода элемента 47 НЕ на входы элементов 48 неравнозначности, обеспечивает инвертирование значений сигналов поправки (формируется прямое значение поправки).

Устройство работает следующим образом. Перед началом работы на вход 39 подается сигнал "Сброс", который через пятый элемент 11 ИЛИ устанавливает в нулевое состояние триггер 23 и регистр 24. При поступлении сигнала "Запись" на вход 37 и адреса ячейки памяти на входы 40 в выбранную ячейку записывается информация, поступающая на вход 41. Одновременно подаваемая информация кодируется первым кодирующим устройством 3, и значения контрольных разрядов записываются в избыточный вычислительный канал 2.

При поступлении сигнала "Считывание" по выбранному адресу сигнал со входа 38 через седьмой элемент 13 ИЛИ поступает на вход считывания исходного вычислительного канала 1 и избыточного вычислительного канала 2.

Информация, считываемая с исходного вычислительного канала 1 и избыточного вычислительного канала 2, поступает на блок 5 вычисления синдрома, где она повторно кодируется и сравнивается с значениями контрольных разрядов, т.е. вычисляется синдром ошибки. Кроме этого, сигналом, поступающим со входа 38, разрешается запись информационных разрядов и значения синдрома ошибки в регистр 24.

Через время, определяемое первым элементом 17 задержки, RS-триггер 23 переводится в единичное состояние и его единичный сигнал разрешает считывание информации с регистра 24.

Информация, считываемая с инверсных выходов регистра 24 (тестовое воздействие), через первый 7, второй 8, третий 9 и четвертый 10 элементы ИЛИ поступает на входы исходного вычислительного канала 1 и избыточного вычислительного канала 2.

Через время, определяемое четвертым элементом 20 задержки, сигнал с выхода RS-триггера 23 через седьмой элемент 13 ИЛИ разрешает повторное считывание информации (результатов тестового воздействия) с исходного вычислительного канала 1 и избыточного вычислительного канала 2.

Полученная ответная информация (YT, RT) сравнивается с исходной информацией (Yпр, Rпр) соответственно первым блоком 25 элементов неравнозначности и вторым блоком 26 элементов неравнозначности, т. е. формируется тестовый вектор ошибки В.

Полученное значение информационных разрядов тестового вектора ошибки В кодируется вторым кодирующим устройством 4 (формируется код ошибки тестовых разрядов ЕИ) и затем сравнивается с значением синдрома ошибки ЕС на третьем блоке 27 элементов неравнозначности (формируется значение кода адреса поправки ЕК).

Если ошибок нет, то разряды тестового вектора ошибки имеют нулевые значения, соответственно код адреса поправки ЕК имеет нулевые значения. В этом случае с блока 32 хранения поправок считывается обратное значение поправки, имеющее в своих разрядах все единицы. Так как данное значение поправки не совпадает с значениями информационных разрядов тестового вектора ошибки, то блоком 33 вычисления признака поправки выбирается прямое значение поправки, т. е. нулевые значения поправки. В результате сложения значений поправки и значений информационных разрядов тестового вектора ошибки (имеющих нулевые значения) получим вектор ошибки Е, имеющий нулевые значения. Через время, определяемое вторым элементом 18 задержки, на корректор 6 поступает сигнал, разрешающий коррекцию. Так как вектор ошибки Е имеет нулевые значения, то информационные разряды поступают на выход без изменения. Через время, определяемое третьим элементом 19 задержки, триггер 23 и регистр 24 переводятся в исходное состояние.

При возникновении ошибки во всех информационных разрядах (появлении сигнала на выходе элемента 21 И) или одновременном возникновении ошибок в информационных и контрольных разрядах (появлении сигналов на выходе восьмого 14 и девятого элементов ИЛИ) на выходе десятого элемента 16 ИЛИ формируется сигнал "Отказ устройства".

При возникновении ошибки только в контрольных разрядах (наличие единичного значения сигнала на выходе восьмого элемента 14 ИЛИ) и отсутствии ошибок в информационных разрядах (наличие нулевого значения сигнала на выходе девятого элемента 15 ИЛИ) на выходе первого дешифратора 29 появляется сигнал, который через элемент 31 НЕ, блок 22 элементов И запрещает подачу сигналов вектора ошибки Е на корректор 6.

При возникновении скрытой ошибки третьим блоком 27 неравнозначности формируется код адреса поправки ЕК, по которому вторым дешифратором 30 выбирается обратное значение поправки из блока 32 хранения поправок. В результате сравнения значения выбранной поправки с значениями информационных разрядов тестового вектора ошибки блоком 33 вычисления признака поправки выбирается прямое или обратное значение поправки. В результате сложения значений информационных разрядов тестового вектора ошибки с выбранным значением поправки четвертым блоком 28 элементов неравнозначности формируется вектор ошибки Е.

Исправление ошибки корректором 6 осуществляется путем сложения информационных разрядов Yпр, содержащих ошибку, с вектором ошибки Е.

Предлагаемое устройство позволяет обеспечить:

обнаруживать правильные и скрытые ошибки любой кратности;

корректировать ошибки в информационных разрядах кратности d≤k-1;

минимальные аппаратурные затраты на обеспечение защиты информации по сравнению со структурными методами резервирования и традиционными методами обнаружения и коррекции кратных ошибок на основе линейных кодов, которые составляют 20-40% исходного оборудования и соизмеримы с затратами кода, исправляющего одиночную ошибку;

определение конфигурации ошибки по результатам мгновенного контроля (в результате подачи одного тестового воздействия, которое может подаваться только при возникновении ошибки), т. е. практически без снижения быстродействия исходного устройства.

Источники информации

1. Авторское свидетельство СССР 1716521, кл. G 06 F 11/18, 1989 г.

2. Щербаков Н. С. Достоверность работы цифровых устройств. М.: Машиностроение, 1989, с. 82, рис. 39, 224 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО | 1999 |

|

RU2210805C2 |

| ОТКАЗОУСТОЙЧИВОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2579954C2 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМЫ СВЯЗИ | 2000 |

|

RU2211486C2 |

| АДАПТИВНОЕ РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО | 2000 |

|

RU2210806C2 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМЫ СВЯЗИ | 2000 |

|

RU2210811C2 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМЫ СВЯЗИ | 1999 |

|

RU2210812C2 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ | 2004 |

|

RU2297030C2 |

Изобретение относится к области автоматики и вычислительной техники. Техническим результатом является расширение функциональных возможностей. Устройство содержит два кодирующих устройства, блок вычисления синдрома, корректор, десять элементов ИЛИ, блок элементов И, RS-триггер, регистр, четыре блока элементов неравнозначности, два дешифратора, элемент НЕ, блок хранения поправок, блок вычисления признака поправки, исходный и избыточный вычислительные каналы. 2 ил.

Отказоустойчивое оперативное запоминающее устройство, содержащее исходный вычислительный канал, избыточный вычислительный канал, первое кодирующее устройство, блок вычисления синдрома, первый дешифратор, адресные входы устройства, информационные входы устройства, вход записи, вход считывания, корректор, выходы которого являются информационными выходами устройства, отличающееся тем, что дополнительно содержит второе кодирующее устройство, с первого по десятый элементы ИЛИ, с первого по четвертый элементы задержки, элемент И, блок элементов И, RS-триггер, регистр, с первого по четвертый блоки элементов неравнозначности, второй дешифратор, элемент НЕ, блок хранения поправок, блок вычисления признака поправки, вход "Сброс", причем адресные входы подключены к первым входам исходного вычислительного канала, информационные входы через первый и второй элементы ИЛИ подключены ко вторым входам исходного вычислительного канала и к первым входам первого кодирующего устройства, подключенного своими выходами через третий и четвертый элементы ИЛИ к первым входам избыточного вычислительного канала, вход "Сброс" через пятый элемент ИЛИ подключен к нулевым входам регистра и RS-триггера, вход "Считывание" подключен к входу "Запись регистра", через седьмой элемент ИЛИ - к третьему входу исходного вычислительного канала, к второму входу избыточного вычислительного канала и через первый элемент задержки - к единичному входу RS-триггера, вход "Запись" через шестой элемент ИЛИ подключен к четвертому входу исходного вычислительного канала, третьему входу избыточного вычислительного канала, выходы исходного вычислительного канала подключены к вторым входам регистра, к первым входам блока вычисления синдрома и к первым входам первого блока элементов неравнозначности, выходы избыточного вычислительного канала подключены к вторым входам блока вычисления синдрома, к третьим входам регистра и к первым входам второго блока элементов неравнозначности, выходы блока вычисления синдрома подключены к четвертым входам регистра, единичный выход RS-триггера подключен к входу "Считывание регистра", через второй элемент задержки - к первому входу корректора, через третий элемент задержки - к второму входу пятого элемента ИЛИ, через четвертый элемент задержки к второму входу седьмого элемента ИЛИ, первая группа выходов регистра подключена к вторым входам с первого по четвертый элементов ИЛИ, вторая группа выходов регистра подключена к вторым входам первого блока элементов неравнозначности и к вторым входам корректора, третья и четвертая группы выходов регистра подключены соответственно к вторым входам второго блока элементов неравнозначности и к первым входам третьего блока элементов неравнозначности, выход первого блока элементов неравнозначности - к входам второго кодирующего устройства, к входам элемента И, к входам девятого элемента ИЛИ, к первым входам четвертого блока элементов неравнозначности и к первым входам блока вычисления признака поправки, выходы второго блока элементов неравнозначности подключены к входам восьмого элемента ИЛИ, выходы восьмого элемента ИЛИ, девятого элемента ИЛИ и элемента И подключены к входам первого дешифратора, первый выход которого через элемент НЕ подключен к первому входу блока элементов И, а вторая группа выходов подключена к входам десятого элемента ИЛИ, выходы третьего блока элементов неравнозначности подключены к входам второго дешифратора, подключенного своими выходами ко входам блока хранения поправок, выходы которого подключены ко вторым входам блока вычисления признака поправки, соединенного своими выходами со вторыми входами четвертого блока элементов неравнозначности, выходы четвертого блока элементов неравнозначности через блок элементов И подключены к третьим входам корректора, выходы которого являются информационными выходами устройства, выход десятого элемента ИЛИ является выходом формирования сигнала "Отказ устройства".

| ЩЕРБАКОВ Н.С | |||

| Достоверность работы цифровых устройств | |||

| - М.: Машиностроение, 1989, с.82, рис.39 | |||

| Самокорректирующееся дискретное устройство | 1989 |

|

SU1716521A1 |

| RU 2053578 C1, 27.01.1996 | |||

| US 6163871 A, 19.12.2000 | |||

| US 5515381 A, 07.05.1996. | |||

Авторы

Даты

2003-08-27—Публикация

2001-04-28—Подача