Известно устройство памяти с обнаружением двойных ошибок [1], содержащее узел памяти, отличающееся тем, что оно дополнительно содержит входной блок кодирования, выходной блок кодирования, блок сравнения, блок элементов И, элемент И, элемент ИЛИ, вход установки устройства в нулевое состояние, вход записи, вход считывания, адресные входы, информационные входы, вход синхронизации, информационные выходы, выход сигнала «ошибка», причем вход установки в нулевое состояние, вход записи, вход считывания, адресные входы подключены соответственно к первому, второму, третьему и четвертому входам узла памяти, информационные входы подключены к пятым входам узла памяти и к входам входного блока кодирования, выходы которого подключены к шестым входам узла памяти, вход синхронизации подключен к седьмому входу узла памяти и к первым входам блока элементов И и элемента И, первые выходы узла памяти подключены к входам выходного блока кодирования и к вторым входам блока элементов И, выходы выходного блока кодирования подключены к первым входам блока сравнения, к вторым входам которого подключены вторые выходы узла памяти, а выходы подключены к входам элемента ИЛИ, выход элемента ИЛИ подключен к второму входу элемента И, выходы блока элементов И являются информационными выходами устройства, выход элемента И является выходом сигнала «ошибка».

Недостатком устройства является ограниченная область его применения, так как оно позволяет обеспечить достоверность функционирования только запоминающих устройств ЭВМ.

Наиболее близким по техническому решению является процессор [2], содержащий управляющий узел, операционный узел, первая группа входов управляющего узла является входами процессора, вторая группа входов управляющего узла подключена к первым выходам операционного узла, выходы управляющего узла подключены к первым входам операционного узла, вторые входы которого являются входами данных, а вторые выходы являются выходами данных.

Недостатком устройства является низкая достоверность функционирования процессора, так как не обеспечивается обнаружение ошибок при выполнении арифметических и логических операций (преобразователей информации: сумматора, регистров сдвига, устройств выполнения логических операций).

Целью изобретения является повышение достоверности функционирования процессора за счет обнаружения и коррекции возникающих ошибок.

Поставленная цель достигается тем, что процессор, содержащий управляющий узел, операционный узел, первая группа входов управляющего узла является входами процессора, вторая группа входов управляющего узла подключена к первым выходам операционного узла, выходы управляющего узла подключены к первым входам операционного узла, вторые входы которого являются входами данных, а вторые выходы являются выходами данных, отличающийся тем, что он дополнительно содержит дешифратор кода операции, генератор тактовых импульсов, блок управления, первый коммутатор, второй коммутатор, третий коммутатор, счетчик команд, счетчик сдвигов, регистр адреса, регистр числа, регистр сумматора, регистр дополнительный, регистр дополнительного кода, сумматор, блок контроля, управляющую память, блок логических операций и контроля, включающий блок логического сложения по mod2, блок инвертирования, блок логического сложения, блок логического умножения, функциональную схему формирования поправки при выполнении арифметических операций, функциональную схему формирования поправки при выполнении операции ИЛИ, функциональную схему формирования поправки при выполнении операции И, функциональную схему формирования поправки при выполнении операции сдвига, элемент задержки, первый блок элементов неравнозначности, второй блок элементов неравнозначности, третий блок элементов неравнозначности, первый блок элементов ИЛИ, второй блок элементов ИЛИ, блок кодирования, первый блок элементов И, второй блок элементов И, элемент И, выходы устройства обмена подключены к первому входу блока управления и к первому входу второго коммутатора, вторые входы которого подключены к выходам запоминающего устройства, первые выходы второго коммутатора поступают на вход устройства обмена, вторые выходы поступают на вход запоминающего устройства, а третьи выходы подключены соответственно к первым входам счетчика команд, счетчика сдвигов, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к входам дешифратора кода операции, к вторым входам блока управления, к первому входу первого коммутатора, первый выход которого подключен к первому входу регистра адреса, третий вход блока управления подключен к выходам дешифратора кода операции, а четвертый вход подключен к выходам генератора тактовых импульсов, а пятый вход подключен к первому выходу управляющей памяти, первый выход блока управления подключен к входу управляющей памяти, первые выходы которой подключены к первым входам блока контроля, второй выход блока управления подключен к второму входу первого коммутатора, третьи и четвертые входы которого подключены соответственно к выходам регистра адреса и счетчика команд, а с второго выхода снимается адрес ячейки памяти запоминающего устройства, третий выход блока управления подключен соответственно к вторым входам блока контроля, к вторым входам счетчика команд, счетчика сдвигов, регистра адреса, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к первой группе входов третьего коммутатора, к третьей группе входов второго коммутатора, к первой группе входов блока логических операций и контроля и является выходом синхроимпульсов, второй, третий, четвертый, пятый выходы управляющей памяти подключены к третьим, четвертым, пятым и шестым входам блока контроля, при этом второй выход подключен к четвертому входу второго коммутатора, а третьи, четвертые и пятые выходы блока управляющей памяти подключены соответственно к третьим, четвертым, пятым и шестым входам счетчика команд, счетчика сдвигов, регистра адреса, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к первой группе входов третьего коммутатора, к третьей группе входов второго коммутатора, к первой группе входов блока логических операций и контроля и являются выходами управляющих сигналов, сигналов считывания, сигналов записи, сигналов установки устройств в нулевое состояние, шестой выход блока управляющей памяти подключен к пятому входу блока управления, выходы регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода подключены к вторым входам третьего коммутатора и к пятым входам второго коммутатора, выход счетчика сдвигов подключен к шестым входам второго коммутатора, первые выходы третьего коммутатора подключены соответственно к входам сумматора и к вторым входам блока логических операций и контроля, выходы сумматора подключены к третьим входам блока логических операций и контроля, вторые, третьи, четвертые, пятые, шестые, седьмые и восьмые выходы третьего коммутатора подключены к четвертым, пятым, шестым, седьмым, восьмым, девятым и десятым входам блока логических операций и контроля, выходы которого подключены к седьмым, восьмым и девятым входам второго коммутатора.

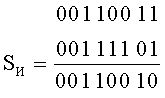

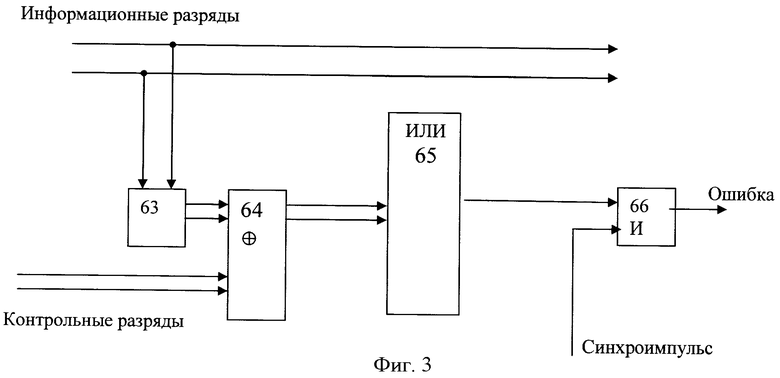

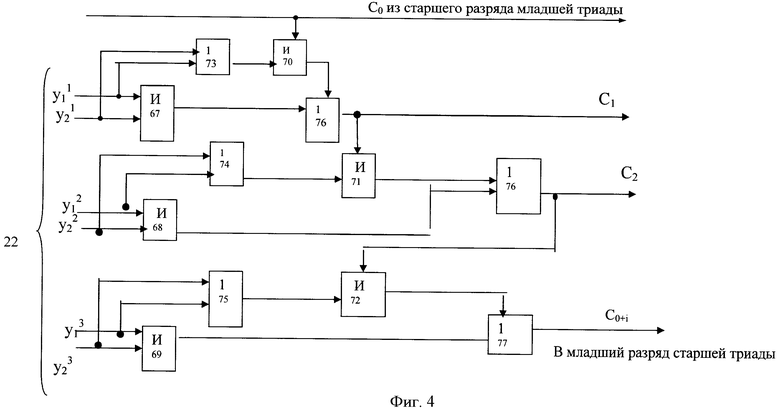

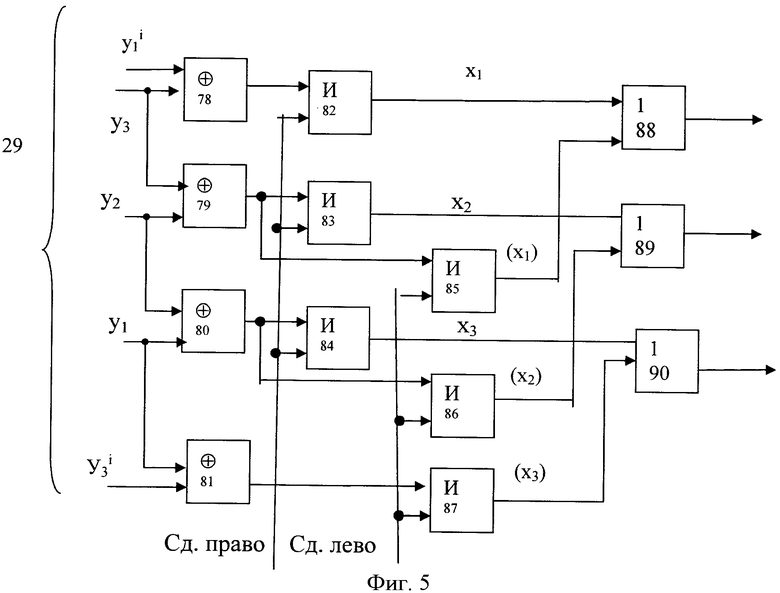

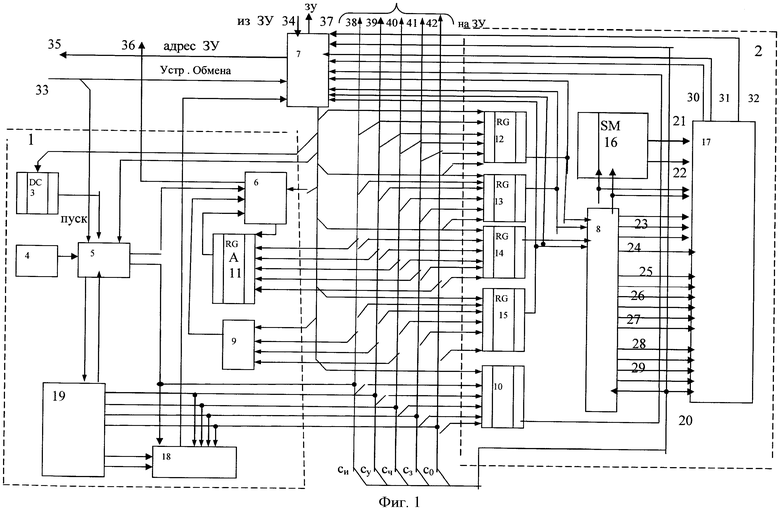

На фиг.1 представлена блок-схема устройства; на фиг.2 - функциональная схема блока логических операций и контроля; на фиг.3 - функциональная схема блока контроля; на фиг.4 - функциональная схема формирования поправки при выполнении арифметических операций; на фиг.5 - функциональная схема формирования поправки при выполнении операции сдвига.

Процессор (фиг.1) содержит управляющий узел 1, операционный узел 2, дешифратор 3 кода операции, генератор 4 тактовых импульсов, блок 5 управления, первый коммутатор 6, второй коммутатор 7, третий коммутатор 8, счетчик 9 команд, счетчик 10 сдвигов, регистр 11 адреса, регистр 12 числа, регистр 13 сумматора, регистр 14 дополнительный, регистр 15 дополнительного кода, сумматор 16, блок 17 логических операций и контроля, блок 18 контроля, управляющую память 19, с первого 20 по десятый 29 входы блока 18 логических операций и контроля, с первого 30 по третий 32 выходы блока 17 логических операций и контроля, входы 33 устройства обмена, входы 34 данные из запоминающего устройства, выход 35 на устройство обмена, выход 36 адрес запоминающего устройства, выходы 37 данные на запоминающее устройство, выходы 38 синхроимпульсов, выходы 39 для сигналов управления, выходы 40 для команды считывание, выходы 41 для сигналов записи, выходы 42 для сигналов установки в нулевое состояние.

Блок 17 логических операций и контроля (фиг.2) содержит блок 43 логического сложения по mod2, блок 44 инвертирования, блок 45 логического сложения, блок 46 логического умножения, функциональную схему 47 формирования поправки при выполнении арифметических операций, функциональную схему 48 формирования поправки при выполнении операции ИЛИ, функциональную схему 49 формирования поправки при выполнении операции И, функциональную схему 50 формирования поправки при выполнении операции сдвига, элемент 51 задержки, первый блок 52 элементов неравнозначности, второй блок 53 элементов неравнозначности, третий блок 54 элементов неравнозначности, первый блок 55 элементов ИЛИ, второй блок 56 элементов ИЛИ, первый блок 57 кодирования, второй блок 58 кодирования, первый блок 59 элементов И, второй блок 60 элементов И, элемент 61 И, группу 62 элементов ИЛИ.

Блок 18 контроля (фиг.3) содержит кодирующую схему 63, схему 64 обнаружения ошибки, группу 65 элементов ИЛИ, элемент 66 И.

Функциональная схема формирования поправки при выполнении арифметических операций (фиг.4) содержит первый элемент 67 И, второй элемент 68 И, третий элемент 69 И, четвертый элемент 70 И, пятый элемент 71 И, шестой элемент 72 И, первый элемент 73 ИЛИ, второй элемент 74 ИЛИ, третий элемент 75 ИЛИ, четвертый элемент 76 ИЛИ, пятый элемент 77 ИЛИ.

Функциональная схема формирования поправки при выполнении операции сдвига (фиг.5) содержит первый элемент 78 неравнозначности, второй элемент 79 неравнозначности, третий элемент 80 неравнозначности, четвертый элемент 81 неравнозначности, первый элемент 82 И, второй элемент 83 И, третий элемент 84 И, четвертый элемент 85 И, пятый элемент 86 И, шестой элемент 87 И, первый элемент 88 ИЛИ, второй элемент 89 ИЛИ, третий элемент 90 ИЛИ, информационные входы 29, вход управляющего сигнала сдвиг вправо, вход управляющего сигнала сдвиг влево.

Выходы 33 устройства обмена подключены к первому входу блока 5 управления и к первому входу второго коммутатора 7, вторые входы которого подключены к выходам запоминающего устройства, первые выходы второго коммутатора 7 поступают на вход устройства обмена, вторые выходы поступают на вход запоминающего устройства, а третьи выходы подключены соответственно к первым входам счетчика 9 команд, счетчика 10 сдвигов, регистра 12 числа, регистра 13 сумматора, регистра 14 дополнительного, регистра 15 дополнительного кода, к входам дешифратора 3 кода операции, к вторым входам блока 5 управления, к первому входу первого коммутатора 6, первый выход которого подключен к первому входу регистра 11 адреса, третий вход блока 5 управления подключен к выходам дешифратора 3 кода операции, а четвертый вход подключен к выходам генератора 4 тактовых импульсов, а пятый вход подключен к первому выходу управляющей памяти 19, первый выход блока 5 управления подключен к входу управляющей памяти 19, первые выходы которой подключены к первым входам блока 18 контроля, второй выход блока управления подключен к второму входу первого коммутатора 6, третьи и четвертые входы которого подключены соответственно к выходам регистра 11 адреса и счетчика 9 команд, а с второго выхода снимается адрес ячейки памяти запоминающего устройства, третий выход блока 5 управления подключен соответственно к вторым входам блока 5 контроля, к вторым входам счетчика 9 команд, счетчика 10 сдвигов, регистра 11 адреса, регистра 12 числа, регистра 13 сумматора, регистра 14 дополнительного, регистра 15 дополнительного кода, к первой группе входов третьего коммутатора 8, к третьей группе входов второго коммутатора 7, к первой группе входов блока 17 логических операций и контроля и является выходом синхроимпульсов, второй, третий, четвертый, пятый выходы управляющей памяти 19 подключены к третьим, четвертым, пятым и шестым входам блока 18 контроля, при этом второй выход подключен к четвертому входу второго коммутатора 7, а третьи, четвертые и пятые выходы блока управляющей памяти 19 подключены соответственно к третьим, четвертым, пятым и шестым входам счетчика команд 9, счетчика 10 сдвигов, регистра 11 адреса, регистра 12 числа, регистра 13 сумматора, регистра 14 дополнительного, регистра 15 дополнительного кода, к первой группе входов третьего коммутатора 8, к третьей группе входов второго коммутатора 7, к первой группе входов блока 17 логических операций и контроля и являются выходами управляющих сигналов, сигналов считывания, сигналов записи, сигналов установки устройств в нулевое состояние, шестой выход блока управляющей памяти 19 подключен к пятому входу блока 5 управления, выходы регистра 12 числа, регистра 13 сумматора, регистра 14 дополнительного, регистра 15 дополнительного кода подключены к вторым входам третьего коммутатора 8 и к пятым входам второго коммутатора 7, выход счетчика 10 сдвигов подключен к шестым входам второго коммутатора 7, первые выходы третьего коммутатора 8 подключены соответственно к входам сумматора 16 и к вторым входам блока 17 логических операций и контроля, выходы сумматора 16 подключены к третьим входам блока 17 логических операций и контроля, вторые, третьи, четвертые, пятые, шестые, седьмые и восьмые выходы третьего коммутатора 8 подключены к четвертым, пятым, шестым, седьмым, восьмым, девятым и десятым входам блока 17 логических операций и контроля, выходы которого подключены к седьмым, восьмым и девятым входам второго коммутатора 7.

Процессор включает в себя два основных устройства: управляющий узел 1 и операционный узел 2.

Управляющий узел 1 координирует действия узлов операционного узла 2 между собой и с другими устройствами ЭВМ, а также выполняет набор операций, включающих команды обращения к памяти. Он вырабатывает в определенной временной последовательности управляющие сигналы, под действием которых в узлах операционного узла 2 выполняются требуемые действия.

Каждое такое элементарное действие, выполняемое в операционном узле 2 в течение одного тактового периода, называется микрооперацией.

В определенные тактовые периоды одновременно могут выполняться несколько микроопераций. Такая совокупность одновременно выполняемых микроопераций называется микрокомандой, а весь набор микрокоманд, предназначенных для решения определенной задачи, называется микропрограммой.

Общий временной интервал, в течение которого происходит выборка, хранение и преобразование одной команды в набор управляющих сигналов, называется циклом работы управляющего узла 1.

Таким образом, управляющий узел 1 осуществляет преобразование команды в соответствующий набор управляющих сигналов и обеспечивает:

чтение команды, находящейся в очередной ячейке памяти;

расшифровку кода операции (команды);

отыскание операндов (чисел) по указанному адресу, содержащемуся в команде;

обеспечить выдачу управляющих сигналов в операционный узел для выполнения над ними действий, указанных в коде операции команды.

В данном случае используется микропрограммный управляющий узел 1, в котором микрокоманды хранятся в управляющей памяти 19.

В этом случае слова, отображающие команды, хранятся в памяти в последовательно пронумерованных ячейках, что позволяет формировать адрес очередной команды добавлением единицы к адресу предыдущей команды, при этом слово состоит из нескольких частей: например, кода операции, указывающего вид операции, и адресов чисел, над которыми должна быть произведена соответствующая операция.

Дешифратор 3 кода операций по выбранной из оперативной памяти команде определяет номер требуемой микропрограммы в управляющей памяти 19.

Генератор 4 тактовых импульсов предназначен для формирования тактовых и синхронизирующих импульсов.

Счетчик 9 команд предназначен для формирования адреса ячейки памяти очередной команды путем естественной выборки, т.е. прибавлением к его содержимому единицы.

Регистр 11 адреса предназначен для формирования адреса ячейки памяти при командах условного или безусловного перехода с возвратом.

Блок 5 управления предназначен для определения адреса очередной микрокоманды в управляющей памяти 20, формирования адреса очередной команды (управления работой первого коммутатора 6), координации работы (выдачи синхроимпульсов) устройств процессора 1.

Управляющая память 19 представляет собой постоянное запоминающее устройство и предназначена для выдачи (в зависимости от кода операции) управляющих сигналов (сигналов управления, сигналов считывания, сигналов записи, сигналов установки в нулевое состояние) на функциональные узлы процессора. При этом слово памяти содержит информационные разряды (для управляющих сигналов) и контрольные разряды, сформированные на основе предлагаемого метода кодирования.

Блок 18 контроля (фиг.3) предназначен для обнаружения и исправления ошибок, возникающих при считывании информации с управляющей памяти 19. В этом случае при считывании микрокоманды, кодирующей схемой 63, проводится формирование контрольных разрядов принятого кодового набора, значения которых поразрядно сравниваются с принятыми значениями контрольных разрядов схемой 64 обнаружения ошибки. При несовпадении информации на выходе элемента 65 ИЛИ формируется сигнал ошибки, поступающий через второй коммутатор на входы устройства обмена.

Операционный узел 2 предназначен для выполнения арифметических и логических операций и включает в свой состав (фиг.1) счетчик 10 сдвигов, регистр 12 числа, регистр 13 сумматора, регистр 14 дополнительный, регистр 15 дополнительного кода, сумматор 16, блок 18 контроля.

Счетчик 10 сдвигов предназначен для подсчета количества сдвигов при выполнении операций умножения и деления, количества сдвигов промежуточных результатов и нормализации.

Регистр 11 адреса представляет собой регистр памяти и предназначен для хранения адреса очередной команды.

Регистр 12 числа представляет собой регистр памяти и предназначен для хранения операндов при выполнении арифметических и логических операций (хранения множимого, при выполнении операции умножения и делителя при выполнении операции деления).

Регистр 13 сумматора (аккумулятора) представляет собой регистр сдвига (вправо - при выполнении операции умножения и влево - при выполнении операции деления) и предназначен для хранения делимого старших разрядов результата умножения.

Заметим, что при выполнении операции деления блоком 5 управления анализируется значение знакового разряда регистра 12 числа и регистра 13 сумматора дополнительного.

Регистр 14 дополнительный представляет собой регистр сдвига (вправо - при выполнении операции умножения и влево - при выполнении операции деления) и предназначен для хранения множителя и младших разрядов результата умножения при выполнении операции умножения и результата деления при выполнении операции деления).

Заметим, что при выполнении операции умножения блоком 5 управления анализируется значение младшего разряда регистра 14 дополнительного.

Регистр 15 дополнительного кода представляет собой регистр памяти и предназначен для хранения отрицательного числа в дополнительном коде (при выполнении операции вычитания и операции деления).

Сумматор 16 представляет собой параллельный n-разрядный сумматор и предназначен для выполнения операции сложения чисел.

Блок 17 логических операций и контроля (фиг.2) предназначен для обнаружения и коррекции ошибок, возникающих при выполнении арифметических и логических операций.

Схема формирования поправки при выполнении арифметических операций (фиг.4) предназначена для формирования поправки при выполнении арифметических операций.

Так, при выполнении операции арифметических операций результат суммы с выхода сумматора 16 поступает на второй вход 21 блока 17 логических операций и контроля. Одновременно значения информационных разрядов слагаемых поступают на третий вход 22 блока 17 логических операций и контроля, при этом схема 47 формирования поправки при выполнении арифметических операций формирует вектор переносов С0, C1…Cn.

Допустим, требуется сложить два трехразрядных числа (отсутствует перенос в младший разряд): А=001 01 и В=011 10. В этом случае открывается элемент 67 И, который обеспечивает единичное значение сигнала С1. В свою очередь, единичное значение второго разряда второго слагаемого и единичное значение C1 обеспечит открытие элемента 71 И. В результате получим значение вектора переносов: С0=0; C1=1; C2=1.

Значение данного вектора через первый блок 55 элементов ИЛИ (фиг.2) поступает на вход первого блока 57 кодирования, который формирует значение поправки П в соответствии с выбранным методом кодирования информации: p1=С0⊕С1; p2=C1⊕С2, т.е. П=10.

При выполнении арифметической операции относительно информационных разрядов получим результат S=100. Сложение по mod2 значений контрольных разрядов, поступающих на вход первого блока 52 элементов неравнозначности (вход 29 блока логических операций и контроля), даст результат 11. Поразрядное сложение по mod2 полученного значения контрольных разрядов 11 со значением поправки 10 вторым блоком 53 элементов неравнозначности даст правильное значение контрольных разрядов 01 относительно полученной арифметической суммы 100.

Действительно: r1=y1⊕y2=0; r2=y2⊕y3=1.

Сравнение контрольных разрядов, сформированных относительно результата суммирования вторым блоком 58 кодирования со значением переданных контрольных разрядов с учетом поправки третьим блоком 54 элементов неравнозначности, даст нулевой результат, что свидетельствует об отсутствии ошибки.

При контроле операций сдвига схема формирования поправки при выполнении операции сдвига (фиг.5) вектора информации для вычисления поправок вычисляются в соответствии с выражениями: при сдвиге вправо x1=y1 1⊕y3; x2=y2⊕y3; x3=y2⊕y1; при сдвиге влево: x1=y3⊕y2; x2=y2⊕y1; x3=y3 1⊕y1.

При отсутствии переносов из младшей (старшей) триады вектора поправок получаются из выражений: x1=0⊕y3; x2=y2⊕y3; x3=y2⊕y1; при сдвиге влево: x1=y3⊕y2; x2=y2⊕y1; x1=0⊕y3.

Допустим, необходимо выполнить операцию сдвига вправо содержимое 110 10 (результаты частных произведений) регистра 13 сумматора). Тогда на выходе первого элемента 78 неравнозначности (фиг.5) имеем единичное значение, на выходе второго элемента 79 неравнозначности имеем нулевое значение, а на выходе третьего элемента 80 неравнозначности также имеем единичное значение сигнала, т.е. имеем вектор 101. Кодирование данного вектора первым блоком 57 выбранным методом даст значение поправки 11. При сдвиге информации вправо получим значение информационных разрядов 011, для которых значение контрольных разрядов соответствует значению 01.

Поразрядное сложение по mod2 вторым блоком 53 кодирования (фиг.2) исходного значения контрольных разрядов 10 со значением поправки 11 даст результат 01, который соответствует правильному значению контрольных разрядов при сдвиге рассматриваемой информации вправо.

При сдвиге влево информационных разрядов рассматриваемого примера получим результат 100 10. Вектор информации для вычисления поправки относительно исходной информации соответствует 010 (имеем нулевое значение сигналов на выходах второго элемента 80 неравнозначности, единичное значение сигнала на выходе третьего 81 элемента неравнозначности и нулевое значение сигнала на выходе четвертого элемента 80 неравнозначности. На выходе первого блока 57 кодирования имеем значение поправки 11. При сдвиге влево исходной информации имеем значении 100, для которой правильное значение контрольных разрядов равно 01. Поразрядное сложение исходного значения контрольных разрядов 10 со значением поправки 11 вторым блоком 53 элементов неравнозначности даст правильное значение контрольных разрядов для операции сдвига влево.

При выполнении логического умножения значение вектора для вычисления поправки к контрольным разрядам осуществляется схемой 48 формирования поправки при выполнении операции ИЛИ путем выполнения операции И относительно одноименных разрядов слагаемых.

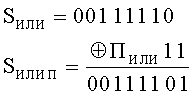

Так, например, при выполнении операции ИЛИ относительно информационных разрядов и сложения по mod2 контрольных разрядов первым блоком 52 элементов неравнозначности (фиг.2) чисел А=001 01 и В=011 10 имеем результат 011 11. Операция И относительно информационных разрядов даст значение вектора для вычисления поправки 001. В этом случае значение поправки равно 10. Тогда для рассматриваемого примера имеем результат 011 01, т.е. имеем правильное значение контрольных разрядов.

Аналогичным образом формируется поправка при выполнении логического умножения, только при формировании вектора поправки схемой 49 формирования поправки при выполнении операции И реализуется поразрядная операция ИЛИ относительно одноименных разрядов множимого и множителя.

Для операций логического сложения по mod2 блоком 43 сложения по mod2 и операции отрицания блоком 44 инвертирования формирование поправки к контрольным разрядам не требуется.

Значения контрольных разрядов, сформированные вторым блоком 58 кодирования относительно информационных разрядов, полученных при выполнении арифметических и логических операций, поразрядно сравниваются третьим блоком 54 элементов неравнозначности с переданными значениями контрольными разрядами с учетом поправки.

При отсутствии ошибок на его выходах имеем нулевое значение сигналов.

Работа процессора начинается с приходом сигнала "Пуск" по входной группе 33 входов устройства обмена процессора с периферийными блоками. По этой команде блок 5 выдает команду на считывание с управляющей памяти 19 содержимого первой ячейки памяти.

В первой ячейке памяти расположена команда "Сброс системы", которая устанавливает в исходное состояние регистры и блоки процессора. В счетчик 9 команд записывается "1", устройство управления 1 выдает микрокоманды в следующей последовательности.

1) На первом такте сигналы микрокоманды и значения контрольных разрядов поступают на выход блока 18 контроля, где проводится обнаружение и коррекция возникающих ошибок в соответствии с функциональной схемой, представленной на фиг.3.

В этом случае при считывании микрокоманды кодирующей схемой 62 проводится формирование контрольных разрядов принятого кодового набора.

Схемой 63 обнаружения ошибки производится поразрядное сравнение сформированных и переданных значений контрольных разрядов.

В случае возникновения ошибок на выходе группы 64 элементов ИЛИ появится единичный сигнал, свидетельствующий о ее наличии, который при поступлении синхроимпульса на вход элемента 65 И через второй коммутатор 7 поступает на устройство обмена.

Если ошибок нет, набор микрокоманд поступает на вход считывания счетчика 9 команд и на вход записи регистра 11 адреса, при этом содержимое счетчика 9 команд пересылается в регистр 11 адреса (или через первый коммутатор 6 на адресные входы запоминающего устройства при естественной выборке команд непосредственно со счетчика 9 команд).

2) На втором такте к содержимому счетчика 9 команд прибавляется единица - подготавливается адрес следующей команды.

1) На третьем такте сигналы микрокоманды поступают на вход считывания регистра 11 адреса и на вход считывания содержимого ячейки памяти запоминающего устройства по указанному адресу. При этом команда, хранящаяся в первой ячейке памяти, записывается в регистр 12 числа.

2) На четвертом такте сигналы микрокоманды подаются на вход считывания регистра 12 числа, вход второго коммутатора 7 и на вход дешифратора 3 кода операции, где раскодируются, после чего управляющий узел 1 переходит ко второму этапу работы.

Для примера рассмотрим порядок исполнения одной из команд, записанной в регистре 12 числа после выполнения первых четырех тактов.

Пусть в поле кода операции команды содержимого регистра 12 числа записана команда сложения содержимого регистра 13 сумматора с числом, расположенным запоминающем устройстве по адресу, указанному в поле адреса регистра 12 числа (при использовании одноадресной команды).

Управляющий узел 1 при этом выдает следующие микрокоманды:

3) На пятом такте сигналы микрокоманды подаются на вход считывания регистра 12 числа, на вход второго коммутатора 7, первого коммутатора 6 и на вход записи регистра 11 адреса (адрес, хранящийся в регистре 12 числа, записывается в регистр 11 адреса, содержимое регистра 12 числа обнуляется).

4) На шестом такте сигналы микрокоманды подаются на вход считывания регистра 11 адреса, на вход первого коммутатора 6, на вход считывания запоминающего устройства и на вход записи регистра 12 числа (из запоминающего устройства в регистр 12 числа записывается второе слагаемое (считаем, что первое слагаемое уже находится в регистре 13 сумматора).

5) На седьмом такте сигналы микрокоманды подаются на вход считывания регистра 12 числа и регистра 13 сумматора, при этом арифметико-логическое устройство осуществляет операцию сложения и запись результата сложения в регистр 13 сумматора следующим образом.

Результат суммы с выхода сумматора 16 поступает на блок 17 логических операций и контроля (фиг.2), далее устройство работает в соответствии с примером выполнения арифметических операций, приведенным выше. При этом сформированные значения контрольных разрядов относительно полученной операции сравниваются с переданными значениями контрольных разрядов третьим блоком 54 элементов неравнозначности (фиг.2). При отсутствии ошибки на его выходах имеем нулевые значения сигналов. При наличии ошибки и поступлении синхроимпульса на выходе элемента 61 И появится единичное значение сигнала. Информационные и контрольные разряды снимаются соответственно с выходов первой 59 и второй 60 групп элементов И.

Аналогичным образом процессор функционирует при выполнении логических операций.

8) На восьмом такте выдается микрокоманда "Конец операций" осуществляется переход на следующую операцию: блок 5 управления приводится в исходное состояние и выдает разрешение на начало выполнения следующей команды, адрес которой указан в счетчике 9 команд.

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Патент на полезную модель №76479 "Устройство памяти с обнаружением двойных ошибок" / Бородай В.Э., Царьков А.Н., Осипенко П.Н., Бобков С.Г., Павлов А.А., от 04.04.2008 г.

2. Калабеков Б.А, Микропроцессоры и их применение в системах передачи и обработки сигналов. М.: Радио и связь, 1988, 368 с.(стр.30, рис.1.3).

ПРИЛОЖЕНИЕ

1. Введение и постановка задачи

Характерной особенностью современных средств измерений является широкое использование автоматизированных систем измерения (АИС).

Отличительной особенностью АИС от отдельных измерительных приборов, обладающих ограниченными функциональными возможностями, является то, что она включает в свой состав ЭВМ, позволяющую осуществлять централизованное автоматизированное (автоматическое) управление объектом исследования, процессом измерения и обработки измерительной информации [1].

Во многих случаях практики изучаемый объект находится на значительном удалении от потребителя измерительной информации. При этом наряду с задачей получения информации непосредственно от объекта возникает задача передача этой информации по каналу связи от объекта к потребителю.

Независимо от способа передачи сигналы должны быть представлены в форме, удобной для обработки в ЭВМ, обеспечивать однозначность представления сообщений и обладать устойчивостью к искажениям, возникающим по тем или иным причинам в устройствах хранения и передачи информации [1].

Необходимость контроля арифметических и логических операций, выполняемых в арифметико-логических устройствах (АЛУ) процессора, объясняется тем, что в этом устройстве осуществляется наиболее сложное преобразование информации, являющееся завершающим этапом работы ЭВМ в целом. Поэтому элементы арифметического устройства (АУ) работают в более напряженных режимах, чем элементы других устройств, что является причиной возникновения сбоев в работе.

Задача контроля - выявление возникающих сбоев в АУ и устранение последствий этих сбоев.

Эффективность автоматизированных систем измерительной техники в значительной степени определяется достоверностью информации, которая обрабатывается в данных системах [4].

В свою очередь, достоверность функционирования цифровых устройств существенно зависит от выбранного метода обнаружения ошибок (обнаруживающей способности выбранного метода контроля информации и аппаратурных затрат, необходимых для реализации данного метода).

В настоящее время широкое распространение получил контроль арифметических операций сложения по модулю, который основан на известных тождествах [2].

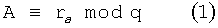

Из теории чисел известно, что любое число можно записать в виде тождества:

(читается: А сравнимо или тождественно с остатком га модуля q), которое устанавливает следующее соотношение между числами А, га и q:

где А, q, t и га - целые числа;

А - любое контролируемое n-разрядное число;

q - модуль или делитель;

t - частное;

rа - остаток от деления числа А на модуль q (контрольный код числа А).

Каждому контролируемому n-разрядному числу А придаются еще m дополнительных разрядов, в которые записывается контрольный код, т.е. величина остатка га от деления А на mod q, по которому осуществляется контроль.

При контроле по модулю должно выполняться условие m<n; в противном случае из-за большого объема контрольной аппаратуры надежность контролируемой системы снижается.

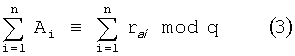

При числовом контроле по модулю контрольным кодом числа является остаток от деления самого числа А на mod q. В этом виде контроля справедливо тождество:

означающее, что сумма чисел сравнима с суммой остатков этих же чисел по одному и тому же модулю.

Если q=p, то А≡ a i modp и контроль не имеет смысла, так как мы контролируем только младший разряд a i числа А, а старшие разряды не будут принимать участия в образовании остатка и ошибки в этих разрядах не будут выявляться, т.е. контроль будет малоэффективным.

Гораздо большую обнаруживающую способность имеет метод контроля информации по mod3, однако реализация данного метода требует больших аппаратурных затрат на построение схем сверток и временных затрат, связанных с задержкой прохождения сигнала.

Контрольный код при цифровом контроле есть сумма цифр данного числа - по некоторому модулю.

В настоящее время для этой цели наиболее широко используется метод контроля на четность, который требует минимальных аппаратурных затрат для обнаружения ошибок двоичного набора.

При q=р (контроль по mod 2) для цифрового контроля тождество (1) выполняется с дополнительным условием, заключающимся в том, что при контроле арифметических операций необходимо учитывать все переносы, возникающие при сложении двух чисел.

Недостатком данного метода является низкая обнаруживающая способность, так как обнаруживаются только одиночные (нечетные) ошибки.

В то же время в экстремальных условиях работы АИС (воздействий электромагнитных или радиационных излучений и т.п.) возрастает вероятность появления двойных и ошибок прочей кратности.

В связи с этим возникает необходимость в разработке метода контроля выполнения арифметических операций, обнаруживающего 100% одиночных ошибок и максимальное количество двойных ошибок при минимальных аппаратурных и временных затратах на декодирование.

Для этой цели в данной работе предлагается использовать метод обнаружения ошибок в устройствах хранения и передачи информации, предложенный в работах [3.5].

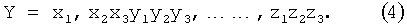

В этом случае при кодировании двоичного набора с произвольным числом информационных разрядов (пусть число информационных разрядов кратно трем) двоичный набор разбивается на блоки информации, по три разряда в каждом блоке:

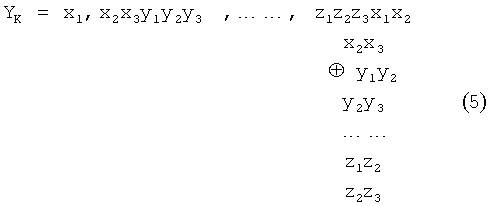

В результате кодирования рассматриваемого двоичного набора предлагаемым методом получим кодовый набор:

или

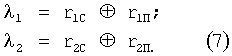

Обнаружение ошибок производится путем поразрядного сложения по mod2 значений контрольных разрядов r1C и r2C, считываемых с устройства хранения информации соответственно со значениями контрольных разрядов r1П и r2П, сформированных относительно полученных информационных разрядов:

Нулевой результат суммы свидетельствует об отсутствии ошибки и ее наличии в противном случае.

Данный метод позволяет обнаруживать 100% одиночных ошибок и до 80% двойных ошибок.

2. Обнаружение и исправление ошибок при выполнении арифметических операций

Преимущественное распространение в современных вычислительных машинах имеют сумматоры параллельного действия, в которых передача чисел и образование суммы происходит одновременно для всех разрядов.

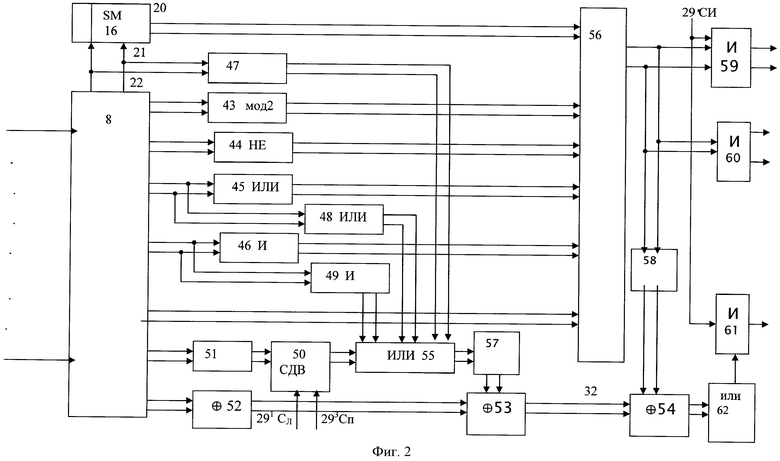

Рассмотрим основные положения метода контроля операции сложения на примере.

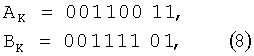

Допустим, требуется сложить два шестиразрядных числа: А=001100 и В=001111. При кодировании данных чисел предлагаемым методом получим кодовые наборы соответственно:

которые будут записаны в устройстве хранения информации.

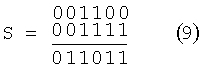

Арифметическое суммирование информационных разрядов данных кодовых наборов с учетом переносов даст результат:

Для полученной суммы значения контрольных разрядов должны иметь соответственно значения 00.

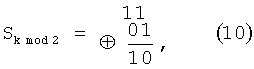

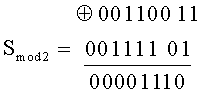

Однако сложение контрольных разрядов слагаемых по mod 2 даст результат:

который отличается от правильного значения 00.

В связи с этим для формирования правильных значений контрольных разрядов возникает необходимость определения поправки к значению контрольных разрядов Skmod2.

Правило формирования поправки может быть получено на основе кодирования информации, учитывающей все переносы, возникающие при сложении двух чисел.

Для рассматриваемого примера при сложении информационных разрядов перенос единичных значений сигналов осуществляется в четвертый и пятый разряды (см.9), т.е. информация, учитывающая переносы, имеет вид: SП=011000.

Свойство 1. Формирование поправки Пк к значению контрольных разрядов Skmod2 осуществляется путем кодирования информации, учитывающей переносы SП, выбранным методом кодирования.

Для рассматриваемого примера кодирование значения SП=011000 предлагаемым методом даст значение поправки Пк=10.

Поразрядное сложение по mod2 значения Skmod2=10 и значения поправки Пк=10 даст правильное значение контрольных разрядов для полученной арифметической суммы S=011011.

В результате имеем правильный кодовый набор суммы:

Sк=011011 00.

3. Метод контроля АЛУ при выполнении логических операций

Рассмотрим контроль АЛУ на основе предлагаемого метода кодирования при выполнении следующих наиболее распространенных логических операций:

а) операции сложения по mod2,

б) операции сдвига,

в) операции логического сложения,

г) операции логического умножения,

д) операции инвертирования,

3.1 Контроль операции сложения по mod2

Контроль операции сложения по mod2 рассмотрим на примере.

Допустим, требуется сложить два шестиразрядных числа: А=001100 и В=001111. При кодировании данных чисел предлагаемым методом получим кодовые наборы соответственно: Ак=001100 11 и Вк=001111 01, которые будут записаны в устройстве хранения информации. Сложение кодовых наборов по mod2 даст результат:

Свойство 1. Результат сложения по mod2 контрольных разрядов слагаемых соответствует результату сложения по mod2 информационных разрядов рассматриваемых слагаемых.

Данное свойство позволяет контролировать операцию сложения по mod2 и при этом обнаруживать и исправлять возникающие ошибки по правилам предлагаемого метода кодирования.

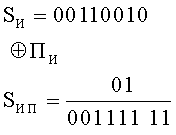

3.2 Контроль операции сдвига

Рассмотрим основные положения способа контроля операции сдвига на примере кодового набора, содержащего три информационных разряда:

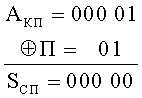

АК=001 01.

Пусть требуется провести операцию сдвига информационных разрядов вправо на один разряд, в результате получим кодовый набор: АКП=000 01, у которого значение контрольных разрядов, не соответствует полученному результату.

В связи с этим возникает необходимость формирования поправки, позволяющей получить набор контрольных разрядов, соответствующий значению информационных разрядов, полученных при сдвиге вправо.

Для получения правильного значения контрольных разрядов сформируем поправку к имеющемуся значению контрольных разрядов.

Значение поправки при сдвиге вправо формируется на основе исходного значения информационных разрядов следующим образом: x1=0⊕y3; (0, если в старший разряд не переносится единица из другого регистра, в противном случае x1=y1 i⊕y3, где y1 i - значение сигнала переноса из другого регистра, например в старший разряд регистра дополнительного из младшего разряда регистра сумматора при выполнении операции умножения) x2=y3⊕y2; x3=y2⊕y1.

Для рассматриваемого примера при сдвиге вправо (при отсутствии переноса из другого регистра)Ак=001 01 получим

АКП=000 01.

Двоичный набор для получения поправки П, равный:

ХП=(x1=0, x2=0, x3=1).

При кодировании данного набора предлагаемым методом получим значение поправки ПП=01.

Сложение по mod2 исходного значения контрольных разрядов со значением поправки даст правильное значение контрольных разрядов при сдвиге информационных разрядов вправо:

При сдвиге информационных разрядов влево значение поправки формируется на основе исходного значения информационных разрядов следующим образом: x1=y3⊕y2; x2=y2⊕y1; x3=y3 i⊕y1

(х3=y3 i⊕y1, где у3 i - значение сигнала переноса старшего разряда одного регистра в младший разряд другого).

Пусть требуется провести операцию сдвига влево(при отсутствии переноса из другого регистра) на один разряд для двоичного набора АК=001 01, в результате получим кодовый набор: АКЛ=010 01, у которого значение контрольных разрядов не соответствует полученному результату (значению контрольных разрядов, равному 11).

Информация для поправки имеет вид: ХЛ==(x1=0, x2=1, x3=1).

При кодировании данного набора предлагаемым методом получим значение поправки ПЛ=10.

Сложение по mod2 исходного значения контрольных разрядов со значением поправки даст правильное значение контрольных разрядов при сдвиге информационных разрядов влево:

Свойство 2. Сложение по mod2 исходного значения контрольных разрядов со значением поправки при сдвиге вправо (влево) даст правильное значение контрольных разрядов при сдвиге информационных разрядов.

Данное свойство позволяет контролировать операцию сдвига и при этом обнаруживать и исправлять возникающие ошибки по правилам предлагаемого метода кодирования.

3.3 Контроль выполнения логической операции ИЛИ

Рассмотрим основные положения способа контроля операции ИЛИ на примере.

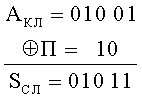

Допустим, требуется выполнить логическую операцию ИЛИ относительно двух шестиразрядных числа: А=001100 и В=001111. При кодировании данных чисел предлагаемым методом получим кодовые наборы соответственно: АК=001100 11 и ВК=001111 01, которые будут записаны в устройстве хранения информации.

Логическое сложение информационных разрядов кодовых наборов и сложение по mod2 контрольных разрядов даст результат:

В этом случае значение контрольных разрядов не соответствует полученному результату (правильное значение контрольных разрядов имеет значение 01).

В связи с этим возникает необходимость формирования поправки, позволяющей получить набор контрольных разрядов, соответствующий значению информационных разрядов, полученных при выполнении операции логического сложения.

Для формирования поправки построим двоичный набор, используя логическую операцию И относительно информационных разрядов рассматриваемых чисел, в результате получим кодовый набор: 001100.

Кодирование полученного двоичного набора выбранным методом кодирования даст значения поправки к контрольным разрядам при выполнении операции ИЛИ:

ПИЛИ=11

Сложение по mod2 полученного значения контрольных разрядов со значением поправки даст правильное значение контрольных разрядов для рассматриваемой операции:

Свойство 3. Операция сложения по mod2 полученных значений контрольных разрядов и значения поправки, сформированной на основе кодирования информации, полученной при выполнении логической операции И относительно информационных разрядов, даст правильное значение контрольных разрядов.

3.4 Контроль выполнения логической операции И

Рассмотрим основные положения способа контроля операции И на примере.

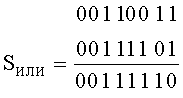

Допустим, требуется выполнить логическую операцию И относительно двух шестиразрядных числа: А=0011 00 и В=0011 11. При кодировании данных чисел предлагаемым методом получим кодовые наборы соответственно: АК=00110011 и ВК=00111101, которые будут записаны в устройстве хранения информации.

Логическое умножение информационных разрядов кодовых наборов и сложение по mod2 контрольных разрядов даст результат:

В этом случае значение контрольных разрядов не соответствует полученному результату (правильное значение контрольных разрядов имеет значение 11).

В связи с этим возникает необходимость формирования поправки, позволяющей получить набор контрольных разрядов, соответствующий значению информационных разрядов, полученных при выполнении операции логического сложения.

Для формирования поправки построим двоичный набор, используя операцию логическую ИЛИ относительно информационных разрядов рассматриваемых чисел, в результате получим кодовый набор: 001 111.

Кодирование полученного двоичного набора выбранным методом кодирования даст значения поправки к контрольным разрядам при выполнении операции И:

ПИ=01

Сложение по mod2 полученного значения контрольных разрядов со значением поправки даст правильное значение контрольных разрядов для рассматриваемой операции:

Свойство 5. Операция сложения по mod2 полученных значений контрольных разрядов и значения поправки, сформированной на основе кодирования информации, полученной при выполнении логической операции ИЛИ относительно информационных разрядов, даст правильное значение контрольных разрядов.

3.5 Контроль выполнения логической операции НЕ

Рассмотрим основные положения способа контроля операции инверсии на примере.

Допустим, требуется выполнить логическую операцию НЕ для кодового набора: АК=001100 11

При выполнении операции НЕ для информационных разрядов получим кодовый набор АК=110 011 11, у которого значения контрольных разрядов соответствуют правильному значению контрольных разрядов.

Свойство 6. Значения контрольных разрядов при выполнении логической операция НЕ имеют правильное значение.

Таким образом, предлагаемый метод обнаружения ошибок позволяет обнаруживать все одиночные ошибки и максимальное количество двойных ошибок АЛУ при незначительном увеличении аппаратурных затрат по отношению к методу контроля на четность, без снижения быстродействия обработки информации.

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Куликовский К.Л., Купер В.Я. Методы и средства измерений. M.: - Энергоатомиздат, 1986, 447 с.

2. Путинцев Н.Д. Аппаратный контроль управляющих цифровых вычислительных машин. М.: Советское радио, 1966, 424 с.

3. Павлов А.А., Павлов П.А. Царьков А.Н., Хоруженко О.В. Функционально-кодовый контроль ошибок в автоматизированных системах измерительной техники. // Измерительная техника, 2009, №9, с.3-5.

4. Щербаков Н.С. Достоверность работы цифровых устройств. М.: Машиностроение, 1989, 224 с.

5. A.A.Pavlov, P.A.Pavlov A.N.Tsarkov and O.V.Khoruzheko. Functional cod error monitoring in computerized data-acquisiti systems. / Measurement Techniques, Springer New York, V0f. 52, №9, 2009, p.891-893.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2018 |

|

RU2708956C2 |

| ОТКАЗОУСТОЙЧИВАЯ ЭВМ | 2018 |

|

RU2704325C1 |

| УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2421786C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2422923C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ИСПРАВЛЕНИЕМ ОДИНОЧНЫХ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ И ОБНАРУЖЕНИЕМ ПРОИЗВОЛЬНЫХ ОШИБОК В БАЙТАХ ИНФОРМАЦИИ | 2011 |

|

RU2450331C1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ИСПРАВЛЕНИЕМ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ И ОБНАРУЖЕНИЕМ ОШИБОК В БАЙТАХ ИНФОРМАЦИИ | 2011 |

|

RU2448359C1 |

| УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ С КОРРЕКЦИЕЙ ОДИНОЧНЫХ ОШИБОК И ОБНАРУЖЕНИЕМ ДВОЙНЫХ ОШИБОК | 2024 |

|

RU2826822C1 |

Изобретение относится к области вычислительной техники. Техническим результатом является повышение достоверности функционирования процессора за счет обнаружения и коррекции возникающих ошибок. Он достигается тем, что дополнительно в известный процессор введены: дешифратор кода операции, генератор тактовых импульсов, блок управления, первый коммутатор, второй коммутатор, третий коммутатор, счетчик команд, счетчик сдвигов, регистр адреса, регистр числа, регистр сумматора, регистр дополнительный, регистр дополнительного кода, сумматор, блок контроля, управляющая память, блок логических операций и контроля, включающий блок логического сложения по mod2, блок инвертирования, блок логического сложения, блок логического умножения, функциональную схему формирования поправки при выполнении арифметических операций, функциональную схему формирования поправки при выполнении операции ИЛИ, функциональную схему формирования поправки при выполнении операции И, функциональную схему формирования поправки при выполнении операции сдвига, элемент задержки, первый блок элементов неравнозначности, второй блок элементов неравнозначности, третий блок элементов неравнозначности, первый блок элементов ИЛИ, второй блок элементов ИЛИ, блок кодирования, первый блок элементов И, второй блок элементов И, элемент И. 5 ил.

Процессор повышенной достоверности функционирования, содержащий управляющий узел, операционный узел, первые входы управляющего узла являются входами процессора, вторая группа входов управляющего узла подключена к первым выходам операционного узла, выходы управляющего узла подключены к первым входам операционного узла, вторые входы которого являются входами данных, а вторые выходы являются выходами данных, отличающийся тем, что он дополнительно содержит дешифратор кода операции, генератор тактовых импульсов, блок управления, первый коммутатор, второй коммутатор, третий коммутатор, счетчик команд, счетчик сдвигов, регистр адреса, регистр числа, регистр сумматора, регистр дополнительный, регистр дополнительного кода, сумматор, блок контроля, управляющую память, блок логических операций и контроля, включающий блок логического сложения по mod2, блок инвертирования, блок логического сложения, блок логического умножения, функциональную схему формирования поправки при выполнении арифметических операций, функциональную схему формирования поправки при выполнении операции ИЛИ, функциональную схему формирования поправки при выполнении операции И, функциональную схему формирования поправки при выполнении операции сдвига, элемент задержки, первый блок элементов неравнозначности, второй блок элементов неравнозначности, третий блок элементов неравнозначности, первый блок элементов ИЛИ, второй блок элементов ИЛИ, блок кодирования, первый блок элементов И, второй блок элементов И, элемент И, выходы устройства обмена подключены к первому входу блока управления и к первому входу второго коммутатора, вторые входы которого подключены к выходам запоминающего устройства, первые выходы второго коммутатора поступают на вход устройства обмена, вторые выходы поступают на вход запоминающего устройства, а третьи выходы подключены соответственно к первым входам счетчика команд, счетчика сдвигов, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к входам дешифратора кода операции, к вторым входам блока управления, к первому входу первого коммутатора, первый выход которого подключен к первому входу регистра адреса, третий вход блока управления подключен к выходам дешифратора кода операции, а четвертый вход подключен к выходам генератора тактовых импульсов, а пятый вход подключен к первому выходу управляющей памяти, первый выход блока управления подключен к входу управляющей памяти, первые выходы которой подключены к первым входам блока контроля, второй выход блока управления подключен к второму входу первого коммутатора, третьи и четвертые входы которого подключены соответственно к выходам регистра адреса и счетчика команд, а с второго выхода снимается адрес ячейки памяти запоминающего устройства, третий выход блока управления подключен соответственно к вторым входам блока контроля, к вторым входам счетчика команд, счетчика сдвигов, регистра адреса, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к первой группе входов третьего коммутатора, к третьей группе входов второго коммутатора, к первой группе входов блока логических операций и контроля и является выходом синхроимпульсов, второй, третий, четвертый пятый выходы управляющей памяти подключены к третьим и четвертым пятым и шестым входам блока контроля, при этом второй выход подключен к четвертому входу второго коммутатора, а третьи, четвертые и пятые выходы блока управляющей памяти подключены соответственно к третьим, четвертым, пятым и шестым входам счетчика команд, счетчика сдвигов, регистра адреса, регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода, к первой группе входов третьего коммутатора, к третьей группе входов второго коммутатора, к первой группе входов блока логических операций и контроля и являются выходам управляющих сигналов, сигналов считывания, сигналов записи, сигналов установки устройств в нулевое состояние, шестой выход блока управляющей памяти подключен к пятому входу блока управления, выходы регистра числа, регистра сумматора, регистра дополнительного, регистра дополнительного кода подключены к вторым входам третьего коммутатора и к пятым входам второго коммутатора, выход счетчика сдвигов подключен к шестым входам второго коммутатора, первые выходы третьего коммутатора подключены соответственно к входам сумматора и к вторым входам блока логических операций и контроля, выходы сумматора подключены к третьим входам блока логических операций и контроля, вторые, третьи, четвертые, пятые, шестые, седьмые и восьмые выходы третьего коммутатора подключены к четвертым, пятым, шестым, седьмым, восьмым, девятым и десятым входам блока логических операций и контроля, выходы которого подключены к седьмым, восьмым и девятым входам второго коммутатора.

| КАЛАБЕКОВ Б.А | |||

| Микропроцессоры и их применение в системах передачи и обработки сигналов | |||

| - М.: Радио и связь, 1988, с.30 | |||

| Прибор для опробования нефтяных пластов в буровых скважинах | 1934 |

|

SU51428A1 |

| МИКРОПРОЦЕССОР ГИБРИДНЫЙ | 2007 |

|

RU2359315C2 |

| WO 2010068492 A2, 17.06.2010. | |||

Авторы

Даты

2012-01-10—Публикация

2010-07-08—Подача