Изобретение относится к области техники связи и может быть использовано в системах передачи данных, а также в системах телеизмерения и телеуправления для передачи информации без предварительного фазирования.

Кодек или кодирующее и декодирующее устройства, описанные в настоящей заявке, применимы для кодирования и декодирования линейных циклических помехоустойчивых кодов. Помимо кодирования и декодирования информации осуществляется также цикловая синхронизация помехоустойчивого кода. Причем синхронизирующие признаки передаются словами помехоустойчивого кода и для синхронизации не требуется передача дополнительных синхронизирующих символов, а используется избыточность самого помехоустойчивого кода. После установления синхронизации, признаки синхронизации снимаются с помехоустойчивого кода, не уменьшая корректирующую способность кода.

При этом актуальной является задача сокращения количества операций при синхронизации, а также кодировании и декодировании помехоустойчивого кода и упрощение кодека.

Известен кодек циклического помехоустойчивого кода, содержащий на передающей стороне формирователь информационной части кодового слова, состоящий из регистра сдвига, соединенного с сумматором по модулю два, и формирователь синхронизирующей части кодового слова, причем выходы формирователей соединены с сумматором по модулю два частей кодового слова, а на приемной стороне содержащий двоичный фильтр информационной части кодового слова, состоящий из регистра сдвига, соединенного с сумматорами по модулю два, и дешифратор [1].

Однако это устройство имеет сложную аппаратную реализацию.

Наиболее близким к предлагаемому устройству является кодек помехоустойчивого кода (прототип), содержащий на передающей стороне формирователь информационной части кодового слова, состоящий из регистра сдвига, соединенного с сумматором по модулю два, и формирователь синхронизирующей части кодового слова, причем выходы формирователей соединены с сумматором по модулю два частей кодового слова, а на приемной стороне содержащий двоичный фильтр информационной части кодового слова, состоящий из регистра сдвига, соединенного с сумматорами по модулю два, и накопитель, блок коррекции ошибок, дешифратор, при этом накопитель подключен к выходу сумматора по модулю два двоичного фильтра, а выход дешифратора соединен с управляющим входом блока коррекции ошибок [2].

Недостатком этого устройства является высокая сложность, поскольку для выделения информационной и синхронизирующей частей кода требуется дополнительное количество операций и значительные аппаратные затраты при реализации.

Цель предлагаемого изобретения - упрощение кодека циклического помехоустойчивого кода за счет того, что информационная и синхронизирующая части кодового слова разделены и для их выделения не требуется дополнительных операций, а значит и устройств.

Для достижения цели предложен кодек помехоустойчивого кода, содержащий на передающей стороне формирователь информационной части кодового слова, состоящий из регистра сдвига, соединенного с сумматором по модулю два, и формирователь синхронизирующей части кодового слова, причем выходы формирователей соединены с сумматором по модулю два частей кодового слова, а на приемной стороне содержащий двоичный фильтр информационной части кодового слова, состоящий из регистра сдвига, соединенного с сумматорами по модулю два, и накопитель, блок коррекции ошибок, дешифратор, при этом накопитель подключен к выходу сумматора по модулю два двоичного фильтра, а выход дешифратора соединен с управляющим входом блока коррекции ошибок. Новым является то, что на передающей стороне введен переключатель, первый вход которого подключен к выходу сумматора по модулю два частей кодового слова, а второй вход подключен к выходу формирователя информационной части кодового слова, на приемной стороне введен регистр информационной части кодового слова, вход которого подключен к выходу регистра сдвига двоичного фильтра, при этом выходы накопителя подключены к входам дешифратора и блока коррекции ошибок, выходы которого соединены с инвертирующими входами регистра информационной части кодового слова.

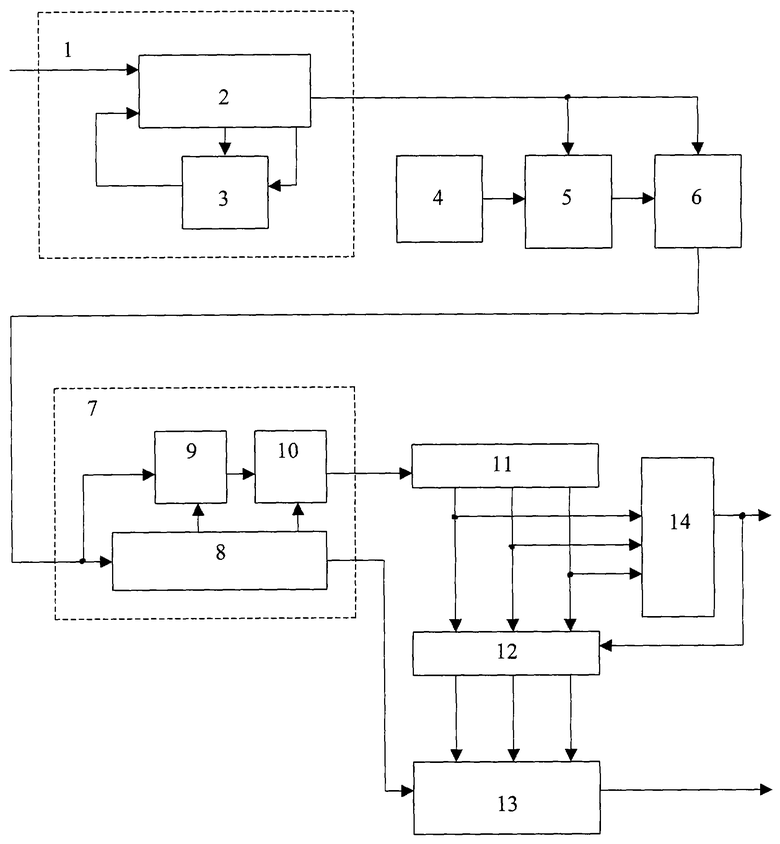

На чертеже приведена структурная схема предлагаемого устройства.

На передающей стороне кодек циклического помехоустойчивого кода (кодирующее устройство) содержит формирователь информационной части кодового слова 1, состоящий из регистра сдвига 2, соединенного с сумматором по модулю два 3, формирователь синхронизирующей части кодового слова 4, сумматор по модулю два частей кодового слова 5 и переключатель 6.

На приемной стороне кодек циклического помехоустойчивого кода (декодирующее устройство) содержит двоичный фильтр 7, состоящий из регистра сдвига 8, соединенного с сумматорами по модулю два 9 и 10, накопитель 11, блок коррекции ошибок 12, регистр информационной части кодового слова 13 и дешифратор 14.

Предлагаемое устройство работает следующим образом.

На передающей стороне линии связи формирователь информационной части кодового слова 1 генерирует кодовое слово циклического помехоустойчивого кода. С этой целью в цепи обратной связи регистра сдвига 2 включен сумматор по модулю два регистра сдвига 2, включен сумматор по модулю два 3. Отводы регистра сдвига 2 на сумматор по модулю два 3 соответствуют ненулевым коэффициентам образующего многочлена циклического помехоустойчивого кода g(x).

В начале работы k бит исходной информации записывается в k разрядный регистр сдвига 2. Затем в течение n тактов, где n - блоковая длина кода, осуществляется сдвиг этой информации. При этом в течение первых k тактов на выходе регистра сдвига 2 будут символы исходной информации, а в течение последующих n-k тактов - проверочные символы кода.

Переключатель 6 в течение первых k тактов пропускает k символов исходной информации с выхода формирователя информационной части кодового слова 1 в линию связи. В течение последующих n-k тактов осуществляется суммирование на сумматоре по модулю два 5 проверочных символов кода с символами синхронизирующей последовательности. При этом переключатель 6 подключает выход сумматора по модулю два 5 к линии связи. В качестве синхронизирующей последовательности может использоваться любая двоичная последовательность длины n-k символов с хорошими синхронизирующими свойствами, например, последовательность Баркера или последовательность максимальной длины (М - последовательность).

Синхронизирующая последовательность генерируется формирователем синхронизирующей части кодового слова 4. Формирователь синхронизирующей части кодового слова 4 может быть выполнен, например, в виде регистра сдвига, имеющего n-k разрядов, в который по сигналу начальной установки записывается постоянная синхронизирующая последовательность.

Таким образом, на выход передающей части кодека поступает n-битное кодовое слово, первые k бит которого составляет исходная информация в неизменном виде, а следующие n-k бит представляют собой сумму по модулю два проверочных символов кодового слова и символов синхронизирующей последовательности.

На приемной стороне кодовые слова поступают на вход двоичного фильтра 7, который содержит регистр сдвига 8 и сумматоры по модулю два 9 и 10, включенные в соответствии с образующим многочленом кода g(x). При этом двоичный фильтр 7 вычисляет синдром циклического помехоустойчивого кода, т. е. сумму по модулю два проверочных символов кода, вычисленных по принятым информационным символам и принятых проверочных символов. При поступлении безошибочного кодового слова синдром кода равен нулю и в результате вычисления синдрома будет получена передаваемая синхронизирующая последовательность. При поступлении на вход слова с ошибками будет вычислена комбинация из некоторого множества двоичных комбинаций, соответствующая сумме ненулевого синдрома кода и синхронизирующей последовательности.

Синхронизирующая последовательность с наложенным синдромом с выхода двоичного фильтра 7 поступает в накопитель 11, а информационная последовательность с выхода регистра сдвига 8 - в регистр информационной части кодового слова 13.

К накопителю 11 подключен дешифратор 14, настроенный на структуру синхронизирующей последовательности с учетом синдрома кода, соответствующего комбинации ошибок допустимой кратности. При этом допустимая кратность ошибок определяется исправляющей способностью помехоустойчивого кода или минимальным кодовым расстоянием помехоустойчивого кода. Выбор подмножества дешифрируемых ошибок проводится с учетом эффекта размножения канальных ошибок, вызванных прохождением последовательности через двоичный фильтр 7.

Срабатывание дешифратора 14 свидетельствует о приеме синхронизирующей последовательности с допустимой кратностью ошибок. При этом в регистре информационной части кодового слова 13 будет находиться принятая информация.

Место расположения ошибок локализуется блоком коррекции ошибок 12 при определении комбинации синдрома кода с наложенной синхронизирующей последовательностью. Блок коррекции ошибок может быть выполнен, например, в виде постоянного запоминающего устройства (ПЗУ), в которое записаны таблицы ошибок. Входом этих таблиц является двоичная комбинация, соответствующая комбинации синдрома с наложенной синхронизирующей последовательностью, а выходом - соответствующая двоичная комбинация ошибок в информационной части кодового слова.

Это позволяет произвести исправление ошибочных знаков в регистре информационной части кодового слова 13. Исправление ошибок в регистре информационной части кодового слова 13 осуществляется путем инверсии соответствующих разрядов в принятой информации.

Далее откорректированная информация поступает на выход кодека.

Наложение синхронизирующей последовательности на кодовые слова придает словам помехоустойчивого кода свойство самосинхронизируемости и не требует введения дополнительной избыточности для целей синхронизации.

В предлагаемом изобретении, в отличие от известного устройства, информационная и синхронизирующая части кодового слова разделены между собой, поэтому не требуется дополнительных устройств для выделения информационной части кодового слова. Кроме того, информационная часть кодового слова передается в неизменном виде и отпадает необходимость в специальном формирователе информационной части кодового слова, как в известном устройстве.

Достигаемым техническим результатом предлагаемого кодека циклического помехоустойчивого кода является уменьшение его сложности и аппаратных затрат на реализацию.

Источники информации

1. Авторское свидетельство СССР 365033, кл. Н 03 К 13/04, опубл. 21.11.73.

2. Авторское свидетельство СССР 809550, кл. Н 03 К 13/04, опубл. 28.02.81.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2254676C2 |

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2251210C1 |

| УСТРОЙСТВО АДАПТИВНОЙ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2259638C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2302701C1 |

| СПОСОБ ДЕКОДИРОВАНИЯ ЦИКЛИЧЕСКОГО ПОМЕХОУСТОЙЧИВОГО КОДА | 2002 |

|

RU2231216C2 |

| СПОСОБ АДАПТИВНОЙ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2001 |

|

RU2210870C2 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ ПОМЕХОУСТОЙЧИВЫМ КОДОМ С ПЕРЕМЕННЫМИ ПАРАМЕТРАМИ | 2004 |

|

RU2260246C1 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2001 |

|

RU2214689C2 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С ИНТЕГРИРОВАННЫМИ МЯГКИМИ И ЖЕСТКИМИ РЕШЕНИЯМИ | 2011 |

|

RU2450464C1 |

Изобретение относится к области техники связи. Технический результат заключается в упрощении и уменьшении затрат на реализацию кодека циклического помехоустойчивого кода. Сущность изобретения заключается в том, что на передающей стороне введен переключатель, первый вход которого подключен к выходу сумматора по модулю два частей кодового слова, а второй вход подключен к выходу формирователя информационной части кодового слова, на приемной стороне введен регистр информационной части кодового слова, вход которого подключен к выходу регистра сдвига двоичного фильтра, при этом выходы накопителя подключены к входам дешифратора и входам блока коррекции ошибок, выходы которого соединены с инвертирующими входами регистра сдвига информационной части кодового слова. 1 ил.

Кодек циклического помехоустойчивого кода, содержащий на передающей стороне формирователь информационной части кодового слова, состоящий из регистра сдвига, соединенного с сумматором по модулю два и формирователь синхронизирующей части кодового слова, причем выходы формирователей соединены с сумматором по модулю два частей кодового слова, а на приемной стороне - двоичный фильтр информационной части кодового слова, состоящий из регистра сдвига, соединенного с сумматорами по модулю два и накопитель, блок коррекции ошибок, дешифратор, при этом накопитель подключен к выходу двоичного фильтра, а выход дешифратора соединен с управляющим входом блока коррекции ошибок, отличающийся тем, что на передающей стороне введен переключатель, первый вход которого подключен к выходу сумматора по модулю два частей кодового слова, а второй вход - к выходу формирователя информационной части кодового слова, при этом переключатель подключает выход формирователя 1 информационной части кодового слова и сумматор по модулю два 5 к линии связи, а на приемной стороне введен регистр информационной части кодового слова, вход которого подключен к выходу регистра сдвига двоичного фильтра, при этом выходы накопителя подключены к входам дешифратора и блока коррекции ошибок, выходы которого соединены с инвертирующими входами регистра информационной части кодового слова.

| Декодирующее устройство | 1979 |

|

SU809550A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 0 |

|

SU365033A1 |

| СПОСОБ КОЛИЧЕСТВЕННОГО ОПРЕДЕЛЕНИЯ МИКРООРГАНИЗМОВ В ВЕЩЕСТВАХ | 0 |

|

SU200124A1 |

| СИСТЕМА ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ С ИСПРАВЛЕНИЕМ ОШИБОК | 1991 |

|

RU2007042C1 |

Авторы

Даты

2003-09-10—Публикация

2002-03-20—Подача