Изобретение относится к области техники связи и может быть использовано в системах передачи данных, а также в системах телеизмерения и телеуправления для передачи информации без предварительного фазирования.

Кодек или кодирующее и декодирующее устройства, описанные в настоящей заявке, применяют для кодирования и декодирования помехоустойчивых линейных циклических кодов, а также для цикловой синхронизации этих помехоустойчивых кодов. В предлагаемом устройстве в канал связи передают последовательность символов, равную сумме символов помехоустойчивого кода и символов синхронизирующей последовательности. Цикловую синхронизацию осуществляют с помощью синхронизирующей последовательности, наложенной на помехоустойчивый код, и поэтому передачи избыточных дополнительных символов для целей синхронизации не требуется.

После установления синхронизации синхронизирующую последовательность снимают с помехоустойчивого кода, не уменьшая при этом корректирующей способности кода.

В настоящее время цифровые каналы связи ультракоротковолновых и дециметровых диапазонов, в частности спутниковые каналы, характеризуются большими массивами передаваемой информации. Причем скорость обработки информации во вновь вводимых линиях связи достигает 120 Мбит/с и более. Информация в современных системах, использующих компьютеры, может передаваться по шинам данных в параллельном коде, что предъявляет повышенные требования к быстродействию кодеков помехоустойчивых кодов.

При работе кодека помехоустойчивого циклического кода в групповых трактах многоканальных систем передачи информации и при использовании методов многоосновной модуляции, при которой каждый канальный символ соответствует нескольким битам информации, сообщения также передают в параллельном коде и должна обеспечиваться высокая скорость обработки информации на передающей и приемной сторонах линии связи.

В связи с этим актуальной является задача создания кодека помехоустойчивого циклического кода, обладающего высоким быстродействием и не требующего большого количества операций при кодировании и декодировании сообщений, а также и при установлении цикловой синхронизации.

Известен кодек помехоустойчивого циклического кода, содержащий на передающей стороне формирователь информационной части кодового слова, состоящий из регистра сдвига, соединенного с сумматором по модулю два, и формирователь синхронизирующей части кодового слова, причем выходы формирователей соединены с сумматором по модулю два частей кодового слова, а на приемной стороне содержащий двоичный фильтр информационной части кодового слова, состоящий из регистра сдвига, соединенного с сумматорами по модулю два, и дешифратор (авт. св. СССР №365033, кл. Н 03 К 13/04, опубл. 1973).

Однако это устройство имеет низкое быстродействие из-за того, что для кодирования сообщения помехоустойчивым кодом требуется большое количество сдвигов входной информации, равное, по крайней мере, числу проверочных символов в кодовом слове, а для декодирования помехоустойчивого кода число сдвигов должно быть не меньше количества символов в помехоустойчивом коде.

Наиболее близким к предлагаемому устройству является кодек помехоустойчивого циклического кода (прототип), содержащий на передающей стороне формирователь информационной части кодового слова, состоящий из элементов памяти регистра сдвига и сумматора по модулю два формирователя информационной части кодового слова, формирователь синхронизирующей части кодового слова и сумматор по модулю два информационной и синхронизирующей частей кодового слова, причем входы элементов памяти регистра сдвига являются информационными входами устройства, выход последнего элемента памяти регистра сдвига и выход формирователя синхронизирующей части кодового слова соединены с входами сумматора по модулю два информационной и синхронизирующей частей кодового слова, выход которого соединен с каналом связи, выход сумматора по модулю два формирователя информационной части кодового слова подключен к входу первого элемента памяти регистра сдвига, на приемной стороне содержащий двоичный фильтр, состоящий из элементов памяти регистра сдвига двоичного фильтра и сумматора по модулю два двоичного фильтра, регистр сдвига информационной части кодового слова, дешифратор, накопитель и блок коррекции ошибок, при этом накопитель подключен к выходу сумматора по модулю два двоичного фильтра, выход накопителя соединен с дешифратором и входом блока коррекции ошибок, выход дешифратора связан с входом блока коррекции ошибок и одновременно является выходом синхронизации устройства, вход первого элемента памяти регистра сдвига двоичного фильтра соединен с каналом связи и входом сумматора по модулю два двоичного фильтра, выход последнего элемента памяти регистра сдвига двоичного фильтра связан с входом регистра сдвига информационной части кодового слова, выход которого является информационным выходом устройства (авт. св. СССР №809550, кл. Н 03 К 13/04, опубл. 1981).

Недостатком этого устройства является низкое быстродействие, обусловленное тем, что информацию при кодировании и декодировании сообщений представляют в последовательном коде и за один такт рабочей частоты устройства обрабатывают один бит исходной информации или один бит слова помехоустойчивого кода.

Цель предлагаемого изобретения - повышение быстродействия устройства за счет того, что входную и выходную информацию представляют в последовательно-параллельном коде и за один такт рабочей частоты устройства обрабатывают группу из m(m>1) бит входной информации кодирующего или декодирующего устройства.

Для достижения цели предложен кодек помехоустойчивого циклического кода, содержащий на передающей стороне формирователь информационной части кодового слова, состоящий из элементов памяти регистра сдвига и сумматора по модулю два формирователя информационной части кодового слова, формирователь синхронизирующей части кодового слова и сумматор по модулю два информационной и синхронизирующей частей кодового слова, причем входы элементов памяти регистра сдвига являются информационными входами устройства, выход последнего элемента памяти регистра сдвига и выход формирователя синхронизирующей части кодового слова соединены с входами сумматора по модулю два информационной и синхронизирующей частей кодового слова, выход которого соединен с каналом связи, выход сумматора по модулю два формирователя информационной части кодового слова подключен к входу первого элемента памяти регистра сдвига, на приемной стороне содержащий двоичный фильтр, состоящий из элементов памяти регистра сдвига двоичного фильтра и сумматора по модулю два двоичного фильтра, регистр сдвига информационной части кодового слова, дешифратор, накопитель и блок коррекции ошибок, при этом накопитель подключен к выходу сумматора по модулю два двоичного фильтра, выход накопителя соединен с дешифратором и входом блока коррекции ошибок, выход дешифратора связан с входом блока коррекции ошибок и одновременно является выходом синхронизации устройства, вход первого элемента памяти регистра сдвига двоичного фильтра соединен с каналом связи и входом сумматора по модулю два двоичного фильтра, выход последнего элемента памяти регистра сдвига двоичного фильтра связан с входом регистра сдвига информационной части кодового слова, выход которого является информационным выходом устройства. Новым является то, что на передающей стороне введены блоки вычисления проверочных частей помехоустойчивого кода формирователя информационной части кодового слова, входы которых соединены с выходами элементов памяти регистра сдвига, а выходы блоков вычисления проверочных частей помехоустойчивого кода формирователя информационной части кодового слова связаны с входами сумматора по модулю два формирователя информационной части кодового слова, на приемной стороне введены блоки вычисления проверочных частей помехоустойчивого кода двоичного фильтра, блок формирования синхронизирующей части кодового слова и блоки сумматоров по модулю два, причем входы блоков вычисления проверочных частей помехоустойчивого кода двоичного фильтра соединены с выходами элементов памяти регистра сдвига двоичного фильтра, выходы блоков вычисления проверочных частей помехоустойчивого кода двоичного фильтра связаны с входами сумматора по модулю два двоичного фильтра, выход дешифратора соединен с входом блока формирования синхронизирующей части кодового слова, выходы которого связаны с первыми входами блоков сумматоров по модулю два, вторые входы которых соединены с выходами блока коррекции ошибок, выходы блоков сумматоров по модулю два соединены с инвертирующими входами регистра сдвига информационной части кодового слова.

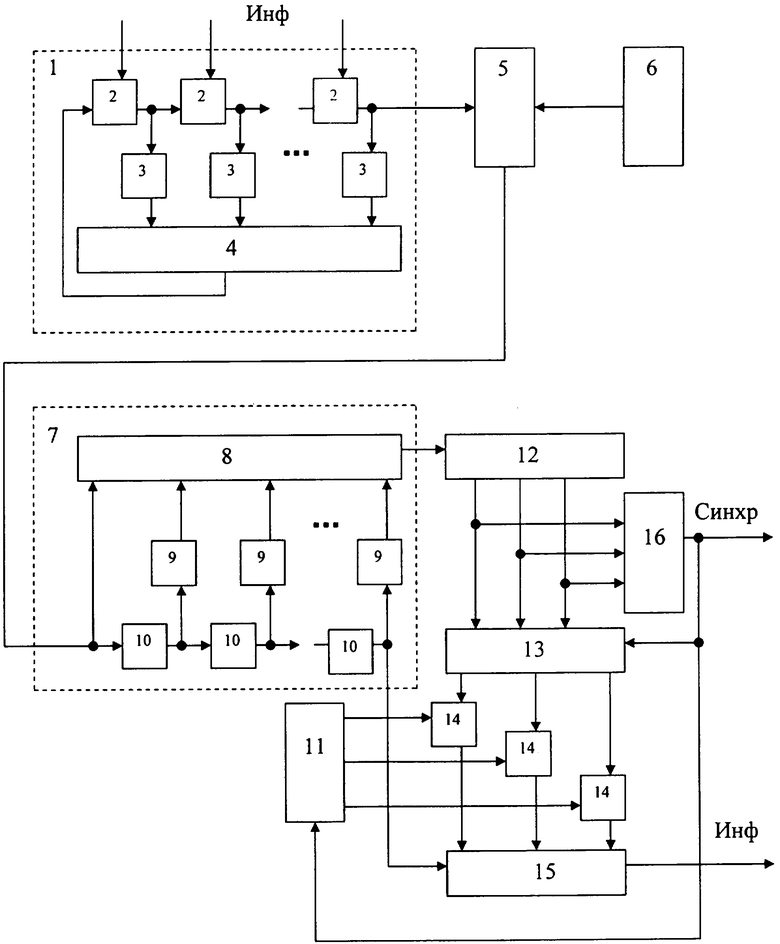

На чертеже приведена структурная схема предлагаемого устройства.

На передающей стороне кодек помехоустойчивого циклического кода (кодирующее устройство) содержит формирователь информационной части кодового слова 1, состоящий из элементов памяти регистра сдвига 2, блоков вычисления проверочных частей помехоустойчивого кода формирователя информационной части кодового слова 3, соединенных с сумматором по модулю два формирователя информационной части кодового слова 4, сумматор по модулю два информационной и синхронизирующей частей кодового слова 5 и формирователь синхронизирующей части кодового слова 6.

На приемной стороне кодек помехоустойчивого циклического кода (декодирующее устройство) содержит двоичный фильтр 7, состоящий из сумматора по модулю два двоичного фильтра 8, блоков вычисления проверочных частей кодового слова двоичного фильтра 9, соединенных с элементами памяти регистра сдвига двоичного фильтра 10, блок формирования синхронизирующей части кодового слова 11, накопитель 12, блок коррекции ошибок 13, блоки сумматоров по модулю два 14, регистр сдвига информационной части кодового слова 15, дешифратор 16.

Предлагаемое устройство работает следующим образом.

На передающей стороне формируют выходную последовательность. Для этого исходное сообщение объемом k символов вначале кодируют помехоустойчивым циклическим кодом. В результате кодирования информации получают слово циклического кода C(n,k)=с0,с1,... ,сn-1, информационная длина которого составляет k символов, а блоковая n символов.

Количество элементов памяти регистра сдвига 2 в формирователе информационной части кодового слова 1 в устройстве соответствует количеству символов k в исходной информационной последовательности, для которой формируется помехоустойчивый код. Количество разрядов в каждом элементе памяти в регистре сдвига 2 равно m и общее количество элементов памяти регистр сдвига 2 будет равно s=k/m.

Вначале исходная информационная последовательность, состоящая из k символов, поступает в параллельном коде на вход устройства, и символы этой информационной последовательности записываются в элементы памяти регистра сдвига 2.

Для описания работы устройства будем представлять исходную информацию в виде информационного полинома f(x), коэффициентами которого являются информационные символы.

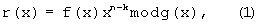

Проверочная часть r(х) слова помехоустойчивого циклического кода в полиномиальной форме записи может быть записана в виде

где g(x) - порождающий полином помехоустойчивого циклического кода степени n-k.

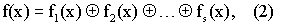

Информационная часть помехоустойчивого кода в соответствии с порядком записи ее в регистр сдвига 2, состоящий из s m разрядных групп элементов памяти, может быть представлена в форме

где fi(x) есть i-ая m разрядная компонента информационной части кода, записанная в соответствующий i-ый m разрядный элемент памяти регистра сдвига 2, s - общее число элементов памяти регистра сдвига 2 (k=m× s).

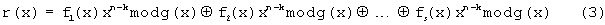

Подставляя уравнение (2) в (1), получим проверочную часть помехоустойчивого кода в виде

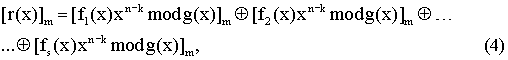

и первые (старшие) m разрядов проверочной части кода будут равны

где [ ]m обозначает первые m разрядов полинома.

Вычисления проверочных символов помехоустойчивого кода в формирователе информационной части кодового слова кодирующего устройства осуществляют в соответствии с уравнением (4).

Для этого каждая группа символов, находящаяся в элементах памяти сдвигового регистра 2, т.е. i-ая m разрядная компонента информационной части кода fi(x) подается на входы i-ого блока вычисления проверочных частей помехоустойчивого кода формирователя информационной части кодового слова 3.

Каждый блок вычисления проверочной части помехоустойчивого кода формирователя информационной части кодового слова 3 может быть выполнен в виде запоминающего устройства, например постоянного запоминающего устройства (ПЗУ). Входами блоков вычисления проверочной части кодового слова 3 являются адресные входы ПЗУ, выходами - содержимое ПЗУ, находящееся по данному адресу.

В i-ом блоке вычисления проверочной части кодового слова 3 определяют i-ое слагаемое [fi(x)n-kmod g(x)]m, входящее в уравнение (4). В i-ом блоке вычисления проверочной части кодового слова 3 (в ПЗУ) хранится постоянно одна и та же информация, а именно помещается таблица, состоящая из 2m строк. Адресным входом ПЗУ является i-ая m разрядная компонента информационной части кода fi(x), а содержимым ячейки ПЗУ с этим адресом будет [fi(х)хn-kmod g(x)]m.

Соответствующее содержимое ПЗУ формируют заранее по правилу

fi(x)→ [fi(x)xn-kmod g(x)]m

и выходом ПЗУ будет i-ая m разрядная компонента проверочной части кода, входящая в уравнение (4).

После вычисления в блоках вычисления проверочных частей помехоустойчивого кода формирователя информационной части кодового слова 3 по таблицам, записанным в ПЗУ, всех компонентов проверочной части помехоустойчивого кода [fi(x)xn-kmod g(x)]m, i=1... s, осуществляют определение первых m разрядов проверочной части кода. Для этого в соответствии с уравнением (4) компоненты проверочной части помехоустойчивого кода, сформированные на выходах блоков вычисления проверочной части кодового слова 3 суммируют в сумматоре по модулю два формирователя информационной части кодового слова 4.

Одновременно формируют постоянную циклическую синхронизирующую последовательность длины n символов. Такой последовательностью может быть любая последовательность подходящей длины с хорошими синхронизирующими свойствами, например последовательность максимальной длины (код Рида-Маллера 1-го порядка) с образующим многочленом r(х)

D(n)=d0,d1,... ,dn-1

Синхронизирующую последовательность получают в формирователе синхронизирующей части кодового слова 6. Формирователь синхронизирующей части кодового слова 6 может быть выполнен, например, в виде ПЗУ, в котором записана постоянная синхронизирующая последовательность.

Символы выходной последовательности на передающей стороне

В(n)=b0,b1,... ,bn-1

получают сложением по модулю два символов циклического помехоустойчивого кода с символами синхронизирующей последовательности:

bi=сi⊕di, i=0... n-1

Суммирование символов кода с символами синхронизирующей последовательности осуществляют на сумматоре по модулю два информационной и синхронизирующей частей кодового слова 5. С выхода этого сумматора символы выходной последовательности поступают в канал связи.

На приемной стороне принятая последовательность из-за ошибок в канале связи может отличается от передаваемой последовательности В(n).

На приемной стороне символы принятой последовательности сначала поступают в последовательно-параллельном коде группами по m символов на вход двоичного фильтра 7. При этом символы принятой последовательности записываются в первый элемент памяти регистра сдвига двоичного фильтра 10. Блоки вычисления проверочных частей кодового слова двоичного фильтра 9 и сумматор по модулю два двоичного фильтра 8 аналогичны соответствующим блокам и сумматору формирователя информационной части кодового слова 1 передающей стороны кодека. Сумматор по модулю два двоичного фильтра 8 вычисляет синдром помехоустойчивого циклического кода, т.е. сумму по модулю два проверочных символов кода, вычисленных по принятым информационным символам, и принятых проверочных символов. При поступлении безошибочного кодового слова синдром кода равен нулю и в результате вычисления синдрома будет получена преобразованная в двоичном фильтре 7 передаваемая синхронизирующая последовательность. При поступлении на вход слова с ошибками будет вычислена комбинация из некоторого множества двоичных комбинаций, соответствующая сумме ненулевого синдрома помехоустойчивого кода и преобразованной синхронизирующей последовательности.

Преобразованная синхронизирующая последовательность с наложенным синдромом с выхода сумматора по модулю два двоичного фильтра 8 далее поступает в накопитель 12.

В тоже время с выхода последнего элемента памяти регистра сдвига двоичного фильтра 10 информационная последовательность поступает на вход регистра сдвига информационной части кодового слова 15.

К накопителю 12 подключен дешифратор 16, настроенный на структуру синхронизирующей последовательности с учетом синдрома кода, соответствующего комбинации ошибок допустимой кратности. При этом допустимая кратность ошибок определяется исправляющей способностью помехоустойчивого кода или минимальным кодовым расстоянием помехоустойчивого кода. Выбор подмножества дешифрируемых ошибок проводится с учетом эффекта размножения канальных ошибок, вызванных прохождением последовательности через двоичный фильтр 7.

Срабатывание дешифратора 16 свидетельствует о приеме синхронизирующей последовательности с допустимой кратностью ошибок и определенным фазовым сдвигом. При этом в регистре сдвига информационной части кодового слова 15 будут находиться, с тем же фазовым сдвигом информационные символы помехоустойчивого циклического кода.

Место расположения ошибок в символах кода определяется (локализуется) блоком коррекции ошибок 13 при распознавании соответствующей комбинации синдрома кода с наложенной синхронизирующей последовательностью. Блок коррекции ошибок 13 может быть выполнен, например, в виде постоянного запоминающего устройства (ПЗУ), в которое записаны таблицы ошибок. Адресным входом этого ПЗУ является двоичная комбинация, соответствующая комбинации синдрома с наложенной синхронизирующей последовательностью и с учетом определенного фазового сдвига, а выходом ПЗУ - соответствующая двоичная комбинация ошибок в информационных символах кодового слова.

Это позволяет произвести исправление ошибочных знаков в регистре сдвига информационной части кодового слова 15.

Одновременно сигнал с выхода дешифратора 16 поступает на блок формирования синхронизирующей части кодового слова 11. При этом с выхода этого блока синхронизирующая последовательность с определенным фазовым сдвигом поступает на входы блоков суммирования по модулю два 14, на другие входы которых с выхода блока коррекции ошибок 13 подается двоичная комбинация, соответствующая расположению ошибок в информационных символах кодового слова.

Исправление ошибок в регистре сдвига информационной части кодового слова 15 и снятие синхронизирующей последовательности осуществляется по сигналам с выходов блоков сумматоров по модулю два 14 путем инверсии соответствующих разрядов в принятых символах кодового слова.

В момент появления сигнала с выхода дешифратора 16 в регистре сдвига информационной части кодового слова 15 будут находиться информационные символы помехоустойчивого циклического кода. Поэтому сигнал с выхода дешифратора 16 является синхронизирующим сигналом устройства, свидетельствующим о том, что декодированная информация с выхода регистра сдвига информационной части кодового слова 15 поступает на выход кодека и может считываться получателем информации.

Отметим, что наложение синхронизирующей последовательности на кодовые слова придает словам помехоустойчивого кода свойство самосинхронизируемости и не требует введения дополнительной избыточности в помехоустойчивом коде для целей цикловой синхронизации.

Предлагаемое устройство может быть реализовано как аппаратным, так и программно-аппаратным путем. В последнем случае использование отдельных элементов ЭВМ (сумматоров, запоминающих устройств, регистров) позволяет получить существенный выигрыш в объеме используемого оборудования.

В предполагаемом изобретении, в отличие от известного устройства, обработка информации осуществляется в последовательно-параллельном коде, причем за один такт обрабатывается не один символ помехоустойчивого циклического кода, как в прототипе, а группа из m (m>1) символов, что повышает быстродействие устройства примерно в m раз.

Достигаемым техническим результатом предлагаемого кодека помехоустойчивого циклического кода является повышение его быстродействия.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2254676C2 |

| КОДЕК ЦИКЛИЧЕСКОГО ПОМЕХОУСТОЙЧИВОГО КОДА | 2002 |

|

RU2212101C1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2302701C1 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| УСТРОЙСТВО АДАПТИВНОЙ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2259638C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2001 |

|

RU2197788C2 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

Изобретение относится к области техники связи, в частности к системам телеизмерения и телеуправления для передачи информации без предварительного фазирования. Техническим результатом является повышение быстродействия устройства. Технический результат достигается тем, что кодек помехоустойчивого циклического кода на передающей стороне содержит формирователь информационной части кодового слова, состоящий из элементов памяти регистра сдвига, блоков вычисления проверочных частей помехоустойчивого кода формирователя информационной части кодового слова и сумматора по модулю два формирователя информационной части кодового слова, формирователь синхронизирующей части кодового слова и сумматор по модулю два информационной и синхронизирующей частей кодового слова, на приемной стороне содержит двоичный фильтр, состоящий из элементов памяти регистра сдвига двоичного фильтра, блоков вычисления проверочных частей помехоустойчивого кода двоичного фильтра и сумматора по модулю два двоичного фильтра, регистр сдвига информационной части кодового слова, дешифратор, накопитель, блок коррекции ошибок, блок формирования синхронизирующей части кодового слова и блоки сумматоров по модулю два. 1 ил.

Кодек помехоустойчивого циклического кода, содержащий на передающей стороне формирователь информационной части кодового слова, состоящий из элементов памяти регистра сдвига и сумматора по модулю два формирователя информационной части кодового слова, формирователь синхронизирующей части кодового слова и сумматор по модулю два информационной и синхронизирующей частей кодового слова, причем входы элементов памяти регистра сдвига являются информационными входами устройства, выход последнего элемента памяти регистра сдвига и выход формирователя синхронизирующей части кодового слова соединены с входами сумматора по модулю два информационной и синхронизирующей частей кодового слова, выход которого соединен с каналом связи, выход сумматора по модулю два формирователя информационной части кодового слова подключен к входу первого элемента памяти регистра сдвига, на приемной стороне содержащий двоичный фильтр, состоящий из элементов памяти регистра сдвига двоичного фильтра и сумматора по модулю два двоичного фильтра, регистр сдвига информационной части кодового слова, дешифратор, накопитель и блок коррекции ошибок, при этом накопитель подключен к выходу сумматора по модулю два двоичного фильтра, выход накопителя соединен с дешифратором и входом блока коррекции ошибок, выход дешифратора связан с входом блока коррекции ошибок и одновременно является выходом синхронизации устройства, вход первого элемента памяти регистра сдвига двоичного фильтра соединен с каналом связи и входом сумматора по модулю два двоичного фильтра, выход последнего элемента памяти регистра сдвига двоичного фильтра связан с входом регистра сдвига информационной части кодового слова, выход которого является информационным выходом устройства, отличающийся тем, что на передающей стороне введены блоки вычисления проверочных частей помехоустойчивого кода формирователя информационной части кодового слова, входы которых соединены с выходами элементов памяти регистра сдвига, а выходы блоков вычисления проверочных частей помехоустойчивого кода формирователя информационной части кодового слова связаны с входами сумматора по модулю два формирователя информационной части кодового слова, на приемной стороне введены блоки вычисления проверочных частей помехоустойчивого кода двоичного фильтра, блок формирования синхронизирующей части кодового слова и блоки сумматоров по модулю два, причем входы блоков вычисления проверочных частей помехоустойчивого кода двоичного фильтра соединены с выходами элементов памяти регистра сдвига двоичного фильтра, выходы блоков вычисления проверочных частей помехоустойчивого кода двоичного фильтра связаны с входами сумматора по модулю два двоичного фильтра, выход дешифратора соединен с входом блока формирования синхронизирующей части кодового слова, выходы которого связаны с первыми входами блоков сумматоров по модулю два, вторые входы которых соединены с выходами блока коррекции ошибок, выходы блоков сумматоров по модулю два соединены с инвертирующими входами регистра сдвига информационной части кодового слова.

| Декодирующее устройство | 1979 |

|

SU809550A1 |

| Декодирующее устройство линейного циклического кода | 1990 |

|

SU1718386A1 |

| Кодирующее устройство | 1983 |

|

SU1239868A1 |

| СИСТЕМА ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ С ИСПРАВЛЕНИЕМ ОШИБОК | 1991 |

|

RU2007042C1 |

| СПОСОБ КОЛИЧЕСТВЕННОГО ОПРЕДЕЛЕНИЯ МИКРООРГАНИЗМОВ В ВЕЩЕСТВАХ | 0 |

|

SU200124A1 |

| US 4698813 A1, 06.10.1987 | |||

| US 5132975 A1, 21.07.1992. | |||

Авторы

Даты

2005-04-27—Публикация

2003-10-06—Подача