Изобретение относится к области техники связи и может быть использовано в системах передачи данных, а также в системах телеизмерения и телеуправления для передачи информации без предварительного фазирования.

Кодек, или кодирующее и декодирующее устройства, описанные в настоящей заявке, применяют для кодирования и декодирования помехоустойчивых линейных циклических кодов, а также для цикловой синхронизации этих помехоустойчивых кодов. В предлагаемом устройстве в канал связи передают последовательность символов, равную сумме символов помехоустойчивого кода и символов синхронизирующей последовательности, а также последовательность символов, полученную при суммировании символов рекуррентных продолжений помехоустойчивого кода и символов синхронизирующей последовательности. Цикловую синхронизацию осуществляют с помощью синхронизирующей последовательности, наложенной на помехоустойчивый код, и поэтому передачи избыточных дополнительных символов для целей синхронизации не требуется.

После установления синхронизации помехоустойчивого кода, синхронизирующую последовательность снимают с помехоустойчивого кода, не уменьшая этим корректирующей способности кода.

Наиболее эффективно предлагаемое устройство может быть применено в каналах связи с группированием ошибок, поскольку декодирование осуществляют в скользящем окне приема, а за пределами окна приема допускают возникновение произвольного числа ошибок в принятой последовательности, не приводящих к трансформации помехоустойчивого кода. Например, предлагаемое устройство может использоваться в каналах связи с многолучевым распространением сигнала. При этом сообщение будет принято, если длительность времени между соседними замираниями сигнала, вызванная интерференцией лучей распространения сигнала, не меньше длительности скользящего окна приема. Под скользящим окном приема в данной заявке будем понимать последовательность, состоящую из n подряд идущих символов помехоустойчивого кода, с учетом циклических перестановок символов кода, где n - постоянная величина, равная блоковой длине помехоустойчивого кода.

Предлагаемое изобретение направлено на решение актуальной задачи повышения помехоустойчивости приема циклического кода при работе в каналах связи с высоким уровнем помех.

Известен кодек помехоустойчивого циклического кода, содержащий на передающей стороне формирователь информационной части кодового слова, состоящий из регистра сдвига, соединенного с сумматором по модулю два, формирователь синхронизирующей части кодового слова и сумматор по модулю два частей кодового слова, причем выходы формирователей соединены с сумматором по модулю два частей кодового слова, а на приемной стороне содержащий двоичный фильтр информационной части кодового слова, состоящий из регистра сдвига, соединенного с сумматорами по модулю два, и дешифратор [1].

Однако это устройство имеет низкую помехоустойчивость, так как для декодирования помехоустойчивого кода необходим неискаженный прием символов кода.

Наиболее близким к предлагаемому устройству является кодек помехоустойчивого циклического кода (прототип), содержащий на передающей стороне формирователь информационной части кодового слова, состоящий из регистра сдвига, соединенного с сумматором по модулю два информационной части кодового слова, формирователь синхронизирующей части кодового слова и сумматор по модулю два частей кодового слова, причем вход регистра сдвига формирователя информационной части кодового слова является информационным входом устройства, а выход регистра сдвига формирователя информационной части кодового слова и выход формирователя синхронизирующей части кодового слова соединены со входами сумматора по модулю два частей кодового слова, выход которого соединен с каналом связи, на приемной стороне содержащий двоичный фильтр, состоящий из регистра сдвига двоичного фильтра и подключенных к нему сумматора по модулю два синхронизирующей части кодового слова двоичного фильтра и сумматора по модулю два информационной части кодового слова двоичного фильтра, блок формирования информационной части кодового слова, состоящий из регистра сдвига блока формирования информационной части кодового слова с подключенным к нему сумматором по модулю два блока формирования информационной части кодового слова, дешифратор синхронизирующей последовательности, накопитель, блок коррекции ошибок и коммутатор, при этом накопитель подключен к выходу сумматора по модулю два информационной части кодового слова двоичного фильтра, выход накопителя соединен с дешифратором синхронизирующей последовательности и входом блока коррекции ошибок, выходы которого соединены с соответствующими инвертирующими входами регистра сдвига блока формирования информационной части кодового слова, выход которого является информационным выходом устройства, вход регистра сдвига блока формирования информационной части кодового слова через коммутатор подключен к выходу сумматора по модулю два синхронизирующей части кодового слова двоичного фильтра, выход дешифратора синхронизирующей последовательности соединен с управляющим входом коммутатора и входом блока коррекции ошибок [2].

Недостатком этого устройства является невысокая помехоустойчивость, поскольку прием сообщения возможен лишь при наличии в принятой последовательности ошибок, кратность которых не выше исправляющей способности кода.

Цель предлагаемого изобретения - повышение помехоустойчивости приема сообщения за счет введения дешифратора сдвига информационной части кодового слова и элемента задержки, что позволяет осуществлять декодирование помехоустойчивого кода в скользящем окне приема, а за пределами скользящего окна возможно возникновение произвольного количества ошибок в принятой последовательности, в том числе превышающее корректирующую способность помехоустойчивого кода.

Для достижения цели предложен кодек помехоустойчивого циклического кода, содержащий на передающей стороне формирователь информационной части кодового слова, состоящий из регистра сдвига, соединенного с сумматором по модулю два информационной части кодового слова, формирователь синхронизирующей части кодового слова и сумматор по модулю два частей кодового слова. Причем вход регистра сдвига формирователя информационной части кодового слова является информационным входом устройства, а выход регистра сдвига формирователя информационной части кодового слова и выход формирователя синхронизирующей части кодового слова соединены с входами сумматора по модулю два частей кодового слова, выход которого соединен с каналом связи, на приемной стороне содержащий двоичный фильтр, состоящий из регистра сдвига двоичного фильтра и параллельно подключенных к нему сумматора по модулю два синхронизирующей части кодового слова двоичного фильтра и сумматора по модулю два информационной части кодового слова двоичного фильтра, блок формирования информационной части кодового слова, состоящий из регистра сдвига блока формирования информационной части кодового слова с подключенным к нему сумматором по модулю два блока формирования информационной части кодового слова, дешифратор синхронизирующей последовательности, накопитель, блок коррекции ошибок и коммутатор. При этом накопитель подключен к выходу сумматора по модулю два информационной части кодового слова двоичного фильтра, выход накопителя соединен с дешифратором синхронизирующей последовательности и входом блока коррекции ошибок, выходы которого соединены с соответствующими инвертирующими входами регистра сдвига блока формирования информационной части кодового слова, выход которого является информационными инвертирующими входами регистра сдвига блока формирования информационной части кодового слова, выход которого является информационным выходом устройства, вход регистра сдвига блока формирования информационной части кодового слова через коммутатор подключен к выходу сумматора по модулю два синхронизирующей части кодового слова двоичного фильтра, выход дешифратора синхронизирующей последовательности соединен с управляющим входом коммутатора и входом блока коррекции ошибок. Новым является то, что на приемной стороне введены дешифратор сдвига информационной части кодового слова и элемент задержки. При этом выходы накопителя соединены с входами дешифратора сдвига информационной части кодового слова, выход которого подключен к входу элемента задержки, выход которого является вторым управляющим входом коммутатора и синхронизирующим выходом устройства.

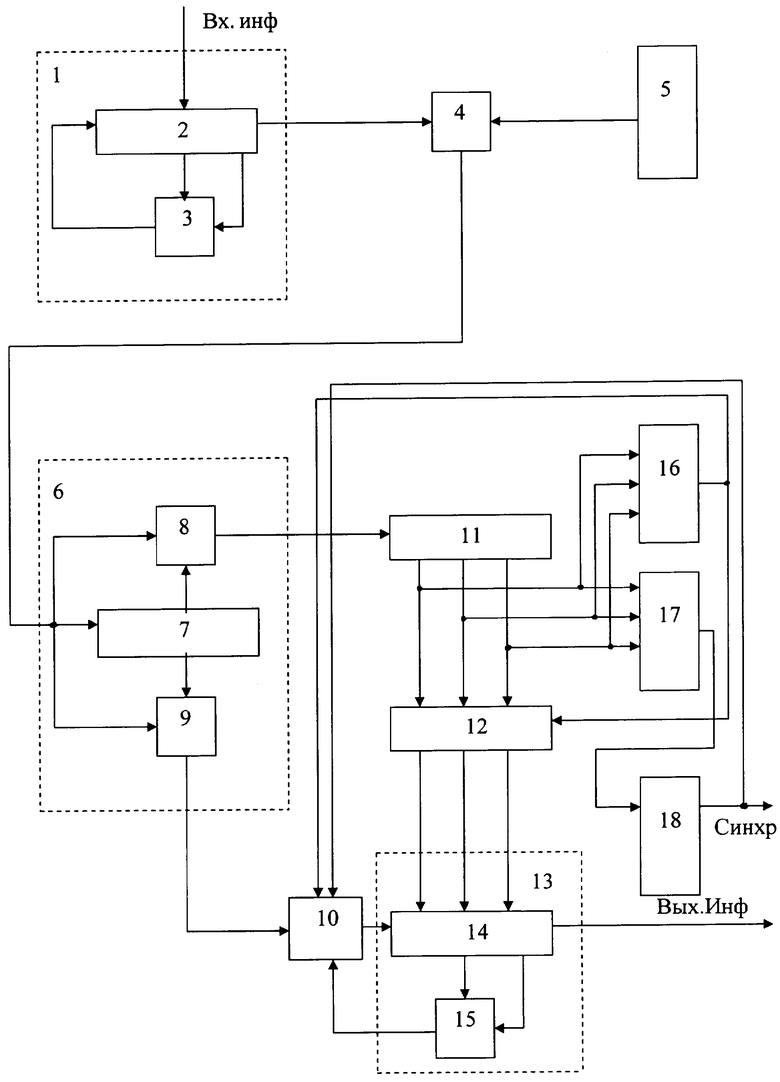

На чертеже приведена структурная схема предлагаемого устройства. На передающей стороне кодек помехоустойчивого циклического кода (кодирующее устройство) содержит формирователь информационной части кодового слова 1, состоящий из регистра сдвига 2, соединенного с сумматором по модулю два информационной части кодового слова 3, сумматор по модулю два информационной и синхронизирующей частей кодового слова 4 и формирователь синхронизирующей части кодового слова 5.

На приемной стороне кодек помехоустойчивого циклического кода (декодирующее устройство) содержит двоичный фильтр 6, состоящий из регистра сдвига двоичного фильтра 7, соединенного с сумматором по модулю два информационной части кодового слова двоичного фильтра 8 и сумматором по модулю два синхронизирующей части кодового слова двоичного фильтра 9, коммутатор 10, накопитель 11, блок коррекции ошибок 12, блок формирования информационной части кодового слова 13, состоящий из регистра сдвига блока формирования информационной части кодового слова 14 с подключенным к нему сумматором по модулю два блока формирования информационной части кодового слова 15, дешифратор синхронизирующей последовательности 16, дешифратор сдвига информационной части кодового слова 17 и элемент задержки 18.

Предлагаемое устройство работает следующим образом.

На передающей стороне формируют выходную последовательность. Для этого исходное сообщение объемом k символов вначале кодируют помехоустойчивым циклическим кодом. В результате кодирования информации получают слово помехоустойчивого циклического кода C(n,k)=a0,a1,...,an-1, информационная длина которого составляет k символов, а блоковая n символов. Поскольку код является циклическим, существует рекуррентное соотношение, с помощью которого можно получить все проверочные символы кода

Далее слово циклического кода C(n,k) рекуррентно продолжают с помощью того же соотношения до длины n1≥n и при этом, в силу цикличности помехоустойчивого кода, получают последовательность, состоящую из тех же символов кода

K(n1,k)=a0,a1,...,an-1, a0,a1,...,an-1,..., a0,a1,...,

т.е. получают код с повторением (двукратным или многократным повторением). Свойством такого кода, в отличие от обычного кода с повторением, будет то, что любая комбинация символов в скользящем окне длины n символов будет словом помехоустойчивого кода C(n,k).

На передающей стороне линии связи слово помехоустойчивого циклического кода получают с помощью формирователя информационной части кодового слова 1. С этой целью в цепи обратной связи регистра сдвига 2 включен сумматор по модулю два 3. Отводы регистра сдвига 2 на сумматор по модулю два 3 соответствуют ненулевым коэффициентам проверочного многочлена помехоустойчивого циклического кода h(x) и в процессе сдвигов информации в регистре сдвига 2 осуществляют вычисление проверочных символов кода в соответствии с рекуррентным соотношением (1).

В начале работы кодека k бит исходной информации, поступающей по информационному входу устройства, записывают в k разрядный регистр сдвига 2. Затем в течение n1 тактов, где n1 - длина выходной последовательности, осуществляют сдвиг этой информации. При этом в течение первых k тактов на выходе регистра сдвига 2 получают символы исходной информации, в течение последующих n-k тактов - проверочные символы кода, а в течение оставшихся n1-n тактов - символы рекуррентного продолжения кода.

Одновременно формируют постоянную циклическую синхронизирующую последовательность длины n символов. Такой последовательностью может быть любая последовательность подходящей длины с хорошими синхронизирующими свойствами, например, последовательность максимальной длины (код Рида - Маллера 1-го порядка) с проверочным многочленом r(x). Эту последовательность рекуррентно продолжают до длины n1 символов

D(n1)=d0,d1,...,dn-1, d0,d1,...,dn-1,..., d0,d1,...

Синхронизирующую последовательность получают из формирователя синхронизирующей части кодового слова 5. Формирователь синхронизирующей части кодового слова 5 может быть выполнен, например, в виде регистра сдвига, имеющего n1 разрядов, в который по сигналу начальной установки записывают постоянную синхронизирующую последовательность (разряды регистра сдвига по сигналу начальной установки переводятся в определенное состояние).

Символы выходной последовательности на передающей стороне

B(n1)=b0,b1,...,bn-1, b0,b1,...,bn-1,..., b0,b1,...

получают сложением по модулю два символов циклического помехоустойчивого кода с символами синхронизирующей последовательности:

bi=ci⊕di i=0...n-1

Суммирование символов кода с символами синхронизирующей последовательности осуществляют на сумматоре по модулю два информационной и синхронизирующей частей кодового слова 4. С выхода этого сумматора символы выходной последовательности поступают в канал связи.

На приемной стороне принятая последовательность, из-за ошибок в канале связи, в общем случае отличается от передаваемой последовательности B(n1) и может быть записана в виде:

На приемной стороне символы принятой последовательности сначала поступают на вход двоичного фильтра 6, который содержит регистр сдвига двоичного фильтра 7, сумматор по модулю два информационной части кодового слова двоичного фильтра 8 и сумматор по модулю два синхронизирующей части кодового слова двоичного фильтра 9. Сумматор по модулю два информационной части кодового слова двоичного фильтра 8 включен в соответствии с проверочным многочленом помехоустойчивого кода h(x), т.е. отводы регистра сдвига двоичного фильтра 7 на сумматор по модулю два информационной части кодового слова двоичного фильтра 8 соответствуют ненулевым коэффициентам проверочного многочлена помехоустойчивого циклического кода h(x). Аналогично, сумматор по модулю два синхронизирующей части кодового слова двоичного фильтра 9 включен в соответствии с проверочным многочленом синхронизирующей последовательности r(х). При этом сумматор по модулю два информационной части кодового слова двоичного фильтра 8 вычисляет синдром помехоустойчивого циклического кода, т.е. сумму по модулю два проверочных символов кода, вычисленных по принятым информационным символам, и принятых проверочных символов. При поступлении на вход двоичного фильтра 6 безошибочного кодового слова, синдром кода равен нулю, и в результате вычисления синдрома будет получена преобразованная в двоичном фильтре 6 передаваемая синхронизирующая последовательность. При поступлении на вход двоичного фильтра 6 кодового слова с ошибками будет вычислена комбинация из некоторого множества двоичных комбинаций, соответствующая сумме ненулевого синдрома помехоустойчивого кода и преобразованной синхронизирующей последовательности.

Преобразованная синхронизирующая последовательность с наложенным синдромом помехоустойчивого кода с выхода сумматора по модулю два информационной части кодового слова двоичного фильтра 8 далее поступает в накопитель 11.

Аналогичным образом сумматор по модулю два синхронизирующей части кодового слова двоичного фильтра 9 вычисляет синдром синхронизирующей последовательности и, в результате, получают символы помехоустойчивого кода, т.е. информационную последовательность с наложенным синдромом синхронизирующей последовательности.

С выхода сумматора по модулю два синхронизирующей части кодового слова двоичного фильтра 9 эта информационная последовательность поступает через коммутатор 10 на вход блока формирования информационной части кодового слова 13. При этом символы кода с определенным фазовым сдвигом, определяемым положением скользящего окна приема в принятой последовательности, записывают в регистр сдвига блока формирования информационной части кодового слова 14.

К накопителю 11 подключен дешифратор синхронизирующей последовательности 16, настроенный на структуру синхронизирующей последовательности с учетом синдрома кода, соответствующего комбинации ошибок допустимой кратности. При этом допустимая кратность ошибок определяется исправляющей способностью помехоустойчивого кода или минимальным кодовым расстоянием помехоустойчивого кода. Выбор подмножества дешифрируемых ошибок проводится с учетом эффекта размножения канальных ошибок, вызванных прохождением последовательности через двоичный фильтр 6.

Срабатывание дешифратора синхронизирующей последовательности 16 свидетельствует о приеме синхронизирующей последовательности с допустимой кратностью ошибок. При этом в регистре сдвига блока формирования информационной части кодового слова 14 будут находиться, с определенным фазовым сдвигом относительно информационных символов кода, символы помехоустойчивого циклического кода.

Место расположения ошибок в символах кода локализуется блоком коррекции ошибок 12 при определении комбинации синдрома кода с наложенной синхронизирующей последовательностью. Блок коррекции ошибок 12 может быть выполнен, например, в виде постоянного запоминающего устройства (ПЗУ), в которое записаны двоичные комбинации ошибок (таблицы ошибок). Адресным входом этого ПЗУ является двоичная комбинация, соответствующая комбинации синдрома с наложенной синхронизирующей последовательностью, а выходом - соответствующая двоичная комбинация ошибок в символах кодового слова.

Это позволяет произвести исправление ошибочных знаков в регистре сдвига блока формирования информационной части кодового слова 14. Исправление ошибок в регистре сдвига блока формирования информационной части кодового слова 14 осуществляют путем инверсии соответствующих разрядов в принятых символах кодового слова.

Одновременно по сигналу с дешифратора синхронизирующей последовательности 16 срабатывает коммутатор 10, и выход сумматора по модулю два блока формирования информационной части кодового слова 15 через коммутатор 10 соединяется с входом регистра сдвига блока формирования информационной части кодового слова 14. Блок формирования информационной части кодового слова 13 переводится в режим автономной генерации информационной части кодового слова.

Прием символов из канала связи осуществляют скользящим окном, поэтому символы кодового слова в регистре сдвига блока формирования информационной части кодового слова 14 могут иметь определенный фазовый сдвиг относительно информационных символов помехоустойчивого кода. Величину этого фазового сдвига определяют по величине сдвига преобразованной синхронизирующей последовательности, находящейся в накопителе 11. К накопителю 11 подключен дешифратор сдвига информационной части кодового слова 17, заранее настроенный на структуру синхронизирующей последовательности с учетом синдрома кода, соответствующего комбинации ошибок допустимой кратности. При срабатывании дешифратора сдвига информационной части кодового слова 17, величина фазового сдвига с выхода этого дешифратора поступает на вход элемента задержки 18 и задает временную задержку, необходимую для получения в регистре сдвига блока формирования информационной части кодового слова 14 информационных символов кода. Элемент задержки 18 может быть выполнен, например, в виде реверсивного счетчика, состояние которого устанавливается сигналом с выхода дешифратора сдвига информационной части кодового слова 17. При возвращении счетчика в исходное состояние сигнал нулевого состояния счетчика будет соответствовать величине задержки времени с момента установки счетчика сигналом с дешифратора до момента времени перехода счетчика в нулевое состояние.

В момент появления сигнала с выхода элемента задержки 18, в регистре сдвига блока формирования информационной части кодового слова 14 будут находиться информационные символы помехоустойчивого циклического кода. Сигнал с выхода элемента задержки 18 является синхронизирующим сигналом устройства, свидетельствующим о том, что декодированная информация с выхода регистра сдвига блока формирования информационной части кодового слова 14 поступает на выход кодека и может считываться получателем информации. Этот же сигнал возвращает коммутатор 10 в исходное состояние приемная сторона кодека готова к приему следующего сообщения.

Отметим, что наложение синхронизирующей последовательности на кодовые слова в сумматоре по модулю два информационной и синхронизирующей частей кодового слова 4 придает словам помехоустойчивого кода свойство самосинхронизируемости и не требует введения дополнительной избыточности для целей цикловой синхронизации.

В предлагаемом изобретении, в отличие от известного устройства, символы помехоустойчивого циклического кода рекуррентно продолжены, прием кодового слова осуществляют скользящим окном, причем в скользящем окне приема допускают количество ошибок в пределах корректирующей способности кода, а за пределами окна возможно возникновение произвольного числа ошибок в принятой последовательности, не приводящее к трансформации помехоустойчивого кода. Поэтому предлагаемое устройство позволяет осуществлять прием сообщений в каналах связи с независимыми и группирующимися ошибками при более высоком уровне помех.

Достигаемым техническим результатом предлагаемого кодека помехоустойчивого циклического кода является повышение его помехоустойчивости.

Источники информации:

1. Авторское свидетельство СССР №365033, кл. Н 03 К 13/04, опубл. 21.11.73.

2. Авторское свидетельство СССР №809550, кл. Н 03 К 13/04, опубл. 28.02.81.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2251210C1 |

| КОДЕК ЦИКЛИЧЕСКОГО ПОМЕХОУСТОЙЧИВОГО КОДА | 2002 |

|

RU2212101C1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2302701C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С ИНТЕГРИРОВАННЫМИ МЯГКИМИ И ЖЕСТКИМИ РЕШЕНИЯМИ | 2011 |

|

RU2450464C1 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

| Способ кодовой цикловой синхронизации для каскадного кода Рида-Соломона и Боуза-Чоудхури-Хоквингема [РС(32,16,17), БЧХ(31,16,7)] при одновременном применении жестких и мягких решений | 2020 |

|

RU2747623C1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

Изобретение относится к области техники связи, в частности к системам передачи данных, а также к системам телеизмерений и телеуправления. Кодек помехоустойчивого циклического кода содержит на передающей стороне формирователь информационной части кодового слова (ИЧКС), выход которого и выход формирователя синхронизирующей части кодового слова (СЧКС)соединены с входами сумматора по модулю два, на приемной стороне - двоичный фильтр, выход ИЧКС которого подключен к накопителю, соединенному с дешифратором синхронизирующей последовательности и блоком коррекции ошибок, выходы которого соединены с соответствующими инвертирующими входами формирователя ИЧКС, выход которого является информационным выходом устройства, выход СЧКС двоичного фильтра через коммутатор подключен ко входу блока формирования ИЧКС, выход дешифратора синхронизирующей последовательности соединен с управляющим входом коммутатора и входом блока коррекции ошибок, причем на приемной стороне выходы накопителя соединены с входами дешифратора сдвига информационной части кодового слова, выход которого подключен к входу элемента задержки, выход которого является вторым управляющим входом коммутатора и синхронизирующим выходом устройства. Техническим результатом изобретения является повышение помехоустойчивости. 1 ил.

Кодек помехоустойчивого циклического кода, содержащий на передающей стороне формирователь информационной части кодового слова, выход которого и выход формирователя синхронизирующей части кодового слова соединены с входами сумматора по модулю два информационной и синхронизирующей частей кодового слова, выход которого соединен с каналом связи, вход формирователя информационной части кодового слова является информационным входом устройства, на приемной стороне - двоичный фильтр, выход информационной части кодового слова которого подключен к накопителю, соединенному с дешифратором синхронизирующей последовательности и блоком коррекции ошибок, выходы которого соединены с соответствующими инвертирующими входами блока формирования информационной части кодового слова, выход которого является информационным выходом устройства, выход синхронизирующей части кодового слова двоичного фильтра через коммутатор подключен ко входу блока формирования информационной части кодового слова, выход дешифратора синхронизирующей последовательности соединен с управляющим входом коммутатора и входом блока коррекции ошибок, отличающийся тем, что на приемной стороне введены дешифратор сдвига информационной части кодового слова и элемент задержки, при этом выходы накопителя соединены с входами дешифратора сдвига информационной части кодового слова, выход которого подключен к входу элемента задержки, выход которого является вторым управляющим входом коммутатора и синхронизирующим выходом устройства.

| Декодирующее устройство | 1979 |

|

SU809550A1 |

| СИСТЕМА ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ С ИСПРАВЛЕНИЕМ ОШИБОК | 1991 |

|

RU2007042C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СЛОВАРЕЙ НЕЛИНЕЙНЫХ РЕКУРРЕНТНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1989 |

|

RU2024053C1 |

| US 6049903 A, 11.04.2000 | |||

| Устройство для обработки посевного материала | 1982 |

|

SU1152540A1 |

Авторы

Даты

2005-06-20—Публикация

2003-08-11—Подача