Изобретение относится к области элек- трорадиоизмерений и может быть использовано для измерения сдвига фаз сигналов, в составе которых присутствует постоянная составляющая, за малое время измерения, в том числе и за время измерения меньшее периода сигнала, а также некратное периоду сигнала, с повышенной точностью и помехоустойчивостью.

Целью изобретения является повышение точности и быстродействия измерения фазового сдвига при наличии в сигнале постоянной составляющей.

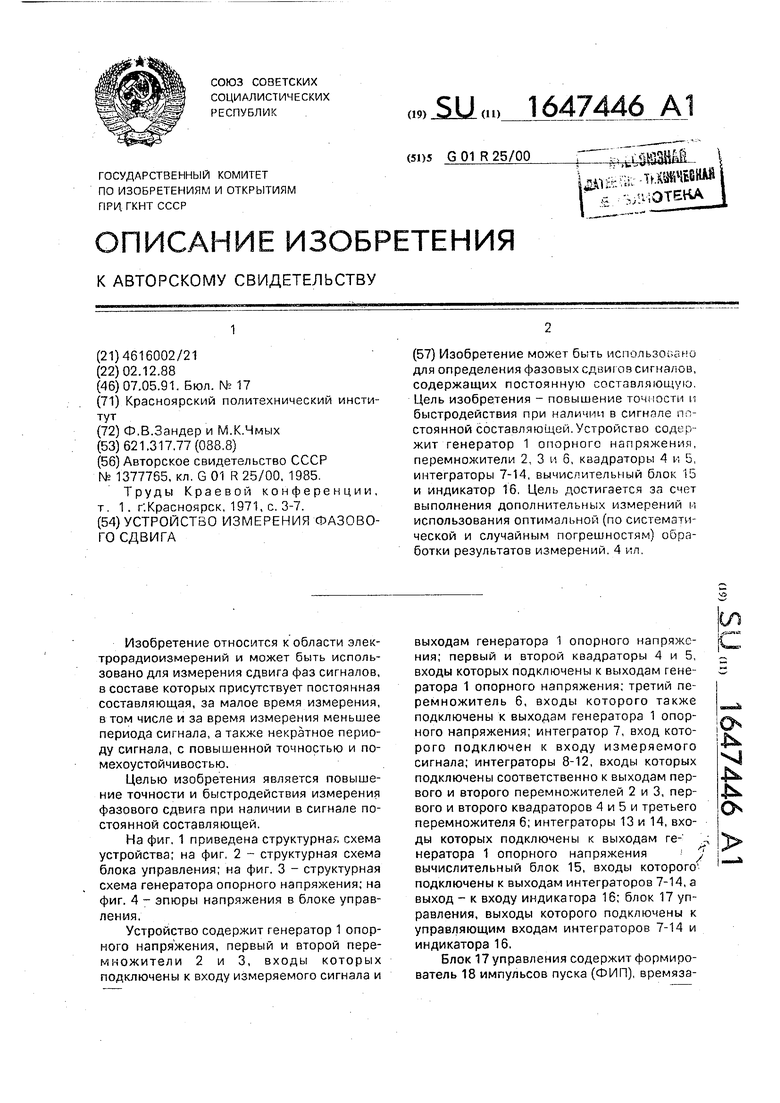

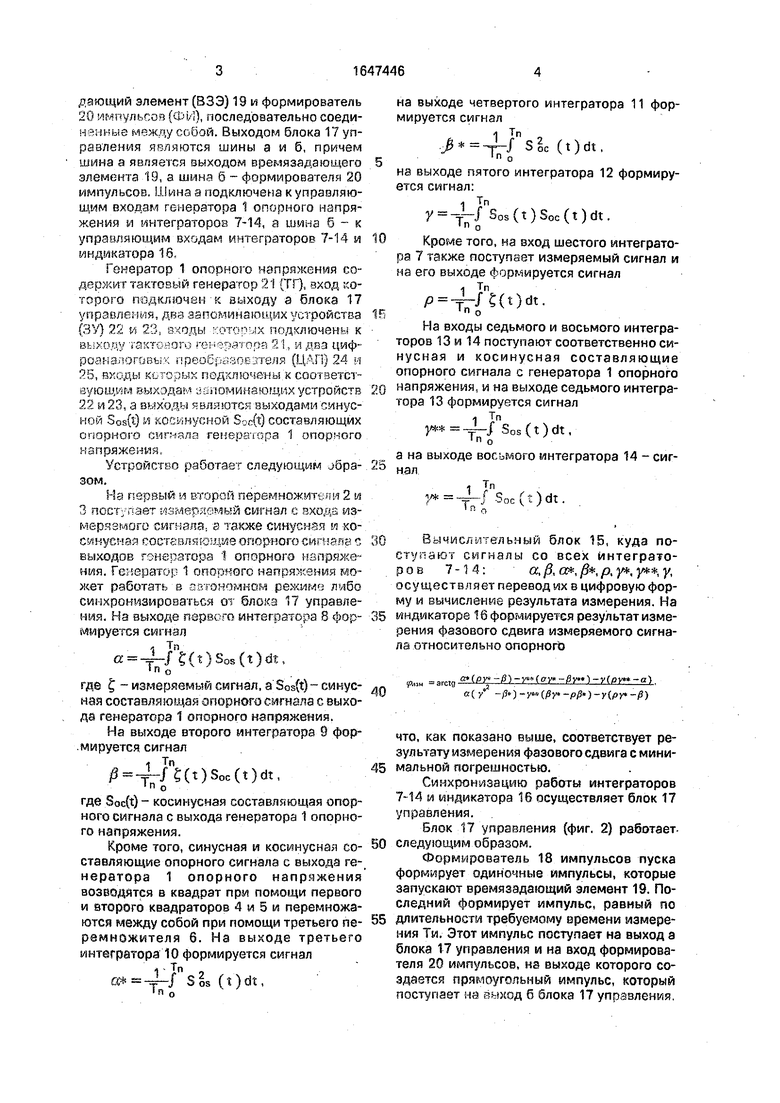

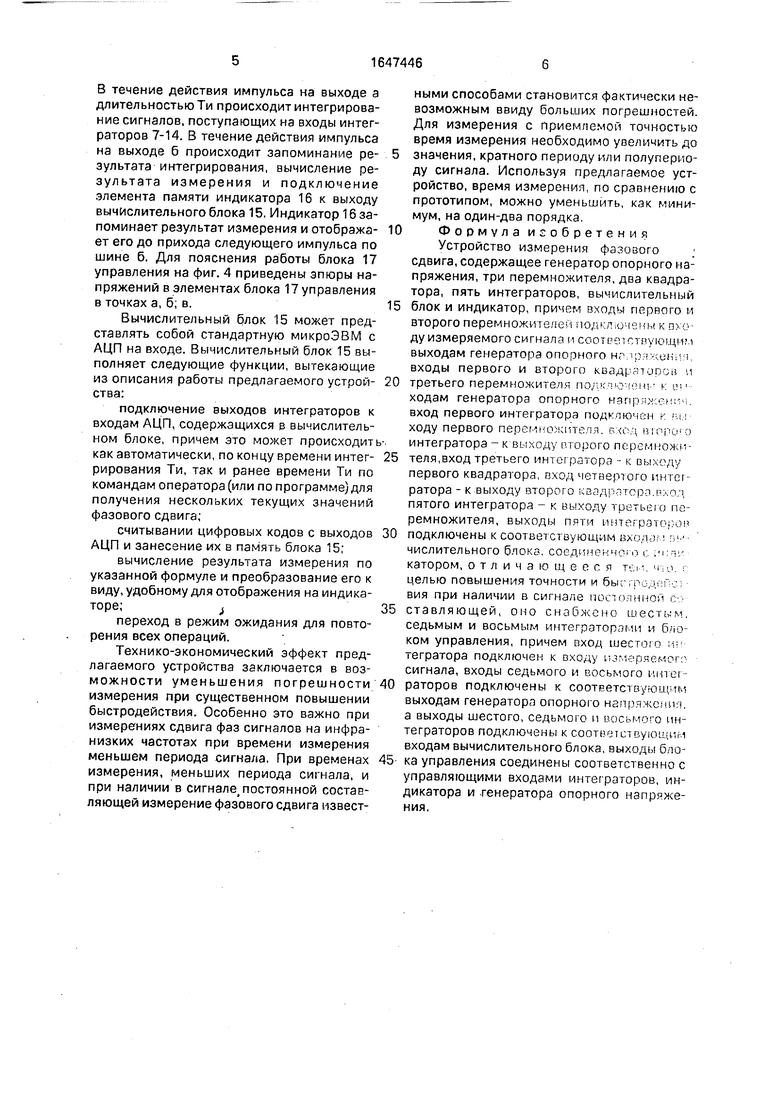

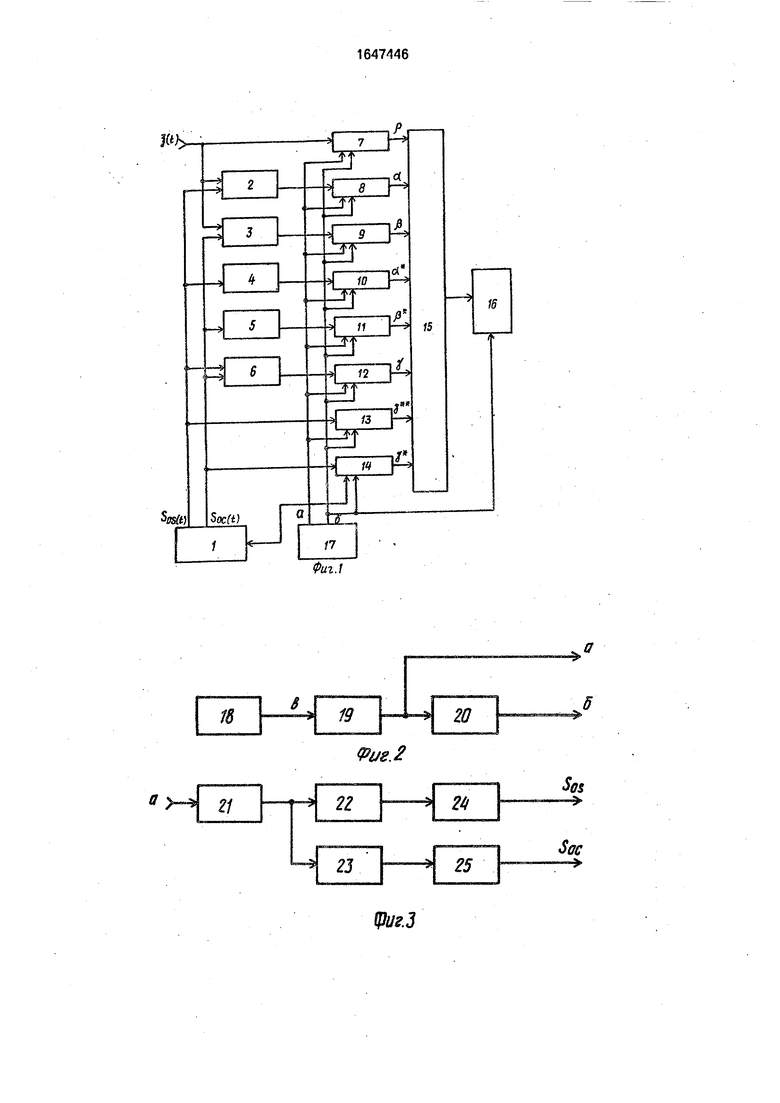

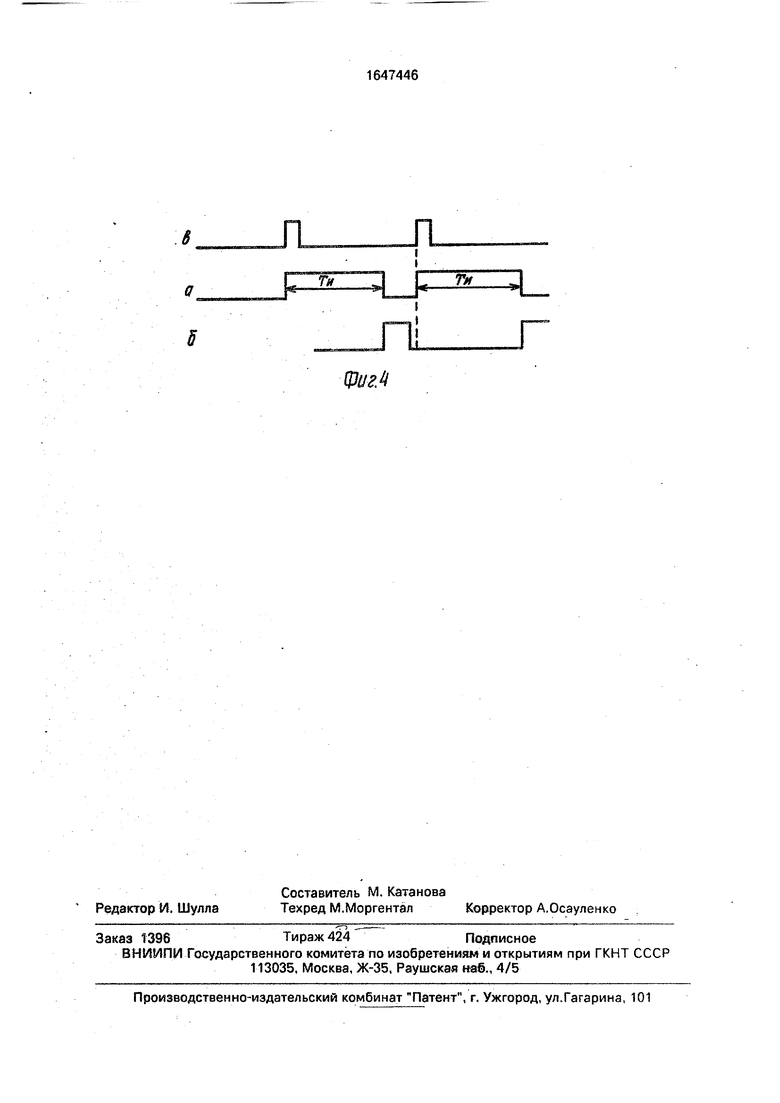

На фиг. 1 приведена структурна, схема устройства; на фиг, 2 - структурная схема блока управления; на фиг. 3 - структурная схема генератора опорного напряжения; на фиг. 4 - эпюры напряжения в блоке управления.

Устройство содержит генератор 1 опорного напряжения, первый и второй перемножители 2 и 3, входы которых подключены к входу измеряемого сигнала и

выходам генератора 1 опорного напряжения; первый и второй квадраторы 4 и 5, входы которых подключены к выходам генератора 1 опорного напряжения; третий перемножитель 6, входы которого также подключены к выходам генератора 1 опорного напряжения; интегратор 7, вход которого подключен к входу измеряемого сигнала; интеграторы 8-12, входы которых подключены соответственно к выходам первого и второго перемножителей 2 и 3, первого и второго квадраторов 4 и 5 и третьего перемножителя 6, интеграторы 13 и 14, входы которых подключены к выходам ге- ., нератора 1 опорного напряжения7

вычислительный блок 15, входы которого подключены к выходам интеграторов 7-14, а выход - к входу индикатора 16; блок 17 управления, выходы которого подключены к управляющим входам интеграторов 7-14 и индикатора 16,

Блок 17 управления содержит формирователь 18 импульсов пуска (ФИП), времязаХ|

4 О

дающий элемент (ВЗЭ) 19 и формирователь

20 мнп/лксоч (fbil), последовательно соеди- чанные межп(у собой. Выходом блока 17 управления являются шины а и б, причем шина а является выходом времязадающего элемента 19, а шиня 6 - формирователя 20 импульсов. Шина а подключена к управляющим входам генератора 1 опорного напряжения и интеграторов 7-14, а шина б - к управляющим входам интеграторов 7-14 и индикатора 16Генератор 1 опорного напряжения содержит тактовый генератор 21 (ТО- ВХ°Д которого подключен к выходу а блока 17 упровлпшя, два запоминающих устройства {ЗУ} 22 я 23, от- jx подключены к BL о w . е; no, 11, и ;лвз циф- роэнЗ Юговь ч npeoC;.c; iOЈ.лепя ()24 ч Р5, входы педкшочены к соответствующем выхэдаи ,i .поминающих устройств 22 и 23, а вих оды являются выходами синусной Sos(i) и ко нусной (t) составляющих спорного сигнала генеранзра 1 опорного напряжения,

Устройство работает следующие j5pa- зом.

На первый и второй перемножив ли 2 и 3 пост, пэет зсчерл -мый сигнал с входа измеряемого сигнала, а также синусная и ко- синуснэя составляющие опорного сигчгяг с выходов гонепатора 1 опор-нога напряжения. Генератор 1 опорного напряжения может работать в сзюнпмном режиме либо синхронизироваться oi блокэ 17 управления. На выходе первого интегратора 8 формируется сигнал

a (t)Sos(t)di,

п о

где - измеряемым сигнал, а Sos{t}- синусная составляющая опорного сигнала с выхода генератора 1 опорного напряжения.

На выходе второго интегратора 9 формируется сигнал

jS -f-mt)Soc(t)dt,

ln о

где Soc(t) - косинусная составляющая опорного сигнала с выхода генератора 1 опорного напряжения.

Кроме того, синусная и косинусная составляющие опорного сигнала с выхода генератора 1 опорного напряжения возводятся в квадрат при помощи первого и второго квадраторов 4 и 5 и перемножаются между собой при помощи третьего пе- ремножителя 6. На выходе третьего интегратора 10 формируется сигнал

Sis (t)dt,

in 0

на выходе четвертого интегратора 11 формируется сигнал

1 /П52С (t)dt,

°

на выходе пятого интегратора 12 формируется сигнал:

1 1П уа / Sos(t)Soc(t)dt.

I П 0

Кроме того, на вход шестого интегратора 7 также поступает измеряемый сигнал и на его выходе формируется сигнал

/o 4-mt}dt.

о

На входы седьмого и восьмого интеграторов 13 и 14 поступают соответственно синусная и косинусная составляющие опорного сигнала с генератора 1 опорного

напряжения, и на выходе седьмого интегратора 13 формируется сигнал

1 I у / sos(t)dt,

ln о

а на выходе восьмого интегратора 14 - сигнал

у

1 1П

. pSoc(:)dt.

Вслчисльз-ельный блок 15, куда поступают сигналы со всех интеграторов 7-14:a, ft, a, /, р, у, у, у, осуществляет перевод их в цифровую форму и вычисление результата измерения. На

индикаторе 16 формируется результат измерения фазового сдвига измеряемого сигнала относительно опорного

40

(й,зм arcig

e()-y-()-y(.

«( )()-г(ру-0)

что, как показано выше, соответствует результату измерения фазового сдвига с минимальной погрешностью.

Синхронизацию работы интеграторов 7-14 и индикатора 16 осуществляет блок 17 управления.

Блок 17 управления (фиг. 2) работаетследующим образом.

Формирователь 18 импульсов пуска формирует одиночные импульсы, которые запускают времязадающий элемент 19. Последний формирует импульс, равный по

длительности требуемому времени измерения Ти. Этот импульс поступает на выход а блока М управления м на вход формирователя 20 импульсов, на выходе которого создается прямоугольный импульс, который поступает на выход б блока 17 управления.

В течение действия импульса на выходе а длительностью Ти происходит интегрирование сигналов, поступающих на входы интеграторов 7-14. В течение действия импульса на выходе б происходит запоминание ре- зультата интегрирования, вычисление результата измерения и подключение элемента памяти индикатора 16 к выходу вычислительного блока 15 Индикатор 16 запоминает результат измерения и отобража- ет его до прихода следующего импульса по шине б. Для пояснения работы блока 17 управления на фиг. 4 приведены эпюры напряжений в элементах блока 17 управления в точках а, б, в.

Вычислительный блок 15 может представлять собой стандартную микроЭВМ с АЦП на входе. Вычислительный блок 15 выполняет следующие функции, вытекающие из описания работы предлагаемого устрой- ства:

подключение выходов интеграторов к входам АЦП, содержащихся в вы ислитель- ном блоке, причем это может происходит как автоматически, по концу времени интег- рирования Ти, так и ранее времени Ти по командам оператора (или по программе) для получения нескольких текущих значений фазового сдвига,

считывании цифровых кодов с выходов АЦП и занесение их в память блока 15;

вычисление результата измерения по указанной формуле и преобразование его к виду, удобному для отображения на индикаторе;;

переход в режим ожидания для повторения всех операций.

Технико-экономический эффект предлагаемого устройства заключается в возможности уменьшения погрешности измерения при существенном повышении быстродействия. Особенно это важно при измерениях сдвига фаз сигналов на инфра- низких частотах при времени измерения меньшем периода сигнала, При временах измерения, меньших периода CHI нала, и при наличии в сигнале,постоянной составляющей измерение фазового сдвига известными способами становится фактически невозможным ввиду больших погрешностей Для измерения с приемлемой точностью время измерения необходимо увеличить до значения, кратного периоду или полупериоду сигнала. Используя предлагаемое устройство, время измерении по сравнению с прототипом, можно уменьшить, как минимум, на один-два порядка

Формула исобретения Устройство измерения фазового сдвига, содержащее генератор опорного напряжения, три перемножителя, два квадратора, пять интеграторов, вычислительный блок и индикатор, причем входы первого и второго перемножтечи iiio,ui и ду измеряемого сигнала и СООТО ТР ЮЩИМ выходам генератора опооного нг ь i входы первого и второю квад| -iijn is 1 третьего перемножитепч по/ п HI р ходам генератора опорного ичпр м , вход первого интегратора под тючс н - ходу первого перемно чит п insoiiui интегратора - к BI хсд пороге nt рсммом теля.вход третьего интегратора - к выходу первого квадратора вход четвертого итог ратора - к выходу второго кзад. ор i i пятого интегратора - У выходу чиитьст по ремножителя, выходы пяти пнте рзтс . он подключены к соответствующим ext i1 числительного бтокз сосдипг-ги Ч| катером, отличающееся т. , , целью повышения точности и бы о вия при наличии в сигнале HHO.I i ставляющей, оно снабжено n. седьмым и восьмым интеграторами и 6 io ком управления, причем пход шест п тегратора подключен к вхсд i п -рч го л сигнала, входы седьмого и восьмого i mer раторов подключены к соотретств/юш м выходам генератора опорною на трчже m а выходы шестого, седьмою и i nor ro интеграторов подключены к соотвектпую ам входам вычислительного блока выходы б ю ка управления соединены соответственно с управляющими входами интеграторов, индикатора и генератора опорного напряжения.

Фиг, 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ измерения сдвига фаз | 1985 |

|

SU1310742A1 |

| Способ измерения амплитуды сигнала | 1986 |

|

SU1465786A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ АМПЛИТУДЫ СИГНАЛА | 2004 |

|

RU2280877C1 |

| Способ определения фазового сдвига | 1986 |

|

SU1377765A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ АМПЛИТУДЫ СИГНАЛА | 2000 |

|

RU2212676C2 |

| Способ определения фазового сдвига | 1988 |

|

SU1651227A2 |

| СПОСОБ ИЗМЕРЕНИЯ ПОСТОЯННОЙ СОСТАВЛЯЮЩЕЙ ГАРМОНИЧЕСКОГО СИГНАЛА | 2005 |

|

RU2281519C1 |

| Способ определения амплитуды сигнала | 1989 |

|

SU1674003A1 |

| Способ определения фазового сдвига | 1987 |

|

SU1430904A1 |

| СПОСОБ ИЗМЕРЕНИЯ ПОСТОЯННОЙ СОСТАВЛЯЮЩЕЙ СИГНАЛА | 2003 |

|

RU2239842C1 |

Изобретение может быть использо ми для определения фазовых сдвиг ов сигналов, содержащих постоянную составляющую Цель изобретения - повышение точности и быстродействия при наличии в сигнале п-- стоянной составляющей Устройство содержит генератор 1 опорного напряжения, перемножители 2, 3 и 6, квадраторы Д и Ь интеграторы 7-14, вычислительный блок 15 и индикатор 16, Цель достигается за счет выполнения дополнительных измерений и использования оптимальной (по систематической и случайным погрешностям) обработки результатов измерений 4 ил

фиг.З

6

n

о

pert

ФигМ

л

TV

| Способ определения фазового сдвига | 1986 |

|

SU1377765A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| г .Красноярск, 1971, с | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-07—Публикация

1988-12-02—Подача