Изобретение относится к вычислительной технике и может быть использовано для повышения производительности компьютера.

Аналогом изобретения является устройство, состоящее из ассоциативного накопителя АН разрядностью m x n, соединенного входом с выходом селектора адреса и дешифратора и выходом регистра маски, и выходом с выходным регистром и памятью фиксации реакций, регистра аргумента поиска ПАj, соединенного выходом со входом регистра маски, регистра маски Mj, соединенного входом с регистром аргумента поиска и выходом с входом ассоциативного накопителя, памяти фиксации реакций, соединенной входом с выходом ассоциативного накопителя, выходом - с анализатором многократного совпадения, анализатора многократного совпадения, соединенного выходом с шифратором, и входом с памятью фиксации реакций, шифратора, соединенного входом с выходом анализатора многократных совпадений и выходом с входом селектора адреса и дешифратора, селектора адреса и дешифратора, соединенного входом с шифратором и выходом с ассоциативным накопителем, и выходной регистр Bj, соединенный входом c выходом ассоциативного накопителя и выходом с внешними устройствами (см., например,[1]).

В известном устройстве доступ к данным осуществляется только по их информационному содержимому и не обеспечивается возможность доступа к каждой ячейке памяти отдельно, по ее адресу.

Наиболее близким аналогом-прототипом является ассоциативное запоминающее устройство, содержащее четыре регистра, блок памяти, схему сравнения и функциональную схему, причем первый и второй регистры группами информационных входов, а третий регистр первой группой информационных входов, одновременно соединены группой информационных входов устройства, группы информационных выходов первого, второго и третьего регистров подключены соответственно к первой, второй и третьей группам информационных входов блока памяти, первой и второй группами информационных выходов соединенного соответственно со второй группой информационных входов третьего регистра и с первой группой информационных входов схемы сравнения, группой информационных выходов, подключенной к группе соответствующих входов четвертого регистра, а второй и третьей группами информационных входов соединенной соответственно со вторыми группами информационных выходов первого и второго регистров, при этом вторая группа информационных выходов третьего регистра подключена к группе информационных выходов устройства и функциональная схема группой информационных входов подключена к группе информационных выходов четвертого регистра, а группой информационных выходом - с выходом устройства (см., например, [1]).

В этом ассоциативном устройстве доступ к данным осуществляется так же, как и в аналоге, только по их содержимому и не обеспечивается возможность доступа по адресу к каждой ячейке памяти.

Сущность изобретения состоит в том, что в ассоциативное запоминающее устройство, содержащее четыре регистра, блок памяти и схему сравнения, причем первый и второй регистры группами информационных входов, а третий регистр первой группой информационных входов одновременно соединены с группой информационных входов устройства, группа информационных выходов третьего регистра подключена к группе информационных входов блока памяти, первой и второй группами информационных выходов соединенного соответственно со второй группой информационных входов третьего регистра и с первой группой информационных входов схемы сравнения, группой информационных выходов подключенной к группе соответствующих входов четвертого регистра, а второй и третьей группами информационных входов соединенной соответственно со вторыми группами информационных выходов первого и второго регистров, при этом вторая группа информационных выходов третьего регистра подключена к группе информационных выходов устройства, введены дополнительный регистр и блок управления, причем блок управления группой адресных выходов одновременно соединен с группами адресных входов дополнительного регистра, блока памяти и группой адресных входов четвертого регистра, дополнительной группой информационных входов подключенного к дополнительной группе информационных входов устройства, одновременно соединенных с первой группой информационных входов блока управления, первым и вторым управляющим выходом подключенного к первому и второму управляющим входам четвертого регистра, третьим управляющим выходом одновременно соединенного с третьим управляющим входом четвертого регистра и первым управляющим входом блока памяти, вторым управляющим входом одновременно подключенного к первому управляющему входу третьего регистра и к четвертому управляющему выходу блока управления, пятым и шестым управляющим выходом соединенного соответственно с управляющими входами первого и второго регистров, седьмым управляющим выходом соединенного с управляющим входом дополнительного регистра, который группой командных входов одновременно соединен с группой командных входов блока памяти и группой командных выходов блока управления, группой управляющих выходов соединенного с группой управляющих входов третьего регистра, причем дополнительный регистр группой информационных выходов подключен к группе вторых информационных входов блока управления, третьей группой информационных входов подключенного к группе информационных выходов третьего регистра, а группой управляющих входов соединенного с группой управляющих входов устройства и выходом подключенного к управляющему выходу устройства.

При таком выполнении ассоциативное запоминающее устройство обеспечивает возможность и адресного, и ассоциативного обращения к информации, хранящейся в его памяти.

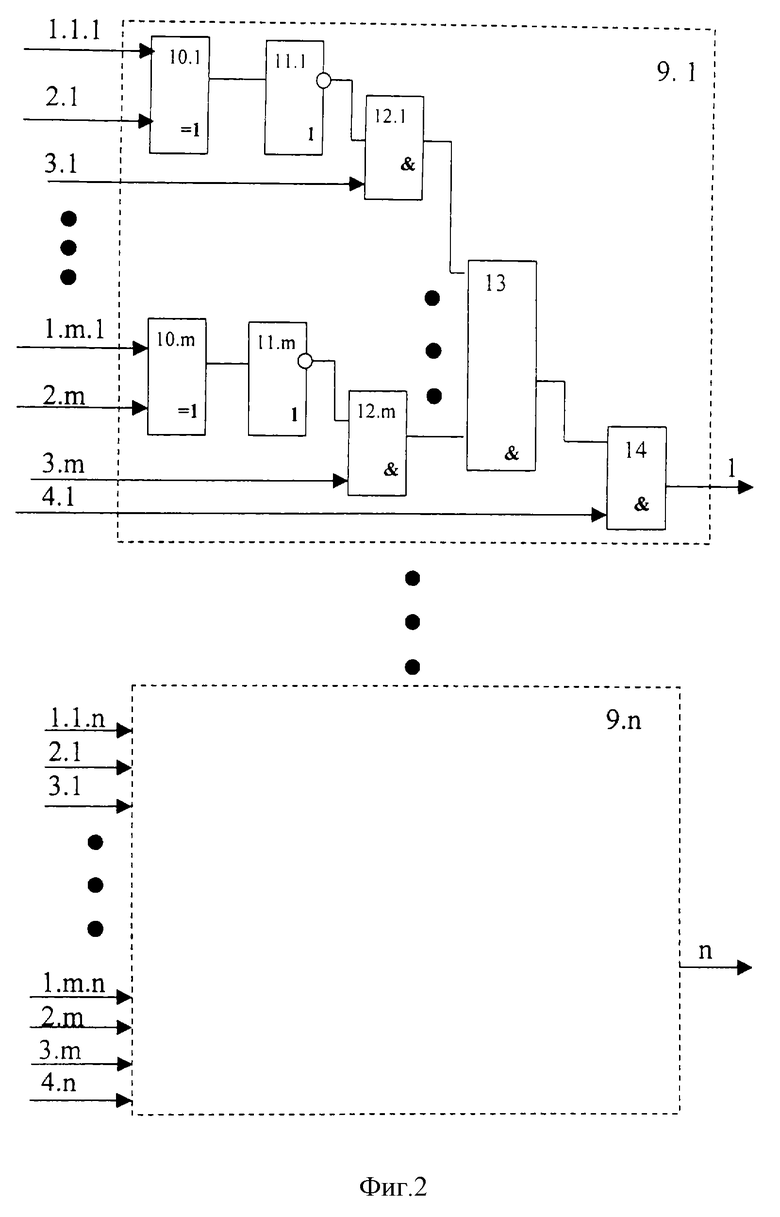

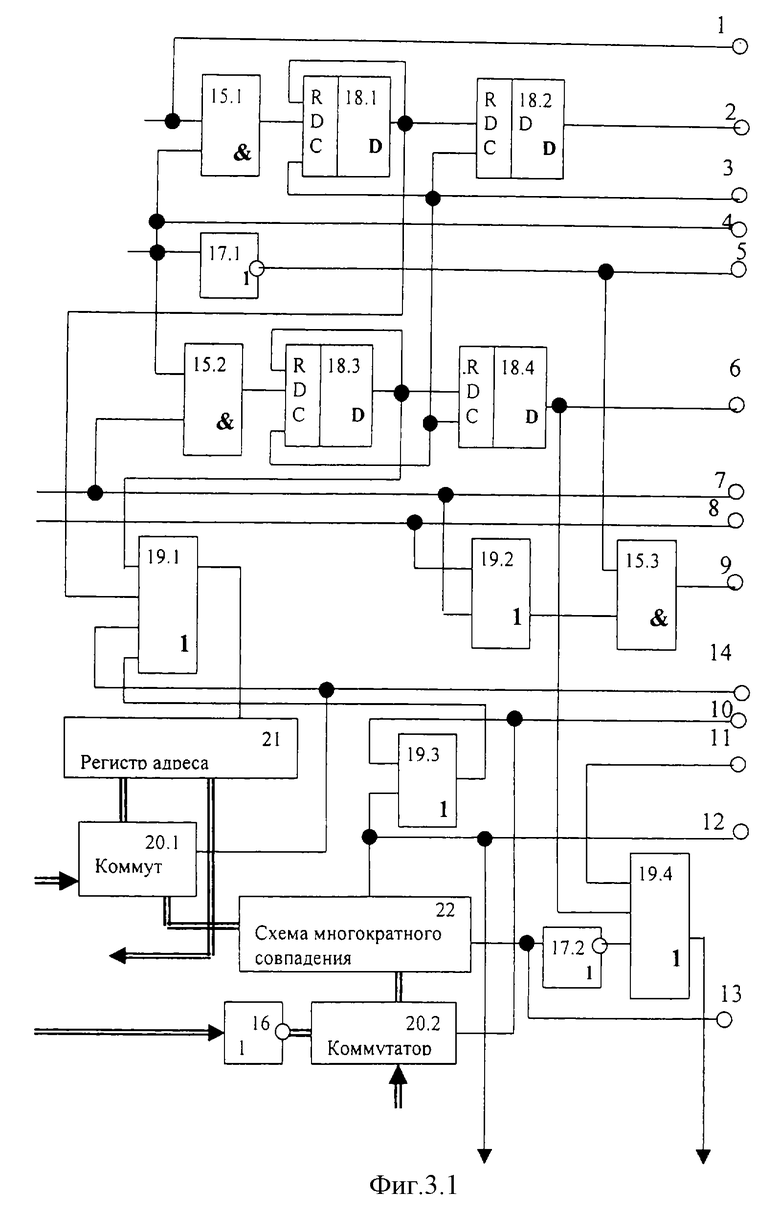

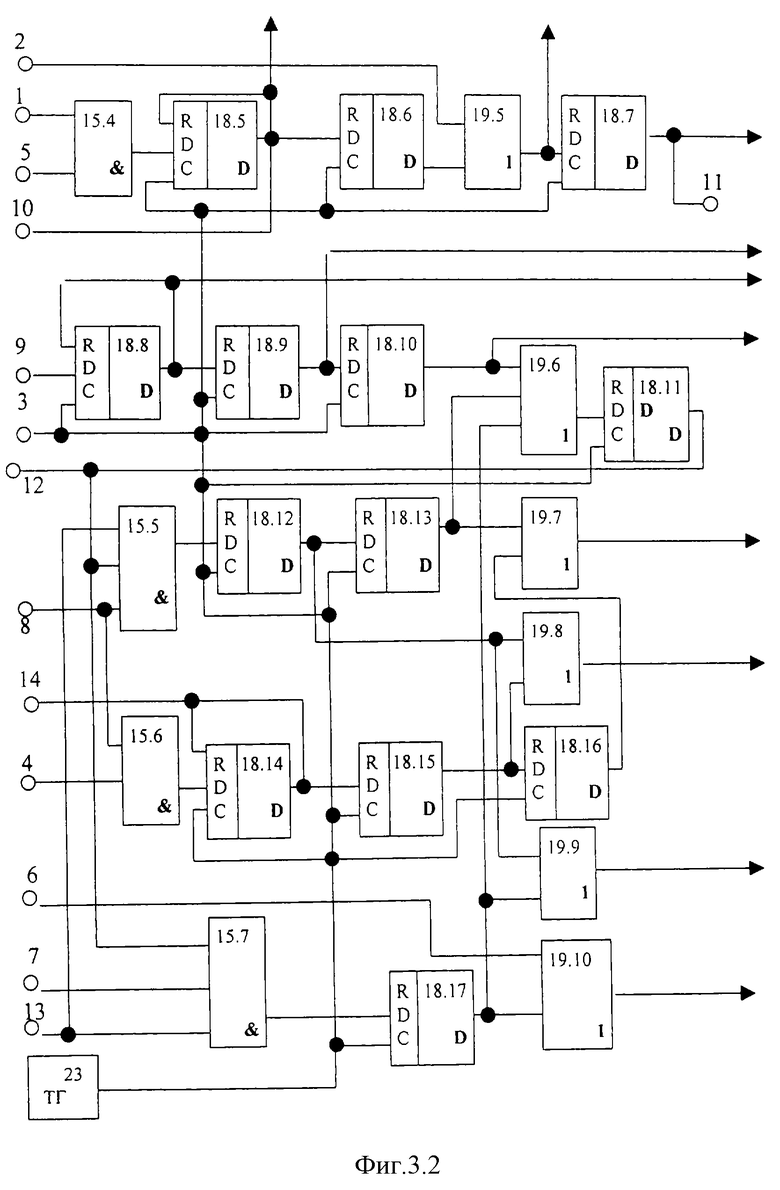

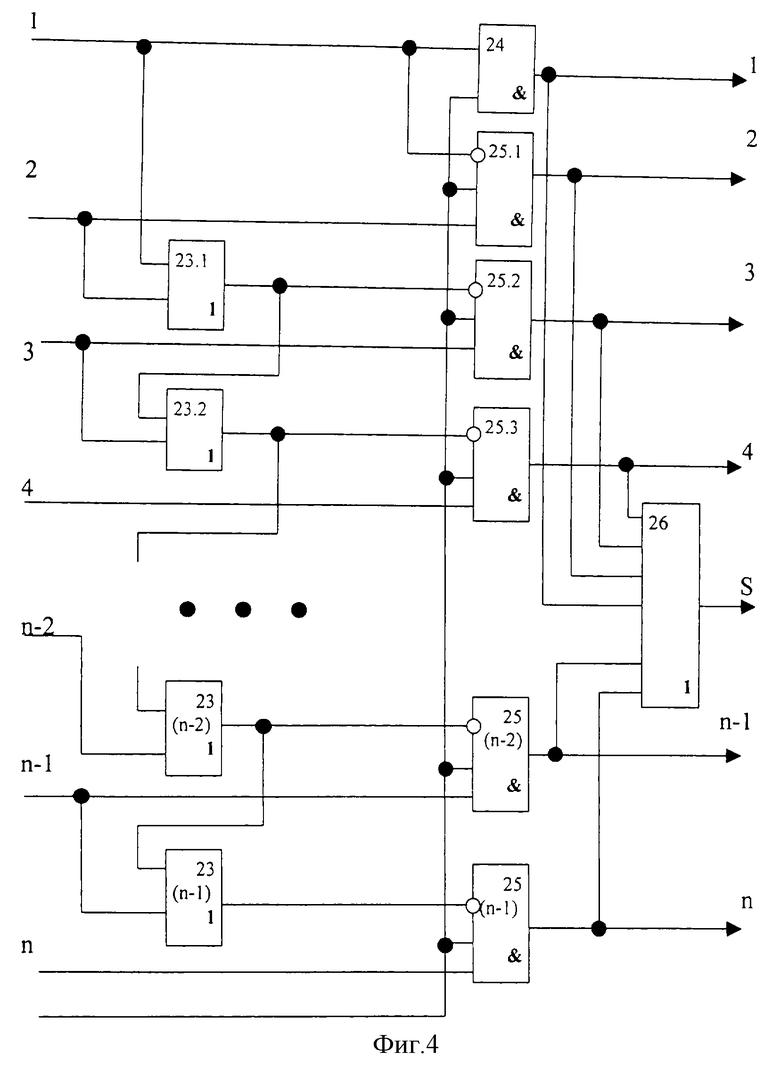

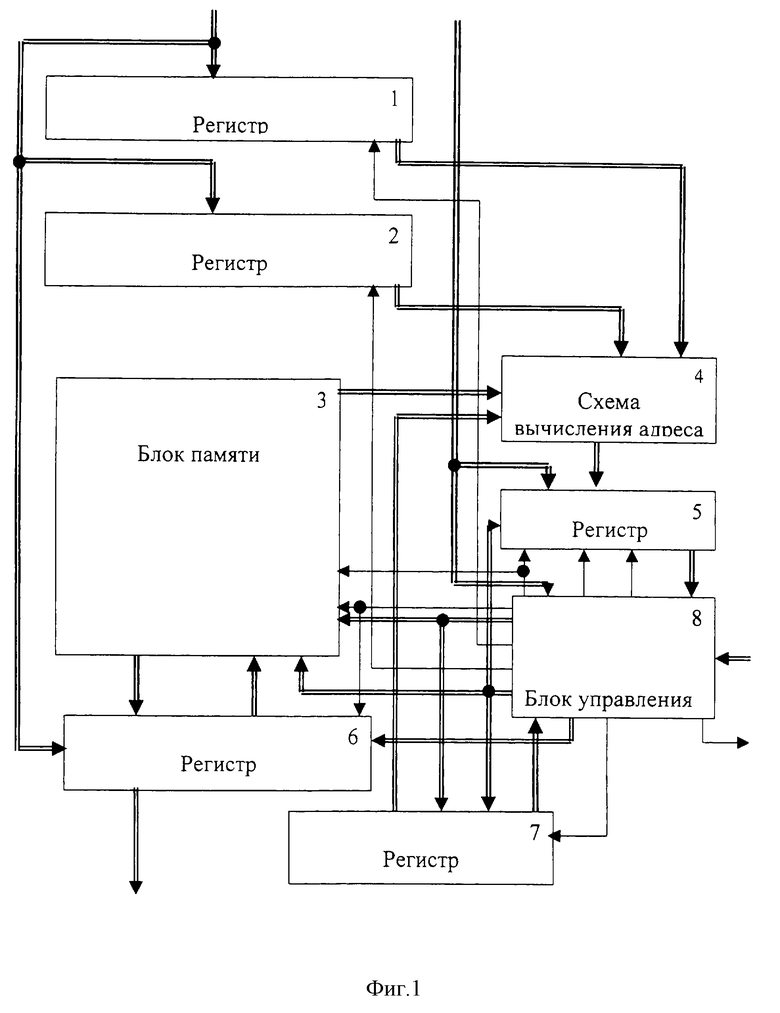

На фиг. 1 представлена функциональная блок-схема устройства, на фиг.2 приведена структурная схема устройства сравнения, на фиг.3 (3.1 и 3.2) представлена схема блока управления, а на фиг.4 показан пример выполнения входящего в блок управления анализатора.

Ассоциативное запоминающие устройство содержит регистры 1, 2, 3, 4 и 5 параллельного приема и выдачи информации (см., например, [2]). Регистры 1, 2, и 3 содержат по m (m=1,..., М) разрядов, где М-разрядность запоминаемого слова, регистры 4 и 5 по n (n=1,...,N) разрядов, где N-количество слов, хранимых в устройстве. Регистр 1 предназначен для хранения маски (типа трафарета), указывающей разряды, принимающие участие в ассоциативном поиске, регистр 2 - для хранения ассоциативного признака, по которому производится ассоциативный поиск, регистр 3 является буферным между запоминающим устройством и внешними шинами данных, в регистре 4 хранится информация о вычисленных записях, а в регистре 5 находится информация о занятости конкретной ячейки блока 6 памяти. Блок 6 памяти выполнен в виде адресного запоминающего устройства (см. , например, [2]) разрядностью m x n и предназначен для хранения информации.

Кроме того, ассоциативное запоминающие устройство содержит схему 7 вычисления адреса на основании данных, полученных из блока памяти и регистров 1, 2 и 5, определяет адреса, где находится искомая информация, и заносит их в регистр 4 и блок 8 управления, функционирующий на основании поступающих в него по группе управляющих входов команд и адресов, поступающих по дополнительной шине данных и из регистров 4 и 5 при помощи командных сигналов управляет работой устройства, причем регистры 1 и 2 группами информационных входов, а регистр 3 первой группой информационных входов одновременно соединены с группой информационных входов устройства. Группа информационных выходов регистра 3 подключена к группе информационных входов блока 6 памяти, первой и второй группами информационных выходов соединенного соответственно со второй группой информационных входов регистра 3 и с первой группой информационных входов схемы 7 вычисления адреса, группой информационных выходов подключенной к группе соответствующих входов регистра 4, а второй и третьей группами информационных входов соединенной соответственно со вторыми группами информационных выходов регистров 1 и 2. При этом вторая группа информационных выходов регистра 3 подключена к группе информационных выходов устройства, блок 8 управления группой адресных выходов одновременно соединен с группами адресных входов регистра 5, блока 6 памяти и группой адресных входов регистра 4, второй группой информационных входов подключенного к дополнительной группе информационных входов устройства, одновременно соединенных с первой группой информационных входов блока 8 управления, первым и вторым управляющим выходом подключенного к первому и второму управляющим входам регистра 4. Регистр 4 третьим управляющим выходом одновременно соединенного с третьим управляющим входом регистра 4 и первым управляющим входом блока 6 памяти, вторым управляющим входом одновременно подключенного к первому управляющему входу регистра 3 и к четвертому управляющему выходу блока 6 управления, пятым и шестым управляющим выходом соединенного соответственно с управляющими входами регистров 1 и 2, седьмым управляющим выходом соединенного с управляющим входом регистра 5. Регистр 5, который группой командных входов одновременно соединен с группой командных входов блока 6 памяти и группой командных выходов блока 8 управления, группой управляющих выходов соединенного с группой управляющих входов регистра 3, причем регистр 5 группой информационных выходов подключен к группе вторых информационных входов блока 8 управления, третьей группой информационных входов подключенного к группе информационных выходов регистра 3, а группой управляющих входов соединенного с группой управляющих входов устройства и выходом подключенного к управляющему выходу устройства.

Схема 7 вычисления адреса содержит N блоков 9 логики (см. фиг.2), выходами подключенных к соответствующим выходам группы выходов схемы 7 вычисления адреса, а первыми выходами соединенных с соответствующими от 1.1.1 по 1.m.n входами первой группы информационных входов схемы 7 вычисления адреса, причем каждый k-ый блок 9 логики подключен к этой группе информационных входов соответствующими от 1.1.k до 1.M.k, где k=1...n.

Вторыми и третьими входами (от 2.1 и 3.1 до 2.М и 3.М соответственно) блоки 9 логики подключены к соответствующим входам соответственно второй и третьей группам информационных входов схемы 7 вычисления адреса, а четвертыми входами (от 4.1 до 4.m) соединены соответственно с соответствующими входами четвертой информационной группы входов.

Каждый из n блоков 9 логики состоит из М модулей 10 "исключающее ИЛИ" (см., например, [3]), через инвертор 11 выходами соединенных с первым входом соответствующего элемента 12 "И", вторым входом подключенного к соответствующему входу соответствующего блока 9 логики, соединенному с третьей группой информационных входов схемы 7 вычисления адреса и выходом соединенного с соответствующим входом элемента 13 "И", выходом подключенного к первому входу элемента 14 "И", вторым входом соединенного с соответствующим входом соответствующего блока 9 логики, подключенного к четвертой группе информационных входов схемы 7 вычисления адреса. При этом выход элемента 14 "И" соединен с соответствующим выходом группы выходов блока 9 логики.

Блок 6 управления содержит семь элементов 15 "И", причем элементы 15.1.. .15.4 и 15.6 выполнены с двумя входами, а элементы 15.5 и 15.7 "И" - с тремя входами, узел 16 инверторов, два инвертора 17, семнадцать D-триггеров 18, десять элементов 15 "ИЛИ", при этом элементы 19.2, 19.3, 19.5 и 19.7...19.10 "ИЛИ" выполнены с двумя входами, элементы 19.4 и 19.6 выполнены с тремя входами, а элемент 19.1 выполнен с четырьмя входами, два коммутатора 20, регистр 21 адреса, схему многократного совпадения 22, и тактовый генератор 23.

Первые входы элементов 15.1 и 15.4 "И" одновременно подключены к первому входу группы управляющих входов блока 6 управления, при этом второй вход элемента 15.1 "И" соединен со вторым входом группы управляющих входов блока 6 управления, одновременно подключенного ко входам инвертора 17.1, первому входу элементов 15.2 "И" и второму входу элемента 15.6 "И".

Выход элемента 15.1 "И" соединен с D-входом D-триггера 18.1, R-входом одновременно подключенного к выходу этого триггера, а также к D-входу D-триггера 18.2 и к первому входу элемента 19.1 "ИЛИ". С-вход D-триггера 18.1 одновременно соединен с С-входами D-триггеров 18.2-18.17 выходом тактового генератора 23.

Выход D-триггера 18.2 подключен к первому входу элемента 19.5 "ИЛИ", вторым входом соединенного с выходом D-триггера 18.6, а выходом подключенного к первому выходу группы управляющих выходов блока 6 управления и к D-входу D-триггера 18.7.

Выход элемента 15.4 "И" соединен с D-входом D-триггера 18.5, R-входом одновременно подключенного к выходу этого триггера, к седьмому управляющему выходу блока 6 управления, к первому входу элемента 19.3 "ИЛИ", а также к D-входу D-триггера 18.6 и к управляющему входу коммутатора 20.2.

Выход D-триггера 18.7 подключен к первому выходу в группе командных выходов блока 6 управления и к первому входу элемента 19.4 "ИЛИ", вторым выходом соединенным с выходом D-триггера 18.4, а третьим входом подключенным к выходу инвертора 17.2 и выходом соединенным с выходом блока 6 управления.

Выход инвертора 17.1 соединен со вторым входом элемента 15.4 "И", с первым входом элемента 15.3 "И", вторым входом соединенным с выходом элемента 19.2 "ИЛИ". При этом вторые входы элементов 15.2 "И", 19.2 "ИЛИ" и элемента 15.7 "И" одновременно подключены к третьему входу группы управляющих входов блока 6 управления, при этом первый вход элемента 19.2 "ИЛИ" подключен к четвертому входу группы управляющих входов блока 6 управления, подключенной к третьему входу элемента 15.5 "И" к первому входу элемента 15.6 "И".

Выход элемента 15.2 "И" соединен с D-входом D-триггера 18.3, R-входом одновременно подключенного к выходу этого триггера, а также к D-входу D-триггера 18.4 и к первому входу элемента 19.1 "ИЛИ". Выход D-триггера 18.4 подключен к первому входу элемента 19.10 "ИЛИ", выходом подключенного ко второму выходу группы управляющих выходов блока 6 управления.

Третий вход элемента 19.1 "ИЛИ" соединен с выходом D-триггера 18.14 и управляющими входами схемы многократного совпадения и коммутатора 20.1, а выход подключен к управляющему входу регистра 21. При этом элемент 19.3 "ИЛИ" вторым входом подключен к первому управляющему выходу блока 6 управления, второму входу элемента 15.5 "И", первому входу элемента 15.7 "И" и к выходу D-триггера 18.11.

Регистр адреса 21 группой входов соединен с группой выходов коммутатора 20.1, первой группой входов соединенный с первой группой информационных входов блока 6 управления, а второй группой входов соединенный с группой выходов схемы многократного совпадения, и группой выходов соединен с группой адресных выходов блока 6 управления.

Схема многократного совпадения 22 группой входов подключена к группе выходов коммутатора 20.2, а управляющим выходом соединена со входом инвертора 17.2, первым входом элемента 15.5 "И" и третьим входом элемента 15.7 "И".

Группа инверторов 16 группой входов соединена со второй группой информационных входов блока 6 управления а группой выходов подключена к первой группе входов коммутатора 20.2, второй группой входов подключенный к третьей группе информационных входов блока 6 управления.

Выход элемента 15.3 "И" соединен с D-входом D-триггера 18.8, R-входом одновременно подключенного к выходу этого триггера, к шестому управляющему выходу блока 6 управления, а также к D-входу D-триггера 18.9, причем D-триггер 18.9 своим выходом подключен к пятому управляющему выходу блока 6 управления, а также к D-входу D-триггера 18.10.

Выход D-триггера 18.10 подсоединен к первому входу элемента 19.6 "ИЛИ" и к третьему управляющему выходу блока 6 управления, при этом второй вход элемента 19.6 "ИЛИ" подключен к выходу D-триггера 18.13, а выход соединен с D-входом D-триггера 18.11.

Выход элемента 15.5 "И" соединен с D-входом D-триггера 18.12, при этом D-триггер 18.12 своим выходом соединен с D-входом D-триггера 18.13 и первыми входами элементов 19.8 и 19.9 "ИЛИ".

Выход D-триггера 18.13 подключен к первому входу элемента 19.7 "ИЛИ", который своим вторым входом соединен с выходом D-триггера 18.16, а выходом соединен вторым выходом в группе управляющих выходов.

Выход элемента 15.6 "И" соединен с D-входом D-триггера 18.14, при этом D-триггер 18.14 своим выходом соединен с D-входом D-триггера 18.15. D-триггер 18.15 выходом соединен с D-входом D-триггера 18.16 и вторым входом элемента 19.8 "ИЛИ", выходом соединенным с четвертым управляющим выходом.

Выход элемента 15.7 "И" соединен с D-входом D-триггера 18.17, при этом D-триггер 18.17 своим выходом соединен с третьим входом элемента 19.6 "ИЛИ" и вторыми входами элементов 19.9 и 19.10 "ИЛИ", при этом выход элемента 19.9 соединен со вторым управляющим выходом блока 8 управления.

Схема 22 анализатора многократного совпадения содержит n-1 двухвходовых элементов 23 "ИЛИ", элемент 24 "И", n-1 элементов 25 "И" с одним инвертирующим входом и n в ходовой элемент 26 "ИЛИ".

При этом первый вход группы входов схемы 22 анализатора многократного совпадения одновременно соединен с первыми входами элементов 23.1 "ИЛИ" и элемента 24 "И", причем вторые входы элемента 24 "И" и элементов 25.1 25. n "И" одновременно подключены к первому (управляющему) входу схемы 22 анализатора многократного совпадения.

Выходы элементов 24 и 25 "И" соединены с соответствующими с первого по n входами элемента 26 "ИЛИ" и одновременно подключены к соответствующим с первого по n выходам группы выходов схемы 22 анализатора многократного совпадения, своим выходом соединенной с выходом элемента 26 "ИЛИ".

При этом вторые входы элементов 23.1-23.n-1 "ИЛИ" подключены к соответствующим от второго по n-1 входам группы входов схемы 22 анализатора многократного совпадения и к третьим входам соответствующих элементов 25.2-25. n-2 "И", инвертирующим (первым) входами соединенных с выходами соответствующих элементов 23.1-23.n-1 "ИЛИ", одновременно подключенным к первым входам элементов 23.2-23.n-1 "ИЛИ" соответственно, причем третий вход элемента 25.n-1 "И" соединен с n входом группы входов схемы 22 анализатора многократного совпадения.

Ассоциативное запоминающее устройство (далее-АЗУ) функционирует в составе вычислительного комплекса (не показан).

АЗУ работает в шести режимах.

Режим 1-ассоциативное занесение информации в АЗУ.

От вычислительного комплекса на блок 8 управления через первый вход группы управляющих входов подают управляющий сигнал-запись (в двоичном-коде "1"), а через второй вход группы управляющих входов подают сигнал режим (в двоичном коде-"0"). Одновременно на регистр 6 через группу входов АЗУ подают информацию, которую через этот регистр передают в блок 3 памяти. Работой АЗУ в режиме 1 управляют элементы 15.4, 18.5, 18.6, 18.7, 19.1, 19.3, 19.4 и 19.5 блока управления. Информация о занятости ячеек с информационного выхода регистра 7 по команде, переданной с седьмого управляющего выхода блока 8 управления поступает на второй информационный вход блока 8 через вторую группу информационных входов. Далее информацию о занятости ячеек инвертируют в блоке инверторов 16 и через коммутатор 20.2 передают на схему многократного совпадения, которая определяет адрес старшей 1, и через коммутатор 20.1 заносит его в регистр адреса 21. Записываемую информацию записывают в регистр 6 по команде, переданной по Первому управляющему выходу блока 8 управления. Далее по адресу, переданному из блока 8 управления по группе адресных выходов на адресные входы блока 3 памяти и регистра 7 по команде, переданной по первому выходу в группе командных выходов блока 8 управления одновременно происходит запись информации из регистра 6 в блок памяти 3 и устанавливают разряд регистра 7, соответствующий переданному адресу, в 1. По окончании операции на выходе блока 8 управления формируется сигнал окончания работы ("1" в двоичном коде).

Режим 2-адресное занесение информации в АЗУ.

От вычислительного комплекса на блок 8 управления через первый вход группы управляющих входов подают управляющий сигнал-запись (в двоичном-коде "1"), а через второй вход группы управляющих входов подают сигнал-режим (в двоичном коде - "1"). Одновременно на регистр 6 через группу входов АЗУ подают информацию, а через дополнительную группу информационных входов АЗУ на блок 8 управления подают сигнал-адрес. Работой АЗУ в режиме 2 управляют элементы 15.1, 18.1, 18.2, 18.7, 19.1, 19.4 и 19.5 блока управления. Записываемую информацию записывают в регистр 6 по команде, переданной по первому управляющему выходу блока 8 управления. Адрес запоминают в регистре адреса 21, а затем по адресу, переданному из блока 8 управления по группе адресных выходов на адресные входы блока 3 памяти и регистра 7, по команде, переданной по первому выходу в группе командных выходов блока 8 управления, одновременно происходит запись информации из регистра 6 в блок памяти 3 и устанавливают разряд регистра 7, соответствующий переданному адресу, в 1. По окончании операции на выходе блока 8 управления формируется сигнал окончания работы ("1" в двоичном коде).

Режим 3-ассоциативное удаление информации в АЗУ.

От вычислительного комплекса на блок 8 управления через второй вход группы управляющих входов подают управляющий сигнал-удаление (в двоичном-коде "1"), а через второй вход группы управляющих входов подают сигнал-режим (в двоичном коде - "0"). Одновременно на регистр 1 через группу входов АЗУ подают маску, а затем на регистр 2 через группу входов АЗУ подают ассоциативный признак. Ассоциативное удаление записей происходит в два этапа. На первом этапе вычисляют признак совпадения, который хранится в регистре 4, при этом работой АЗУ управляют элементы 15.3, 18.8, 18.9, 18.10 и 19.2. В регистр 1 по команде с пятого управляющего выхода блока 8 управления заносят маску, а затем в регистр 2 по команде с шестого управляющего выхода блока 8 управления заносят ассоциативный признак. Далее по команде с третьего управляющего выхода блока 8 управления производят ассоциативную выборку, при этом схема вычисления адреса на основании маски, ассоциативного признака и содержимого блока 3 памяти вычисляет признак совпадения и запоминает его в регистре 4. На втором этапе происходит циклическое удаление записей из АЗУ, при этом работой АЗУ управляют элементы 15.7. 18.11, 18.17, 19.1, 19.3, 19.4, 19.6, 19.9 и 19.10. Из регистра 4 на третий информационный вход блока 8 управления признак совпадения по команде, переданной по первому управляющему выходу блока 8 управления через коммутатор 20.2 попадает на схему многократного совпадения. Если в признаке совпадений есть хотя бы одна 1, то управляющий выход схемы 22 многократного совпадения устанавливают в 1, и адрес старшей 1 через коммутатор 20.1 заносит его в регистр адреса 21. Далее по адресу, переданному из блока 8 управления по группе адресных выходов на адресные входы блока 3 памяти и регистра 7 по команде, переданной по второму выходу в группе командных выходов блока 8 управления одновременно происходит удаление записи в блоке памяти 3 и устанавливают разряд регистра 7, соответствующий переданному адресу, в 0, при этом по команде, переданной по второму управляющему выходу блока 8 управления разряд регистра 4 также устанавливают в 0, а затем происходит возврат к началу цикла. Если же в признаке совпадения, переданном из регистра 4, не окажется ни одной 1, то тогда операция удаления завершается. Цикл прерывается, и на выходе блока 8 управления формируется сигнал окончания работы ("1" в двоичном-коде).

Режим 4 - адресное удаление информации в АЗУ.

От вычислительного комплекса на блок 8 управления через второй вход группы управляющих входов подают управляющий сигнал-удаление (в двоичном-коде "1"), а через второй вход группы управляющих входов подают сигнал-режим (в двоичном-коде "1"). Одновременно через дополнительную группу информационных входов АЗУ на блок 8 управления подают сигнал-адрес. Работой АЗУ в режиме 4 управляют элементы 15.2, 18.3, 18.4, 19.1, и 19.10 блока управления. Адрес запоминается в регистре адреса 21, а затем по адресу, переданному из блока 8 управления по группе адресных выходов на адресные входы блока 3 памяти и регистра 7, по команде, переданной по второму выходу в группе командных выходов блока 8 управления одновременно происходит удаление информации в блоке памяти 3 и устанавливают разряд регистра 7, соответствующий переданному адресу, в 0. По окончании операции на выходе блока 8 управления формируется сигнал окончания работы ("1" в двоичном-коде).

Режим 5-ассоциативное считывание информации в АЗУ.

От вычислительного комплекса на блок 8 управления через третий вход группы управляющих входов подают управляющий сигнал-удаление (в двоичном коде - "1"), а через второй вход группы управляющих входов подают сигнал-режим (в двоичном коде - "0"). Одновременно на регистр 1 через группу входов АЗУ подают маску, а затем на регистр 2 через группу входов АЗУ подают ассоциативный признак. Ассоциативное считывание записей происходит в два этапа. На первом этапе вычисляют признак совпадения, который хранится в регистре 4, при этом работой АЗУ управляют элементы 15.3, 18.8, 18.9, 18.10 и 19.2. В регистр 1 по команде с пятого управляющего выхода блока 8 управления заносится маска, а затем в регистр 2 по команде с шестого управляющего выхода блока 8 управления заносится ассоциативный признак. Далее по команде с третьего управляющего выхода блока 8 управления производят ассоциативную выборку, при этом схема вычисления адреса на основании маски, ассоциативного признака и содержимого блока 3 памяти вычисляет признак совпадения и запоминает его в регистре 4. На втором этапе происходит циклическое удаление записей из АЗУ, при этом работой АЗУ управляют элементы 15.5, 18.11, 18.12, 18.13, 19.1, 19.3, 19.4, 19.6, 19.7, 19.8 и 19.9. Из регистра 4 на третий информационный вход блока 8 управления признак совпадения по команде, переданной по первому управляющему выходу блока 8 управления через коммутатор 20.2, попадает на схему многократного совпадения. Если в признаке совпадений есть хотя бы одна 1, то управляющий выход схемы 22 многократного совпадения устанавливается в 1 и адрес старшей 1 через коммутатор 20.1 заносит его в регистр адреса 21. Далее по адресу, переданному из блока 8 управления по группе адресных выходов на адресные входы блока 3 памяти по команде, переданной по четвертому управляющему выходу блока 8 управления, одновременно происходит считывание записи в блоке памяти 3 и запись ее в регистр 6, далее происходит выдача информации с информационного выхода регистра 6 на группу выходов АЗУ по команде, переданной по второму выходу в группе командных выходов блока 8 управления, при этом по команде, переданной по второму управляющему выходу блока 8 управления, разряд регистра 4 устанавливается в 0, а затем происходит возврат к началу цикла. Если же в признаке совпадения, переданном из регистра 4, не окажется ни одной 1, то тогда операция удаления завершается. Цикл прерывается, и на выходе блока 8 управления формируется сигнал окончания работы ("1" в двоичном коде).

Режим 6 - адресное считывание информации в АЗУ. От вычислительного комплекса на блок 8 управления через третий вход группы управляющих входов подают управляющий сигнал-удаление (в двоичном коде - "1"), а через второй вход группы управляющих входов подают сигнал режим (в двоичном коде - "1"). Одновременно через дополнительную группу информационных входов АЗУ на блок 8 управления подают сигнал-адрес. Работой АЗУ в режиме 2 управляют элементы 15.6, 18.14, 18.15, 18.16, 19.1, 19.4, 19.7 и 19.8 блока управления. Адрес запоминают в регистре адреса 21, а затем по адресу, переданному из блока 8 управления по группе адресных выходов на адресные входы блока 3 памяти но команде, переданной по четвертому управляющему выходу блока 8 управления, одновременно происходит считывание записи в блоке памяти 3 и запись ее в регистр 6, далее происходит выдача информации с информационного выхода регистра 6 на группу выходов АЗУ по команде, переданной по второму выходу в группе командных выходов блока 8 управления.

Литература

1. Каган Б.М. "Электронные вычислительные машины и системы". Москва, Энергоатомиздат, 1991 г. стр.106-108.

2. Огнев И. В. , Борисов В.В. "Ассоциативные среды". Москва, "Радио и связь", 2000 г., стр.58-62.

3. Справочник "Цифровые интегральные микросхемы", Москва, "Радио и связь", 1994 г., стр.31, 32.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ВВОДА И ХРАНЕНИЯ КЛЮЧЕВОЙ ИНФОРМАЦИИ | 2000 |

|

RU2175775C1 |

| Устройство для распаковки команд | 1990 |

|

SU1702367A1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ И ДЕМУЛЬТИПЛЕКСИРОВАНИЯ КОМПОНЕНТНЫХ СИГНАЛОВ В ЦИФРОВЫХ ПОТОКАХ | 2012 |

|

RU2514092C2 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА РЕГИСТРАЦИИ ПЕРСОНАЛЬНЫХ БИОМЕТРИЧЕСКИХ ДАННЫХ ЗАЯВИТЕЛЕЙ НА ПОЛУЧЕНИЕ ПАСПОРТНО-ВИЗОВЫХ ДОКУМЕНТОВ | 2008 |

|

RU2395838C1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ИНФОРМАЦИОННОГО ОБСЛУЖИВАНИЯ ОБРАЩЕНИЙ ГРАЖДАН | 2008 |

|

RU2378688C1 |

| СИСТЕМА ОБРАБОТКИ СИГНАЛОВ | 2006 |

|

RU2326359C1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| СИСТЕМА ЭЛЕКТРОННОГО ДИСТАНЦИОННОГО SMS-ГОЛОСОВАНИЯ | 2010 |

|

RU2421813C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

Изобретение относится к вычислительной технике и может быть использовано для повышения производительности компьютера. Техническим результатом является возможность доступа к ячейкам памяти не только по их содержимому, но и по их адресу. устройство содержит пять регистров, блок памяти, схему сравнения, блок управления. 4 ил.

Ассоциативное запоминающее устройство, содержащее четыре регистра, блок памяти и схему сравнения, причем первый и второй регистры группами информационных входов, а третий регистр первой группой информационных входов одновременно соединены с группой информационных входов устройства, группа информационных выходов третьего регистра подключена к группе информационных входов блока памяти, первой и второй группами информационных выходов соединенного соответственно со второй группой информационных входов третьего регистра и с первой группой информационных входов схемы сравнения, группой информационных выходов подключенной к группе соответствующих входов четвертого регистра, а второй и третьей группами информационных входов соединенной соответственно со вторыми группами информационных выходов первого и второго регистров, при этом вторая группа информационных выходов третьего регистра подключена к группе информационных выходов устройства, отличающееся тем, что в него введены дополнительный регистр и блок управления, причем блок управления группой адресных выходов одновременно соединен с группами адресных входов дополнительного регистра, блока памяти и группой адресных входов четвертого регистра, дополнительной группой информационных входов подключенного к дополнительной группе информационных входов устройства, одновременно соединенных с первой группой информационных входов блока управления, первым и вторым управляющим выходом подключенного к первому и второму управляющим входам четвертого регистра, третьим управляющим выходом одновременно соединенного с третьим управляющим входом четвертого регистра и первым управляющим входом блока памяти, вторым управляющим входом одновременно подключенного к первому управляющему входу третьего регистра и к четвертому управляющему выходу блока управления, пятым и шестым управляющим выходом соединенного соответственно с управляющими входами первого и второго регистров, седьмым управляющим выходом соединенного с управляющим входом дополнительного регистра, который группой командных входов одновременно соединен с группой командных входов блока памяти и группой командных выходов блока управления, группой управляющих выходов соединенного с группой управляющих входов третьего регистра, причем дополнительный регистр группой информационных выходов подключен к группе вторых информационных входов блока управления, третьей группой информационных входов подключенного к группе информационных выходов третьего регистра, а группой управляющих входов соединенного с группой управляющих входов устройства и выходом подключенного к управляющему выходу устройства.

| КАГАН Б.М | |||

| Электронные вычислительные машины и системы | |||

| - М.: Энергоатомиздат, 1991, с.106-108 | |||

| Огнев И.В | |||

| и др | |||

| Ассоциативные среды | |||

| - М.: Радио и связь, 2000, с.58-62 | |||

| US 6131143 A, 10.10.2000 | |||

| US 5412592 А, 02.05.1995 | |||

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2045787C1 |

Авторы

Даты

2003-09-20—Публикация

2001-11-13—Подача