..-(54) ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1989 |

|

RU2028663C1 |

| ФОРМУЛЬНЫЙ ПРОЦЕССОР С КОМАНДОПОДОБНЫМИ ЛОГИЧЕСКИМИ УПРАВЛЯЮЩИМИ ЭЛЕМЕНТАМИ | 1997 |

|

RU2143726C1 |

| Процессор ввода-вывода | 1980 |

|

SU934465A1 |

| Процессор микропрограмируемой ЭВМ | 1989 |

|

SU1697082A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Процессор микропрограммируемой ЭВМ | 1979 |

|

SU860077A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

1

Изобретение относится к вычислительной технике и может быть исполь эовано, например, для обработки данных физических экспериментов, для ре-j шения задач автоматизированного управления в реальном масштабе времени и для научных расчетов, требукяцих высокой прои.зводительности и большого объема памяти.

Известны высокопроизводительные вычислительные системы, содержащие один или два центральных процессора, пери- . ферийные процессоры и основное запоминающее устройство (ОЗУ). Каждый не-15 зависимо работающий периферийный процессор может одновременно обслуживать ряд каналов, связанных с внешними .устройствами (накопителями на магнитных дисках, магнитных лентах, устройства-20 ми визуального отображения, алфавитно-цифровыми печатающими устройствами и др.). Один из периферийных процессоров выделен для организации переключения с одной задачи на другую, 25 приема заказов на внешние обмены, т.е. для выполнения функций диспетчера;операционных систем. Все перечисленные, процессоры физическиимеют одно .ройство управления, которое обслужи- 30

вает один процессор за другим кольцевым методом 1 .

Центральный процессор содержит многофункциональное арифметическое устройство, в котором каждый блок независимо выполняет определенное арифметическое или логическое действие. В ариметическое устройство входят два блока умножения, блоки сложения чисел с плавающей запятой, сложения чисел с фиксированной запятой, сдвига,деления логических операций, преобразования чисел в дополнительный код, блок выработки условий перехода. Эти блоки арифметического устройства непосредственно связаны с внутренними регистрами, предназначенными для хранения операндов и результатов вычислений. В состав центрального процессора входят блок памяти команд, регистры номера команды, общей базы, длины поля программы, условия выполнения про грамм.

В этой вычислительной системе широко используется разграничение команд обращений к памяти и команд выполнения арифметических операций; арифметическое устройство способно параллельно выполнять несколько orjeраций, которые не связаны мезкду собой, т.е. в процессоре используется магистральная (или поточная) обра, ..,°.5, данных. Все это позволяетдоG fffn Tb в системе большой проиЭводатдльнрс.ти... . -„ Кроме того,, широко используется принцип базирования, который не позв Ьяет в полной мере применить метод повторной входимости йрограмглы, т..е, исключается:возможность одновремен:ногЬ выполнения помещенной в память програмгйл несколькими процессорами / /с/различными данными. Поэтому, например, при трансляции программ двух или брлее пользователей программатранслятор должна быть помещена в область памяти, вьщеленную оп ределенному пользователю. . : Отсутствие аппаратной реализаЦий ряда Конструкций алгоритмических язы ков не позволяет обеспечить их эффек тивную трансляцию и высокое качертво оттранслированных программ.Известны также многопроцессорные вычислйтельные системы с модульной организацией. Они более надежны, кро ме тЬго, в них несколько процессоров могут работать на общую память. Это дает вЪзможность -строить системы раз личной производительности с оптималь H@/t соотношением мощности процессоров , ёмкости ОЗУ и внешней памяти. В системе СДС 770Q находитотраже ние модульная организация. Однако в этой системе содержатся цен традьных процессора, которые могут функционировать одновременно, или вто рой процессор может, использоваться в качестве резервного . Система включает.также два процессора ввода-вывода двадцати периферийных процессоров . В системе отсутствует возможностъ наращиёанйя производительности они не позволяет удовлетворять рартуадие требования к таким характеристи кам, как экономичность, адаптивнррть Мультипроцессорный вариант вычислительной системы 370, реализованный с Я«1Мощью операционной системы OS/V52 Release 2, включает два центральныз4, Й| оцёб6ора, осн вйое запоминаюЩёё уст ройство / внешние запоминающие устройства, устройства ввода-вывода, каналы передачи входных и выходных данных, которые обеспечивают перемещение дан.ных меж,цу основным запоминающими уст ройртвами и внешними устройствами не. зависимо , от центрального процесoopaif 2/.: ,; .,. ; йграниченная рамками совместимосГ;ти система 370 сохранила набор команд системы 360 и, следовательно, ас семблерное программирование. В ней 15еал йзой а;йй вйртуальная память, мно .гопроцерсорность, блок - мультиплек ёбр нШ канал. Однако вйртуаль.ная па мя.трБ ррставляет всего 2 рлов. Этот SEnKetca следствием того, что в аппаратуресистемы 360 исполь зуется 24-разрядный адрес байта. Каждый центральный процессор содержит буферный блок памяти кэшевого типа. Проблема общих данных в ристеме решается путем выполнения операции записи одновременно в буферные; блоки памяти обоих процессоров. Подобное решение снижает эффективность использования буферной памяти. Наиболее близкой по технической сущности к данному изобретению является система фирмы Burroughs З. Эта вычислительная система содержит центральные процессоры, каждый из которых роединен двусторонними управляющими .и контрольными связями с другими центральными процессорами, процессоры ввода-вывода данных, соединенные двуртороннимиуправляющими связями с каждым центральным процессором, адресные, информационные и управлякнцие шины каждого центрального процессора и каждого процессора ввода-вывода данных через коммутатор соединены соответственно с адресными информационными иуправляющими входами и выходами основного запоминающего устройства, процессоры передачи данных, соединенные двусторонними связями с процессорами ввода-вйвода данных и подключенные входами и выходами к соответствующим выходам и входам системы, каждый процессор ввода-вывода данных через блоки управления внешними уртройствами и блоки управления внешними запоминающими устройствами соединен с соотвеЧствующими внешними устройствами и внешними запоминающими устройствами, пульт управления, соединенный двусторонними связями с процессорами ввода-вывода данных, выход пультра управления подключен к управляющим входам центральных процессоров, процессоров передачи данных и процесроров ввода-вывода данных, причем каждый из дентральных процесроров включает устройство со- пряжения, входы ивыходы которого подключены.соответственно к упомянутым входам и выходам центрального процессора, блок буферной памяти команд, блок анализа прерываний, которые соединены двусторонними связями. с устройством сопряжения и устройством управления, блок базовых, регистров/ соединенный двусторонними связями с устройством- управления и блокОм формирования процедур, выход которого подключен к входу блока буферной памяти команд, выход которого . соединен с входом блока базовых регистров , выход которого подключен к первому входу устройства формирования команд, управляющий вход устройства формирования команд подключен к соответствующему выходу устройства управления, блоки индексации, вызова значений, обработки строк, арифметическо-логическое устройство, информа ционные выходьз которых и информацион ный выход блока формирования процеду соединены с первыми информационными входами буферного стека операндов и Ассоциативного запоминаквдего устройс за, вторые информационные входы которых соединены с информационным выходом устройства сопряжения, выход буферного стека операндов подключен к первым входам блоков формирования про цедур, индексации, вызова значений, обработки строк, арифметическо-логического устройства и к третьему информационному входу, ассоциативного запоминающего устройства, выход которого соединен с третьим информационным входом буферного стека операндов и вторыми входами блока индексации и арифметическо-логического устройства, каждый процессор ввода-вывода данных включает устройство управления вводом-выводом, соединенное двусторонними связями с устройством сопряжения с процессором передачи данных и с группами каналов средней производительности и высокой производительности , которые информационными адресными и управляющими шинами через устройство сопряжения с основным запоминающим устройством соединены с информационными, адресными и управляющими входами и выходами процес сора ввода-вывода данных, входы и вы ходы устройства управления вводом-вы водом, устройства сопряжения с процессором передачи данных и упомянутых каналов соединены с соответствую щими входами и выходами процессора ввода-вывода данных. В такой, системе только два регист ра, являющиеся верхними ячейками буферного стека операндов, связаны с арифметическо-логическим устройством Это решение не позволяет реализовать параллельную обработку нескольких команд в арифметическо-логическом устройстве, т.е. реализовать поточну обработку данных. В системе используется адресация по физическим адресам с применением специальных признаков, которые указывают местонахождение затребованной информации (в основном запоминающем, устройстве или во внешней памяти.) . Когда в системе осуществляется ди намическое перераспределение объемов памяти, то требуется выполнись операции сканирования для нахождения ссылок на адреса данных, которые пер сылаются из основного запоминающего устройства на внешние запомниа1няцие устройства, выполнение этих операций связано с непроизводительными затратами машинного времени. В том случае, когда отдельные час ти сложной программы пишутся на раэ1НЫХ алгоритмических языках, например на Алголе и Фортране, и часть на Фортране Является подпрограммой любого необходимого уровня основной программы на Алголе, в известной системе при работе с массивами требуется как МИНИМУМ два обращения в память для считывания слов. При первом обращени1л считывается описатель и индексируется для формирования адреса. При втором обращении считывается нужное слово. Это снижает эффективность использования оборудования цeнтpaJ1ьнoгo процессора.. , Недостатком системы является также отсутствие возможности сопряжения каналов высокой производительности между собой. Поэтому, например, сопряжение двух или более вычислительных систем для увеличения вычислительных мощностей возможно только при использовании телефонных или телеграфных линий связи, подключаеьмх к процессорам передачи данных. Отсутствие указанной возможности не позволяет проводить тестовую проверку каналов в отсутствии внешних устройств, а также производить передачу данных из одной области основного запоминающего устройства в другую (корирование массивов) без использования центрсшьного процессора. В такой системе машинные слова сопровождаются признаком, запоминающим три разряда.. Этот признак содержит информацию для операционной системы для идентификации дескрипторов управляющих слов, обеспечения защиты памяти и описания числовых данных с удвоенной или обычной точностью. В системе сделаны первые шаги по аппаратурной реализации языка, который приближался бы к алгоритмическим средствам программирования. Однако, для сложения целых и вещественных чисел, для операций с удвоенной точностью используются разные алгоритмы. При этом требуется следить за тем, чтобы не перепутать типы и форматы чисел. Поэтому усложняется процесс создания и .отладки программ, так как, наприме программист может сделать ошибку в . определении типов и форматов данных. Целью изобретения является ПОВЬЕУСние эффектив.ности работы и обеспечение возможности наращивания вычислительных мощностей. Поставленная цель достигается тем, что в состав каждого центрального процессора введены устройство преобразования математических адресов в физические и устройство распределения адресов стека, соединенное двусторон;ними связями С УСТРОЙСТВОМ управлвния и подключенное выходом к второму входу устройства формирования команд, первый выход которого соединен с вторыми входами блоков формирования процедур, .вызова значений, обработки строк и

с третьим входом блока индексации, второй выход - с третьим входом ариф..метическо-логического устройства;- третий выход подключен к адресным входам ассоциативного запоминающего устройства и устройства преобразования математических адресов в физические, математические адресные входы которых соеди

нены, с математическими адресными выходами блоков формирования процедур, индексации, вызова значений, обработ| и строк, адресные выходы которых и сщресный выход арифметическо-логичес- . кого устройства подключены к адресным

входам устройства управления, устройства распределения адресов стека и буферного стека операндов, вход 15

которого соединен с третьим выходом устройства формирования команд, выход арифметическо-логиче кого устройства подключен к третьму входу устройства формирования команд, устрой- 20 ство преобразования математических адресов в физические соединено двусторонними связями с ассоциативным запоминающим устройством .и выходом с соответствующим входом устройства 25 сопряжения, выход блока анализа прерываний, подключен к третьму входу блока формирования процедур, управляющий выход которого соединен с cocJTветствующим входом устройства сопря- , жения, а в каждый процессор ввода-вы- вода данных введены по числу каналов высокой производительности блоки за дания направления и вида обмена, ка {сдый .из которых соединен двусторонними связями с соответствующим каналом высокой производительности и с соответствующим блоком задания направления и вида о бмена, шина связи одного из каналов высокой производительности соединена с выходом системы, второй управ- 40 ляющий вход устройства управления вводом-выводом соединен с управляющим- входом процессора ввода-вывода и входом

подачи внешних сигналовпрерывания , системы. .. 45

Этопозволяет реализовать поточную обработку команд в каждом центральном процессоре и решить проблему защиты мёЖД пользователями с помощью введейия в систему математической памяти, , когда для каждой задачи выделяется адресное пространство слов, которое расходуется во время прогона задачи. Разоёщёййость между различными :математичеекими памятями, выданными для пользователей, обеспечивая надежную защиту55

между задачами, создаетопределенные

npbt aiWiHpidfiaHHH :операци- ; онной бйсг емй; : : --v - - -i----v.;. ..

Поэтому для обеспечения большей общности адресации информации,находя- д щёйся в 1раз1ных матемйтических памяТГЙ2«7-пряййлёгйрованным процедурам

операцй6нной сйсте11йЭ 1рЖзрШа ё е:я работать.по физическим адресам. Для некоторых процедур операционной

е

;например для процедур управления памятью, пользование физическими адресата довольно естественно, так как списки памяти основываются на физических адресах.

Когда в системе используются физические адреса, указывающие на сегменты пользователей или операционной системы,: то при необходимости перемещения этих сегментов операционная система выявляет соответствующие физические адреса, которые находятся в извесных ей местах в ограниченном объеме, и производят необходимую1 коррекцию их.

Данные, которые содержат физичес.кие адреса и помещают,ся в сегменты, доступные пользователю (например в стек),снабжаются признаком неразрушаемой в обычном ре.жиме информации. При попытке записи в эти ячейки в режиме пользователя формируется сигнал прерывания, запускается процедура операционной системы, а информация остаётся неизменной. В самой процедуре не указываются математические адреса, а лишь индексные значения в массивах. Первый массив, который индексируется, это массив базовых регистров. В такой индексации с соответствующего базового регистра выбирается словоописатель (дескриптор), определяющий некоторую область данных, как правило с конкретным запуском какой-либо процедуры. После индексации этого де.скриптора получается математический адрес данных в памяти. При каждой индексации аппаратными средствами проверяется выход индексного значения за пределы описываемого массива.

Выделение под каждый очередной запрос новой области математической памяти не допускает переиспользование математических адресов. Такой метод прост и обеспечивает надежную защиту, так как исключает ситуацию, когда после уничтожения какого-либо массива. его память назначается другому сегменту и в результате сшшбочного использования зависших адресов в старой процедуре может произойти доступ к новому сегменту.

Каждое машинное слово в системе сопровождается разрядами признака, которые позволяют указывать его тип и формат и автоматически определять алгоритм операций. При таком подходе программист не сможет перепутать типы

Кроме этого, обеспечивается возможность сопряжения вычислительных систем с помощью каналов высокой производительности, что позволяет производить распараллеливание алгоритмов решаемых задач не только на уровне центральных процессоров, а и йа уровне вычислйтельньгх систем и осуществлять тестовые проверки каналов без приключения внешних устройств, либо

при логически откдюченньпс внешних устройствах.

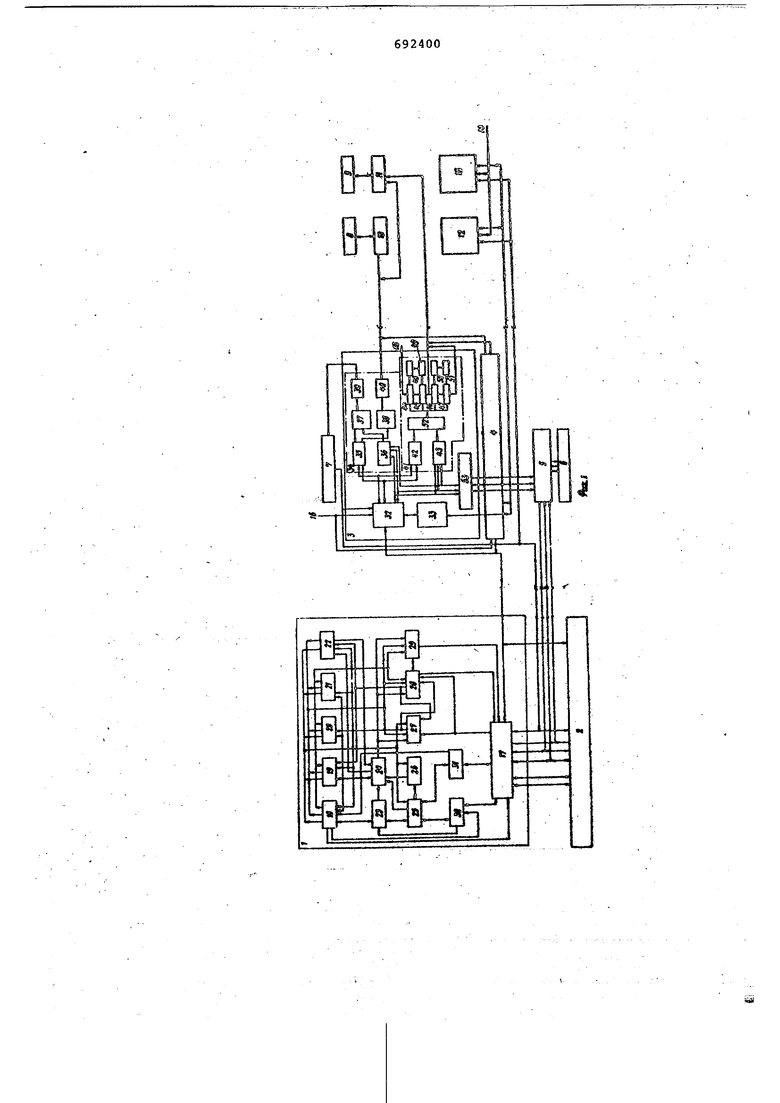

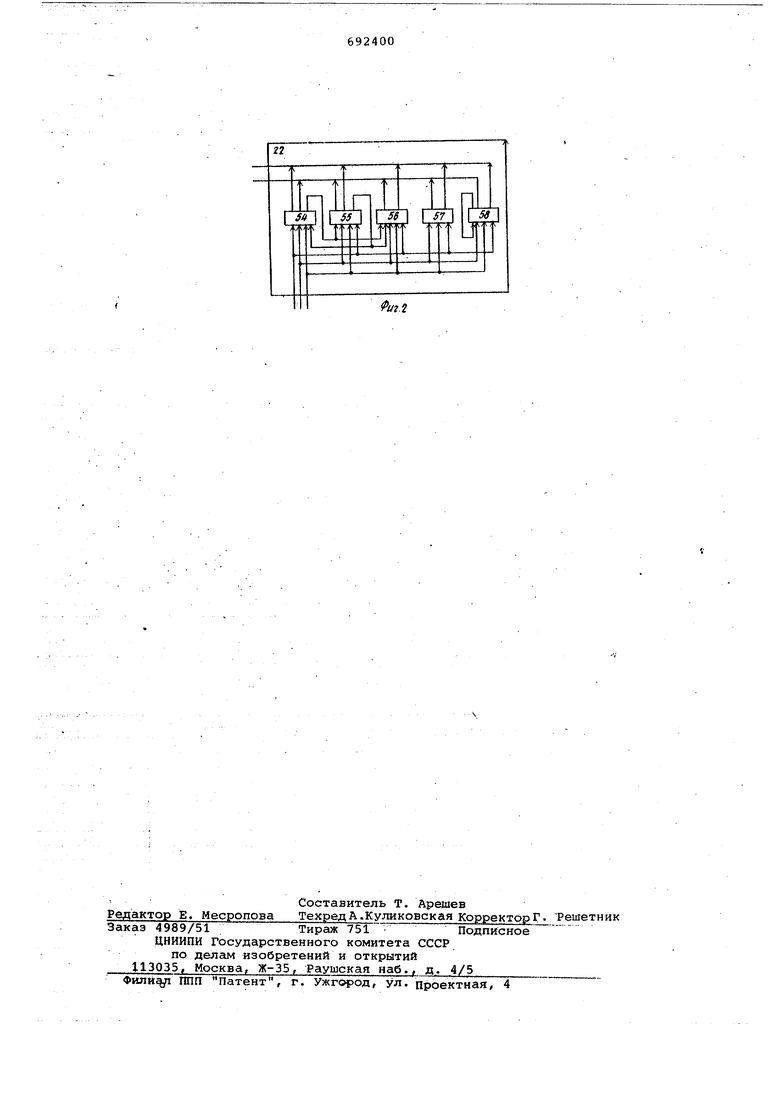

На фиг. 1 представлена блок-схема вычислительной системы; на фиг, 2 показан пример реализации арифметическо-логичес.кого устройства.

В состав вычислительной , систеьол входят центральные процессоры 1,2 (ЦП), процессоры 3,4 ввода-вывода данных (ПВВ), коммутатор 5, основное запоминающее устройство б (ОЗУ), пульт управления, внешние устройства 8 (ВУ) рнешние запоминающие устройства 9 , (ВЗУ).блоки 10 управления внешними устройствами, блоки 11 управления внешними 3 апоминаюгцими устройствами, процессоры 12, 13 передачи данных (ППД), входы и выходы 14 устройства, шина 15 связи (выход) системы, вход 16 подачи внешних сигналов прерывания систе:мы.

Каждый центральный процессор включает устройство 17 сопряжения, блок 18 формирования процедур, блок 19 индексации, блок 20 вызова значений, блок 21 обработки строк, арифметическо-логическое устройство 22, блок 23 базовых регистров, устройство 24 .формирования команд, устройство 25 управления, устройство 26 распределения адресов стека, буферный стек 27 операндов, ассоциативное запоминающее устройство 28, устройство 29 преобразования математических адресов в физические, блок 30 буферной памяти команд, блок 31 анализа прерываний.

В состав процессора ввода-вывода данных входят устройство 32 управления вводом-выводом, устройство 33 сопряжения с процессором передачи данных, группа каналов 34 средней производительности , включаквдая блок 35 связи с управлением, блок 36 связи с памятью, буферное запоминающее устройство 37, блок 38 управления, 39 40 сопряжения с управлением внешними устройствами, группа каналов 41 высокой производительности, включающая блок 42 связи с управлением, блок 43 связи с памятью, каналы 44-47, блоки 48-51, .задания направления и вида обмена, блок 52 приоритетного выбора} устройство 53 сопряжения с основным запоминагадим устройством.

В состав арифметическо-логйческого устройства (фиг, 2) входят блоки умножения 54, сложения 55, деления 56, преобразования кодов 57 и выполнения логических операций 58.

В состав вычислительной системы могут входить до десяти центральных процессоров, до четырех процессоров ввода-вывода данных, каждый из которых подключается к основному запоминающему устройству, включающему, например, до 32 модулей памяти.

Через ПВВ к системе подключаются внешние устройства, внешниё § а;П 5ННнающие устройства и линии связи. Работа с линиями связи осуществляется через ППД, который имеет свою систему команд и внутреннюю память.

Все компоненты системы динамически распределяются операционной системой для обслуживания очерёдных задач. Все центральные процессоры равноправны иработают в мультипроцесрорном режиме.

Отличительной особенностью системы команд и внутренней структуры систе0мы является приспособленность их для програ1 ширования на языках высокого уровня, что позволяет достигнуть значительного упрощения системьт математического обеспечения и осуществлять эф5фективную компиляцию nporpciMM вмашинйвй код.

Универсальный стековый механизм, выполнение команды в зависимости от типа и формата данных, рекурсивное ис0пользование процедур, работа нескольких пользователей с общими данными, практически неограниченный объем математической памяти, представляемый в распоряжение пользователей, динамическое распределение и защита памяти,

5 разветвленная система прерываний значительно облегчают программирование.

Высокое быстродействие системы достигается максимальным распараллеливанием обработки командJ перенесением

0 задачи распределения регистров ЦП с этапа компиляции программы на этап ее выполения, где эта задача решается динамически наиболее эффективным образом, выполнением обработки данных

5 в простых случаях без дополнительных издержек-, связанных с анализом типа и формата данных/ широким применением сверхоперативных ассоциативньсс запоминающих устройств (АЗУ),

0

Для достижения параллелизма в обработке команд используется организация работы по принципу поточной линии, когда в процессе обработки на разных стадиях выполнения,одновременно находятся несколько команд, а так5же имеются специализированные блоки сложения, умножения,.деления, индексации, формирования процедур, работающие параллельно и независимо один от другого. .

0

АЗУ содержит наиболее активные об-( ласти адресации ЦП, оно позволяет приблизить темп обработки команд к такту ЦП и снижает поток заявок по обращению ЦП к ОЗУ, что особенно важно для мМо5гопроцессорной системы, в АЗУ хранятся наиболее часто употребляемь1е операнды, не содержащиеся в буферном стеке операндов.

Структура центрального процессора спроектирована таким образом, чтобы

0 обеспечить высокую степень параллелизма при выполнении независимых последовательностей команд. Например, последовательнсэсти команд, соответствующие операндам X с + d, MOf-ут

5 выполняться независимо, несмотря на то, что операнды а, с и.Ь, d должны бьши бы использовать одни И те же яч ки буферного стека 27 операндов. Это Достигается благодаря тому, что пр1и выполнении команд считывания для эти (Операндов будут назначены разные яче ки. При этом принимаются меры для сохранения стековой дисциплины. Номе ра ячеек стека 27, которые назначают ся под результат каждой операции, яв ляются универсальным средством идентификации операндов в процессоре. Каждый операнд при передаче его по информационным шинам процессора сопровождается приписанным ему номеpotvi стековой ячейки. По этим номерам содержащимся в командах, блоки 18-21 опознают предназначенные для них опе ранды и принимают их на входные регистры для выполнения операции. Такой подход к передаче и приему, опера Дбвевязан с тем, что операнды могут появляться на информационных шинах в произвольном порядке относительно по следовательности дешифрации и Зс1р)анее Тнейзвестно, для какой бпёрации предназначена считываемая из ОЗУ или полученная в результате предыдущей операции информация. При отсутст вии конфликтных ситуаций каждый такт на обработку выдается новая команда. Когда на каком-либо урЬвне поточной линии В1Озникает конфликтная ситуация не позволяющая продвинуться на очередной шаг, то на всех предыдущих уровнях, содержащих команды, вырабаты ваются сигналы .блокировки, сохраняюЩйе содержш юе этих уровней до разре шения конфликтной ситуации. Блок 30 буферной памяти команд предназначен для создания необходимо запаса командных слов, обеспечивающе го непрерывную дешифрацию команд, а также для организации небольших циклов . Для управления выборкой команд в нем имеется два счетчика, один из которых служит -для выборки очередной команды на дешифрацию, а второй - для формирования запроса за очередным командным словом. Запрос в ОЗУ за командным словом формируется, когда запас слов в буфере становится меньше нёбёхбдймогбминимума. В блоке предусмотрены два регистра для приема Командных слов в направлений в гтвлёнйя. Обращение в ОЗУ за этими слова(и 1прдисхбдйтдо ТОГО, как будет рп рёлелёнб условие ветвления. Для организации циклов внутри блока на специальных регистрах запоминаются номера команд начала и конца цикла, что позволяет при работе в цикле переход 1ть с Icoнцa J aJeгp,начало. „, ,„..,.„ В блоке 3Q осуществляется предварительная дешифрация командних слО1в и формирование дополнительной информации (констант). Установка счетчика команд блока 30 вначале ос5лаествляется по скгнапам, пбступающим с пульта 7. Вызов командных слов из ОЗУ разрешается по управляющим сигналам (сигналам прерывания) , поступающим от ПВВ 3, 4, или По сигналу с пульта 7. В дальнейшем установка счетчика команд и связанных с ним регистров программной базы и программного индекса производится блоком 18 формирования процедур при выполнении команд динамических переходов , процедур и прерываний. С помощью устройства 25 управления, устройства 26 распределения адресов стека и устройства 24 формирования команд осуществляется преобразование безадресных команд во внутренний трехаДрёсный формат. При этом в качестве адресов используются номера .ячеек буферного стека 27 операндов, которые свободны в данный момент. В устройстве 26 хранятся номера ячеек буферного стека 27 операндов, упорядоченные по стековому принципу, и номера неиспольз.ованных ячеек, образующих ресурс свободных ячеек. В устройстве 26 сохраняется информация о порядке дешифрации всех выполняемых в процессоре команд. Сформированные в устройстве 24 команды выдаются на исполнение в соответствующие блоки и одновременно выполняется обращение в стек 27 за исходными операндами. При распределении команд по исполнительным блокам осуществляется проверка занятости этих блоков и хранение команд до их освобождения. Устройство 25 управления совместно с блoкoJM 31 анализа прерываний Обеспечивается восстановление состояния ЦП при прерываниях и отменах условной ветви выполнения программы. Устройство 25 дает возможность организовать автоматический режим выполнения по одной команде (без совмещения с выполнением других), останов после выполнения каждой команды, останов перед выполнением команды с заданным индексом. . .Каждая команда, передаваемая на выполнение, содержит код операции ад-, реса первого, второго операндов и результата (.адреса стека 27) , константу. В зависимости от сложности команды те или иные адреса в команде могут отсутствовать. Выдача команды и заданный исполнительный блок производится при условии его свободности по общим для группы блокрв шинам. Исполнительные блоки разбиты на две группы, в одну из которых входят блоки арифметическо-логического устройства, в другую - блоки 18-21. В сортве.тствии с этим команды с устройства 24 выдаются по двум шинам. Все свободные в данный момент исполнительные блоки 81-21 или блоки устройства 22 принимают команду, но запускается для работы лишь тот блок, которому адресована данная команда, а .Остальные блоки продолжают оставаться .свободными и воспринимают последующие команды.. . Для адресования информации по АЗУ 28 используется дополнительный пятиразрядный адрес, так как возможны слу чаи одновременного занесения информации в буферный стек 27 и АЗУ 28. Устройства 24, 25, 26 реализуются с помощью основных компонентов: регис тра операции дешифрированной команды, адресного стека выполнения, адресного стека свободных ячеек, очереди выполнения команд, узла формирования адресов исполнительных, команд, буфера исполнительных команд,- узлов формирования временной диаграммы, управляющих сигналов блокировок выполнения команд, анализа готовности команд в вершине очереди регистра опе раций очереди выполнения. Вершина стека процесса, остальная часть которого расположена в ОЗУ, размещается в ячейках буферного стека 27 операндов и предназначена для хранения промежуточных результатов при вычислении выражений. Буферный стек 27 операндов реализуется с применением интегральной памяти, коммутатора и дешифратора адресов, группы триггеров готовности информации, при оритетного узла, узла распаковки слов Имеется один канал считывания и один канал записи. Записываемая в стек 27 информация заносится в выходной р гистр стека. Такое решение примен,ено для ускоренияпроцесса передачи операндов в исполнительные блоки, а также для передачи на выходную шину стека 27 информации, считанной из ОЗ которая не должна быть помещена в буферный стек 27. В данном случае ис полнительные блоки настроены на прие информации по индивидуальным адресам Обращения в буферный стек 27 поступа ют от исполнительных блокоэ 18-2.1, устройств 17, 22 и АЗУ 28 на, коммута тор адресов, который управляется при оритетным узлом. Через коммутатор операндов поступает слово, подлежащее записи в буферный стек 27. Приоритетный узел . формирует сигнал выборки на основани имеющихся запросов. При переполнении буферного стека 27 часть его содержи мого переписывается в ОЗУ; еся.и в не не хватает операндов для выполнения операции, осуществляется подкачка . на ОЗУ. Базовые регистры блока 23 определяют адресный контекст работающей пр цезуры. Они содержат определенные ел ва (дескрипторы) тех областей математической или физической.памяти, к которым возможно в настоящий момент адресование. С помощью базовых регистров осуществляется преобразовани адресной пары.в абсолютный адрес. Адесная пара (п, 1), содержащаяся в командах вызова значений и загрузки адреса после извлечения команды из блока 30 буферной памяти команд, поступает на базовые регистры блока 23. По номеру п считывается содержимое соответствующего регистра, после чего поле адреса дескриптора складывается с величиной 1. Полученный адрес поступает в устройство 24 формирования команд. Одновременно проверяется, не превышает ли величина 1 размера описываемой дескриптором области. Ассоциативное запоминающее устройство содержит ассоциативные ячейки и предназначено для хранения и быстрой выборки наиболее часто используемых данных. Для считывания инф.ормации из памяти математический адрес (МА) подаётся на вход ассоциативной части, где он одновременно сравнивается с содержимым всех ассоциативных регистров. Если сравнение происходит, то считанное слово спустя такт появляется на выходной шине АЗУ, а затем поступает в буферный стёк, на входные регистры блока 19 и блоков устройства 22. Если требуемая информация обнаруживается в АЗУ,то обращение в ОЗУ блокируется.При выполнении операций записи информации пишется безусловно как в АЗУ, так и в ОЗУ. Если считываемого или запи.сы вгемого слова не оказывается в , то под него отведена ячейка, к которой дольше всего не было обращения. Ассоциативное запоминающее устройство реализуется с помощью ассоциативных регистров, интегральной памяти, схем сравнений адресов, узлов приоритетного выбора запросов, упаковки слов, управления общими данными параллельных процессов, проверки совпадения адресов записи и считывания, контроля, коммутаторов адресов данных и интегральной памяти, выходного регистра математического адреса, выходного регистра данных и узла задания очередности использования ячеек памяти. Устройство 29 предназначено для преобразования математического адреса в физический адрес ОЗУ. Оно содержит 32 строки таблицы страниц. Математи- . ческий адрес поступает одновременно на АЗУ 28 и устройство 29.. Если соответствукнцая строка таблицы страниц находится в устройстве 29, то спустя такт на его выходе появляется физический адрес. К моменту появления физического адреса на выходе устройства 29 в АЗУ формируется сигнал управления выдачей этого Адреса в устройство 17 сопряжения. Если информация,по исходному математическому адресу была иайдена в АЗУ, выдача физического адреса блокируется, в противном случае производится счИ№вание информации из ОЗУ. Кроме физического адреса начала

Страницы ответная часть устройства 29 содержит поле размера страницы для осуществления контроля по выходу за пределы страницы . В случае; когда страница отсутствует, тр нужнцй математический адрес запоминаетсй и затем пе- .

редается в блок 18, с помощьнз которо- 5 го осуществляется аппаратный поиск по таблице страниц, расположенной в ОЗУ, и найденная строка заносится в устройство 29 на место ячейки, к которой дольше всего йе было обращения. Q

В ОЗУ математическим страницам соответствуют страницы переменной длины в соответствии с их фактическим

размером. Они размещаются произвольным образом, т.е. адрес начала стра- 15 няцы яйляется полноразрядным физическим адресом. Адрес слова в ОЗУ определяется сложением адреса начала страницы с адресом слова внутри страницы. Такой способ размещения страниц по- 20 зволяет уменьшить количество незаполненных областей в ОЗУ /и тем самым повысить эффективность ее использования. В ка5кдой ячейке ассоциативной части устройства 29 содержится математичес- jc кий адрес страницы, признак действительности /значимости ) математического адреса, контрольные разряды, признак страницы пользователя, а в ответной - физический адрес начала страницы и ее размер, сопровождаемые конт-30 рольными разрядами. Устройство реализуется с помощью схем сравнения входного .математического адреса с мате- матически.ми адресами, хранящимися в ассоциативной части. Запросы на об- 35 ращение к устройству 29 от блоков 18-21 анализируются узлом приоритетного выбора запросов.

Ассоциативная часть устройства 29 выполнена на регистрах, ответная част.ь40 реализована с использованием интеграль.нрй памяти. В устройстве предусмотрены цепи обращения к ОЗУ непосредственно по физическому адресу, принимаемому во входной регистр. В этом . случае разряды-физического адреса . Й0мё{цак1тся в поле младших разрядов математического адреса и либо сопровождаются признаком физического адреса, либо старшие разряды поля мате - 50 матического адреса находятся в нулевом .состоянии, что в обоих случаях является указанием обращения по физическому адресу. . Во входной регистр устройства 29 принимается признак блокировки мате- 55 матического адреса и признак стирания математического адреса.Признак блокировки формируется запрашиваю цйм блоком ЦП для того, чтобы сохранить математический адрес страницы, Q отсутствующей в устройстве, в регистре, который предназначен длЙ этого.

При поступлении признака стирания осуществляется исключение страницы с матёматическйм адресом, записанным во 5

входном регистре, путем установки в нулевое состояние разряда значимости..

В состав устройства, кррме перечисленных узлов, входят сумматор, узлы управления, контроля и поиска ячейки для записи новой строки таблицы.

В системе предусмотрена возможнрст для программиста организовать вход в процедуру и возврат из процедуры.

В аппаратуру заложены алгоритмы смены окружения при входе и возврате ориентированные на блочную структуру программ, но удобные и для статического распределения памяти, которые запускаются однобайтовыми командами Вход и Возврат. Аналогично предусмотренному входу в процедуру аппаратно реализуются случайный вход и уход на процедуру прерывания. Необхрдимые действия выполняются с помощью блока 18 формирования процедур, который участвует в выполнении операций, связанных со входом в процедуры и возвратом, а также в выполнении команд перехода. Блок 18 обменивается информацией с базовыми регистрами блока 23, считывая и заполняя их при смене окружения, буферным стеком операндов 27 и с ОЗУ 6, формируя и используя связывающую информацию, отражающую динамически возникающие и статически заданные связи процедур.

При прерываниях блок 18 организует считывание специального слова (метки прерывания) и вход в процедуру прерывания. Кроме того, блок 18 выполняет операции откачки и подкачки при регулировке состояния буферного стека операндов, производит поиск по таблице страниц, выполняет операции взаимодействия центральных процессоров) считывания и записи регистров ЦП. . ..

Блок 18 получает команду для вылолнения с устройства 24 вместе с адресами операндов буферного стека 27. Операнды пр1инимаются во входной ре- гистр.

ОбЕ а1дение в буферный стек 27 и ОЗУ осуществляется через выходной KOi nnyтатор блока 18. В ячейках буферной памяти-блока размещаются адреса и указатели, относящиеся к о эганизации работы стека, к таблицам страниц пользователя и таблицам страниц системы. Для формирования связующей информации используется сумматор и соответствующие регистры.

Для управления сменой окружения слу5кит ряд схем сравнения и два ре1гистра признаков. В блоке 18 прове- , ряётся условие при динамических переходах, в нем содержится регистр конфигурации и таймер.

В. блоке 18 формирования процедур осуществляется хранение указателей, описывающих состояние стека (области математической памяти, в которой динамически размещаются локальные данные и рабочие области процедур задачи) ; корректировка указателей при подкачке, откачке, процедурных операциях; считыван ие, формирова ние, из менение и запись связующей информации, в которую могут заноситься состоянйе триггеров блока 18 или других блоков центрального процессора; выборка дескриптора программного сег мента по информации в специальных сл. вах (метке .или управляютдего слова возврата); выдача дескриптора программного сегмента и номера команды в блок 30 буферной памяти команд; уста :Новка триггеров режима при входе, восстановление при возврате; коррекция базовых регистров при входе, воз врате, динамическом переходе; задани номера уровня, на котором работает процедура и определение базовых регистров, к которым можно адресоватьс по адресной паре. С помощью блока 18 осуществляются операции входа в процедуру случайног входа в прерывание, возврата из процедуры, динамического перехода и непосредственного перехода, смены стек поиска страницы формирования метки, подкачки и откачки, считывание регис ров и запись в регистры процессора. Кроме того, выполняются операции вза имодействия центральных процессоров ,системы: прерывание других процессоров - выдаются сигналы прерывания центральным процессорам и ПВВ,указа ным в операнде, поступающим из стека ответ процессора - выдается на процессоры, указанные в операнде. При выполнении опера;ции Ждать из стека поступает операнд, операция заканчивается, когда от всех ЦП, ука занных в операнде, поступают сигналы, причем учитываются сигналы, пришедшие дО начала операции, но после предыдущей операции Ждать. Блок .18 исполняет также команды блокировки внешних прерываний, при этом устанавливается триггер (маска внешних прерываний). Выполняемые в блоке операции проверяются с помощью схем контроля. Блок 19 предназначен для выполне.ния операций индексации, формирова-. ния индексных слон, изменения размер ности массива, взятия подмассива и операций конца цикла. Он реализуется с Помощью регистроь кода операций, дешифратора, схем сравнения адресов для управления приемом операндов, регистров индекса, дескриптора, мате матического адреса ряда сдвигатёлей, сумматора, ряда коммутаторов и узлой управления., Блок 21 предназначен для обрабокт символьной (алфавитно-цифровой, цифровой и битовой информации, перемещ ния массивов в памяти, поиска информации по заданным признакам, сравнения массивов. Он выполняет следующие операции: пересылки слов, пересылки элементов с проверкой отношения и, безусловно, пересылки по шкале, пересылки с переводом и редактированием пересылаемой информации, упаковки и распаковки, поиска по маске, просмотра связанного списка сканирования эталоном, сканирования по шкале, считывания и установки триггеров. Кроме того, блок 21 производит преобразование упа:кованного массива в набор при считывании по- косвенному слову и. преобразование набора и упакованный массив при записи набора. В операциях обрабатывается один или несколько массивов и с каждым массивом связывается указатель массива,состоящий из деск- , риптора и индекса. В качестве индекса может быть целое, битовой набор и индексное слово. Блок 21 реализуется с применением регистра исполнительной команды, буферных регистров, узлов модификации индексов, формирования математического адреса, обработки, узЛа анализа перекрытия массивов и узлов контроля Блок 20 вызова значений предназначен для обращения в ОЗУ за данными для анализа типа поступивших данных по сопровождающим их признакам, установления факта выполнения. задан ой операции или организации повторного считывания данных в случае поступления, например, косвенного слова или дескриптора. . Реализуется данный блок с применением регистров, узлов анализа, принятых в регистры данных, и узлов формирования запросов на обращение в память для считывания иЛи записи данных. С помощью блоков арифметическо-логического устройства 22 выполняются операции сложения, вычитания, умножения, преобразованиякодов, логические операции. Кроме того,, в нем выполняются операции взятия поднабора, взятия элементов, обнуления элементов, установки единичного значения элементов, вставки подна боров и величины; операции сцепления наборов, подсчета числа единиц, нахождения номера первой единицы, операции над типами и форматами (например считывание типа-Формата,( проверка типа-формата.) , преобразования типов в битовый набор, битового набора в любой тип. Каждый блок устройства 22 реализуется с помощью входных регистров приема адресов из устройства 24, приема операндов из буферного стека 27 и АЗУ 28, а также приема адресов и операндов с других блоков устройст.ва. Блок 58 выполнения логических операций, кроме- того, принимает адреса и операнды со своего выхода. Перекрестные связи между блоками устройства 22 позволяют сократить вре мя передачи операндов, если в Kaj bMлибр, блоке одним из операндов является результат выполнения предыдуще операции.; . Кроме того, каждый поступающий на арифмётйческо-логическое устройс ё6 бгтерамд сопровождается признаком типа и формата-данных. Аппаратньми средствами осуществляется распознав ние признака, преобразование типа или .формата, при необходимости, и .з пуск операции, выполняемой по одном алгоритму, заложенному в соответств Щйй блок арифметическо-логического стройства. .,.... Каждый процессор ввода-вывода 3, 4 бсущёствляет передачу информации между ОЗУ и внешними устройствами. двки за обме.н ПВВ получает из рч.ере ДЙ требований, которые центральййй; йрбцёссор формируети записыв.ае В . ОЗУ. Поэтому задача операционной Системы сводится к записи очередей требований в ОЗУ. и прерыванию ПВВ. Всю дальнейшую работу по обмену - з пуск внешних устройств, передачу ин Ф6р1мацйи и завершение обмена - ПВВ йБГЯЬЯняет. автономно ИасиЯхронно с paboTolft центральных процессоров. ПВВ состоит из нескольких функцио.нально самостоятельных частей, которые в процессе обмена работают асинхронно Все передачи данных между ОЗУ и любьам из внешних устройств выполняются через устройство 53 сопряжения с ОЗУ под управлением устройства 32. Каждая группа каналов 34 средней про изводительности и каналов 41 высокой производительности имеет (на фиг. 1 покёзаны по одной группе каждого типа) свои-блоки 35, 36, 42, 43 связи и блоки 39, 40 сопряжения. Связь между внешними устройствами ;и саналами осуществляется через блоки 10 и 11 управления внешними устройс.твами и управления внешними за, помин а ощими устройствами. С помощью устройства 33 осуществляется сопряжение ПВВ с процессорами передачи ;цанныхч.. В блоке 11 предусмотрены коммута TCiJ5ayKOtopiiie дают возможность любому ПВВ связаться, например, с любым накопителем на магнитном барабане или диске. Едоки 48-51 задания направления и вида обмена поэволяют изменять логику работы каналов. Канал с его поЙощью может быть переведен в режим работы блокауправления внешними устройствами, т.е.. канал може.т функ - 1В&й1йр5вате в нормальном режиме ка:Нала йли в режиме внешнего устройст ва. . Процессор ввода-вывода управляет вьябором пути к требуемому устройству Если в данный мОмент все пути к требуемому внешнему устройству зайяты, ePfW ajteKa откладывается до освО- бождения любого из путей. Эта работа выполняется ПВВ без участия центрального процессора. Карта работ, создаваемая операционной системой, состоит из следующих элементов: базовая команда, таблица устройств, таблица очередей, дескриптор выполненных работ, элементь управления вводом-выводом. Вазоваякоманда считывается ПВВ после получения прерывания от центральноГ9 процессора. Только одна команда (пуск обг,екта)-требует доступа ко всем элементам карты работ и является основной командой организации обмена. Остальные команды обеспечивают загрузку, управление работой процессоров передачи данных, установку конфигурации системы, используются для диагностических целей. .В слове таблицы устройств содержится информация о типе устройства, способе его подсоединения к ПВВ, фазе работы по обмену. Каждое слово из таблицы устройств имеет разряд, который позволяет блокировать обращение к слову всех центральных процессоров и процессоров ввода-вывода. Блокировку снимает тот ЦП или ПВВ, который закончил работу с этим устройством или с его элементами карты работ. В таблице очередей указываются адреса первой и последней заявок на работу. Таблица очередей доступна центральному процессору, который достраивает очередь к устройству с конца и изменяет адрес последней заявки. По. мере выполнения заявок на обмен ПВВ сообщает об этом поотве.тствующей записью в очередь выполненных работ. Дескриптор выполненных работ определяет очередь, в которую входят: все. требования на ввод-вывод, указанные в соответствующих запросах, которые были обслуженыИ закончили свою работу; любые ошибки, связанные и не связанные с обменом, которые были зафиксированы процессором ввода-вывода. Устройство 32 управления вводом-выводом организует выбор пути и передачу информации между внешними устройствами и ОЗУ, формирует управляющие слова и передает их в каналы для запуска внешних устройств. Устройство 32. сообщает операционной системе об окончаний работы и результатах обмена, а такясе сообщает об обнаруженных в процессе обмена ошибках; оно осуществляет взаимодействие ПВВ с операционной системой через карту работ. Реализуется устройство с помощью |регистров базовых адресов, используеiiHx для доступа к элементам карты работ, содержит базовые адреса базовой команды, слова таблицы устройств, таблицы очереди работ и очереди выполненных работ; регистров рабочих слов, содержащих информацию о виде и состоянии работ и об адресах связи по памяти. В процессе; выполнения заявок информация этих регистров меняет ся. Кроме того, в состав устройства входит блок памяти, используемый для хранения информации о работающих каналах. , В случае запуска устройства в ячей ку блока памяти, выбранную по номеру кана;1а, записывается номер запущенного устройства и разряд занятости этого канала. . В блоке очередных работ устройства 33 хранятся стоя1дие на очереди не выполненные работы,- в нем запоминают ся признак невыполненной работы и но мер устройства. Если сигналы прерыва ния от ЦП отсутствуют, то выполняютс заявки по приоритету: пуск (окончание) , круговой обход сканирования. Блок окончаний устройства 33 используется для выбора номера окончив шего работу- канала и завершения обслуживания заявки со стороны канала. В устройстве также применяются регис ры приема и выдачи рабочих слов, узлы управления временной диаграммой и элементы, контроля. Запускается уст ройство 33 по сигналу прерывания, по ступающему от центрального процессора.. Каждый канал средней производительности выполнен в соответствии со стандартным интерфейсом ввода-вывода ЕС ЭВМ; работает он в монопольном ре .жиме, т.е. операция ввода-вывода начинается и завершается на внешнем ус ройстве. за одно логическое подключение его к интерфейсу. Группа высокопроизводительных каналов 41 предназначена для осуществл ния обмена систем с такими быстродействующими внешними запоминающими устройствами, как накопители на магнитных барабанах, дисках, а также для выполнения межсистемных обменов по типу канал - канал. В пределах некоторого отрезка вре мени каждый канал может выполнять только одну операцию передачи данных, т.е. канал монополизируется уст ройством для выпфлнения всей операции обмена. Исключение составляют условные операции при работе со смен -ными магнитными дисками, если требуг ётся позиционирование. В этом случае канал освобождается на время позиционирования и может опера-т цию ввода-вывода с другим накопителем. Режим работы канала высокой производительности задается управлянвдим словом канала, которое поступает из устройства 32 во время запуска канал В зависимости от кода операции управлякяцего слова канала воэмоукны спе дующие режимы работы: обмен, массовы обмен, межсистемный обмен, внутренни обмен, тестовая-проверка. В режиме обмена управляюшее слово канала содержит начальный физический адресмассива в оперативной памяти и размер массива в словах. Канал передает указанный массив на внешнее устройство, либо записывает информацию, полученную от внешнего устройства, в заданную область ОЗУ. Массовый обмен отличается от режима обмена тем, что за один запуск канала пройзйбдй тся §§Ьд йЛй вйвод Мае-сива информации из (в) нескольких областей ОЗУ на (с) одно и то же внешнее устройство. В этом случае массив обмена в ОЗУ располагается не непрерывно, а состоит из нескольких областей памяти, описываемых таблицей дескрипторов. Каждый дескриптор таблицы содержит начальный адрес и размер области памяти, откуда или куда передается информация. Начальный адрес по внешнему накопителю и код операции задаются. один раз в начале операции. Такой режим позволяет сократить работу операционной системы.и ПВВ, так как заявка на управление вводом-выводом формируется операционной системой не на каждый отдельный массив обмена, а на весь массив информации вцелом, заданный посредством таблицы дескрипторов. В режиме межсистемного обмена, когда два канала разных ПВВ связаны между собой непосредственно, один из каналов является инициатором обмена, другой канал воспринимает его как внешнее устройство. В режиме внутреннего обмена информация пересылается из одной области ОЗУ в другую без участия внешнего магнитного накопителя. Коммутация.каналов в этом режиме задается операционной системой . Для получения информации о состоянии внешнего устройства введен режим тестовой проверки. В этом режиме по требованию канала от внешнего устройства запрашивается слово состояния, а при получении его формируется дескриптор результата, которь1й затем пересыпается в устройство 32. Управление режимами работы высокопроизводительных каналов осуществляется с помощью блоков 48-51 задания на-( правления и вида обмена. Каждый из указанных блоков реализуется с использованием формирователей сигналов управления, формирователей последовательностей сигналов интерфейса и регистра управления. Канал в этом случае получает команду от другого канала, переведенного в режим работы внешнего устройства, воспринимает ее как дескриптор результата и помещает его на регистр управления. Затем дескриптор результата выдается в устройство у-правлен я Ъводо м-:вйводом, и остается занятым в ожидании запуска. Работа с линиями связИ, по кото Е5ЙМ 6сущёствля.ется обмен данными с улаленными объектами (телефонные и телёграфнйе каналы, линии связи с уд леннами терминальными устройствами) выполняется с помощью процессора пе .редачи данных. Этот процессор предн начеи для выполнения всех основных функций, связанных с приемом и выдачей данных и предварительной обработ кой информации (обнаружение и неправ .ление ошибок, трансляции кодов, сбор ка и разборка символов). Все операции, связанные с обр:аЪот Шй1ипересылкой дНЙШЖ7 К 3 про-изводиться как над отдельными, байтами, так и нал группой байтов. ППД рёайизуется с примейёнйём уст ройств сопряже.ния с линиями, блоков формирования времени, управления, сравнения, рёгистрбв общего назначе ния, блока буферной памяти, устройст - бП Й ён спроцёссораии ввода-вы водами с местной опёративной памяты суг 1матора базового адреса, устройства обработки прерываний, регистра ко манд дешифратора адресов и арифметическо-логического блока, выполняю7 wef6 6nei5aiiHH с:лЬясёнйя, вычигания и яЬгйчёские операции. При обработке запроса из местной оперативной памяти считывается управ ляющая группа слов, в которых записа на вся йнформация, необходимая для работы программы, обслуживающей данную линию. Пульт 7 управления совместно с операционной системой осуществляет управление работой вычислительной системы, управление режимами работы входящих в нее устройств, индикацию СОСТОЯНИЯ устройств. В каждом це.нтральном процессоре, процессоре ввода-вывода данных и ОЗУ ймёется регистр конфигурации, со--дё{5)кййоё которого Может задаваться с пульта управления путем формироваяиясигнала установки исходного состояния, либо, программно путем данных. Поступающих от операционной сиетёмы; Гк-Шйаей дайТРа-льном процессоре содержится, схема формирования сигналов запуска остановленного ЦП при пэстуйтшнйи сигнала запроса от друрих ЦП или ПВВ. . . Передача сигналов прерываний от ЦП к ЦП имеет место во время перврначёлbiioro запуска системы, при необ ходимости освободить определенный пр цессор и в других подобных случаях, когда необходима синхронная работа процессоров. : Йрй:-1ИШтупленйИ еигналов прерываний/ от ПВВ центральный процессор фор ййр ётё11ГгНвл ответам каз1эдому ПВВ 3 наобслуживание в зависимости от соiMpW-e aia ;-.. -- .-.., л - :; л ч.;.,. / : - , .СТОЯНИЯ запрашиваемого центрального процессора. Сигнал отказа обслуживания формируется в том случае, когда в центральном процессоре маскируется прием внешних прерываний или уже имеется более приоритетный запрос. Установка единичного значения соответствующего разряда регистра конфигураций ОЗУ означает, что модуль, являющийся составной частью ОЗУ, может обмениваться данными с соответствующим центральным процессором 1, 2. или процессором. 3, 4 ввода-вывода данйых. . Вь1вод устройства из работающей системы, например, для устранения неисправностей, осуществляется по указанию оператора, когда от операционной системы поступает разрешение вывода. 11еред тем кзк выдать оператору сообщение о разрешении вывода устройства из состава системы, операционная система вводит в регистры конфигураций запрет на прием сигналов прерываний от выводимого устройства. Изобретение в отличие от прототипа позволяет реализовать параллельную обработку команд, т.е. поточную обработку данных; осуществить обращение в ОЗУ по физическим .адресам, известным операционной системе, и по математическим адресам, и.тем самым сократить непроизводительные затраты машинного времени, связанные с поиском зависших адресов при осуществлении динамического перераспределения памяти, и решить проблему защиты между пользователями;сократить количество обращений в ОЗУ при работе с программами, отдельные части которых написаны на разных языках (АЛГОЛ, ФОРТРАН); осуществить сопряжение вычислительных систем с помощью высокопроизводительных каналов и осуществлять тестовую проверку канатов при отсутствии внешних устройств. Введение разрядов признака для всех типов слов, циркулирующих в системе, позволяет автоматически опредёлять алгоритм Выполняёмь1х операций, что упрощает программирование и повышает эффективность защиты программ пользователейi Аппаратурная, реализация фундамен-, тальных функций операционной системы,. например процедурных и функций поиска по таблицам страниц, операций синхронизации. процессов, операций смены стека, также дает возможность повысить эффективность работы системы. ...... .. , . .... ...... . J, -л- - - .. - , . -- - Формула изобретения ВЫЧиеййШй1 Шй1:гиётё1йа; содержащая центральные процессоры, каждый из коfbpEei co Sareft двуйторонйими управляю ИМИ и контрольными связями с другими центральными процессорами, процессоры ввода-выврда данных, соединенные двусторонними управляющими связями с каждым центральным процессором, адрес ные, информационные и управляющие шины каждого центрального процессора и каж дого процессора ввода-вывода данных , через коммутатор соединены, соответственно с адресными информационными и управляющими входами и выходами основ ного запоминающего устройства, процес соры передачи данных, соединенные дву сторонними связями с процессорами вво да-вывода данных и подключенные входами и выходами к соответствующим вхо дам и выходам системы, каждый процессор ввода-вывода данных через блоки управления внешними устройствами и блоки управления внешними запоминающими устройствами, соединены с соответ ггвующими внешними устройствами и внеш ними запоминающими устр&йствами, пуль управления, соединенный двусторонними связями с процессорами ввода-вывода данных, выход пульта управления под-. ключен к управлянядим входам центральных процессоров, процессоров передачи данных и процессоров ввода-вывода дан ных, причем каждый из центральных про цессоров включает устройство сопряжения, входы и выходы которого подключены соответственно к упомянутым входам и выходам центрального процессора блок буферной памяти команд, блок ана лиза прерываний, которые соединены двусторонними связями с устройством сопряжения и устройством управления, блок базовых регистров, соединенный двусторонними связями с устройством управления и блоком формирования процедур, выход которого подключен к входу блока буферной памяти команд выход которого соединен с входом блока базовых регистров, выход -которого подключен к первому входу устройства формирования команд, управляющий вход устройства формирования команд подключен к соответствукяцему выходу устройства управления, блоки индексации, вызова значений, обработки строк арифметическо-логическое устройство информационные выходы которых и информационных, выход блока формирования процедур соединены с первыми ин.1{1Ормационными входами буферного стека операндов и ассоциативного запоминающего устройства,вторые информационные входы которых соединены с информацион -ным выходом устройства сопряжения, вы ход буферного стека операндов подключен к первым входам блоков формирова ния процедур, индексации, вызова значений, обработки строк, арифметическоглогического устройства и к третьему информационному входу ассоциативного запоминающего устройства, выход которого соединен с третьим информационным входом буферного стека операн дов и вторыми входами блока индексации и арифметическо-логического устройства, каждый процессор ввода-вывоа данных включает устройство управления вводом-выводом, соединенное двусторонними связями с устройством сопряжения, с процессором передачи данных и с группами каналов средней производительности и высокой производительности, которые информационными, адресными и управляющими шинами через устройство сопряжения с основным запомина501цим устройством соединены соответственно с информационными, адресными и управляющими входами и выходами процессора вво;(а-вывода данных, в.ходы и выходы устройства управления вводом-выводом, устройства сопряжения с процессором передачи данных и каналов средней производительности и высокой производительностисоединены с соответствуккдими входами и выходами процессора ввода-вывода данных, о тличающаяся тем, что, с целью повышения эффективности работы и обеспечения розможности наращивания вычислительных мощностей, в состав каждого йентральногопроцессора введены устройство преобразования математических адресов в физические и устройство распределения адресов стека, соединенное двусторонними, связями с устройством управления и подключенное выходом к второму входу устройства формирования команд, первый выход которого соединен с вторыми входами.блоков формирования процедур, вызова значений, обработки строк и с третьим входом блока индексации, второй выход - с третьим входом арифметическологического устройства, третий выход подключен к адресным входам ассоциативного запоминающего устройства и устройства преобразования математических адресов в физические, математические адресные входы которых соединены с математическими адресными выходами блоков формирования процедур, индексации, вызова значений,обработки строк, адресные выходы которых и адресный выход арифметическо-логического устройства подключены к адресным входам устройства управления, устройства распределения адресов стека и буферного стека операндов, вход KO-I торого соединен с третьим выходом устройства формирования команд, выход арифметическо-логического устройства подключен к третьму входу устройства формирования команд, устройство преобразования математических адресов в физические соединено двусторонними связями с ассоциативным запоминаихцим устройством и выходом С соответствующим входом устройства сопряжения, выход блока анализа гтрерываний подключен к третьему входу блока формирования процедур, управляющий выход которого соединен с соответствующим входом уст|ройства сопряжения, а в каждый проlieccop ввода-вывода, данных введены по числу к;анапов высокой производительности блоки задания направления в вида обмена, каждый из которых соединен ЙвУсторонними связями с соответствующим каналом высокой производительности и с соответствующим блоком задания направления и вида обмена шина связи одного из каналов высокой производительности соединена с выходом системы, второй управляющий вход устройства управления вводом-выводом соединен с управляющим входом процессора ввода-вывода и входом подачи внешни сигналов прерывания системы.

Источники информации, принятые во внимание при зкспертизе

Авторы

Даты

1980-08-07—Публикация

1977-05-20—Подача