Изобретение относится к вычислительной технике и может быть использовано для распаковки командной информации в конвейере команд процессоров с сокращенным набором команд

Известно устройство, содержащее блок регистров команд, блок управления выборкой команд и блок управления, причем информационный вход устройства соединен с информационным входом блока регистров команд, выход которого является информационным выходом устройства, первый выход блока управления соединен с управляющим входом блока регистров команд первый выход блока управления выборкой команд является адресным выходом

устройства, мультиплексор, дешифратор и блок хранения команд перехода, содержащий регистр сдвига, элемент задержки, элемент НЕ,элемент ИЛИ, две группы элементов И, группу сумматоров по модулю два, две группы регистров, группу элементов ИЛИ, блок управления выборкой команд содержит элемент И, три элемента ИЛИ, сумматор по модулю два, параллельный накапливающий сумматор, два мультиплексора и счетчик, а блок управления содержит группу элементов ИЛИ, группу элементов И, элемент ИЛИ и регистр сдвига, причем первые входы сумматора по модулю два группы блока хранения команд перехода соединены с выходами счетчика параллельного наХ|

О

ю со о

VI

капливэющего сумматора, элемента И и первым выходом блока управления выборкой команд, входы адреса перехода устрой- сгва соединены с первыми входами элементов И первой группы, с входами элемента ME и элемента задержки, с информационными входами регистров первой и второй групп блока .хранения команд перехода, выход элемента ИЛИ и выходы элементов ИЛИ группы которого соединены с первыми группами информационных входов первого и второго мультиплексоров, с первыми управляющими входами первого и второго мультиплексоров и с первым входом первого элемента ИЛИ блока управления выборкой команд, вторые группы информационных входов первого и второго мультиплексоров которого соединены с группой входов адреса команд устройства, вторым входом первого элемента ИЛИ, с вторым и третьим управляющим входами первого и второго мультиплексоров блока управления выборкой команд, инверсный вход элемента И соединен с разрядным выходом регистра сдвига блока управления, выходы элементов ИЛИ группы которого соединены с первым выходом этого блока, первый и второй входы элемента ИЛИ, установочные входы регистра сдвига и первые входы элементов И группы которого соединены с установочным входом устройства, первый и второй входы сумматора по модулю два блока управления выборкой команд соединены с первым и вторым входами элемента ИЛИ этого блока и с выходом мультиплексора, первый и второй входы которого соединены соответственно с информационным входом устройства и с выходом дешифратора, группа входов которого соединена с группой выходов параллельного накапливающего сумматора блока управления выборкой команд, выход первого элемента ИЛИ которого соединен с первым входом третьего элемента ИЛИ этого блока и с входом запуска блока регистров команд, а в блоке управления выборкой команд выходы первого и второго мультиплексоров соединены соответственно с первым входом счетчика и входом параллельного накапливающего сумматора, разрядный выход которого соединен с вторыми входами счетчика и третьего элемента ИЛИ, выход которого соединен с прямым входом элемента И, выходы сумматора по модулю два и второго элемента ИЛИ соединены с третьей группой информационных входов второго мультиплексора, а в блоке управления вторые входы элементов И группы соединены с соответствующими выходами регистра сдвига, выходы элементов И группы соединены с первыми входами элемента ИЛИ группы, вторые входы которого соединены с выходом элемента ИЛИ и с соответствующим установочным входом регистра сдвига,

а в блоке хранения команд перехода выходы регистра сдвига соединены с вторыми входами соответствующих элементов И первой группы, выходы которых соединены с первыми управляющими входами регистров

0 первой и второй групп, вторые управляющие входы последних соединены с выходами соответствующих элементов И второй группы и с соответствующими входами элемента ИЛИ, выходы регистров первой груп5 пы соединены с вторыми входами соответствующих сумматоров по модулю два группы, выходы которых соединены с входами соответствующих элементов И второй группы, выход каждого регистра второй

0 группы соединен с соответствующими входами всех элементов ИЛИ группы, выход элемента НЕ : соединен с вторыми управляющими входами всех регистров первой группы, выход элемента задержки соединен

5 с входом регистра сдвига.

Кроме того, блок регистров команд содержит группу регистров, информационные входы которых соединены с информационным входом блока и с первыми выходами

0 предыдущих регистров группы, а первый управляющий вход каждого из регистров группы соединен с управляющим входом блока и с вторым выходом предыдущего регистра группы, вход запуска блока соединен с вто5 рыми управляющими входами регистров группы, а выход блока соединен с выходами первого регистра группы, выходами первых тридцати двух разрядов и вторым разрядом выходом второго регистра группы.

0 Известно также устройство, содержащее первый и второй буферные регистры команд, первый, второй и третий мультплек- Соры, счетчик адресов команд, D-триггер полуслова, первый и второй D-триггеры

5 формата, D-триггер блокировки, первый, второй и третий элементы ИЛИ, с первого по девятый элементы И, первый и второй элементы НЕ и элемент НЕ-И, причем выходы первого, второго и третьего мультиплек0 соров являются выходами первого, второго и третьего полуслов устройства. В устройстве имеются также выход признака типа адресации команд устройства, выход адреса команды устройства, выход запрета выдачи

5 команды устройства, выход запроса следу ющего слова команды. Информационный вход буферного регистра команд является входом команд устройства. В устройств имеются также первый синхровход уст рои ства, вход разрешения приема команды vr

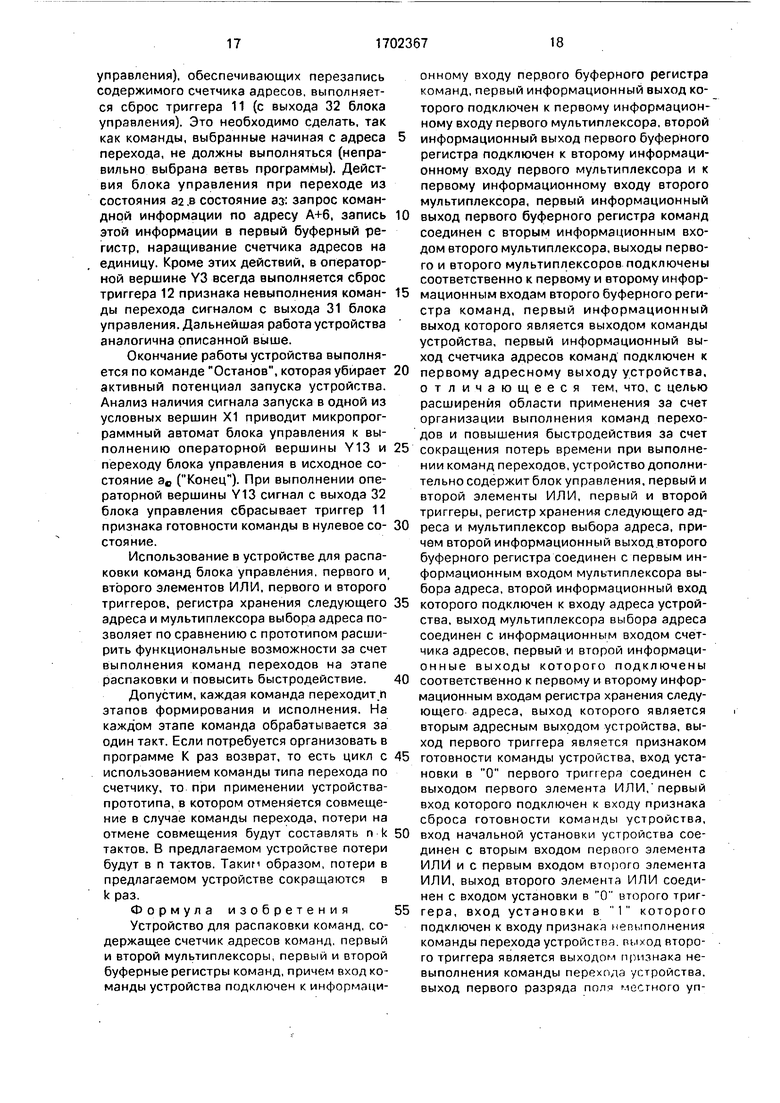

второго буферного регистра б команд, первый информационный выход которого является выходом 35 команды устройства, первым адресным выходом 37 которого является первый выход счетчика 7 адресов, который своим входом подключен к выходу мультиплексора 9 выбора адреса,, который первым информационным входом подключен к выходу 36 адреса команды перехода второго буферного регистра 6, вторым ин- формационным входом подключен к адресному входу 14 устройства, управляющим входом подключен к седьмому выходу 28 блока 2 управления, шестой вход 27 которого подключен к второму управляющему вхо- ду счетчика 7 адресов, подключенного первым 37 и вторым 38 выходами к первому и второму входам регистра 10 хранения следующего адреса, выход которого является вторым адресным выходом 39 устройства, а управляющий вход регистра 10 хранения соединен с восьмым выходом 29 блока 2 управления, девятый выход 30 которого соединен с входом установки первого триггера 11, выход которого является выходом 40 признака готовности команды устройства и подключен к восьмому входу блока 2 управления, вход сброса первого триггера 11 соединен с выходом первого элемента ИЛИ, первый вход которого подключен к один- надцатому выходу 32 блока управления, второй вход подключен к входу 19 сброса признака готовности команды устройства, третий вход соединен с входом 17 начальной установки устройства, который соеди- нен с вторым входом второго элемента ИЛИ 8, первый вход которого подключен к десятому выходу 31 блока 2 управления, выход второго элемента ИЛИ 8 соединен с входом сброса второго триггера 12, вход установки которого подключен к входу 18 сигнала невыполнения команды перехода выход второго триггера является выходом 41 признака невыполнения команды перехода, к которому подключен седьмой вход блока 2 управления, шестой и девятый входы которого соединены соответственно с выходом 34 признака команды перехода второго буферного регистра 6 и вторым выходом 38 счетчика 7 адресов команд, а двенадцатый выход 33 является выходом запроса командной информации устройства.

Первый буферный регистр 1 служит для приема и временного хранения командной информации.

Блок 2 управления предназначен для управления работой устройства.

Первый мультиплексор 3 служит для организации пересылки командной информации в старшую половину второго буферного

регистра 6 из старшей (или из младшей) половины первого буферного регистра 1.

Второй мультиплексор 4 служит для организации пересылки командной информации в младшую половину второго буферного регистра 6 из младшей (или из старшей) половины первого буферного регистра 1.

Первый элемент ИЛИ 5 предназначен для объединения сигналов, сбрасывающих в нулевое состояние первый триггер 11.

Второй буферный регистр 6 служит для формирования и временного хранения команды.

Счетчик 7 адресов команд служит для адресации команд в оперативной памяти.

Второй элемент ИЛИ 8 предназначен для объединения сигналов, сбрасывающих в нулевое состояние второй триггер 12,

Мультиплексор 9 выбора адреса служит для организации пересылки адресной информации из поля адреса второго буферного регистра 6 команд или с входа 14 адресной информации устройства.

Регистр 10 хранения следующего адреса предназначен для временного хранения адреса команды, следующей за командой, сформированной во втором буферном регистре 6 команд.

Первый триггер 11 служит для запоминания признака готовности команды, находящейся во втором буферном регистре 6 команд, второй триггер 12 -для запоминания признака невыполнения команды перехода.

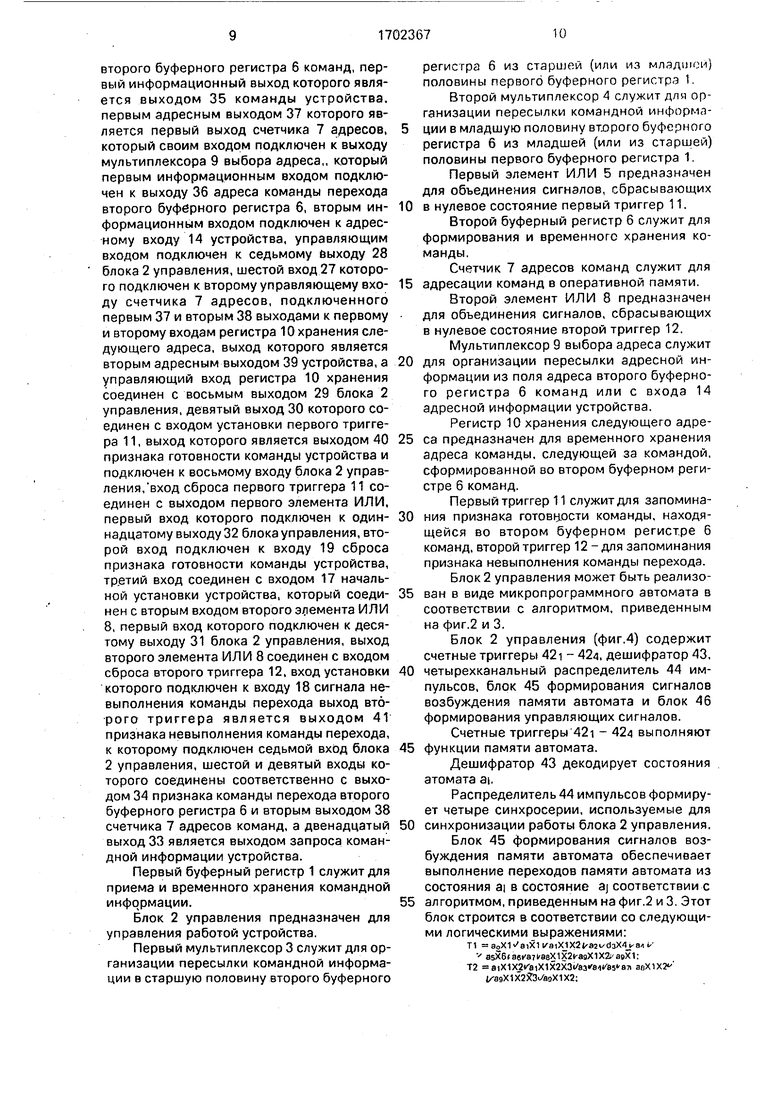

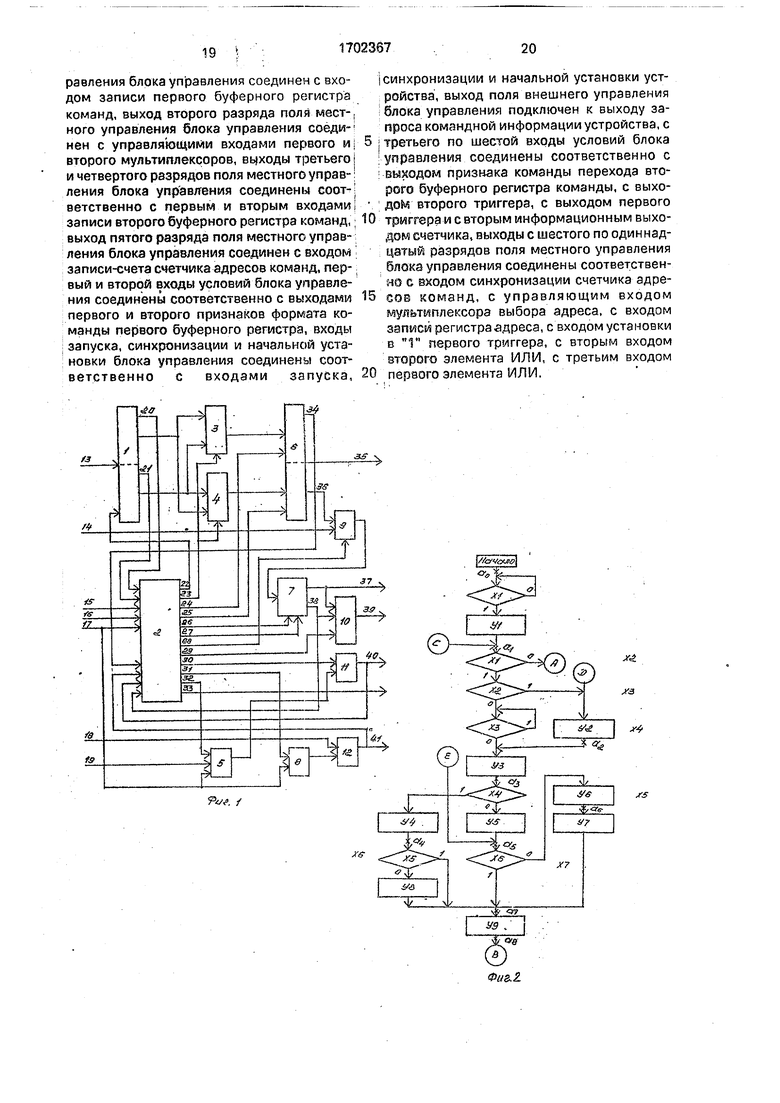

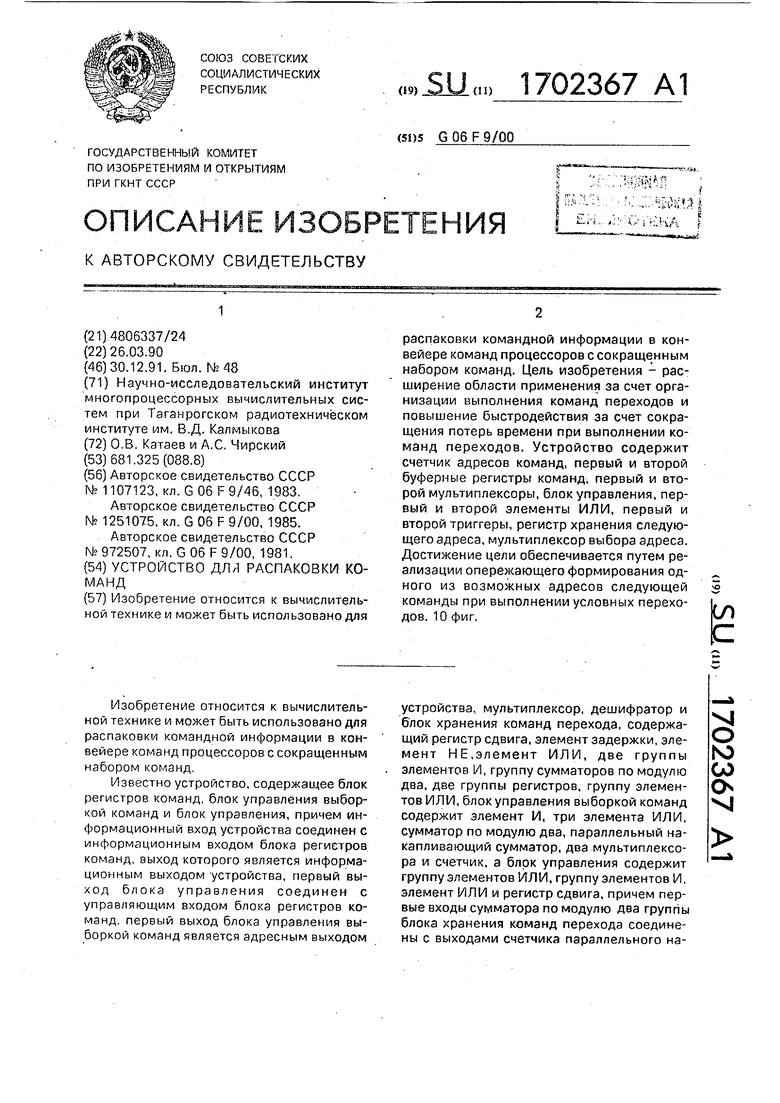

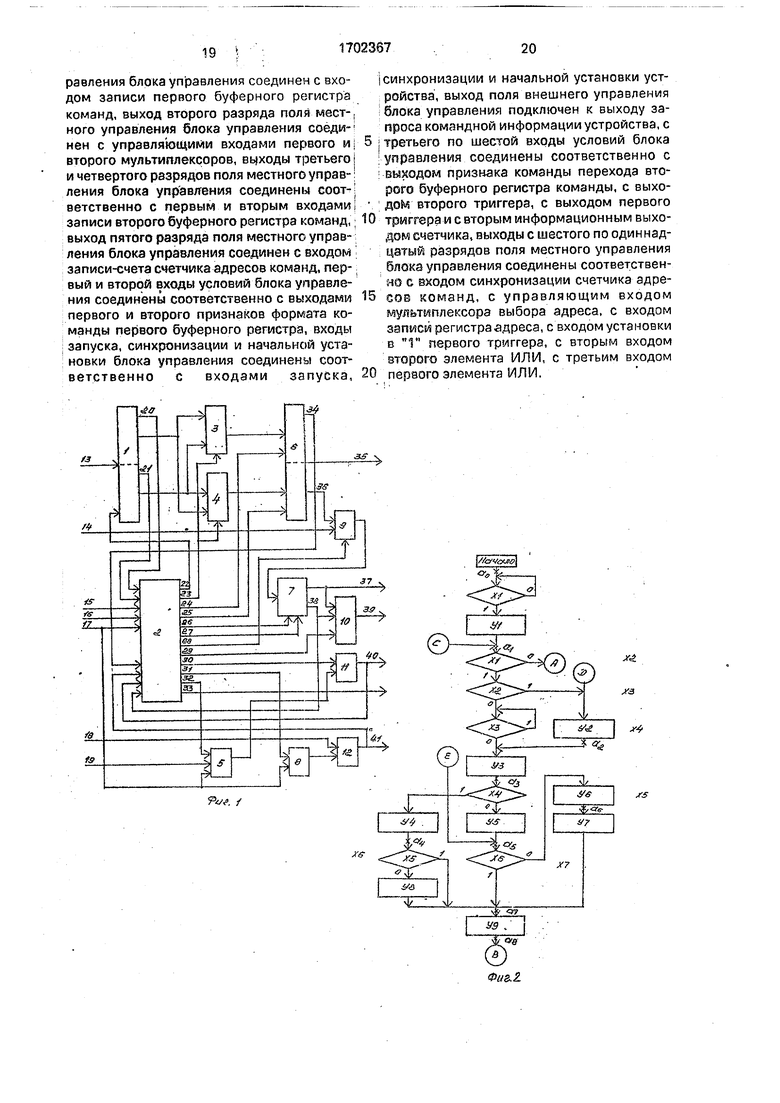

Блок 2 управления может быть реализован в виде микропрограммного автомата в соответствии с алгоритмом, приведенным на фиг.2 и 3.

Блок 2 управления (фиг.4) содержит счетные триггеры 42i - 42з, дешифратор 43, четырехканальный распределитель 44 импульсов, блок 45 формирования сигналов возбуждения памяти автомата и блок 46 формирования управляющих сигналов.

Счетные триггеры 42i - 42з выполняют функции памяти автомата.

Дешифратор 43 декодирует состояния атомата at.

Распределитель 44 импульсов формирует четыре синхросерии, используемые для синхронизации работы блока 2 управления.

Блок 45 формирования сигналов возбуждения памяти автомата обеспечивает выполнение переходов памяти автомата из состояния ai в состояние aj соответствии с алгоритмом, приведенным на фиг.2 и 3. Этот блок строится в соответствии со следующими логическими выражениями:

Т1 a0X1v aiX1l/-aiX1X2 2L ci3X4i a/4

a5X6 aefa7«eX1X2na9X1XZ aeX1: Т2 8iX1X2faiX1X2X3 /a3« aife5 a7i аоХ1Х2 agX1X2X3i/aoX1X2;

13 1X2X3. Т 4 a7jtsX1X2X7«-boX1X2X4X7 aX1 aoX1X VaoXVagX1X2 ,

Блок 46 формирования управляющих сигналов формирует управляющие сигналы в соответствии со следующими логическими выражениями:

ВЫХОД 22 S3 6-aiX1X2X3j a2 -a5X6:

Выход 23 Y4 азХ4;,

ВЫХОД 24 V4 Y5VY12 за/а9Х1Х 2; 3.

Выход 25

ВЫХОД 26 YSk y YSk-YH aiX1X2X3ta2, a.-,-X6 S Va XScagX

ВЫХОД 27 YJ V2,Y10

a0X biX1X2 aaX1X2VagX X2 ariXIX2X7: ВЫХОД 28 aoXH/aiX1X2 aaX1X2 /39X1X2;

Выход 29 Y9

Выход 30 Y9

Выход 31 Ґ3 31X1X2X3 2;

ВЫХОД 32 .. ,

а1Х1Х2/ааХ1Х2иаэХ1Х aiXVa,. эсХ1;

ВЫХОД 33 Y3VY6 3iX1X2X3 - 32 S5X6;

Основные принципы работы устройства заключаются в следующем.

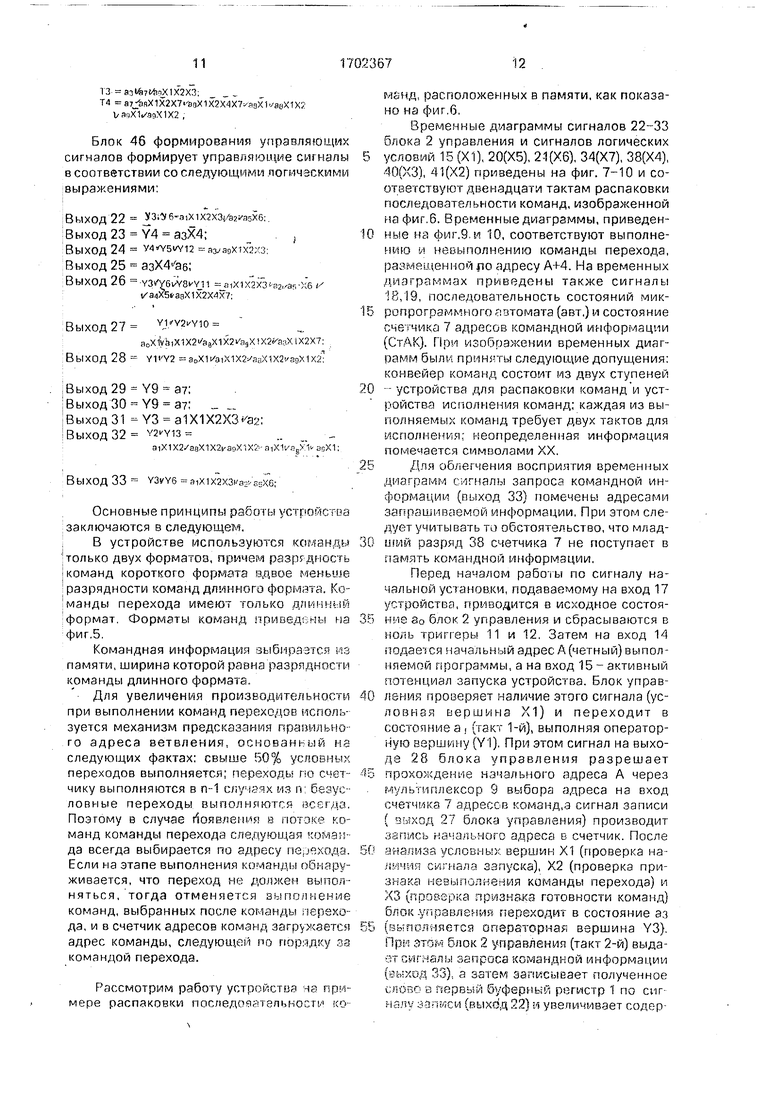

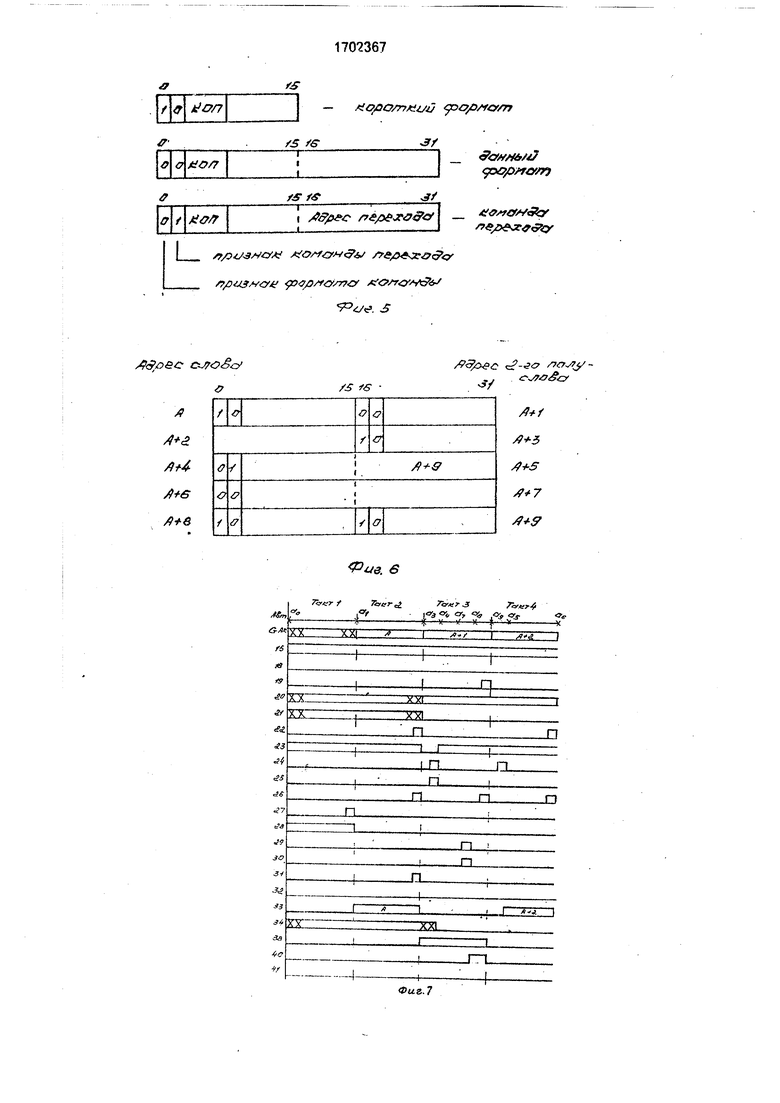

В устройстве используются команды 1 только двух форматов, причем разрядность i команд короткого формата адвое меньше разрядности команд длинного формата, Ко- 1 манды перехода имеют только длинный формат. Форматы команд приведены на фиг.5.

Командная информация зыбнраэтся из памяти, ширина которой равна разрядности команды длинного формата.

Для увеличения производительности при выполнении команд переходов используется механизм предсказания правильного адреса ветвления, основанный на следующих фактах: свыше 50% условных переходов выполняется; переходы по счет- чику выполняются в п-1 случаях из rv безусловные переходы выполняются всегда. Поэтому в случае появления в потзке команд команды перехода следующая комзя- да всегда выбирается по адресу перехода. Если на этапе выполнения команды обнаруживается, что переход не должен выполняться, тогда отменяется выполнение команд, выбранных после команды перехода, и в счетчик адресов команд запыхается адрес команды, следующей по порядку за командой перехода.

Рассмотрим работу устройства чз примере распаковки последовательности коБ

10

5

0

5

0 5

0 15 50 55

манд, расположенных в памяти, как показано на фиг.6.

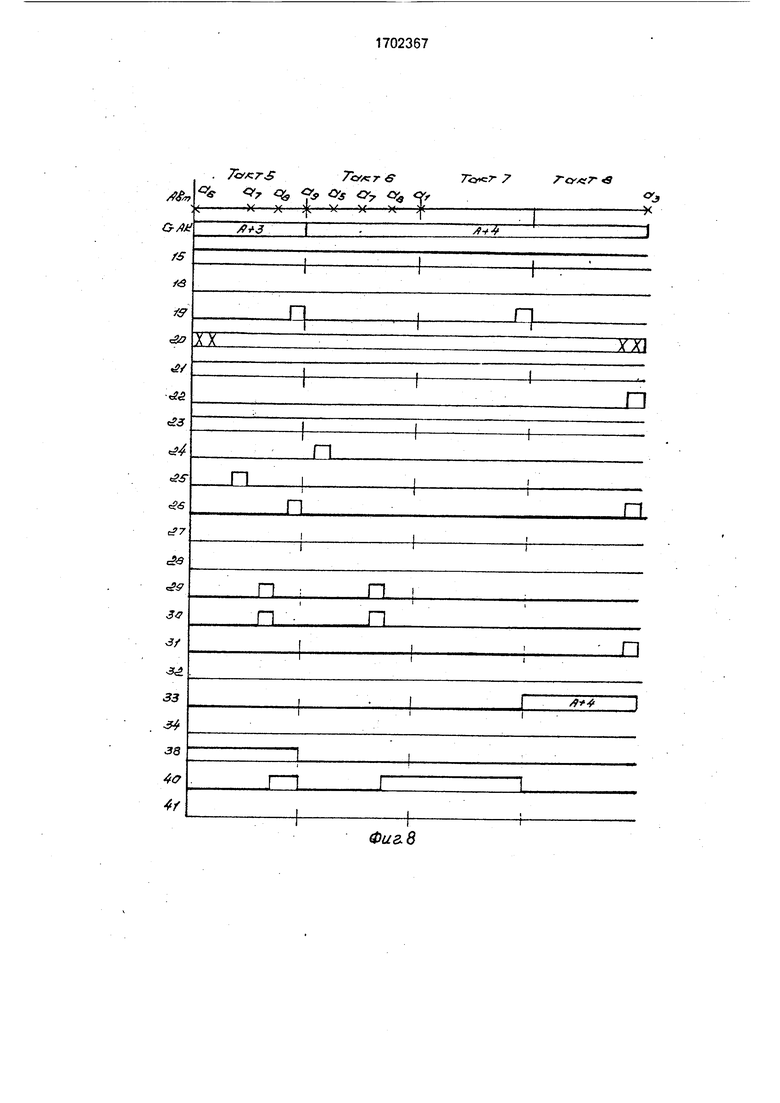

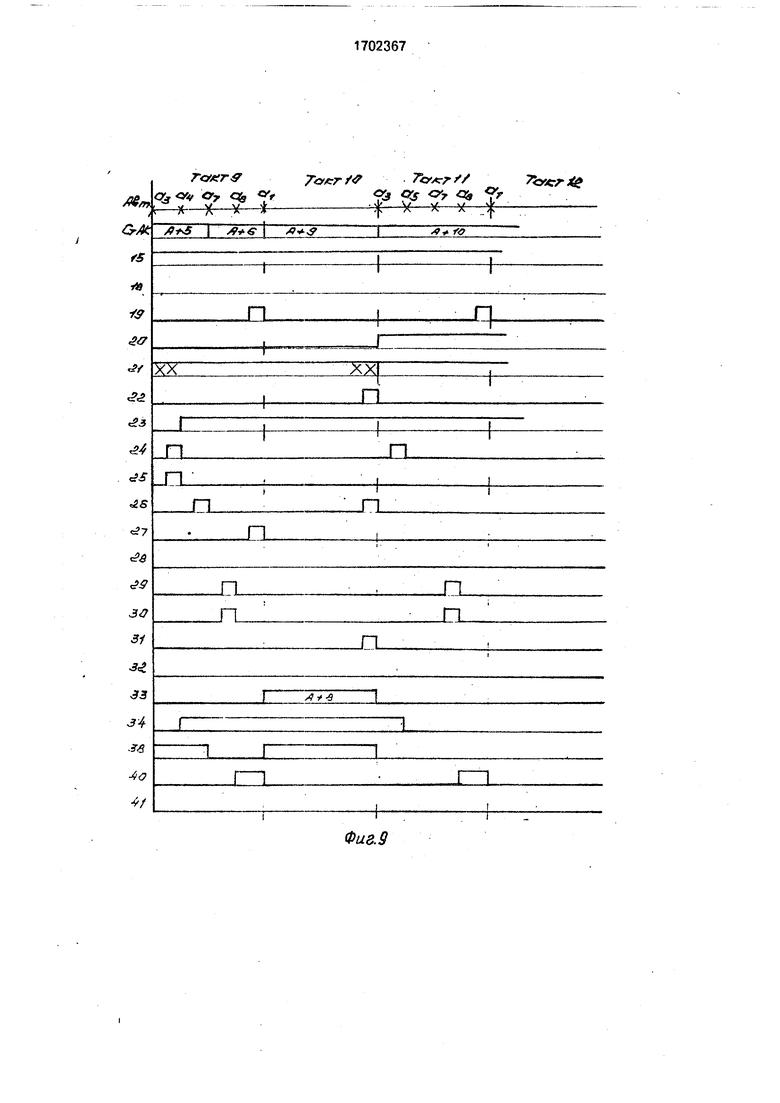

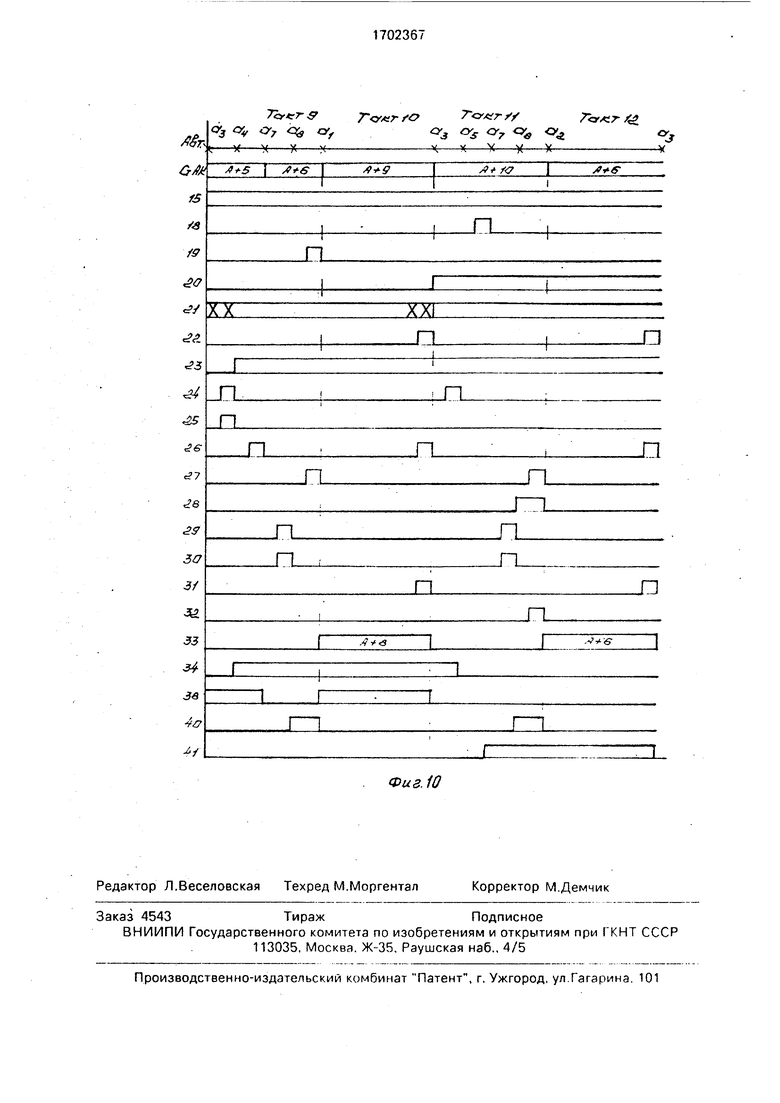

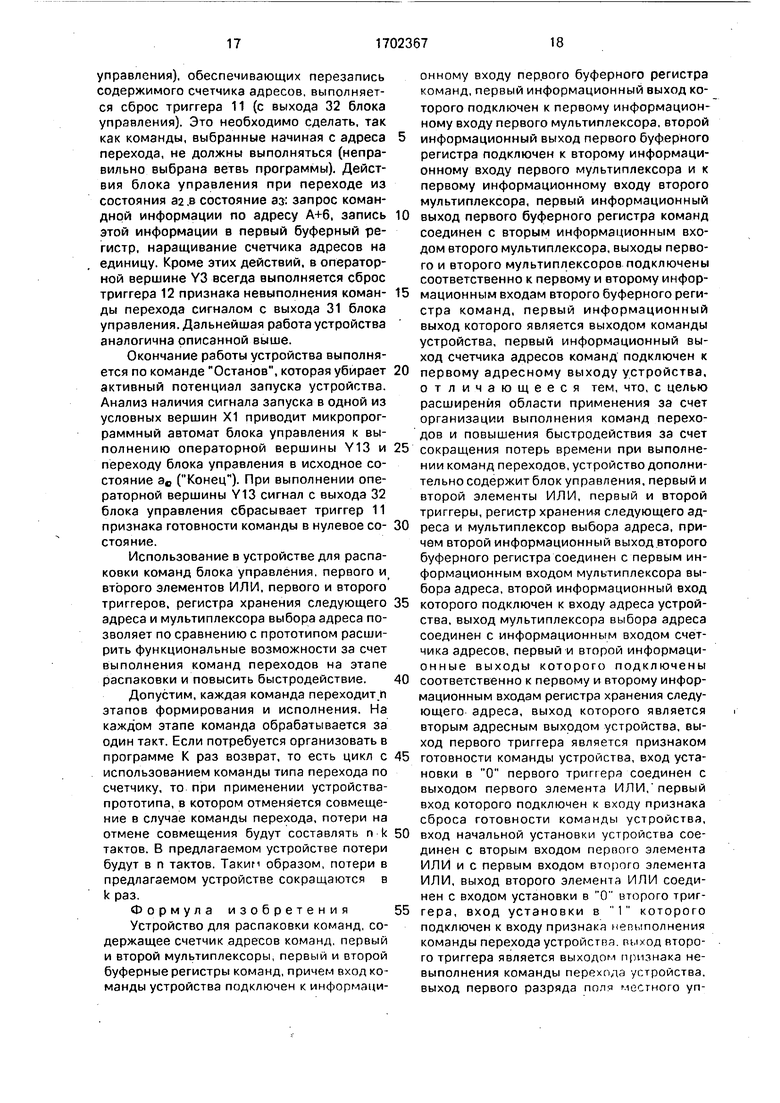

Временные диаграммы сигналов 22-33 блока 2 управления и сигналов логических условий 15 (Х1). 20(Х5), 2-1(Х6), 34(Х7), 38(Х4), 40(ХЗ), 41(Х2) приведены на фиг. 7-10 и соответствуют двенадцати тактам распаковки последовательности команд, изображенной на фиг.6. Временные диаграммы, приведенные на фиг.9, м 10, соответствуют выполнению и невыполнению команды перехода, разметенной ло адресу А+4. На временных диаграммах приведены также сигналы 18,19, последовательность состояний микропрограммного язтомата (авт.) и состояние счетчика 7 адресов командной информации (СтАК). При изображении временных диаграмм были приж ты следующие допущения: конвейер команд состоит из двух ступеней -- устройства для распаковки команд и устройства исполнения команд; каждая из выполняемых команд требует двух тактов для исполнения; неопределенная информация помечается символами XX.

Для облегчения восприятия временных диаграмм сигналы запроса командной информации, (выход 33) помечены адресами запрашиваемой информации, При этом следует учитывать то обстоятельство,что младший разряд 38 счетчика 7 не поступает в память командной информации.

Перед началом работы по сигналу начальной установки, подаваемому на вход 17 устройства, приводится в исходное состояние з0 блок 2 управления и сбрасываются в ноль триггеры 11 и 12. Затем на вход 14 подается начальный адрес А (четный) выполняемой программы, а на вход 15- активный потенциал запуска устройства. Блок управления проверяет наличие этого сигнала (условная вершина Х1) и переходит в состояние a i (такт 1-й), выполняя операторную вершину (Y1). При этом сигнал на выходе 28 блока управления разрешает прохождение начального адреса А через мультиплексор 9 выбора адреса на вход счетчика 7 адресов команд,а сигнал записи ( 9ыход 27 блока управления) производит запись начального адреса в счетчик. После анапмза условных вершин Х1 (проверка наличия сигнала запуска), Х2 (проверка признака невыполнения команды перехода) и ХЗ (проверка признака готовности команд) блок-управления переходит в состояние аз (выполняется операторная вершина Y3). Прк этом блок 2 управления (такт 2-й) выда- птг.игналы запроса командной информации (яь;ход 33), а затем записывает полученное с nose а первый буферный регистр 1 по сиг НИЛУ за-iwcn (выход 22) и увепичивает содертройства, вход признака типа.команд устройства, вход адреса команд устройства и второй синхровход устройства.

Однако известные устройства имеют большие потери времени при выполнении команд переходов.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее счетчик адресов командной информации, регистр адреса памяти, первый и второй буферные регистры команд, -ре- тистр адреса общих регистров, блок управления выборкой команд, выход обращения которого соединен с первым входом регистра адреса памяти и входом счетчика адресов командной информации, выход которого соединен с первым выходом устройства, первый и второй выходы смещения первого буферного регистра команд соединены с вторым выходом устройства, первый вход которого соединен с входом второго буферного регистра команд, первый, второй и третий адресные входы и выход индекса первого буферного регистра команд соединены соответственно с первым, вторым и третьим адресными вхЬдами и входом индекса регистра адреса общих регистров, выход которого соединен с третьим выходом устройства, четвертый выход которого соединен с выходом команды первого буферного регистра команд. Кроме того, устройство содержит блок управления, элемент ИЛИ, элемент И, первый, второй и третий мультиплексоры, первые, вторые, третьи и четвертые информационные входы которых соединены соответственно с первым, вторым, третьим и четвертым информационными входами второго буферного регистра команд,группа выходов формата команды которого соединена с группой входов формата команды блока управления, первый, второй и третий управляющие выходы которого соединены соответственно с управляющими входами первого, второго и третьего мультиплексоров, выходы которых соедине- Hti соответственно с первым, вторым и третьим информационными входами первого буферного регистра команд, группы разрешающих входов которого соединены с группой разрешающих выходов блока уп: равления и группой входов элемента ИЛИ, выход которого соединен с первым входом элемента И, выход которого соединен с пятым выходом устройства, второй вход элемента И соединен с вторым выходом блока управления выборкой команд, первый вход которого соединен с информационным выходом блока управления, управляющий вход которого соединен с управляющим выходом блока управления выборкой команд.

группа выходов увеличения значения блока управления соединена соответственно с группой входов счетчика полуслов, первый и второй выходы которого соединены соот- ветственно с первым и вторым разрешающими входами блока управления, а третий выход счетчика полуслов соединен с третьим разрешающим входом блока управления и с разрешающим входом блока управления

0 выборкой команд, вход сброса которого и вход сброса счетчика полуслов соединены с вторым входом устройства, третий вход которого соединен с входами счета счетчика полуслов и блока управления выборкой ко5 манд.

Однако с помощью такого устройства невозможно формирование адреса перехода.

Цель изобретения - расширение обла0 сти применения за счет организации выполнения команд переходов и повышение быстродействия путем сокращения потерь времени при выполнении команд переходов при предсказании правильного адреса вет5 вления.

Поставленная цель достигается тем. что в устройство, содержащее счетчик адресов команд, первый и второй мультиплексоры, первый и второй буферные регистры ко0 манд, причем вход командной информации устройства подключен к информационному входу первого буферного регистра команд, первый информационный выход которого подключён к первому информационному

5 входу первого мультиплексора и второму информационному входу второго мультиплексора, второй информационный выход первого буферного регистра подключен к второму информационному входу первого

0 мультиплексора и к первому информационному входу второго мультиплексора, выходы первого и второго мультиплексора, выходы первого и второго мультиплексоров подключены соответственно к первому и

5 второму информационным входам второго буферного регистра команд, первый информационный выход которого является выходом команды устройства, первым адресным выходом которого является первый выход

0 счетчика адресов команд, дополнительно введены блок управления, первый и второй элементы ИЛИ, первый и второй триггеры, регистр хранения следующего адреса и мульти- плексор выбора адреса, который первым ин5 формационным входом подключен к второму информационному выходу второго буферного регистра, вторым информационным входом подключен к адресному входу устройства, управляющим входом подключен к седьмому выходу блока управления, а

буферного регистра, вторым информационным входом подключен к адресному входу устройства, управляющим входом подключен к седьмому выходу блока управления, а выходом соединен с входом счетчика адресов, подключенного первым и вторым управляющими входами соответственно к пятому и шестому выходам блока управления, первым и вторым выходами к первому и второму входам регистра хранения следующего адреса, выход которого является вторым адресным выходом устройства, а управляющий вход регистра хранения следующего адреса соединен с восьмым выходом блока управления, девятый выход которого соединен с входом установки первого триггера, выход которого является признаком готовности команды устройства ш подключен к восьмому блока управления, вход сброса первого триггера соединен с выходом первого элемента ИЛИ, первый вход которого подключен к одиннадцатому выходу блока управления, второй вход подключен к входу сброса признака готовности команды устройства, третий вход соединен с входом начальной установки устройства, который соединен с вторым входом второго элемента ИЛИ, первый вход которого подключен к десятому выходу блока управления, выход второго элемента 14ЛИ соединен с входом сброса второго триггера, вход установки которого подключен к входу сигнала невыполнения команды перехода, выход второго триггера является признаком невыполнения команды перехода устройства, к которому подключен седьмой вход блока управления, пустой и девятый входы которого соединены соответственно с выходом признака команды перехода второго буферного регистра и вторым выходом счетчика адресов команд, первый выход блока управления соединен с входом записи первого буферного регистра команд, второй выход соединен с управляющими входами первого и второго мультиплексоров, третий у. четвертый выходы соединены соответственно с первым и вторым вхойами записи второго буферного регистра команд, первый и второй входы соединены соответственно с первым и вторым выходами признаков формата команды первого буферного регистра, третий, четвертый и пятый входы являются соответственно входами запуска, синхронизации и начальной усганонки устройства, а двенадцатый выход подключен к выходу запроса командной информации устройства.

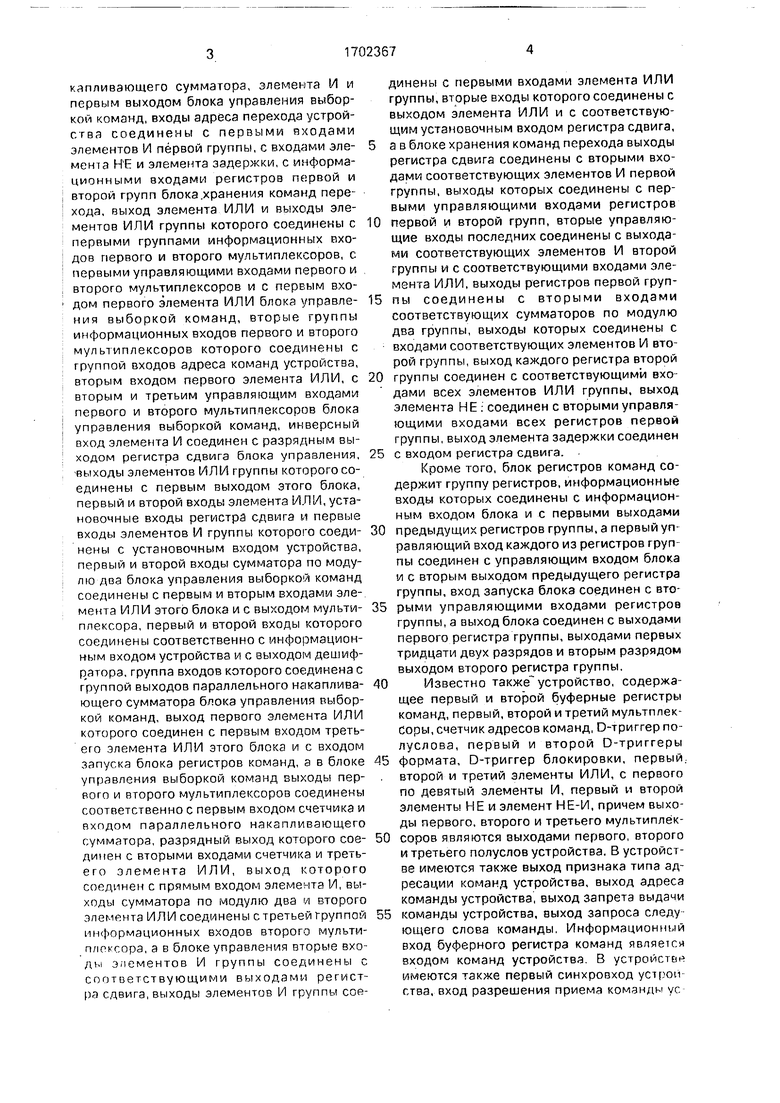

На фиг.1 представлена схема прздлага- емого устройства; на фмг.2 и 3 т алгоритм

работы блока управления; на фиг.4 - схема блока управления; на фиг.5 - форматы команд; на фиг.6 - пример расположения команд в памяти; на фиг, 7-10 - временные

диаграммы, поясняющие работу устройства.

Устройство для распаковки команд (фйг.1) содержит первый буферный регистр 1 команд, блок 2 управления, первый 3 и

0 второй 4 мультиплексоры, первый элемент ИЛИ 5, второй буферный регистр 6 команд, счетчик 7 адресов команд, второй элемент 1АЛ1А 8, мультиплексор 9 выбора адреса, регистр 10 хранения следующего адреса, пер5 вый 11 и второй 12 триггеры, вход 13 командной информации, адресный вход 14,, вход 15 запуска, вход 16 синхронизации, вход 17 начальной установки, вход 18 сигнала невыполнения команды перехода, вход

0 19 сброса признака готовности команды, первый 20 и второй 21 выходы признаков формата команды, группу выходов 22-33 блока управления, выход 34 признака команды перехода, выход 35 команды, выход

5 36 адреса команды перехода, первый адресный выход 37, выход 38 младшего разряда счетчика адресов, второй адресный выход 39. выход 40 признака готовности команды, выход 41 признака невыполнения команды

0 перехода, причем первый выход 22 блока управления 2 соединен с входом записи первого буферного регистра 1 команд, второй выход 23 - с управляющими входами первого 3 и второго 4 мультиплексоров, тре5 тми 24 и четвертый 25 выходы - соответственно с первым и вторым входами записи второго буферного регистра команд 6, пя- гый выход 26 - с первым управляющим входом счетчика адресов 7, первый и второй

0 входы блока управления 2 - соответственно с первым 20 и вторым 21 выходами признаков формата команды первого буферного регистра 1, третий четвертый и пятый входы являются соответственно входами 15 запу5 ска, 16 синхронизации и 17 начальной установки устройства, вход 13 командной информации которого подключен к информационному входу первого буферного регистра 1, первый информационный выход

0 которого подключен к первому информационному входу первого мультиплексора 3 и второму информационному входу второго мультиплексора4, второй информационный выхо$ первого буферного регистра 1 подВ ключей к второму информационному входу первого мультиплексора 3 и первому информационному входу второго мультиплексора 4, выходы первого 3 и второго 4 мультиплек- соров подключены соответственно к перво- му и второму информационным входам

жимое счетчика адресов на единицу (выход 26). Содержимое счетчика становится равным А+1. Анализируя, равен ли единице младший разряд (выход 38) счетчика адресов (условная вершина Х4), блок управления переходит в состояние 3-й), организуя прямую передачу командной информации из первого буферного регистра 1 во второй буферный регистр 6 через первые входы мультиплексоров 3 и 4 (выполняется операторная вершина Y4). При этом блок управления формирует соответствующие управляющие сигналы: управлениямультип- лексорами (выход 23), записи в старшую (выход 24) и младшую (выход 25) половины второго буферного регистра 6. Анализ выхода 20 признака формата команды (условная вершина Х5) показывает, что первая команда имеет короткий формат и, следовательно, готова для передачи из второго буферного регистра для дальнейшей обработки. Блок управления переходит в состояние а, а затем в состояние as. При переходе из состо- яния а в состояние SB выполняется операторная вершина Y9, При этом содер- жимое счетчика 7 адресов (адрес первого полуслова второй команды А+1) записывается в регистр хранения следующего адреса сигналом с выхода 29 и сигналом с выхода 30 устанавливается в 1 триггер 11 - при- знак готовности команды к дальнейшей обработке.

Проверка условных вершин Х1 (наличие сигнала запуска), Х2 (признак невыполнения команды), Х7 (признак команды перехо- да - выход 34 второго буферного регистра 6) и Х4 (проверка, равен ли единице младший разряд счетчика 7) приводит к переходу в состояние ад (выполняется операторная вершина Y11), При этом содержимое счетчи- ка адреса увеличивается на единицу по сигналу, формируемому на выходе 26 блока управления, и становится равным А+2.

Если следующая ступень конвейера команд готова к обработке команды, находя- щейся во втором буферном регистре 6, и признак готовности команды (выход 40 устройства) равен единица, то происходит перезапись информации из второго буферного регистра 6 и регистра 10 хране- ния в соответствующие регистры следующей ступени конвейера. Одновременно следующая ступень конвейера сбрасывает признак готовности команды (триггер 11) в О по входу 19 устройства (такт 3-й), сигна- лизируя блоку управления о том, что можно продолжать распаковку командной информации. Признак готовности команды проверяется блоком 2 управления в условных вершинах Х2.

После проверки условных вершин Х1 (наличие сигнала запуска), Х2 (признак невыполнения команды перехода) и ХЗ (признак готовности команды) блок управления переходит в состояние as (выполняется операторная вершина Y12). При этом осуществляется пересылка первой половины второй команды из младшей половины первого буферного регистра 1 в старшую половину второго буферного регистра 6 по единичному сигналу управления мультиплексорами 3 и 4 (выход 23) и запись в старшую половину второго буферного регистра 6 (выход 24). Анализ выхода 21 признака формата команды (условная вершина Х6) указывает на то, что в первый буферный регистр 6 была записана старшая часть команды длинного формата и поэтому надо выбрать следующее слово командной информации, в котором содержится вторая половина этой команды, Блок управления переходит в состояние ае (выполняется операторная вершина Y6).

При этом формируются сигналы (такт 4-й) запроса командной информации (выход 33), записи слова командной информации, полученной из ячейки с адресом А+2, в первый буферный регистр 1 (выход 22) и увеличения содержимого счетчика адресов команд на единицу (выход 26). Содержимое счетчика 7 адресов после выполнения операторной вершины Y6 равно А+3. Затем блок управления (такт 5-й) переходит в состояние а (выполняется операторная вершина Y7). Управляющие сигналы этой вершины осуществляют запись содержимого старшей половины первого буферного ре- гистрз в младшую половину второго буферного регистра (единичный сигнал на выходе 23 и сигнал с выхода 25 блока управления). После оперативной вершины Y7 вы- полняется операторная вершина Y9 (выполняется переход в состояние as), во время выполнения которой происходит запись содержимого счетчика 7 адреса в регистр 10 храненния следующего адреса (сигналом с выхода 29) и установка признака готовности команды в 1 (сигналом с выхода 30). Анализ условных вершин Х1, Х2, Х7, Х4 приводит к выполнению операторной вершины Y11 (переход в состояние аэ), сигнал которой (выход 26) увеличивает содержимое счетчика адресов на единицу. Содержимое счетчика адресов становится равным А+4. После того как будет сброшен признак готовности команды от следующей ступени конвейера команд, выполняется операторная вершина Y12 (переход в состояние as), сигналы которой записывают содержимое младшей половины первого буферного регистра в старшую половину

второго буферного регистра (выходы 23 и 24 блока управления). Анализ выхода 21 признака формата команды (условная вершина Х6) показывает, что распаковываемая команда имеет короткий формат. Блок управления переходит в состояние а& и выполняет операторную вершину Y9 (запись в регистр 10 хранения адреса А+4 и установка признака готовности команды). После этого в результате анализа условных вершин Х1, Х2, Х7 и Х4 микропрограммный автомат блока управления переходит в состояние ai (без выполнения операторных вершин), к анализу условных вершин Х1, Х2 и ХЗ. В такте 7-м признак готовности команды ХЗ (выход 40) равен единице - продолжает выполняться предыдущая команда, поэтому нет перехода в состояние аз. Если триггер 11 признака готовности команд сброшен в О, (выход 40), блок управления выполняет операторную вершину Y3 (такт 8-й), формирует сигналы запроса командной информации (выход 33), записи в первый буферный регистр (выход 22) и увеличения содержимого счетчика адресов команд (выход 26).

Содержимое счетчика адресов команд становится равным А+5, а очередное слово командной информации, выбранное из ячейки памяти с адресом А+4, записывается в первый буферный регистр 1. Анализ услов- - ной вершины Х4 (четный ли адрес в счетчике адресов) приводит к выполнению операторной вершины Y4 (переход в состояние ). Сигналы, формируемые блоком управления во время выполнения операторной вершины Y4 (выходы 23,24 и 25 блока управления), осуществляют прямую пересылку содержимого первого буферного регистра 1 во второй буферный регистр 6. Анализ выхода 20 признака формата команд (условная вершина Х5) показывает, что в первом буферном регистре 1 команд, а следовательно, и во втором буферном регистре) находится команда длинного формата. Блок управления выполняет операторную вершину Y8 (переход в состояние а), в которой наращивается на единицу содержимое счетчика адресов команд (сигнал с выхода 26 блока управления). В результате содержимое счетчика адресов становится равным А+6, адресуя следующую команду. После выполнения операторной вершины Y9 (переход в состояние ав) блок управления анализирует условные вершины Х1, Х2 и Х7. Анализ условной вершмны Х7 (проверка признака команды условного перехода - выход 34 второго буферного регистра 6) приводит к выполнениюоператорной вершины Y10(ne- реход в состояние ai), так как во втором буферном регистре находится команда перехода. Во время выполнения операторной вершины Y10 по сигналу с выхода 27 блока управления в счетчик 7 адресов с выхода 36 второго буферного регистра 6 заносится адрее перехода А+9. После того, как по входу 19 устройства будет сброшен в ноль признак готовности команды, блок 2 управления выполняет операторную вершину Y3 (переход в состояние аз): запрашивает слово

0 командной информации по адресу А+8 (младший разряд адреса памяти команд соответствует не младшему разряду счетчика 7 адресов команд, а следующему разряду), записывает это слово в первый буферный

5 регистр 1 и увеличивается содержимое счетчика адресов команд на единицу (содержимое его становится равным А+10). Анализ младшего разряда счетчика адресов (условная вершина Х4) показывает, что начало ко0 манды, на которую был совершен переход (в нашем случае вся команда), находится во второй половине слова и, следовательно, в младшей половине первого буферного регистра. Блок 2 управления осуществляет за5 пмсь этой информации в старшую половину второго буферного регистра 6, формируя соответствующие сигналы (выходы 23 и 24 блока управления) при выполнении операторной вершины Y5 (переход в состо0 яние as). Анализ формата команды (условная вершина Х 6 проверяет выход 21 признака формата команды) показывает, что распаковываемая команда имеет коротких формат, и блок управления переходит к выполнению

5 операторной вершины Y9 и так далее.

Рассмотрим, как работает устройство в случае невыполнения команды перехода (фмг.10). Этот факт определяется на этапе выполнения анализа условия перехода в за0 вершающей фазе исполнения команды. При этом сигнал от блока микропрограммного управления, поданный на вход 18 устройства, устанавливает триггер 12 признака невыполнения команды перехода (такт

5 11-й). Блок управления анализирует этот сигнал в одной из условных вершин Х2 (в зависимости оттого, какую ветвь алгоритма обрабатывает микропрограммный автомат блока управления) и производит перезапись

0 адреса А+6 команды, следующей за командой перехода, в счетчик 7 адресов (выполняется операторная вершина Y2). В данном конкретном случае анализ Х2 выполняется при переходе микропрограммного автомата

5 из состояния as в состояние аа. Адрес А+6 поступает на вход. 14 устройства из регистра хранения следующего адреса той ступени конвейера, на которой производится выполнение команд. Одновременно с формированием сигналов (выходы 27 и 28 блока

управления), обеспечивающих перезапись содержимого счетчика адресов, выполняется сброс триггера 11 (с выхода 32 блока управления). Это необходимо сделать, так как команды, выбранные начиная с адреса перехода, не должны выполняться (неправильно выбрана ветвь программы). Действия блока управления при переходе из состояния за,в состояние аз: запрос командной информации по адресу А+6, запись этой информации в первый буферный регистр, наращивание счетчика адресов на единицу. Кроме этих действий, в операторной вершине Y3 всегда выполняется сброс триггера 12 признака невыполнения коман- ды перехода сигналом с выхода 31 блока управления. Дальнейшая работа устройства аналогична описанной выше.

Окончание работы устройства выполняется по команде Останов, которая убирает активный потенциал запуска устройства. Анализ наличия сигнала запуска в одной из условных вершин Х1 приводит микропрограммный автомат блока управления к выполнению операторной вершины Y13 и переходу блока управления в исходное состояние ас (Конец). При выполнении операторной вершины Y13 сигнал с выхода 32 блока управления сбрасывает триггер 11 признака готовности команды в нулевое со- стояние.

Использование в устройстве для распаковки команд блока управления, первого и второго элементов ИЛИ, первого и второго триггеров, регистра хранения следующего адреса и мультиплексора выбора адреса позволяет по сравнению с прототипом расширить функциональные возможности за счет выполнения команд переходов на этапе распаковки и повысить быстродействие.

Допустим, каждая команда переходит/) этапов формирования и исполнения. На каждом этапе команда обрабатывается за один такт. Если потребуется организовать в программе К раз возврат, то есть цикл с использованием команды типа перехода по счетчику, то при применении устройства- прототипа, в котором отменяется совмещение в случае команды перехода, потери на отмене совмещения будут составлять n k тактов. В предлагаемом устройстве потери будут в n тактов. Таким образом, потери в предлагаемом устройстве сокращаются в k раз.

Формула изобретения

Устройство для распаковки команд, содержащее счетчик адресов команд, первый и второй мультиплексоры, первый и второй буферные регистры команд, причем вход команды устройства подключен к информационному входу первого буферного регистра команд, первый информационный выход которого подключен к первому информационному входу первого мультиплексора, второй информационный выход первого буферного регистра подключен к второму информационному входу первого мультиплексора и к первому информационному входу второго мультиплексора, первый информационный выход первого буферного регистра команд соединен с вторым информационным входом второго мультиплексора, выходы первого и второго мультиплексоров подключены соответственно к первому и второму информационным входам второго буферного регистра команд, первый информационный выход которого является выходом команды устройства, первый информационный выход счетчика адресов команд подключен к первому адресному выходу устройства, отличающееся тем, что, с целью расширения области применения за счет организации выполнения команд переходов и повышения быстродействия за счет сокращения потерь времени при выполнении команд переходов, устройство дополнительно содержит блок управления, первый и второй элементы ИЛИ, первый и второй триггеры, регистр хранения следующего адреса и мультиплексор выбора адреса, причем второй информационный выход второго буферного регистра соединен с первым информационным входом мультиплексора выбора адреса, второй информационный вход которого подключен к входу адреса устройства, выход мультиплексора выбора адреса соединен с информационным входом счетчика адресов, первый и второй информаци- онные выходы которого подключены соответственно к первому и второму информационным входам регистра хранения следующего адреса, выход которого является вторым адресным выходом устройства, выход первого триггера является признаком готовности команды устройства, вход установки в О первого триггера соединен с выходом первого элемента ИЛИ, первый вход которого подключен к входу признака сброса готовности команды устройства, вход начальной установки устройства соединен с вторым входом первою элемента ИЛИ и с первым входом второго элемента ИЛИ, выход второго элемента ИЛИ соединен с входом установки в О второго триггера, вход установки в 1 которого подключен к входу признака невыполнения команды перехода устройства пыход второго триггера является выходом признака невыполнения команды перехода устройства, выход первого разряда пола местного управнения блока управления соединен с входом записи первого буферного регистра команд, выход второго разряда поля мест-, ного управления блока управления соеди-1 нен с управляющими входами первого и( второго мультиплексоров, выходы третьего и четвертого разрядов поля местного управления блока управления соединены соот- ( ветственно с первым и вторым входами записи второго буферного регистра команд, выход пятого разряда поля местного управления блока управления соединен с входом записи-счета счетчика адресов команд, первый и второй входы условий блока управления соединены соответственно с выходами первого и второго признаков формата команды первого буферного регистра, входы запуска, синхронизации и начальной установки блока управления соединены соответственно с входами запуска,

(синхронизации и начальной установки устройства, выход поля внешнего управления блока управления подключен к выходу запроса командной информации устройства, с

, третьего по шестой входы условий блока управления соединены соответственно с выходом признака команды перехода второго буферного регистра команды, с выхо- до№ второго триггера, с выходом первого

триггера и с вторым информационным выходом счетчика, выходы с шестого по одиннадцатый разрядов поля местного управления блока управления соединены соответственно с входом синхронизации счетчика адреcos команд, с управляющим входом мультиплексора выбора адреса, с входом записи регистра адреса, с входом установки в 1 первого триггера, с вторым входом второго элемента ИЛИ, с третьим входом

первого элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| Устройство для распаковки команд | 1981 |

|

SU972507A1 |

| Устройство для распаковки команд | 1984 |

|

SU1251075A1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2046395C1 |

| Устройство КЭШ-памяти | 1988 |

|

SU1675881A1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 2007 |

|

RU2336556C1 |

| Устройство для распаковки команд | 1984 |

|

SU1196865A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

Изобретение относится к вычислительной технике и может быть использовано для распаковки командной информации в конвейере команд процессоров с сокращенным набором команд. Цель изобретения - расширение области применения за счет организации выполнения команд переходов и повышение быстродействия за счет сокращения потерь времени при выполнении команд переходов. Устройство содержит счетчик адресов команд, первый и второй буферные регистры команд, первый и второй мультиплексоры, блок управления, первый и второй элементы ИЛИ, первый и второй триггеры, регистр хранения следующего адреса, мультиплексор выбора адреса. Достижение цели обеспечивается путем реализации опережающего формирования одного из возможных адресов следующей команды при выполнении условных переходов. 10 фиг. И

S3

JfS

ТСУХГТ- Г

6

йЈ

/№

fS

&

30

4/

&

Ј3

4

ЈS

Ј

&

S9 34

J/ 3Ј з &

38

40 4f

Pi

% & 5 &7

х-X-X

и:

гт

п

гт

п

п

гт

л

7

«Э

Тг

-

y-F

-чТХ

П

П

п

л

п

А 4

Фиг. 8

Тожг / 7Ьх-л

оз «г ° -

- V у-уsi

O-/(fc

A+G

А+&

гл

XX

XXI

п

п

п

п

п

Д л -з

Фиг. 9

I

/ О

лЛ.

л

п

л

л

л

IX

1L

1 ef

1Г f - 1 XI I 1 I

1ЧС1Г

5 1 /2 ,

:i

Ql ...

- /- t I

-4

i ч

/

Ј /

jp

.

:9CiTOil.

Ј+# Ј+Р Ј+& f+P t+l/

&ffcrtr

/Ъгас/ oe-f

я&меггс/ / I

9+У 9+V f

+y

У

5X

&§ О1Г-3

TO-AT- X/

| Устройство предварительной выборки команд | 1983 |

|

SU1107123A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распаковки команд | 1984 |

|

SU1251075A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распаковки команд | 1981 |

|

SU972507A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-12-30—Публикация

1990-03-26—Подача