Изобретение относится к вычислительной технике, а именно к вычислительным устройствам, использующим управление вычислительным процессом от потока данных, и может быть использовано в цифровых вычислительных системах высокой производительности.

Известно устройство для обработки данных, содержащее процессор, память команд, память данных, блок сопряжения, блок выборки команд, блок распечатки команд и процессор присвоения номера регистра [1].

Однако это устройство не отличается высокой производительностью, так как при выполнении скалярных операций она определяется суммарным временем последовательной работы основных функциональных узлов: процессора, памятей команд и данных.

По технической сущности наиболее близким к предлагаемому устройству является устройство для обработки данных, содержащее процессор, блок ввода-вывода, блок выборки данных, блок памяти команд, причем первый информационный вход блока ввода-вывода соединен с первым информационным выходом процессора, информационный вход для ввода полупакета данных устройства соединен с вторым информационным входом блока ввода-вывода, управляющий вход которого соединен с входом кода режима устройства, второй информационный выход процессора соединен с третьим информационным входом блока ввода-вывода, первый выход которого соединен с первым информационным входом блока выборки данных и выходом результата устройства, выход адреса следующей команды которого соединен с входом аргумента поиска блока выборки данных и с вторым выходом разрядов кода номера команды блока ввода-вывода, первый информационный выход блока выборки данных соединен с первым информационным входом процессора, выход разрешения записи следующего полупакета данных которого является одноименным выходом устройства, выход кода прерывания которого соединен с одноименным выходом процессора, выход разрешения записи следующего пакета данных которого является одноименным выходом устройства, первый управляющий выход процессора соединен с входом разрешения записи результата блока выборки данных, входы синхронизации процессора, блока ввода-вывода, блока выборки данных и блока памяти команд соединены с входом синхронизации устройства [2].

Однако и это устройство не отличается высокой производительностью, так как она определяется в нем периодом следования пакетов команд на исполнение и ограничивается величиной суммарного времени последовательной работы функциональных узлов арифметико-логического устройства (АЛУ), блоков выборки данных и памяти команд.

Целью изобретения является повышение быстродействия за счет обеспечения параллельного формирования функциональных составляющих пакетов команд.

Достигается это тем, что в устройство выборки информации, содержащее устройство для обработки данных, содержащее процессор, блок ввода-вывода, блок выборки данных, блок памяти команд, причем первый информационный вход блока ввода-вывода, соединен с первым информационным выходом процессора, информационный вход для ввода полупакета данных устройства соединен с вторым информационным входом блока ввода-вывода, управляющий вход которого соединен с входом кода режима устройства, второй информационный выход процессора соединен с третьим информационным входом блока ввода-вывода, первый выход которого соединен с первым информационным входом блока выборки данных и выходом результата устройства, выход адреса следующей команды которого соединен с входом аргумента поиска блока выборки данных и с вторым выходом разрядов кода номера команды блока ввода-вывода, первый информационный выход блока выборки данных соединен с информационным входом процессора, выход разрешения записи следующего полупакета данных которого является одноименным выходом устройства, выход кода прерывания которого соединен с одноименным выходом процессора, выход разрешения записи следующего пакета данных которого является одноименным выходом устройства, первый управляющий выход процессора соединен с входом разрешения записи результата блока выборки данных, входы синхронизации процессора, блока ввода-вывода, блок выборки данных и блока памяти команд соединены с входом синхронизации устройства, введены блок формирования пакетов команд и коммутатор загрузки команд, причем вход признака готовности пакета данных соединен с выходом блока формирования пакетов команд, группа информационных входов которого соединена с входами разрядов пакета команды процессора, вход разрешения загрузки пакета данных которого подключен к одноименному входу устройства, соединенному с входом готовности внешнего пакета блока формирования пакетов команд, вход для ввода пакета данных которого является одноименным входом устройства, вход управления режимом работы которого подключен к входу управления начальной загрузкой коммутатора загрузки команд, входу управления режимом работы блока выборки данных и к одноименному входу процессора, выход сигнала управления поиском данных которого соединен с первым информационным входом блока выборки данных, вход управления сбросом памяти которого соединен с одноименным входом устройства, адресный вход которого соединен с одноименным входом коммутатора загрузки команд, выход которого подключен к входу разрядов командного слова и выход признака готовности командного слова которого соединены с соответствующими входами блока формирования пакетов команд, вход первого операнда которого подключен к выходу разрядов кода числа блока ввода-вывода, входы первого разряда и второго разряда кода результата поиска процессора соединены соответственно с одноименными выходами блока выборки данных, выход данных и выход признака готовности данных которого подключены соответственно к входам второго операнда и разрешения записи второго операнда блока формирования пакетов команд, вход признака одиночного операнда и вход разрешения записи первого операнда которого соединены соответственно с одноименным выходом и выходом управления передачей результата процессора, выход управления пуском которого подключен к входу начальной установки блока формирования пакета команд и к входу управления чтением командного слова блока памяти команд, вход управления записью командного слова и выход признака конца записи командного слова которого являются соответственно одноименными входом и выходом устройства, информационный вход командного слова и вход разрешения записи командного слова которого соединены соответственно с входом разрядов командного слова и входом управления приемом командного слова, объединенным с входом признака передачи командного слова блока памяти команд, вход разрядов кода-выборки командного слова коммутатора загрузки команд соединен с одноименным выходом блока ввода-вывода, выход сигнала переполнения памяти блока выборки данных является выходом признака переполнения памяти устройства, а входы синхронизации блока формирования пакетов команд и коммутатора загрузки команд подключены к входу синхронизации устройства.

Блок формирования пакетов команд содержит первый, второй и третий коммутаторы, первый, второй и третий регистры формирования пакета, первый, второй и третий триггеры, элемент И и элемент ИЛИ, причем первый информационный вход первого коммутатора соединен с выходами первого, второго и третьего регистров формирования пакета, первый управляющий вход соединен с выходом элемента И и выходом признака готовности пакета блока формирования пакетов команд, выход разрядов командного слова которого соединен с выходами первого и второго коммутаторов, первые, вторые информационные и управляющие входы последнего из которых соединены с выходом первого, вход начальной установки блока формирования пакетов команд соединен с управляющими входами первого, второго и третьего триггеров, выходы которых соединены с входами элемента И, второй информационный и второй управляющий входы первого коммутатора являются соответственно входом для ввода пакета данных и входом признака готовности внешнего пакета блока формирования пакетов команд, вход разрешения записи второго операнда которого соединен с первым входом элемента ИЛИ и первым управляющим входом третьего коммутатора, выход которого соединен с информационным входом второго регистра, вход чтения-записи которого подключен к выходу элемента ИЛИ, который соединен с входом установки в "1" второго триггера, вход разрешения записи первого операнда блока формирования пакетов команд соединен с входом установки в "1" третьего триггера и входом чтения-записи третьего регистра, информационный вход которого подключен к входу первого операнда блока формирования пакетов команд, вход признака одиночного операнда которого соединен с вторым входом элемента ИЛИ и вторым управляющим входом третьего коммутатора, первый и второй информационные входы которого соединены соответственно с входом логического "0" блока формирования пакетов команд и с входом второго операнда блока формирования пакетов команд, вход строба которого подключен к входу установки в "1" первого триггера и к входу чтения-записи первого регистра, а информационный вход первого регистра соединен с входом команды блока формирования пакетов команд.

Блок выборки данных содержит узел памяти данных и узел ассоциативной выборки адресов, причем узел ассоциативной выборки адресов содержит группу ассоциативных запоминающих элементов, первый, второй, третий и четвертый элементы ИЛИ, группу элементов ИЛИ, коммутатор, первый и второй приоритетные шифраторы, дешифратор, элемент И и элемент НЕ, при этом информационный вход первого разряда и вход сброса каждого запоминающего элемента соединены соответственно с входами управления режимом работы и сбросом памяти узла ассоциативной выборки адресов, входы разрешения записи и чтения подключены соответственно к входам управления записью аргумента и поиском данных узла ассоциативной выборки адресов, информационные входы второго разряда ассоциативных запоминающих элементов подключены к соответствующим выходам дешифратора, информационные входы третьего и четвертого разрядов ассоциативных запоминающих злементов подключены соответственно к входу аргумента поиска узла ассоциативной выборки адресов и к выходу элемента НЕ, первые и вторые информационные выходы ассоциативных запоминающих элементов подключены соответственно к входам первого и второго элементов ИЛИ, выходы которых являются соответственно выходом управления записью и выходом управления чтением узла ассоциативной выборки адресов, третий и четвертый информационные выходы ассоциативных запоминающих элементов подключены соответственно к входам третьего и четвертого элементов ИЛИ и первым и вторым входам соответствующих элементов ИЛИ группы, выходы которых соединены с соответствующими входами первого приоритетного шифратора и управляющими входами коммутатора, входы разрядов адреса которого подключены соответственно к пятым информационным выходам соответствующих ассоциативных запоминающих элементов, шестые информационные выходы которых соединены с входами второго приоритетного шифратора и соответствующими входами элемента И, выход которого является выходом переполнения памяти узла ассоциативной выборки адресов, выход второго приоритетного шифратора соединен с входом дешифратора, вход элемента НЕ соединен с выходом третьего элемента ИЛИ, являющимся первым выходом результата поиска узла ассоциативной выборки адресов, второй выход результата поиска которого соединен с выходом четвертого элемента ИЛИ, выходы коммутатора и первого приоритетного шифратора подключены к выходу адреса данных узла ассоциативной выборки адресов, первый информационный вход блока выборки данных соединен с входом начальной установки узла памяти данных и с входом управления поиском данных узла ассоциативной выборки адресов, второй информационный вход блока выборки данных подключен к входу данных узла памяти данных, вход разрешения записи результата блока выборки данных подключен к входу управления приемом данных узла памяти данных и к входу управления записью аргумента узла ассоциативной выборки адресов, вход управления режимом работы которого является одноименным входом блока выборки данных, входы аргумента поиска и сброса памяти которого соединены с одноименными входами узла ассоциативной выборки адресов, выход переполнения памяти, первый и второй выходы результата поиска пары узла ассоциативной выборки адресов являются одноименными выходами блока выборки данных, выход управления записью, выход управления чтением и выход адреса данных узла ассоциативной выборки адресов соединены с одноименными входами узла памяти данных, выход признака переполнения памяти, выход данных и выход признака готовности данных которого являются одноименными выходами блока выборки данных.

Сущность изобретения заключается в том, что введение блока формирования пакетов команд и коммутатора загрузки команд позволяет обеспечить одновременное исполнение операций в основных функциональных узлах: процессоре, блоке памяти команд и блоке выборки данных.

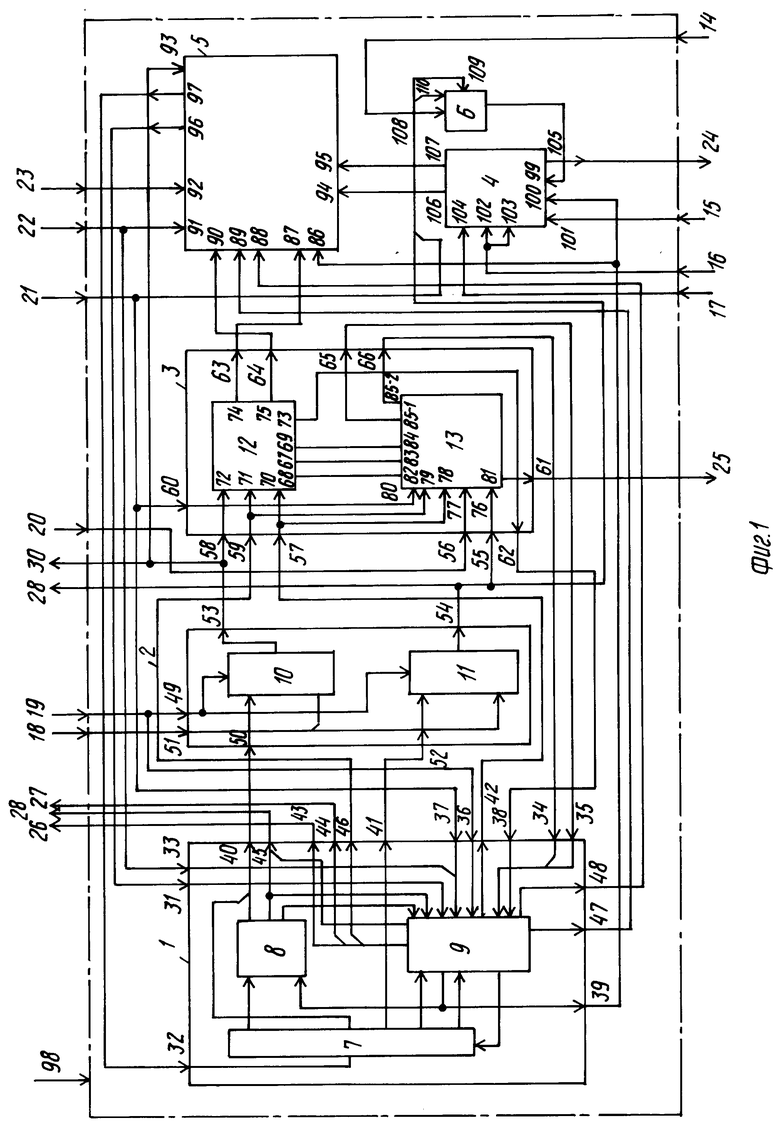

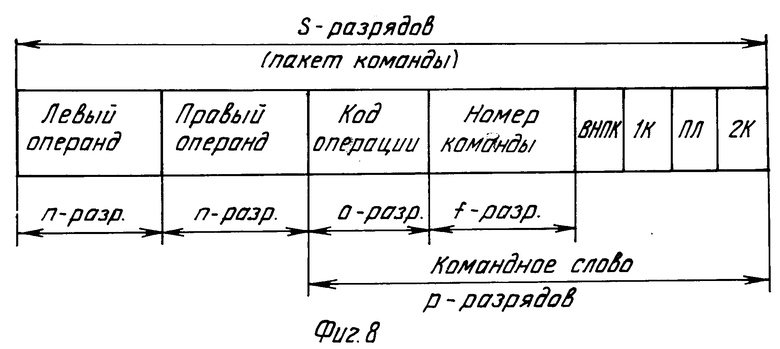

На фиг. 1 представлена функциональная блок-схема устройства для обработки информации; на фиг.2 - функциональная электрическая схема блока входных регистров; на фиг.3 - блока микропрограммного управления; на фиг.4 - узла памяти данных; на фиг.5 - узла ассоциативной выборки адресов; на фиг.6 - ассоциативного запоминающего элемента; на фиг.7 - блока формирования пакетов команд; на фиг.8 показан пример разрядных полей пакета команды.

Устройство содержит процессор 1, блок 2 ввода-вывода, блок 3 выборки данных, блок 4 памяти команд, блок 5 формирования пакетов команд и коммутатор 6 загрузки команд. Процессор 1 содержит блок 7 входных регистров, АЛУ 8 и блок 9 микропрограммного управления. Блок 2 ввода-вывода содержит коммутатор 10 данных и коммутатор 11 номера команд. Блок 3 выборки данных содержит узел 12 памяти данных и узел 13 ассоциативной выборки адресов.

Устройство содержит входы 14...23 соответственно адресный, управления записью командного слова, разрешения записи командного слова, информационного командного слова, для ввода полупакета данных, кода режима устройства, сброса памяти, управления режимом работы устройства, разрешения загрузки пакета данных и для ввода пакета данных и выходы 24...30 соответственно признака конца записи командного слова, признака переполнения памяти, разрешения записи следующего полупакета данных, разрешения записи следующего пакета данных, адреса следующей команды, кода прерывания, результата устройства. Процессор 1 содержит входы 31...38 соответственно признака готовности пакета данных, команды, разрешения загрузки пакета данных, первый и второй результата поиска пары, управления загрузкой полупакета данных, управления режимом работы и информационный и выходы 39...48 соответственно управления пуском, первый и второй информационные, сигнала управления поиском данных, разрешения записи следующего полупакета данных, разрешения записи следующего пакета данных, кода прерывания, управляющий, управления передачей результата, признака одиночного операнда. Блок 2 ввода-вывода содержит управляющий вход 49, первый, второй и третий информационные входы 50, 51 и 52 соответственно и первый и второй выходы 53 и 54.

Блок 3 выборки данных содержит входы 55...60 соответственно аргумента поиска, сброса памяти, первый и второй информационные, разрешения записи результата и управления режимом работы и выходы 61...66 соответственно переполнения памяти, признака переполнения памяти, данных, признака готовности данных и первый и второй результата поиска. Узел 12 памяти данных содержит входы 67...72 управления чтением, управления записью, адреса данных, начальной установки, управления приемом данных и данных и выходы 73...75 признака переполнения памяти, данных и признака готовности данных соответственно. Узел 13 ассоциативной выборки адресов содержит входы 76...80 аргумента поиска, сброса памяти, управления поиском данных, управления записью аргумента, управления режимом работы и выходы 81...84 и 85-1, 85-2 переполнения памяти, управления записью, управления чтением, адреса данных и первый и второй результата поиска соответственно.

Блок 5 формирования пакетов команд содержит входы 86...95 начальной установки, второго операнда, признака одиночного операнда, разрешения записи первого операнда, разрешения записи второго операнда, признака готовности внешнего пакета, для ввода пакета данных, первого операнда, команды и строба и выход 96 признака готовности пакета, группу информационных выходов 97 соответственно. Входы синхронизации процессора 1, блока 2 ввода-вывода, блока 3 выборки данных, блока 4 памяти команд, блока 5 формирования пакетов команд и коммутатора 6 загрузки команд соединены с входом 98 синхронизации устройства.

Блок 4 памяти команд содержит входы 99...104 информационный, управления чтением, управления записью, признака передачи командного слова, управления приемом командного слова и разрядов командного слова и выходы 105...107 признака конца записи командного слова, информационный и признака готовности соответственно. Первый информационный вход 108 коммутатора 6 загрузки команд является адресным входом 14 устройства. Управляющий вход 109 коммутатора 6 подключен к входу 21 управления режимом работы устройства, второй информационный вход 110 коммутатора 6 соединен с вторым выходом 54 блока 2 ввода-вывода, а выход коммутатора 6 соединен с информационным входом 99 блока 4 памяти команд.

Блок 7 входных регистров (фиг.2) содержит соответственно первый, второй, третий, четвертый и пятый буферные регистры 111, 112, 113, 114 и 115 приема пакетов команд, информационный вход 116-1, управляющий вход 116-2 и информационные выходы 117-1...117-5.

АЛУ 8 выполнено аналогично устройству по авт.св. СССР N 1367012, кл. G 06 F 7/36, 1985, и содержит соответственно информационный вход, соединенный с первым информационным выходом 117-1 блока 7. Управляющий вход АЛУ соединен с выходом 139-1 блока 9 микропрограммного управления. Информационный, первый и второй управляющие выходы АЛУ подключены к первому информационному выходу 40 и выходу 45 кода прерывания процессора 1 и входу 138-2 блока 9.

Блок 9 микропрограммного управления (фиг.3) содержит первый, второй и третий элементы ИЛИ 118, 119 и 120, первый, второй и третий элементы И 121, 122 и 123, первый, второй, третий, четвертый и пятый триггеры 124, 125, 126, 127 и 128, четвертый, пятый, шестой, седьмой и восьмой элементы И 129, 130, 131, 132 и 133, элемент НЕ 134, четвертый и пятый элементы ИЛИ 135 и 136 и девятый элемент И 137, входы 138-1...138-9 и выходы 139-1...139-8.

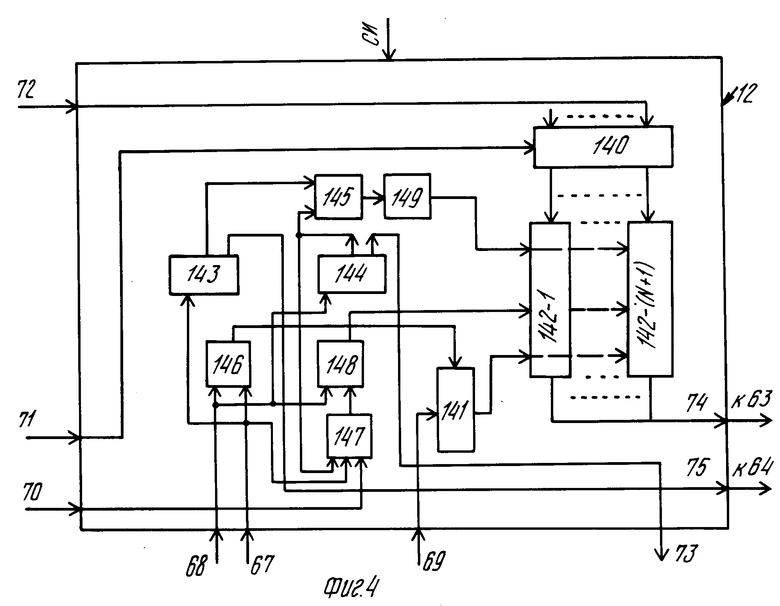

Узел 12 памяти данных (фиг.4) содержит соответственно первый и второй буферные регистры 140 и 141, группу БИС ЗУ 142-1...142-(N+1) прямого доступа типа КР132РУ6, первый и второй регистры 143 и 144 сдвига, первый, второй и третий элементы ИЛИ 145, 146 и 147, триггер 148 и элемент НЕ 149. Информационные входы первого буферного регистра 140 соединены с входом 72 данных узла 12 памяти данных, а выходы БИС ЗУ 142-1...142-(N+1) - с выходом 74 данных узла 12 памяти данных.

Узел 13 ассоциативной выборки адресов (фиг.5) содержит соответственно группу ассоциативных запоминающих элементов 150-1...150-К, первый и второй элементы ИЛИ 151 и 152, группу элементов ИЛИ 153-1...153-К, коммутатор 154, первый и второй приоритетные шифраторы 155 и 156, дешифратор 157, элемент И 158, третий и четвертый элементы ИЛИ 159 и 160, элемент НЕ 161. Каждый i-й элемент из группы элементов ИЛИ 150-1...150-К содержит информационные входы 162-i, 163-i, 164-i и 165-i первого, второго, третьего и четвертого разрядов, входы 166-i и 167-i разрешения записи и разрешения чтения, вход 168-i сброса и первый. . .шестой разряды выходов 169-i...174-i. Первый, второй, третий и четвертый элементы ИЛИ 151, 152, 159 и 160 имеют входы 175-1... 175-К, 176-1...176-К, 177-1...177-К и 178-1...178-К соответственно. Дешифратор 157 имеет выходы 179-1...179-К, каждый i-й из которых подключен к соответствующему i-му входу 163-i разрешения записи ассоциативного запоминающего элемента 150-i. Группа входов 180-1...180-К первого приоритетного шифратора 155 и группа управляющих входов 181-1...181-К коммутатора 154 подключены к выходам соответствующих элементов ИЛИ 153-1...153-К. Входы 181-1.. . 182-К разрядов кода адреса коммутатора 154 подключены к выходам 173-1... 173-К кода адреса числа соответствующих ассоциативных запоминающих элементов 150-1. . .150-К, а входы 183-1...183-К элемента И 158 и входы 184-1... 184-К второго приоритетного шифратора 156 соединены с выходами 174-1... 174-К признака переполнения соответствующих ассоциативных запоминающих элементов 150-1...150-К.

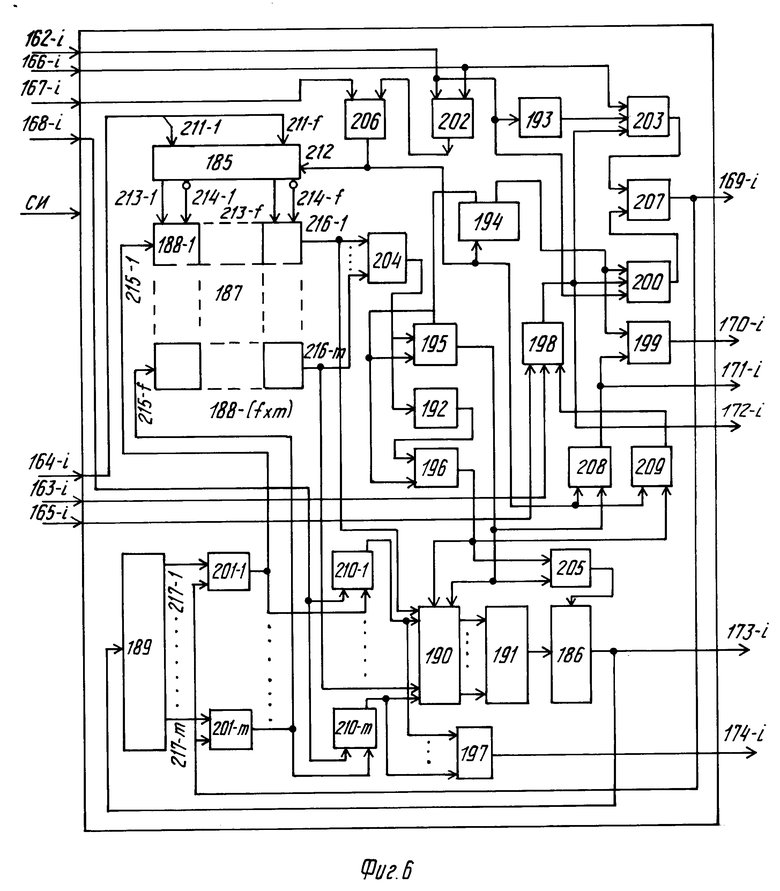

Каждый ассоциативный запоминающий элемент 150-i (фиг.6) содержит первый и второй буферные регистры 185 и 186, матрицу 187 из f x m ассоциативных запоминающих микроэлементов 188-1...188-(f x m), дешифратор 189, коммутатор 190, приоритетный шифратор 191, первый и второй элементы НЕ 192 и 193, регистр 194 сдвига, первый-шестой элементы И 195...200, группу элементов И 201-1. . . 201-m, седьмой и восьмой элементы И 202 и 203, первый-четвертый элементы ИЛИ 204...207, первый и второй триггеры 208 и 209 и группу триггеров 210-1...210-m. Входы 211-1...211-f регистра 185 подключены к соответствующему входу 164-i разрядов номера команды, вход 212 управления регистра 185 подключен к выходу элемента ИЛИ 206. Каждая пара парафазных выходов 213-1, 214-1...213-f, 214-f первого буферного регистра 185 и линейные входы 215-1. . .215-m записи подключены к соответствующим микроэлементам 188-1... 188-(f x m) матрицы 187, выходы 216-1...215-m которой подключены к соответствующим входам первого элемента ИЛИ 204 и коммутатора 190. Выходы 217-1. . . 217-m дешифратора 189 соединены с первыми входами элементов И 201-1...201-m.

Блок 5 формирования пакетов команд (фиг.7) содержит первый, второй и третий коммутаторы 218, 219 и 220, первый, второй и третий регистры 221, 222 и 223 формирования пакета, первый, второй и третий триггеры 224, 225 и 226, элемент И 227 и элемент ИЛИ 228. Первый коммутатор 218 имеет первый и второй информационные входы 229 и 230 и первый и второй управляющие входы 231 и 232. Второй коммутатор 219 имеет первый и второй информационные входы 233 и 234 и первый и второй управляющие входы 235 и 236. Выходы первого и второго коммутаторов подключены к информационному выходу 97 блока 5 формирования пакетов команд. Третий коммутатор 220 содержит первые, вторые информационные и управляющие входы 237, 238 и 239, 240 и выход 241, подключенный к информационному входу второго регистра 222.

Первый информационный вход 50 блока 2 ввода-вывода соединен с первым информационным выходом 40 процессора 1. Вход 18 для ввода полупакета данных устройства соединен с вторым информационным входом 51 блока 2 ввода-вывода, управляющий вход 49 которого соединен с входом 19 кода режима устройства. Второй информационный выход 41 процессора 1 соединен с третьим информационным входом 52 блока 2 ввода-вывода, первый выход 53 которого соединен с первым информационным входом 58 блока 3 выборки данных и выходом 30 результата устройства. Выход 28 адреса следующей команды устройства соединен с входом 55 аргумента поиска блока 3 выборки данных и с вторым выходом 54 блока 2 ввода-вывода. Первый информационный выход 62 блока 3 выборки данных соединен с информационным входом 38 процессора 1, выход 43 разрешения записи следующего полупакета данных которого является одноименным выходом 26 устройства. Выход 29 кода прерывания устройства соединен с одноименным выходом 45 процессора 1, выход 44 разрешения записи следующего пакета данных которого является одноименным выходом 27 устройства. Управляющий выход 46 процессора 1 соединен с входом 59 разрешения записи результата блока 3 выборки данных. Вход 31 признака готовности пакета данных процессора 1 соединен с выходом 96 признака готовности пакета блока 5 формирования пакетов команд, группа информационных выходов 97 которого соединена с входом 32 команды процессора 1, вход 33 разрешения загрузки пакета данных которого является одноименным входом 92 устройства и соединен с входом 91 признака готовности внешнего пакета блока 5 формирования пакетов команд. Вход 92 для ввода пакета данных блока 5 является одноименным входом 23 устройства. Вход 21 управления режимом работы устройства подключен к входу 109 управления коммутатора 6 загрузки команд, входу 60 управления режимом работы блока 3 выборки данных и одноименному входу 37 процессора 1. Выход 42 сигнала управления поиском данных процессора соединен с первым информационным входом 57 блока 3 выборки данных, вход 56 сброса памяти которого соединен с одноименным входом 20 устройства. Адресный вход 14 устройства соединен с первым информационным входом 108 коммутатора 6 загрузки команд, выход которого подключен к информационному входу 99 блока 4 памяти команд. Информационный выход 106 и выход 107 признака готовности блока 4 соединены соответственно с входами 94 и 95 команды и строба соответственно блока 5 формирования пакетов команд. Вход 93 первого операнда блока 5 подключен к выходу 53 блока 2 ввода-вывода. Первый и второй входы 34 и 35 результатов поиска процессора 1 соединены соответственно с одноименными выходами 65 и 66 блока 3 выборки данных, выход 63 данных и выход 64 признака готовности данных которого подключены соответственно к входу 87 второго операнда и входу 90 разрешения записи второго операнда блока 5 формирования пакетов команд. Вход 88 признака одиночного операнда и вход 89 разрешения записи первого операнда блока 5 соединены соответственно с выходом 48 признака одиночного операнда и выходом 47 управления передачей результата процессора, выход 39 управления пуском которого подключен к входу 86 начальной установки блока 5 формирования пакета команд и к входу 100 управления чтением блока 4 памяти команд. Вход 101 управления записью блока 4 является одноименным входом 15 устройства, информационный вход 17 командного слова и вход 16 разрешения записи командного слова которого соединены соответственно с входом 104 разрядов командного слова и входом 103 управления приемом командного слова блока 4 памяти команд. Вход 103 управления приемом командного слова блока 4 соединен с входом 102 признака передачи командного слова блока 4 памяти команд.

Устройство обеспечивает выполнение программы, поступающей по входу 23 от внешней управляющей вычислительной системы (на фигурах не показана), и выдачу результатов обработки по выходу 30. Инициализация работы начинается с момента подачи стартового пакета на вход 92 и управляющего сигнала на вход 91 блока 5 формирования пакетов команд и вход 33 процессора 1. При этом на вход 138-1 блока 9 и далее на вход элемента ИЛИ 119 поступает сигнал признака готовности пакета загрузки, а на его выходе формируется сигнал приема, поступающий на вход 116-2 блока 7 входных регистров. На выходах 117-1. . . 117-5 блока 7 входных регистров формируется код, соответствующий функциональным разрядным полям пакета команды (фиг.8).

Одновременно происходит формирование сигнала "Пуск" на выходе 139-1 блока 9, поступающего на управляющий вход АЛУ 8 и выход 39 процессора 1, откуда поступает на входы 100 и 86 блока 4 памяти команд и блока 5 формирования пакетов команд соответственно. C выхода 40 процессора 1 сигнал разряда кода номера команды поступает через блок 2 ввода-вывода на вход 55 блока 3 выборки данных и вход 110 коммутатора 6, с выхода которого при отсутствии управляющего сигнала на входе 109 подается на вход 100 блока 4 памяти команд.

При наличии на входах 117-3 и 117-4 блока 7 сигнала логической "1", соответствующего наличию признака 2К (двухвходовой команды), на выходе 139-7 блока 9 формируется сигнал управления поиском пары (УПРПП), совпадающий по времени с сигналом "Пуск". Последний поступает на вход 57 блока 3 выборки данных, инициализируя его запуск.

Таким образом, при формировании сигнала "Пуск" в устройстве осуществляются параллельный запуск трех функциональных устройств: процессора 1, блока 3 выборки данных и блока 4 памяти команд, а также обнуление блока 5 формирования пакетов команд.

В узле 13 сигнал УПРПП с входа 57 поступает на входы 167-1...167-К группы ассоциативных запоминающих элементов 150-1...150-К и через элемент ИЛИ 206 формируется управляющий сигнал для буферного регистра 185, по которому на последний принимается код аргумента поиска (разряды номера команды). Запускается сдвиговой регистр 194, и осуществляется установка в нулевое состояние триггеров 208, 209. Парафазный код с выходов 213-1...213-f и 214-1. . . 214-f регистра 185 поступает соответственно на разрядные входы "плюс" и "минус" матрицы 187.

Если происходит совпадение значений разрядов кода с выходов регистра 185 и кода, хранящегося в j-й строке матрицы 187 i-го элемента группы (j=1. . .m, a i=1...K), то на соответствующем выходе 216-j группы выходов матрицы 187 формируется сигнал признака сравнения, который поступает на j-й вход элемента ИЛИ 204 и j-й вход группы входов коммутатора 190. С выхода элемента ИЛИ 204 сигнал поступает на второй вход элемента И 195 и на вход элемента НЕ 192, причем на первый вход элемента И 195 поступает сигнал с первого выхода сдвигового регистра 194. При этом на выходе элемента И 195 формируется сигнал, который поступает на первый вход триггера 208, на первый вход элемента ИЛИ 205 и на первый управляющий вход коммутатора 190. На выходе триггера 208 устанавливается сигнал логической "1", поступающий на третий выход 171 i-го элемента (сигнал признака сравнения CРМi), и на первый вход элемента И 199, на второй вход которого поступает сигнал с второго выхода сдвигового регистра 194. На выходе элемента И 199 формируется сигнал ПРЧТi - признак чтения, который поступает на выход 170 i-го элемента группы.

На j-м выходе группы выходов коммутатора 190 формируется сигнал логической "1", соответствующий j-й строке матрицы 187, где произошло совпадение аргументов, который поступает на приоритетный шифратор 191, формирующий код, соответствующий адресу хранения числа в группе БИС ЗУ узла 12. Этот код с выхода регистра 186 поступает на выход 173-i i-го элемента группы.

Сигналы ПРЧТi, CPMi и код адреса формируются только в том элементе группы, где произошло совпадение аргумента на выходе регистра 185 с аргументом, хранящимся в j-й строке матрицы 187. Выходы всех элементов группы по сигналам ПРЧTi и СРМi объединяются соответственно через элементы ИЛИ 152 и 159, с выходов которых на выходы 82 и 85-1 соответственно поступают сигналы УПРЧТ и СР (сигнал кода результата сравнения аргументов). При этом сигнал УПРЧТ поступает с выхода 82 на вход узла 12, а сигнал СР через выход 85-1 блока 3 поступает на вход 35 процессора 1.

Разряды кода адреса с выхода регистра 186 через выход 173 элемента поступают на соответствующий вход 182-i коммутатора 154, на вход 181-i которого поступает сигнал управления с выхода элемента ИЛИ 153-i, на первый вход которого поступает сигнал признака несравнения аргумента (НСРМ) с выхода 172-i, а на второй вход - сигнал СРМi c выхода 171-i группы элементов.

При наличии сигнала СРМi на выходе i-го элемента (предполагается, что имеется только один парный операнд) сигналы НСРМ1...НСРМК не формируются, так как цепь их формирования блокируется сигналом блокировки записи нулевого уровня с выхода элемента НЕ 161, который поступает на вход 165-i каждого элемента группы, а с него на третий вход элемента И 198. На выходе коммутатора 154 при этом формируются младшие разряды кода адреса, которые поступают на выход 84, куда поступает и код старших разрядов, сформированный на выходе приоритетного шифратора 155, на входах 180-1...180-К которого присутствуют сигналы с выходов группы элементов ИЛИ 153-1...153-К.

С выхода 84 узла 13 разряды кода адреса поступают на вход узла 12 памяти данных и далее на информационный вход регистра 141, на управляющий вход которого поступает при этом сигнал с выхода элемента ИЛИ 146, на первый вход которого поступает сигнал УПРЧТ с выхода 82. На выходе регистра 141 устанавливается код адреса, который поступает на адресный вход группы БИС ЗУ 142-1...142-(N+1).

С выхода триггера 148 поступает сигнал логической "1" на первый вход управления записью-чтением, а на второй вход - сигнал с выхода регистра 143 сдвига сигнала УПРЧТ на время, необходимое для работы БИС ЗУ. При этом через время, определяемое работой БИС ЗУ, на его выходах формируется код числа с признаком ПЛ (место операнда в пакете), а на втором выходе регистра 143 - соответствующий ему по времени сигнал ПЧ (передачи числа), которые поступают соответственно на выходы 63 и 64 блока 3. Сигнал ПЧ поступает на второй вход элемента ИЛИ 228 и на вход 239 управления коммутатора 220, на информационный вход 238 которого поступают разряды кода числа (второго операнда) с признаком ПЛ с входа 87 блока 5. В результате на регистр 222 принимается код второго операнда, выбранного из узла 12 памяти данных по факту совпадения кодов номеров команды, относящейся к ожидаемому результату АЛУ 8. Одновременно происходит установка в единичное состояние триггера 225.

На информационном выходе блока 4 памяти команд по сигналу "Пуск" происходит формирование разрядов кода командного слова, которые поступают на регистр 221 блока 5 по сигналу ПКС (передача командного слова) с выхода блока 4 памяти команд с одновременной установкой в единичное состояние триггера 224.

В процессоре по окончании работы АЛУ 8 формируются разряды кода результата на выходе 40, а на другом выходе - сигнал логической "1", поступающий на вход 138-2 блока 9. При этом на выходе 139-4 блока 9 формируется сигнал УЗПРГ 1 (управления записью в первый регистр пакета). На выходе 53 блока 2 формируется код числа, соответствующий результату на выходе 40 процессора 1, вместе с признаком ПЛ, которые поступают на вход 87 блока 5.

Сигнал УЗПРГ 1 поступает на первый вход триггера 226 и управляющий вход регистра 223, в результате чего на выходе триггера 226 устанавливается сигнал логической "1", а на выходе регистра 223 - код первого операнда с признаком ПЛ. При этом на выходе элемента И 227 формируется сигнал ПРПК, который определяет наличие очередного пакета команды, готового к обработке в процессоре 1.

Разряды кода функциональных групп пакета с выходов регистров 221-223 поступают на первый многоразрядный информационный вход 229 коммутатора 218, на первый вход 231 управления которого поступает сигнал с выхода элемента И 227. С выхода коммутатора 218 разряды кода первого и второго операндов поступают соответственно на первый и второй многоразрядные информационные входы 233 и 234 коммутатора 219, а разряды признаков ПЛ первого и второго операндов поступают на его первый и второй управляющие входы 235 и 236. При этом на первом и втором выходах коммутатора 219 формируются разряды соответственно правого и левого операндов пакета, которые поступают на выход 97 блока 5. Очередной готовый пакет поступает на исполнение.

Когда при сравнении кода входного аргумента с кодами, хранящимися в матрицах элементов 150-1...150-К, равенства кодов не обнаруживается (т.е. ни один из элементов группы не формирует сигнала СРМi), на выходе элемента И 196 формируется сигнал, соответствующий факту несовпадения аргументов, и происходит установка в единичное состояние триггера 209. При этом на выходе регистра 186 формируется код адреса, соответствующий сигналам на входах коммутатора 190, которые соответствуют состоянию группы триггеров 210-1... 210-m, определяющих уровень заполнения матрицы 187, а на выходе элемента И 198 i-го элемента группы устанавливается единичный уровень, определяемый условием совпадения единичных сигналов на его входах. На один вход элемента И 198 при этом поступает единичный уровень с выхода триггера 209, а на другой вход - единичный уровень с входа 165-i элемента, соответствующий сигналу на выходе элемента НЕ 161 (определяемый отсутствием на его входе сигнала СР с выхода элемента ИЛИ 159). На третий вход элемента И 198 i-го элемента группы поступает сигнал разрешения записи в элемент, соответствующий выходу 179-i дешифратора 157 и определяющий номер младшего незаполненного элемента. Код на входе дешифратора формируется шифратором 156 из соответствующих сигналов заполнения элементов на входах 184-1...184-К.

Таким образом, единичный уровень на выходе элемента И 198 и на выходе 172-i появляется только в младшем незаполненном элементе.

При поступлении на выход 172-i сигнала НСРМi на втором управляющем выходе узла 13 формируется сигнал НСР, который поступает на вход 35 процессора 1. При этом на выходе 139-9 блока 9 формируется сигнал управления записью полупакета, который поступает на вход 57 блока 3, и в узле 12 осуществляется прием числа с выхода 53 блока 2 на регистр 140, а в узле 13 происходит формирование сигнала признака записи на выходе элемента И 203 i-го элемента группы. При этом на выходе элемента ИЛИ 207 i-го элемента группы формируется сигнал признака записи ПРЗПi, который поступает на первые входы элементов И 201-1...201-m и на выход 169-i элемента. Адрес, сформированный на выходе регистра 186 и соответствующий свободной строке матрицы 187, поступает на вход дешифратора 189, на выходе 217-j которого формируется сигнал разрешения записи аргумента РЗПАj, поступающий на второй вход соответствующего элемента И 201-j, на выходе которого формируется сигнал, поступающий на вход 215-j линий записи матрицы, что соответствует записи входного аргумента в j-ю строку с одновременной установкой в единичное состояние триггера 210-j.

Сформированный на выходе 169-i сигнал ПРЗПi поступает на вход 175-i элемента ИЛИ 151, с выхода которого (в виде сигнала УПРЗП) поступает на второй управляющий вход узла 12 памяти данных, на второй информационный вход которой поступают разряды кода адреса записи числа с выхода коммутатора 154 и приоритетного шифратора 155. При этом сигналы на входах 180-1... 180-К шифратора 155 и на управляющих входах 181-1...181-К коммутатора 154 определяются условиями формирования сигнала НСРМi на выходе 172-i запоминающего элемента группы.

Сигнал УПРЗП поступает на второй вход элемента ИЛИ 146, на второй вход триггера 148 и на вход сдвигающего регистра 144. При этом происходят прием разрядов адреса на регистр 141 и передача их на адресный вход группы БИС ЗУ 142-1. . . 142-(N+1), установка в нулевое состояние триггера 148 и формирование на выходе элемента НЕ 149 нулевого импульсного сигнала управления в соответствии с задержкой, определяемой первым выходом регистра 144 сдвига, в результате чего осуществляется запись разрядов кода числа с регистра 140 в БИС ЗУ 142-1...142-(N+1). Сформированный на втором выходе сдвигового регистра 144 сигнал КНЗП (конец записи) поступает через выход 62 блока 3 на вход 38 процессора 1, в результате чего происходит установка в единичное состояние триггера 128 (через элемент И 130), что соответствует формированию на выходе блока 9 сигнала запроса пакета, который поступает на выход 27. По этому сигналу от внешней управляющей системы поступают разряды кода пакета загрузки и сигнал признака готовности пакета загрузки ПРПКЗ. Через коммутаторы 218, 219 функциональные группы разрядов пакета поступают на вход 32 процессора 1, а на его вход - сигнал ПРПКЗ.

Когда команда, к которой относится результат текущих вычислений, имеет признак 1К, т. е. является одновходовой, формирование сигнала УПРПП не происходит и блок 3 не работает. По окончании работы АЛУ 8 сигнал ПРГР по условию 1К-1 поступает на блок 9, где на выходе элемента И 131 формируется сигнал признака одиночного операнда ПР1ОП, который через выход блока 9 поступает на вход 86 блока 5, где осуществляются запись нулей в регистр 222 через коммутатор 220 и одновременная установка в единичное состояние триггера 225.

Одновременно с выхода элемента И 131 сигнал ПР1ОП через элемент ИЛИ 135 поступает на выход 139-9 блока 9 в виде сигнала УЗПРГ1, в результате чего осуществляется прием результата АЛУ на регистр 223 формирования пакета. Прием командного слова на регистр 221 происходит аналогично рассмотренному выше.

Таким образом, введение дополнительных узлов позволяет повысить производительность устройства за счет сокращения периода следования готовых пакетов команд на исполнение в АЛУ 8, что достигается путем организации параллельного формирования функциональных разрядных групп, входящих в пакет команды. При этом период следования готового пакета не превышает максимальное время отработки любого функционального узла max Ti. Степень сокращения периода следования пакетов зависит от соотношения времен работы функциональных устройств, участвующих в формировании пакета команды, и может быть представлено как

M =  =

=  где Тi - время работы одного узла;

где Тi - время работы одного узла;

ТППК1 - период следования пакетов при последовательной работе узлов;

ТППК2 - период следования пакетов при параллельной работе узлов.

Макетные испытания показали возможность промышленного использования предлагаемого устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПТИЧЕСКОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2035069C1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| ЦИФРОВОЙ МНОГОКАНАЛЬНЫЙ СИНТЕЗАТОР СЕТКИ ЧАСТОТ | 1995 |

|

RU2108655C1 |

| КОНВЕЙЕРНЫЙ ПРОЦЕССОР | 1992 |

|

RU2032215C1 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1995 |

|

RU2110089C1 |

| СПОСОБ КОДИРОВАНИЯ И ИСПОЛНЕНИЯ КОНТЕКСТНО-ЗАВИСИМОЙ ПРОГРАММЫ МУЛЬТИКЛЕТОЧНЫМ ПРОЦЕССОРОМ, МУЛЬТИКЛЕТОЧНЫЙ ПРОЦЕССОР, КЛЕТКА И КОММУТАЦИОННОЕ УСТРОЙСТВО МУЛЬТИКЛЕТОЧНОГО ПРОЦЕССОРА ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА | 2013 |

|

RU2530690C2 |

| Архитектура параллельной вычислительной системы | 2016 |

|

RU2644535C2 |

| Вычислительная система | 1977 |

|

SU692400A1 |

Изобретение относится к вычислительной технике, в частности к вычислительным устройствам, использующим управление вычислительным процессом от потока данных, и может быть использовано в цифровых вычислительных системах высокой производительности. Устройство для обработки информации содержит процессор, блок ввода-вывода, блок выборки данных, блок памяти команд, блок формирования пакетов команд и коммутатор загрузки команд. Процессор содержит блок входных регистров, АЛУ и блок микропрограммного управления. Блок ввода-вывода содержит коммутатор данных и коммутатор номера команд. Блок выборки данных содержит узел памяти данных и узел ассоциативной выборки адресов. Введение блока формирования пакетов команд и коммутатора загрузки команд позволяет повысить быстродействие за счет обеспечения параллельного формирования функциональных составляющих пакетов команд. 2 з.п.ф-лы, 8 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| The Manchester Prototipe Dataflow Computer, J.R | |||

| Curd и др | |||

| Communication of the ACM, Vol.28, 1. | |||

Авторы

Даты

1995-02-20—Публикация

1991-12-29—Подача