Изобретение относится к электросвязи и может быть использовано для исправления ошибок в каналах связи, подверженных воздействию помех.

Известно устройство [1] для декодирования линейных кодов, позволяющее исправлять ошибки в канале связи и простое для реализации.

Известно устройство [2] для декодирования линейных кодов, обладающее более высокими корректирующими способностями и содержащее блок разделения символов, поразрядно связанные регистр и комбинационный сумматор, N последовательно соединенных блоков декодирования, причем первый, второй и третий выходы каждого блока декодирования связаны соответственно с первым, вторым и третьим входами следующего блока декодирования, первый и второй выходы блока разделения символов связаны соответственно с входом регистра и комбинационного сумматора, а выход регистра связан с первым входом первого блока декодирования, причем первый блок декодирования состоит из проверочного блока, сумматора и элемента задержки, выход которого связан с первым входом сумматора, второй вход которого связан с первым выходом проверочного блока, причем вторым и третьим входами блока декодирования являются соответственно первый и второй входы проверочного блока, а первым, вторым и третьим выходами являются выход сумматора, второй и третий выходы проверочного блока, а остальные блоки декодирования состоят из проверочного блока, регистра, последовательно связанного через элемент задержки с первым входом сумматора, второй вход которого связан с первым выходом проверочного блока, причем первым, вторым и третьим входами блока декодирования являются соответственно вход регистра, первый и второй входы проверочного блока, а первым, вторым и третьим выходами являются выход сумматора, второй и третий выходы проверочного блока, который состоит из последовательно и поразрядно связанных между собой первого коммутатора, первого регистра, решающего устройства и второго коммутатора, второго регистра, выход которого связан с первым входом сумматора и входом решающего устройства, выход которого связан с входом первого коммутатора, вторым входом сумматора и является первым выходом проверочного блока, вторым и третьим выходами которого являются соответственно выход первого регистра и выход сумматора, а второй вход проверочного блока является входом второго регистра; вход блока разделения символов является входом всего устройства. Данное устройство выбрано в качестве прототипа.

Недостатком прототипа является большая задержка декодирования при высокой вероятности ошибок в канале связи. Это обусловлено тем, что при высокой вероятности ошибок в канале для обеспечения допустимой вероятности ошибок на выходе устройства применяется большое число N блоков декодирования [3].

Для устранения рассмотренного недостатка предлагается осуществлять многократное декодирование символа в каждом блоке декодирования.

Задача заявляемого решения на предлагаемое изобретение состоит в уменьшении задержки устройства декодирования.

Для получения технического результата в устройство для декодирования линейных кодов, включающее блок разделения символов, поразрядно связанные регистр и комбинационный сумматор, N последовательно соединенных блоков декодирования, причем первый, второй и третий выходы каждого блока декодирования связаны соответственно с первым, вторым и третьим входами следующего блока декодирования, первый и второй выходы блока разделения символов связаны соответственно с входом регистра и комбинационного сумматора, а выход регистра связан с первым входом первого блока декодирования, причем первый блок декодирования состоит из проверочного блока, сумматора и элемента задержки, выход которого связан с первым входом сумматора, второй вход которого связан с первым выходом проверочного блока, причем вторым и третьим входами блока декодирования являются соответственно первый и второй входы проверочного блока, а первым, вторым и третьим выходами являются выход сумматора, второй и третий выходы проверочного блока, а остальные блоки декодирования состоят из проверочного блока, регистра, последовательно связанного через элемент задержки с первым входом сумматора, второй вход которого связан с первым выходом проверочного блока, причем первым, вторым и третьим входами блока декодирования являются соответственно вход регистра, первый и второй входы проверочного блока, а первым, вторым и третьим выходами являются выход сумматора, второй и третий выходы проверочного блока, который состоит из последовательно и поразрядно связанных между собой первого коммутатора, первого регистра, решающего устройства и второго коммутатора, второго регистра, выход которого связан с первым входом сумматора и входом решающего устройства, выход которого связан с входом первого коммутатора, вторым входом сумматора и является первым выходом проверочного блока, вторым и третьим выходами которого являются соответственно выход первого регистра и выход сумматора, а второй вход проверочного блока является входом второго регистра, вход блока разделения символов является входом всего устройства, введены шесть регистров, причем первым входом проверочного блока является вход его первого регистра, вход первого добавленного регистра является первым входом первого блока декодирования, а выход связан с входом элемента задержки первого блока декодирования, выход комбинационного сумматора через второй добавленный регистр связан со вторым входом первого блока декодирования, выход третьего добавленного регистра связан с третьим входом первого блока декодирования, а первый, второй и третий выходы N-го блока декодирования связаны соответственно с входами четвертого, пятого и шестого добавленных регистров, причем выход четвертого добавленного регистра является выходом устройства.

Предлагаемое техническое решение устройства для декодирования линейных кодов характеризуется тем, что позволяет в несколько раз снизить задержку декодирования, что достигается введением шести регистров и новых связей.

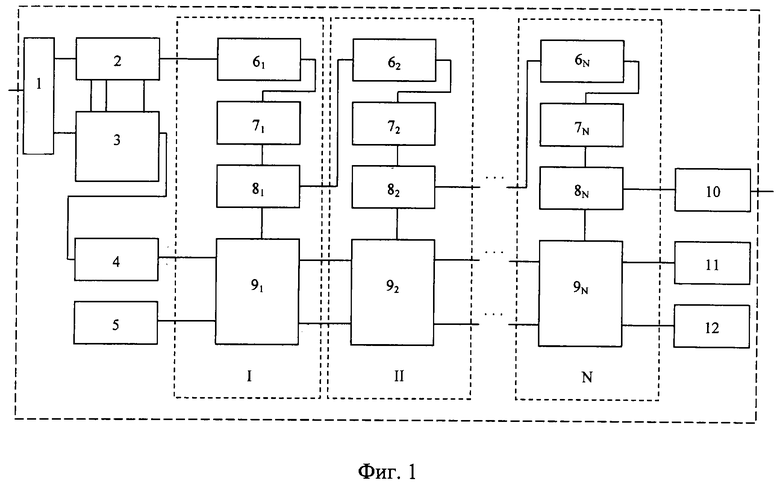

Структурная схема устройства представлена на фиг.1, 2.

Устройство для декодирования линейных кодов включает блок разделения символов 1, шесть буферных регистров 2, 4, 5, 10, 11 и 12, комбинационный сумматор 3 и N последовательно соединенных блоков декодирования, причем первый, второй и третий выходы каждого блока декодирования связаны соответственно с первым, вторым и третьим входами следующего блока декодирования, первый и второй выходы блока разделения символов 1 связаны соответственно с входами поразрядно связанных регистра 1 и комбинационного сумматора 3, а выходы регистров 2, 4 и 5 связаны соответственно с первым, вторым и третьим входами блока декодирования I, причем блок декодирования состоит из проверочного блока 9, информационного регистра 6, последовательно связанного через элемент задержки 7 с первым входом сумматора 8, второй вход которого связан с первым выходом проверочного блока 9, причем первым, вторым и третьим входами блока декодирования I являются соответственно вход информационного регистра 6, первый и второй входы проверочного блока 9, а первым, вторым и третьим выходами являются выход сумматора 8, второй и третий выходы проверочного блока 9, который состоит из последовательно и поразрядно связанных между собой синдромного коммутатора 13, синдромного регистра 14, вход которого является первым входом проверочного блока 9, решающего устройства 15 с коммутатором 16, разностного регистра 17, выход которого связан с первым входом сумматора 18 и входом решающего устройства 15, выход которого связан с входом синдромного коммутатора 13, вторым входом сумматора 18 и является первым выходом проверочного блока 9, вторым и третьим выходами которого являются соответственно выход синдромного регистра 14 и выход сумматора 18, а второй вход проверочного блока 9 является входом разностного регистра 17; выход комбинационного сумматора 3 связан с входом регистра 2, а первый, второй и третий выходы блока декодирования N связаны соответственно с входами регистров 10, 11 и 12, причем вход блока разделения символов 1 является входом всего устройства, выходом которого является выход регистра 10.

Сначала рассмотрим работу блока декодирования, а затем работу всего устройства. При этом считаем, что элементы регистров могут принимать значения 0 и 1.

Блок декодирования работает следующим образом.

На вход информационного регистра 6, первый и второй входы проверочного блока 9 блока декодирования поступают скорректированные элементы информационного, синдромного и разностного регистров предыдущего блока декодирования (элементы регистров 2, 4 и 5, если это первый блок декодирования) соответственно. Декодируемый символ с выхода информационного регистра 6 поступает в элемент задержки 7. Решающее устройство 15 проверочного блока 9 суммирует элементы синдромного регистра 14, соответствующие образующему полиному, и выходной элемент разностного регистра 17. Если полученная сумма больше некоторого порога Т, то с помощью синдромного коммутатора 13 осуществляется инверсия элементов синдромного регистра 14, соответствующих образующему полиному, с помощью сумматора 18 проверочного блока 9 осуществляется инверсия выходного элемента разностного регистра 17 и с помощью сумматора 8 блока декодирования инвертируется декодируемый символ. Иначе все остается без изменений. На следующий блок декодирования передаются скорректированные элементы информационного, синдромного и разностного регистров.

Устройство работает следующим образом.

1. Символ поступает на вход блока разделения символов 1, который выделяет из него информационную и проверочную части. Информационная часть поступает в регистр 2, а проверочная - в комбинационный сумматор 3, где в соответствии с образующим полиномом и содержимым регистра 2 вычисляется элемент синдрома, который поступает в регистр 4. В регистр 5 записывается ноль.

2. Выполняют шаг работы все N блоков декодирования. Выходы последнего блока декодирования поступают в регистры 10, 11 и 12. При этом содержимое всех регистров сдвигается на один элемент вправо.

3. П.2 повторяется К раз, где К - размер регистров. При этом выходы N-го блока декодирования накапливаются в регистрах 10, 11 и 12.

4. В качестве выхода устройства берется выход регистра 10. После этого содержимое всех регистров сдвигается на К-1 элемент влево.

5. Шаги 1-4 повторяются до тех пор, пока не обработаны все входные символы.

Положительный эффект, а именно значительное уменьшение задержки декодирования, а значит, и повышение оперативности обработки данных достигается за счет декодирования символа в каждом блоке декодирования К раз. Результаты моделирования показывают, что применение данного метода позволяет сократить число N блоков декодирования, а соответственно и уменьшить задержку декодирования в несколько раз.

ЛИТЕРАТУРА

1. Золотарев В. В. , Минина Н.Г. Устройство для декодирования линейных сверточных кодов. - Авторское свидетельство СССР 1291984.

2. RU 2035123, кл. Н 03 М 13/00, 1992 (прототип).

3. С.И. Самойленко и др. Вычислительные сети. М.: Наука, 1981.

Изобретение относится к системам связи и может использоваться в системах передачи данных для исправления ошибок. Технический результат заключается в уменьшении задержки декодирования. В устройство, содержащее блок разделения символов, регистр, комбинационный сумматор и множество блоков декодирования, введены шесть регистров. 2 ил.

Устройство для декодирования линейных кодов, включающее блок разделения символов, поразрядно связанные регистр и комбинационный сумматор, N последовательно соединенных блоков декодирования, причем первый, второй и третий выходы каждого блока декодирования связаны соответственно с первым, вторым и третьим входами следующего блока декодирования, первый и второй выходы блока разделения символов связаны соответственно с входами регистра и комбинационного сумматора, а выход регистра связан с первым входом первого блока декодирования, причем первый блок декодирования состоит из проверочного блока, сумматора и элемента задержки, выход которого связан с первым входом сумматора, второй вход которого связан с первым выходом проверочного блока, причем вторым и третьим входами блока декодирования являются соответственно первый и второй входы проверочного блока, а первым, вторым и третьим выходами - выход сумматора, второй и третий выходы проверочного блока, а остальные блоки декодирования состоят из проверочного блока, регистра, последовательно связанного через элемент задержки с первым входом сумматора, второй вход которого связан с первым выходом проверочного блока, причем первым, вторым и третьим входами блока декодирования являются соответственно вход регистра, первый и второй входы проверочного блока, а первым, вторым и третьим выходами - выход сумматора, второй и третий выходы проверочного блока, который состоит из последовательно и поразрядно связанных между собой первого коммутатора, первого регистра, решающего устройства и второго коммутатора, второго регистра, выход которого связан с первым входом сумматора и входом решающего устройства, выход которого связан с входом первого коммутатора, вторым входом сумматора и является первым выходом проверочного блока, вторым и третьим выходами которого являются соответственно выход первого регистра и выход сумматора, а второй вход проверочного блока является входом второго регистра; вход блока разделения символов является входом всего устройства, отличающееся тем, что дополнительно введены шесть регистров, причем первым входом проверочного блока является вход первого регистра, вход первого добавленного регистра является первым входом первого блока декодирования, а выход связан с входом элемента задержки первого блока декодирования, выход комбинационного сумматора через второй добавленный регистр связан со вторым входом первого блока декодирования, выход третьего добавленного регистра связан с третьим входом первого блока декодирования, а первый, второй и третий выходы N-го блока декодирования связаны соответственно с входами четвертого, пятого и шестого добавленных регистров, причем выход четвертого добавленного регистра является выходом устройства.

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ЛИНЕЙНЫХ КОДОВ | 1992 |

|

RU2035123C1 |

| SU 1291984 A1, 23.02.1987 | |||

| ПРИЕМНИК С НАСТРАИВАЕМЫМ УРОВНЕВЫМ ДЕМОДУЛЯТОРОМ СИМВОЛОВ | 1995 |

|

RU2151467C1 |

| US 5077538 А, 12.01.1992 | |||

| Приспособление в пере для письма с целью увеличения на нем запаса чернил и уменьшения скорости их высыхания | 1917 |

|

SU96A1 |

Авторы

Даты

2003-09-20—Публикация

2002-01-28—Подача