Предлагаемое изобретение относится к области вычислительной техники и может быть использовано в процессорах, где предусмотрена аппаратная реализация преобразований из одной системы счисления в другую.

Известны устройства преобразования из десятичного двоично-кодированного представления (BCD-код) в двоичный код, основанные на последовательном делении десятичного числа на 2. Цифры двоичного кода формируются, начиная с младшей, как остатки от этого деления.

Устройство преобразования содержит регистры десятичного и двоичного чисел с общей цепью сдвига вправо на 1 бит и схему коррекции, вход которой соединен с выходом десятичного регистра, а выход подключен к входу этого регистра, а также счетчик тактов по числу разрядов двоичного числа. Преобразование происходит по схеме “сдвиг-коррекция”: на каждом шаге преобразования осуществляется сдвиг регистров вправо, а затем коррекция кода в регистре десятичного числа с целью получения корректного значения частного от деления на 2.

Недостатком описанного устройства является низкая производительность, так как преобразование выполняется за n тактов сдвига и коррекции, где n - разрядность двоичного кода [1, 2].

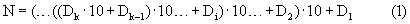

Другой способ преобразования десятичного числа N=DkDk-1...Di...D2D1, где k - число десятичных разрядов, Di - i-я десятичная цифра, состоит в использовании рекуррентной формулы

При выполнении по формуле (1) в двоичной системе получаем двоичное значение N. При этом умножение двоичного числа на 10 заменяется сложением числа, сдвинутого на 3 бита влево (умножение на 8) с этим же числом, сдвинутым на 1 бит влево (умножение на 2).

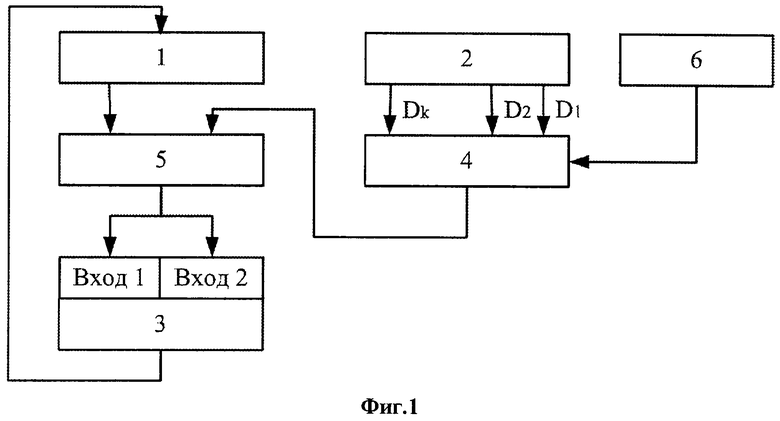

Устройство преобразования (фигура 1) содержит регистры двоичного (1) и десятичного (2) чисел, мультиплексор тетрад десятичного числа (4), первый двоичный сумматор (3), второй двоичный сумматор (5) и счетчик тактов (6) по числу десятичных разрядов k.

Выход регистра двоичного числа соединен с входами двоичного сумматора 3, причем к первому входу он подключен со сдвигом на 3 бита влево, а ко второму входу - со сдвигом на 1 бит влево. Выход двоичного сумматора 3 подключен к первому входу двоичного сумматора 5, ко второму входу которого подключены выходы тетрад десятичного регистра 2 через мультиплексор тетрад десятичного числа 4, управляющий вход которого подключен к выходу счетчика тактов 6, а выход второго двоичного сумматора 5 соединен с входом двоичного регистра 1.

В каждом цикле преобразования выполняются следующие действия:

1) на входы первого двоичного сумматора (3) поступает код из двоичного регистра со сдвигом влево на 3 и 1 бит соответственно (умножение на 10), результат поступает на первый вход второго двоичного сумматора (5);

2) на второй вход второго двоичного сумматора (5) подается код очередной тетрады из десятичного регистра, начиная со старшей, результат поступает в двоичный регистр (1).

Процедура повторяется k раз, где k - разрядность десятичного регистра.

Описанное устройство является прототипом предлагаемого технического решения.

Недостатком устройства является неполное использование возможностей схемы с двумя двоичными сумматорами, полное использование которых позволило бы удвоить быстродействие устройства.

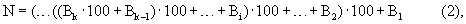

В предлагаемом техническом решении на каждом шаге обрабатывается две тетрады десятичного числа. Преобразование происходит в соответствии с выражением

где Bi - i-й байт (пара тетрад) десятичного числа. Умножение на 100 в соответствии с выражением 100=27+22-25 выполняется сложением двоичного числа, сдвинутого на 7 и 2 битов влево, и вычитанием этого же числа, сдвинутого на 5 битов влево. В состав устройства вводятся двоичное вычитающее устройство и преобразователь кода. На вход преобразователя кода подается старшая тетрада очередного байта десятичного числа, выходы преобразователя кода и младшей тетрады очередного байта десятичного числа соединены со свободными входами двоичного сумматора и двоичного вычитающего устройства.

В основе предлагаемого технического решения лежит то обстоятельство, что при передаче на входы двоичного сумматора и двоичного вычитающего устройства сдвинутых кодов остаются свободными входы семи младших разрядов первого входа двоичного сумматора, два младших разряда его второго входа и пять младших разрядов второго входа двоичного вычитающего устройства. Это позволяет совместить в одном такте умножение числа на 100 и прибавление очередного байта десятичного числа.

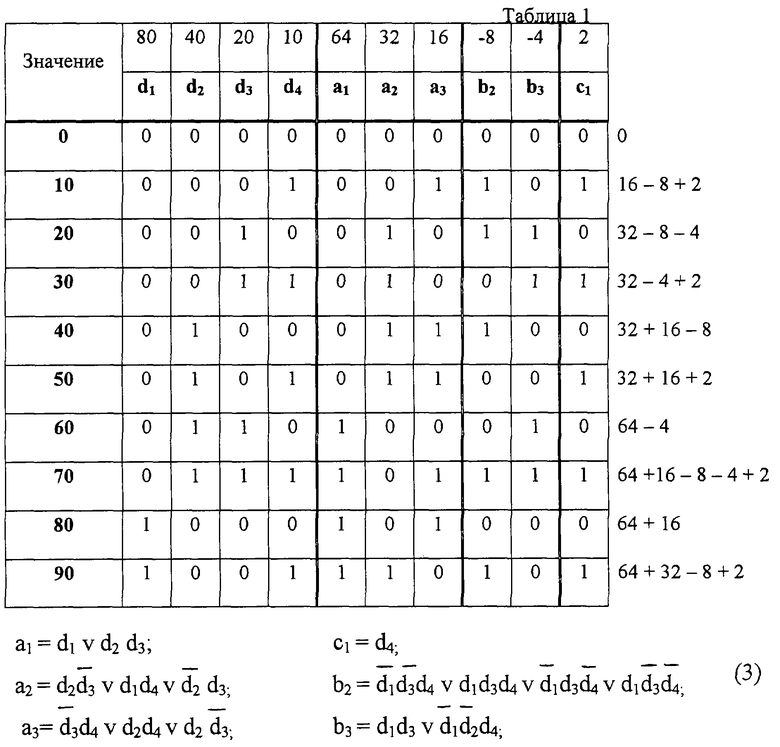

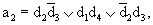

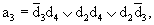

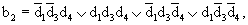

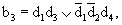

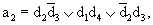

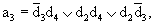

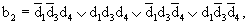

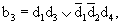

Работа преобразователя кода описывается таблицей 1 и системой логических выражений (3), где d1, d2, d3, d4 - биты старшей тетрады байта десятичного числа; a1, a2, а3, a4, а5, a6, a7 - младшие (свободные) биты первого входа двоичного сумматора; c1, c2 - младшие (свободные) биты второго входа двоичного сумматора; b1, b2, b3, b4, b5 - младшие (свободные) биты второго входа двоичного вычитающего устройства. Цифры над обозначениями этих переменных в таблице соответствуют их весовым значениям.

.

.

Преобразователь кода, осуществляющий следующие преобразования:

c1=d4,

где d1, d2, d3, d4 - биты старшей тетрады байта десятичного числа; а1, а2, а3 - младшие биты первого входа двоичного сумматора; c1, c2 - младшие биты второго входа двоичного сумматора; b2, b3 - младшие биты второго входа двоичного вычитающего устройства, есть комбинационная схема - дешифратор.

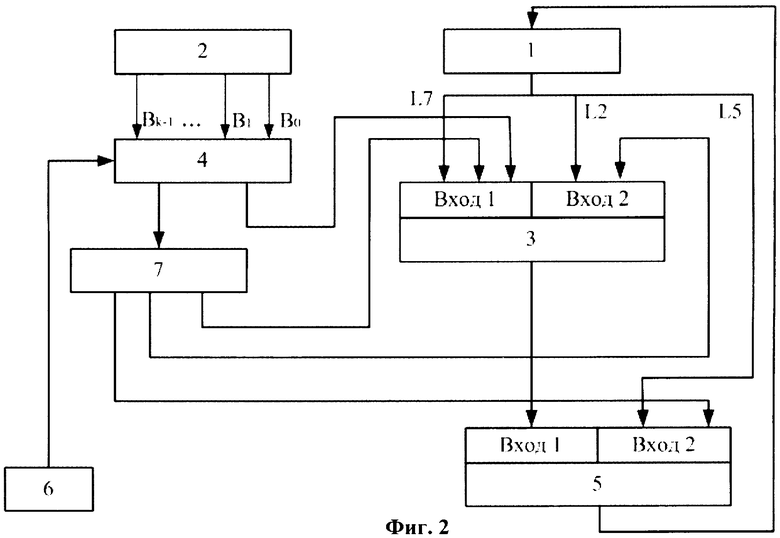

Схема предлагаемого устройства приведена на фигуре 2, где 1 - регистр двоичного числа, 2 - регистр десятичного числа, 3 - двоичный сумматор, 4 - мультиплексор байт, 5 - двоичное вычитающее устройство, 6 - счетчик тактов, 7 - преобразователь кода.

Выход регистра двоичного числа (1) подключен к первому входу двоичного сумматора (3), причем выход разряда i регистра двоичного числа (1) соединен с входом разряда i+7 первого входа двоичного сумматора (3) соответственно, и ко второму входу двоичного сумматора (3), причем выход разряда i регистра двоичного числа (1) соединен с входом разряда i+2 второго входа двоичного сумматора (3) и ко второму входу двоичного вычитающего устройства (5), причем выход разряда i регистра двоичного числа (1) соединен с входом разряда i+5 второго входа двоичного вычитающего устройства (5) (i=1, 2,... n; n - разрядность регистра двоичного числа (1), двоичного сумматора (3) и двоичного вычитающего устройства (5). Значение n зависит и равно разрядности исходного двоично-десятичного кода, который записывается в регистр десятичного числа (2)). Выход двоичного сумматора (3) соединен с первым входом двоичного вычитающего устройства (5). Выходы байтов Bk, Bk-1,... B2, B1 десятичного регистра (2) через мультиплексор байт (4) подключены соответственно старшая тетрада ко входу преобразователя кода (7), а младшая тетрада к младшим разрядам первого входа двоичного сумматора (3), причем управляющий вход мультиплексора байт (4) подключен к выходу счетчика тактов (6), одна группа выходов преобразователя кода (7) (а1a2а3) соединена с 5, 6 и 7 разрядами первого входа двоичного сумматора (3), вторая группа (c1) - со вторым разрядом второго входа двоичного сумматора (3) и третья (b2b3) соответственно с 4 и 5 разрядами второго входа двоичного вычитающего устройства (5). Выход двоичного вычитающего устройства (5) соединен с входом регистра двоичного числа (1).

Устройство работает следующим образом. Вначале в регистр десятичного числа (2) загружается преобразуемый десятичный код, регистр двоичного числа (1) сбрасывается, а в счетчик тактов (6) заносится число пар десятичных разрядов k. Затем выполняется k тактов преобразования. В каждом из них выполняются следующие действия:

1) осуществляется выбор байта из регистра десятичного числа (2) мультиплексором байтов (4) под управлением счетчика тактов (6), начиная с Bk;

2) старшая тетрада выбранного байта поступает на вход преобразователя кода (7), на выходе которого получаем коды а1a2а3, c1 и b2b3;

3) на первый и второй входы двоичного сумматора (3) подаются сдвинутое на 7 и 2 бит соответственно содержимое регистра двоичного числа (1), на младшие разряды с 1 по 4 первого входа двоичного сумматора (3) подается младшая тетрада очередного десятичного байта, на разряды с 5 по 7 первого входа двоичного сумматора (3) подается с преобразователя кода преобразованный код а1a2а3, на младший второй разряд второго входа двоичного сумматора (3) подается с преобразователя кода (7) преобразованный код c1;

4) результат суммирования передается на первый вход двоичного вычитающего устройства (5), а на второй вход двоичного вычитающего устройства (5) подается сдвинутое на 5 бит содержимое регистра двоичного числа (1), а на младшие разряды с 3 по 4 второго входа двоичного вычитающего устройства (5) подается с преобразователя кода (7) преобразованный код b2b3;

5) результат выполнения вычитания записывается в регистр двоичного числа (1).

Операция заканчивается при обнулении счетчика.

Положительный эффект предлагаемого технического решения состоит в сокращении времени преобразования по сравнению с аналогом в 2 раза.

Литература

1. Карцев М.А. Арифметика цифровых машин. М.: Наука, 1969 г. п.1.2.4, п.5.2.2.

2. Злобин В.К., Григорьев В.Л. Программирование арифметических операций в микропроцессорах: Учебное пособие для технических вузов. - М: Высш. шк., 1991. Стр. 134, 141, 127.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления десятичных чисел | 1982 |

|

SU1048473A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1182514A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1501276A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

Устройство относится к области вычислительной техники и может быть использовано в процессорах, где предусмотрена аппаратная реализация преобразований из одной системы счисления в другую. Техническим результатом является сокращение в 2 раза времени преобразования. Указанный результат достигается за счет введения в устройство, содержащее регистры десятичного и двоичного числа, двоичный сумматор и счетчик тактов, двоичного вычитающего устройства, преобразователя кода и мультиплексора байтов. 2 ил., 1 табл.

Устройство преобразования из десятичной системы счисления в двоичную, содержащее регистр десятичного числа, регистр двоичного числа, двоичный сумматор и счетчик тактов, отличающееся тем, что в устройство дополнительно введены двоичное вычитающее устройство, преобразователь кода и мультиплексор байтов, управляющий вход которого подключен к выходу счетчика тактов, а информационные входы соединены с выходами соответствующих байтов регистра десятичного числа, один выход мультиплексора байтов подключен ко входу преобразователя кода, преобразователь кода осуществляет следующие преобразования а1=d1 ∨ d2·d3,

c1=d4,

c1=d4,

где d1, d2, d3, d4 - биты старшей тетрады байта десятичного числа, a1, а2, а3 - младшие биты первого входа двоичного сумматора, c1, c2 - младшие биты второго входа двоичного сумматора, b2, b3 - младшие биты второго входа двоичного вычитающего устройства, а другой - к первому входу двоичного сумматора, одна группа выходов преобразователя кода соединена с первым входом двоичного сумматора, вторая - со вторым входом двоичного сумматора и третья группа - со вторым входом вычитающего устройства, выход регистра выход разряда i регистра двоичного числа соединен с разрядом i+7 первого входа двоичного сумматора, со вторым входом двоичного сумматора, причем выход разряда i регистра двоичного числа соединен с разрядом i+2 второго входа двоичного сумматора и со вторым входом двоичного вычитающего устройства, причем выход разряда i регистра двоичного числа соединен с разрядом i+5 второго входа двоичного вычитающего устройства, где i=1... n, n - разрядность регистра двоичного числа, двоичного сумматора и двоичного вычитающего устройства, выход двоичного сумматора подключен к первому входу двоичного вычитающего устройства, выход которого подключен ко входу двоичного числа.

где d1, d2, d3, d4 - биты старшей тетрады байта десятичного числа, a1, а2, а3 - младшие биты первого входа двоичного сумматора, c1, c2 - младшие биты второго входа двоичного сумматора, b2, b3 - младшие биты второго входа двоичного вычитающего устройства, а другой - к первому входу двоичного сумматора, одна группа выходов преобразователя кода соединена с первым входом двоичного сумматора, вторая - со вторым входом двоичного сумматора и третья группа - со вторым входом вычитающего устройства, выход регистра выход разряда i регистра двоичного числа соединен с разрядом i+7 первого входа двоичного сумматора, со вторым входом двоичного сумматора, причем выход разряда i регистра двоичного числа соединен с разрядом i+2 второго входа двоичного сумматора и со вторым входом двоичного вычитающего устройства, причем выход разряда i регистра двоичного числа соединен с разрядом i+5 второго входа двоичного вычитающего устройства, где i=1... n, n - разрядность регистра двоичного числа, двоичного сумматора и двоичного вычитающего устройства, выход двоичного сумматора подключен к первому входу двоичного вычитающего устройства, выход которого подключен ко входу двоичного числа.

| ЗЛОБИН В.К | |||

| и др | |||

| Программирование арифметических операций в микропроцессорах: Учебное пособие для технических вузов, М.: Высшая школа, 1991, с.127, 131, 141 | |||

| Устройство для преобразования двоично-десятичного кода в двоичный код и обратно | 1990 |

|

SU1755375A1 |

| Силовой цилиндр возвратно-поступательного и вращательного действия | 1982 |

|

SU1138559A1 |

| ЕР 1231716 А2, 14.08.2002 | |||

| JP 7160478 А, 23.06.1995 | |||

| JP 8139608 А, 14.08.2002. | |||

Авторы

Даты

2005-03-10—Публикация

2003-04-04—Подача