Настоящее изобретение относится к вычислительной технике, в частности к вычислительным устройствам, в которых для обработки информации (особенно для применения в цифровых вычислительных системах, обладающих высоким быстродействием) используют управление потоком данных.

ПРЕДПОСЫЛКИ ДЛЯ СОЗДАНИЯ НАСТОЯЩЕГО ИЗОБРЕТЕНИЯ

Устройство для обработки информации, в котором для обработки информации используют поток данных, описано в патенте США 4675806, выданном Учида. Учида описывает систему, в которой выполнение команд осуществляют на основе доступности данных и в которых разделяют поток данных и команды, но данные передают в соответствии с предписаниями и требованиями команд. Такое устройство имеет относительно низкий уровень быстродействия, который является общим для других вычислительных устройств, в которых при вычислении используют управление потоком данных и прямую адресацию к оперативной памяти в качестве аппаратного средства для хранения данных. Пониженное быстродействие имеет место вследствие сложной организации аппаратного обеспечения управляющих средств и затрат времени в процессе динамического распределения памяти.

Другое известное устройство для обработки данных, описанное в патенте Российской Федерации 2029359, в котором поток данных используют для управления процессом вычисления, содержит центральный процессор, переключатель ввода-вывода, переключатель загрузки команд, память для хранения команд, блок доступа к данным, а также первый и второй информационные выходы. В этом устройстве первый управляющий выход центрального процессора соединен с первым управляющим входом переключателя ввода-вывода, первый управляющий вход которого соединен с первым управляющим входом блока доступа к данным, первый информационный вход которого соединен с информационным выходом переключателя загрузки команд, первый управляющий вход которого соединен со вторым управляющим выходом центрального процессора, первый и второй информационные выходы которого соединены, соответственно, с первым информационным входом переключателя загрузки команд и первым информационным входом переключателя ввода-вывода, третий информационный выход процессора соединен с первым информационным выходом компьютера, обнуляющий вход блока доступа к данным соединен с обнуляющим выходом компьютера, а информационный вход памяти для хранения команд и информационный вход переключателя загрузки команд соединены с первым информационным входом компьютера.

В этом устройстве для управления процессом вычисления используют поток данных, а для хранения данных и результатов вычислений - аппаратное обеспечение ассоциативной памяти (блока доступа к данным). Ассоциативная память одновременно выполняет функцию аппаратного обеспечения управляющих средств. В соответствии с этим увеличивается быстродействие, поскольку нет потерь времени на процессы распределения памяти.

Однако в этом устройстве быстродействие устройства непосредственно зависит от ассоциативной памяти (в блоке доступа к данным) и ограничено скоростью вывода данных из ассоциативной памяти (число операндов, готовых для выполнения в единицу времени N=1/Таm, где Таm = время работы ассоциативной памяти с момента запроса вывода данных).

Значение величины Tam непосредственно зависит от объема ассоциативной памяти. Поскольку значение Таm, определяемое из времени запроса из рабочей программы, увеличивается по мере увеличения размера ассоциативной памяти, быстродействие устройства уменьшается по мере увеличения размера ассоциативной памяти.

Таким образом, при обработке больших объемов рабочих программ такое устройство не может иметь высокого уровня быстродействия.

КРАТКОЕ ИЗЛОЖЕНИЕ СУЩНОСТИ НАСТОЯЩЕГО ИЗОБРЕТЕНИЯ

Задачей настоящего изобретения является увеличение быстродействия путем уменьшения объема ассоциативной памяти при введении в то же самое время локальной обработки данных, соответствующей принципам вычисления фон Неймана, без ухудшения общей идеи управления потоком данных вычисления.

Задачей настоящего изобретения является улучшение быстродействия путем введения в систему обработки потока данных процессора программы фрагмента, благодаря чему программы фрагмента, которые являются программами, которые лучше пригодны для выполнения с помощью принципов вычисления фон Неймана, направляются на выполнение в процессор программы фрагмента.

Эту задачу решают в компьютере, содержащем центральный процессор, переключатель ввода-вывода, переключатель загрузки команд, память для хранения команд, блок доступа к данным, первый и второй информационные выходы, обнуляющий вход и первый и второй информационные входы. Первый управляющий выход центрального процессора соединен с первым управляющим входом переключателя ввода-вывода. Первый управляющий выход переключателя ввода-вывода соединен с первым управляющим входом блока доступа к данным. Первый информационный вход блока доступа к данным соединен с информационным выходом переключателя ввода-вывода. Адресный вход памяти для хранения команд соединен с информационным выходом переключателя загрузки команд. Первый управляющий вход переключателя загрузки команд соединен со вторым управляющим выходом центрального процессора. Первый и второй информационные выходы центрального процессора соединены с первым информационным входом переключателя загрузки команд и с первым информационным входом переключателя ввода-вывода соответственно. Третий информационный выход центрального процессора соединен с первым информационным выходом компьютера. Обнуляющий вход блока доступа к данным соединен с обнуляющим входом компьютера. Информационный вход памяти для хранения команд и второй информационный вход переключателя загрузки команд соединены с первым информационным входом компьютера. Вводят процессор программы фрагмента. Первый управляющий выход процессора программы фрагмента соединен со вторым управляющим входом блока доступа к данным. Первый управляющий выход блока доступа к данным соединен со вторым управляющим входом переключателя ввода-вывода. Второй управляющий выход переключателя ввода-вывода соединен с первым управляющим входом центрального процессора и с первым управляющим входом процессора программы фрагмента. Второй управляющий выход процессора программы фрагмента соединен с третьим управляющим входом переключателя ввода-вывода. Второй информационный вход переключателя ввода-вывода соединен с информационным выходом процессора программы фрагмента. Второй управляющий выход блока доступа к данным соединен со вторым управляющим входом центрального процессора. Первый информационный вход центрального процессора соединен с информационным выходом памяти для хранения команд. Управляющий вход памяти для хранения команд соединен с управляющим выходом переключателя загрузки команд. Второй управляющий вход переключателя загрузки команд и первый информационный вход процессора программы фрагмента соединены с первым информационным входом компьютера. Управляющий выход памяти для хранения команд соединен с третьим управляющим входом центрального процессора. Третий управляющий выход центрального процессора соединен с третьим управляющим входом блока доступа к данным. Второй информационный вход блока доступа к данным соединен со вторым информационным входом компьютера. Обнуляющий вход компьютера соединен со вторым управляющим входом процессора программы фрагмента, с четвертым управляющим входом блока доступа к данным, с четвертым управляющим входом переключателя ввода-вывода и с четвертым управляющим входом центрального процессора. Четвертый управляющий выход центрального процессора соединен с пятым управляющим входом блока доступа к данным. Третий информационный вход блока доступа к данным соединен со вторым информационным выходом центрального процессора. Пятый управляющий вход центрального процессора соединен с третьим управляющим выходом блока доступа к данным. Первый информационный выход блока доступа к данным соединен со вторым информационным входом центрального процессора. Второй информационный выход блока доступа к данным соединен со вторым информационным выходом компьютера. Третий управляющий вход процессора программы фрагмента соединен с четвертым управляющим выходом блока доступа к данным. Третий информационный выход блока доступа к данным соединен со вторым информационным входом процессора программы фрагмента. Кроме того, процессор программы фрагмента содержит исполнительный блок, блок выходного регистра, блок регистра загрузки и блок входного регистра. Информационный выход исполнительного блока соединен с информационным входом блока выходного регистра. Первый управляющий вход блока выходного регистра соединен с первым управляющим входом процессора программы фрагмента. Второй управляющий вход процессора программы фрагмента соединен с первым управляющим входом исполнительного блока, со вторым управляющим входом блока выходного регистра, с первым управляющим входом блока регистра загрузки и с первым управляющим входом блока входного регистра. Первый управляющий выход блока входного регистра соединен с первым управляющим выходом процессора программы фрагмента. Первый информационный вход процессора программы фрагмента соединен с информационным входом блока регистра загрузки. Информационный выход блока регистра загрузки и информационный выход блока входного регистра соединены с информационным входом исполнительного блока. Второй управляющий вход исполнительного блока соединен с первым управляющим выходом блока выходного регистра, с первым управляющим выходом блока регистра загрузки и со вторым управляющим выходом блока входного регистра. Третий управляющий выход блока входного регистра и второй управляющий выход блока выходного регистра соединены с третьим управляющим входом исполнительного блока. Первый управляющий выход исполнительного блока соединен со вторым управляющим входом блока регистра загрузки, со вторым управляющим входом блока входного регистра и с третьим управляющим входом блока выходного регистра. Третий управляющий выход блока выходного регистра соединен со вторым управляющим выходом процессора программы фрагмента. Второй информационный вход процессора программы фрагмента соединен с информационным входом блока входного регистра. Третий управляющий вход блока входного регистра, третий управляющий вход блока регистра загрузки и четвертый управляющий вход блока выходного регистра соединены со вторым управляющим выходом исполнительного блока. Третий управляющий выход исполнительного блока соединен с четвертым управляющим входом блока входного регистра, с четвертым управляющим входом блока регистра загрузки и с пятым управляющим входом блока выходного регистра. Информационный выход блока выходного регистра соединен с информационным выходом процессора программы фрагмента. Третий управляющий вход процессора программы фрагмента соединен с пятым управляющим входом блока входного регистра. Шестой управляющий вход блока входного регистра, пятый управляющий вход блока регистра загрузки и шестой управляющий вход блока выходного регистра соединены с четвертым управляющим выходом исполнительного блока. Пятый управляющий выход исполнительного блока соединен с седьмым управляющим входом выходных регистров.

Суть настоящего изобретения в том, что введение процессора программы фрагмента и организация соответствующих соединений обеспечивают повышенное быстродействие компьютера в процессе обработки основных программ посредством увеличения скорости обмена ассоциативной памяти через уменьшение ее рабочего объема.

Для выполнения всей программы используется принцип управления потоком данных вычисления. Обработка фрагментов, имеющая локальный характер вычисления и небольшую параллельность (например, фрагментов в виде тригонометрических или других функций, косвенно связанных с аналогичными фрагментами) выполняется без участия ассоциативной памяти.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

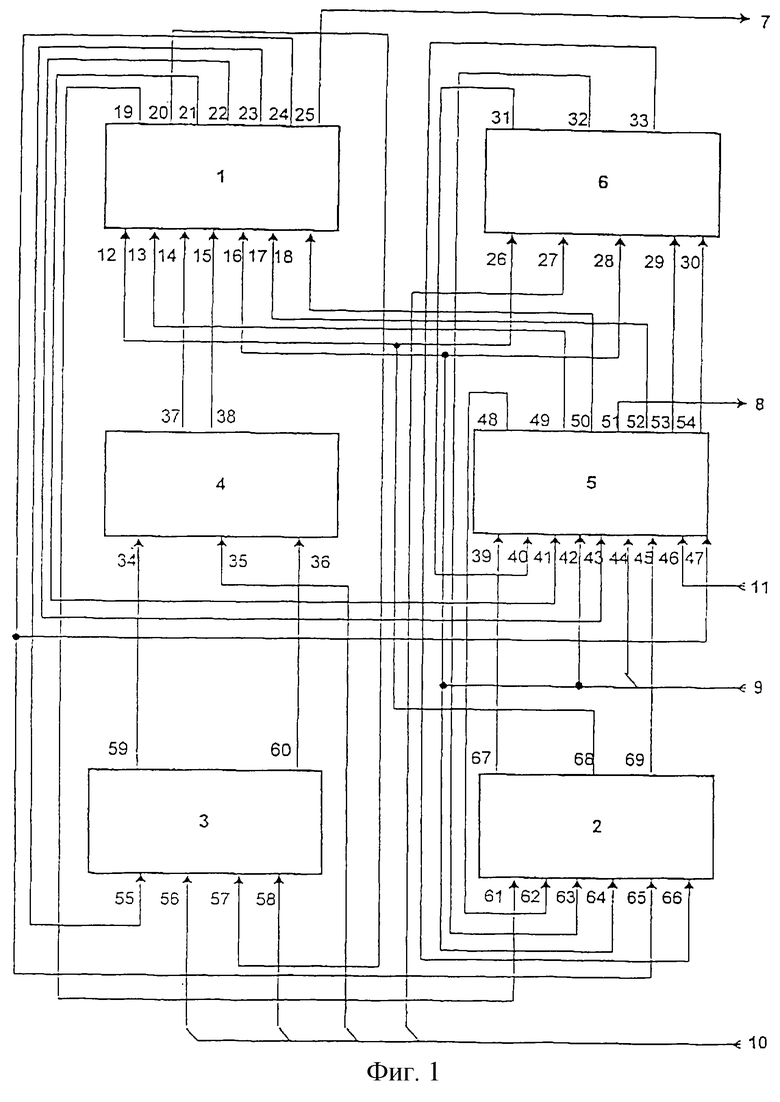

Фиг. 1 - функциональная схема системы, соответствующей настоящему изобретению.

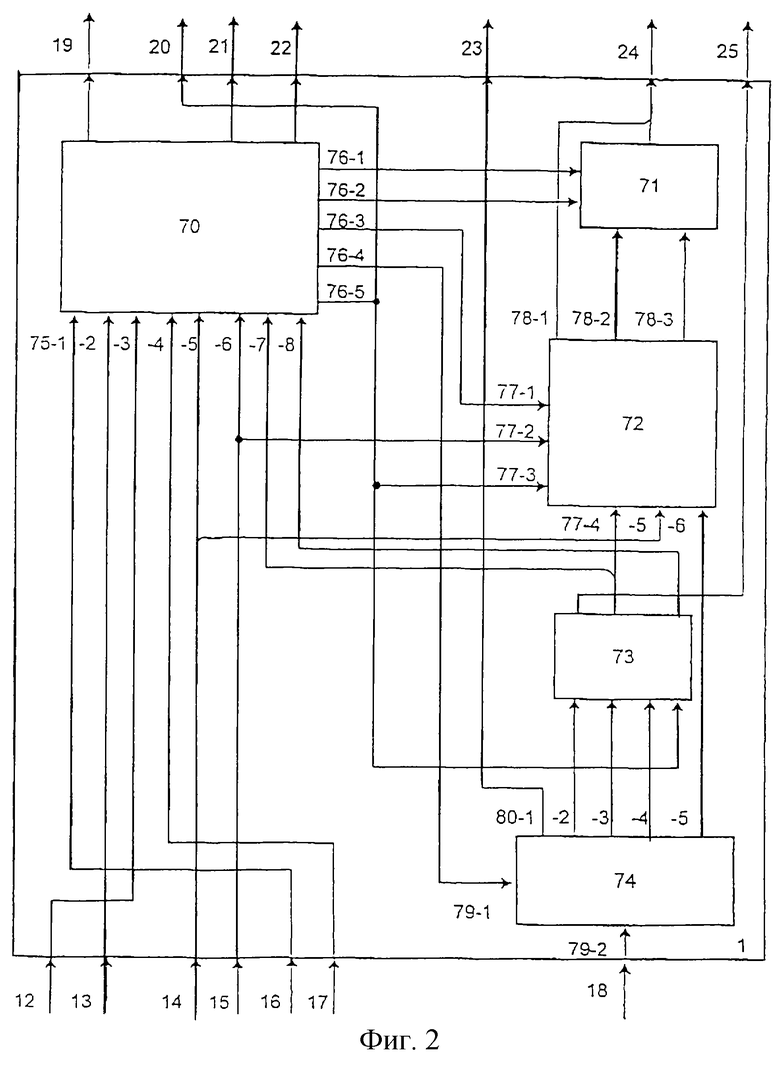

Фиг.2 - функциональная схема центрального процессора.

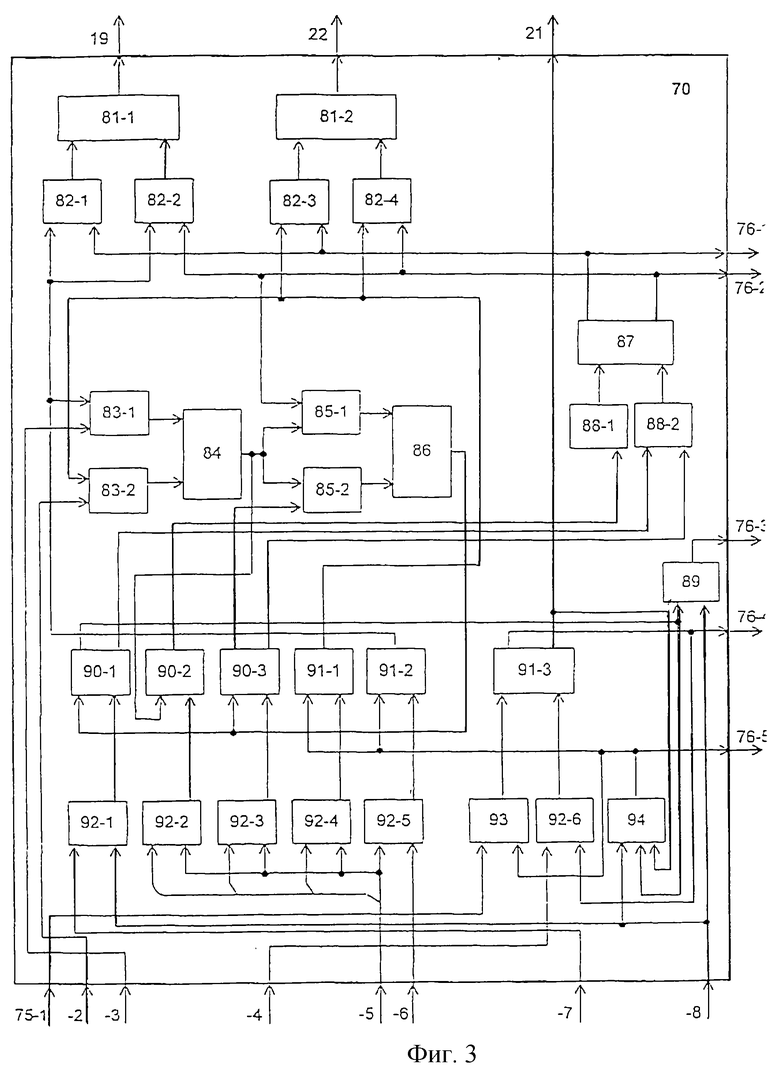

Фиг. 3 - функциональная схема управляющего устройства центрального процессора.

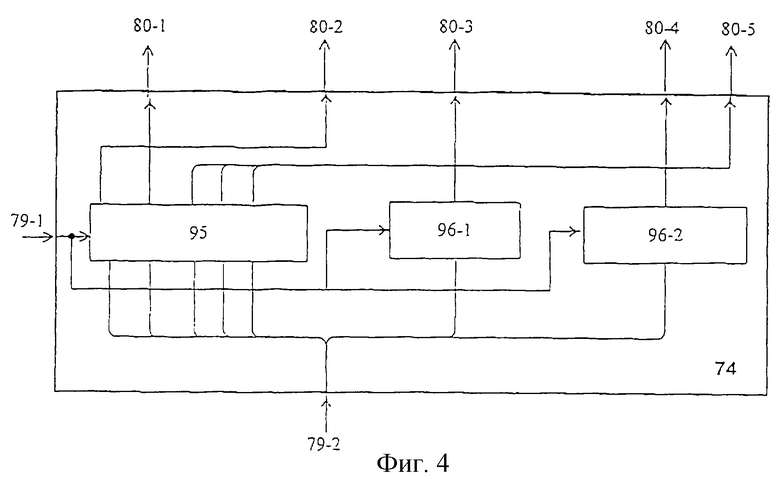

Фиг. 4 - функциональная схема блока входного регистра центрального процессора.

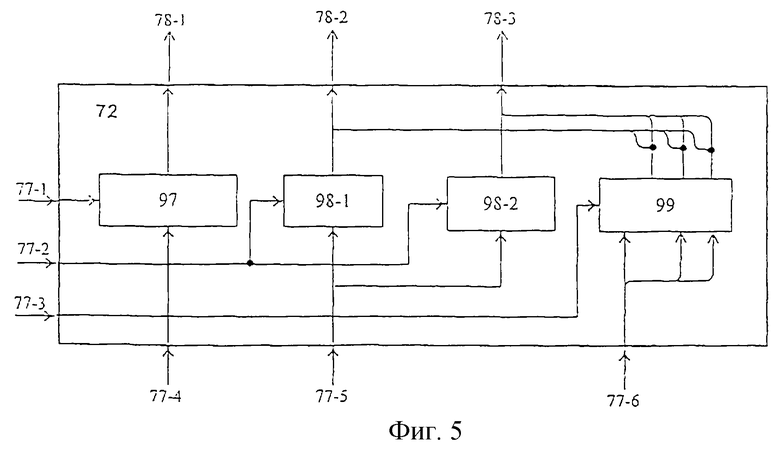

Фиг. 5 - функциональная схема блока выходного регистра центрального процессора.

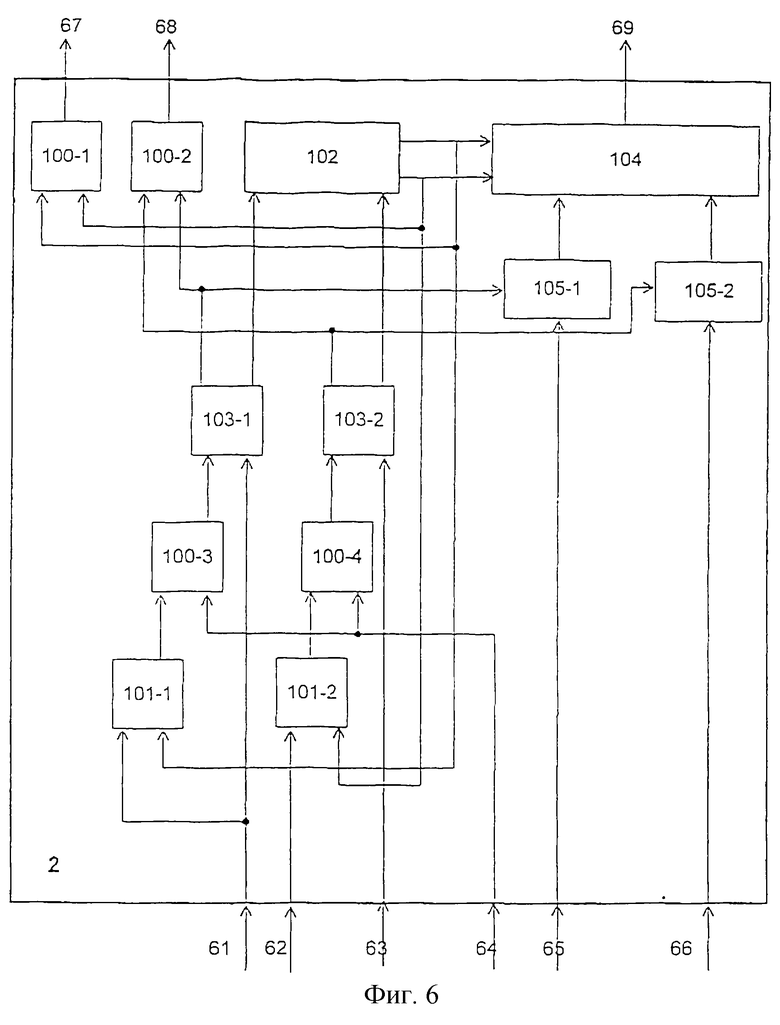

Фиг.6 - функциональная схема переключателя ввода-вывода.

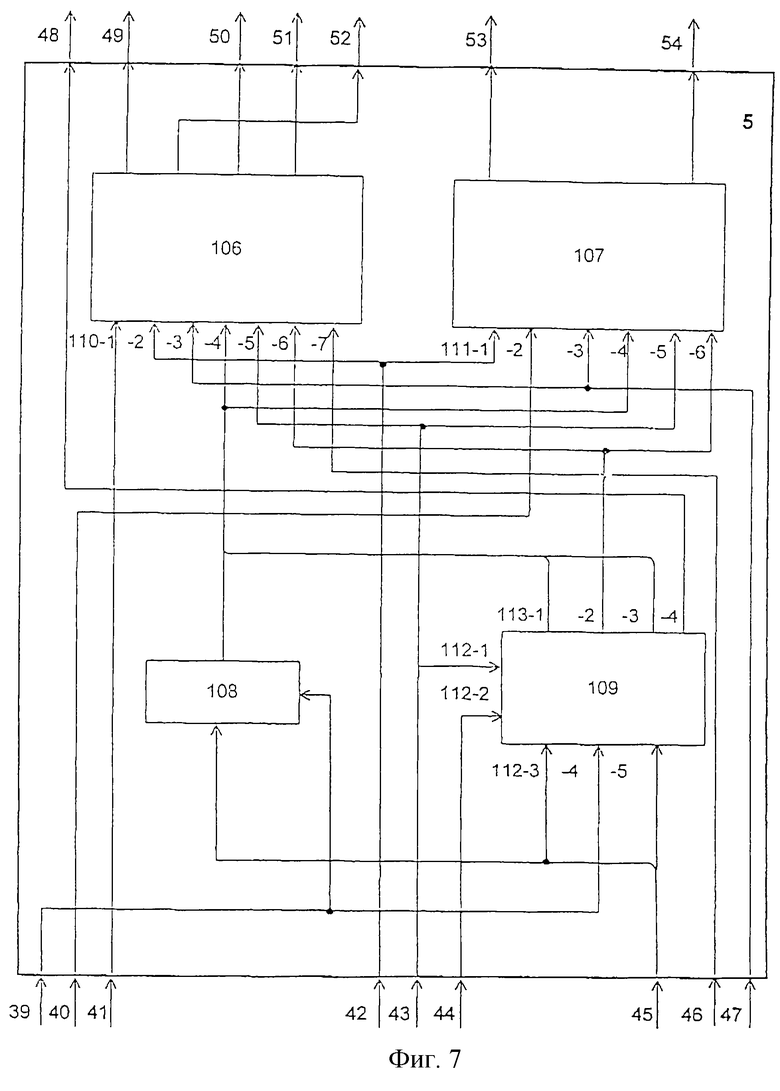

Фиг.7 - функциональная схема блока доступа к данным.

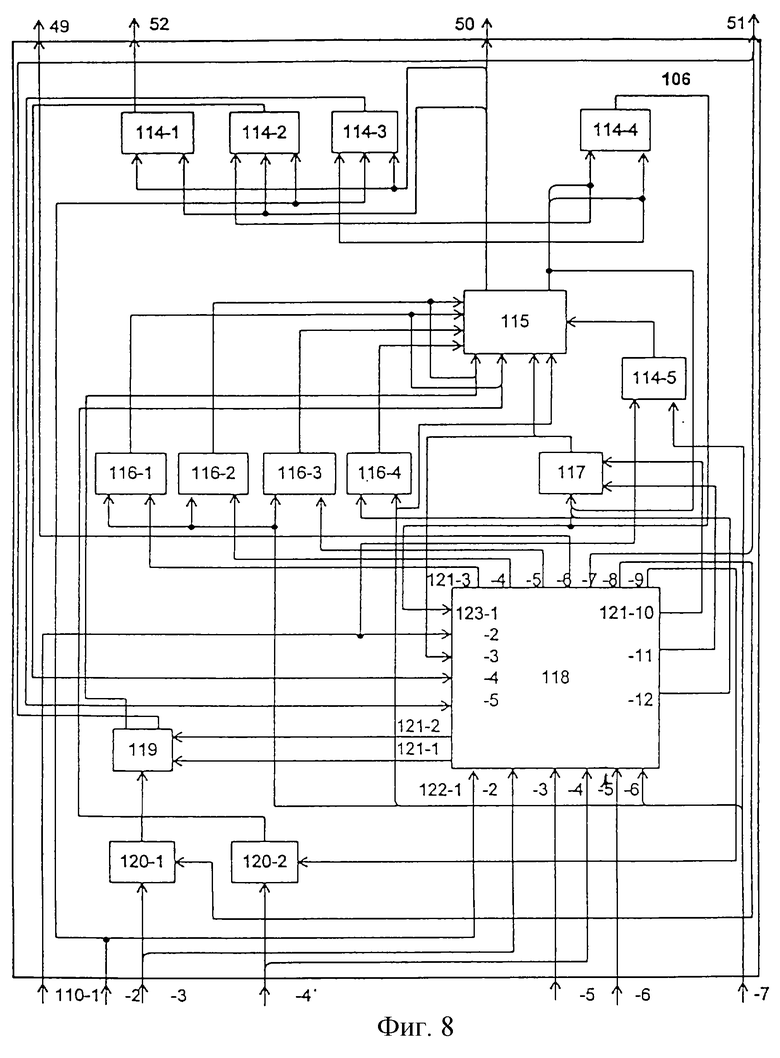

Фиг.8 - функциональная схема буфера блока доступа к данным.

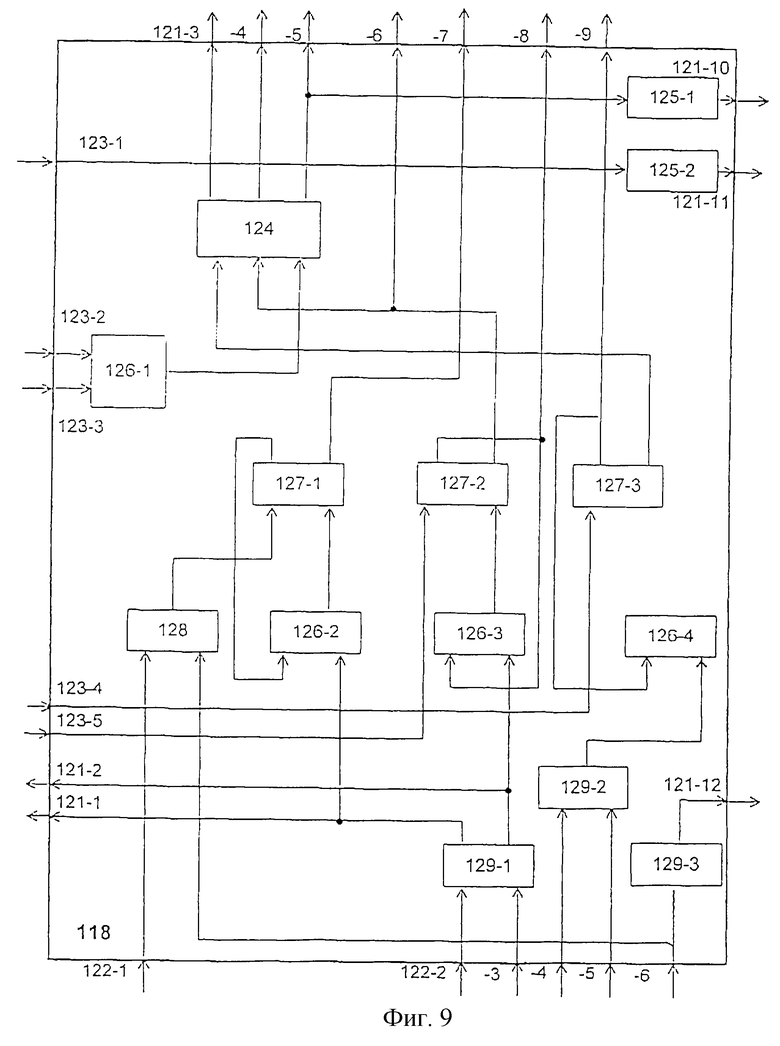

Фиг. 9 - функциональная схема управляющего устройства буфера блока доступа к данным.

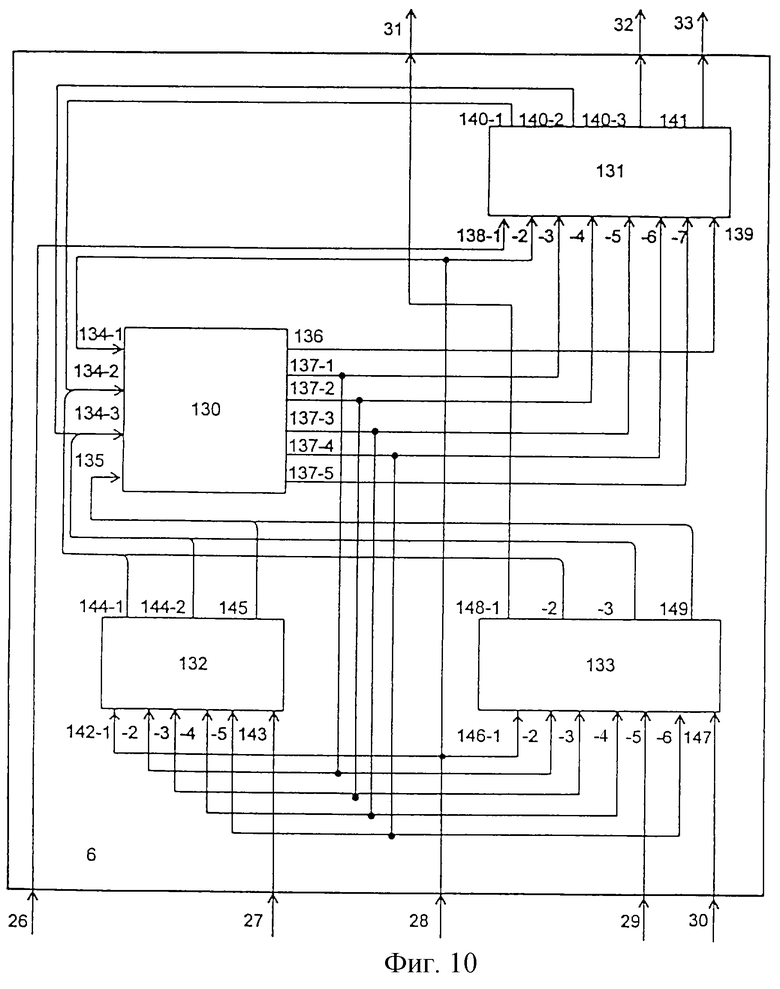

Фиг.10 - функциональная схема процессора программы фрагмента.

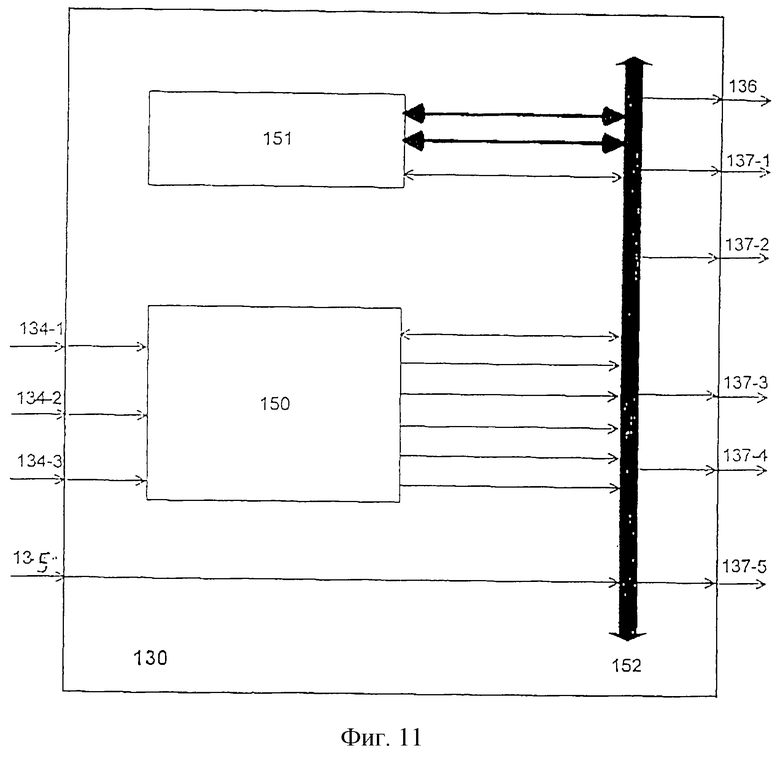

Фиг.11 - функциональная схема исполнительного блока процессора программы фрагмента.

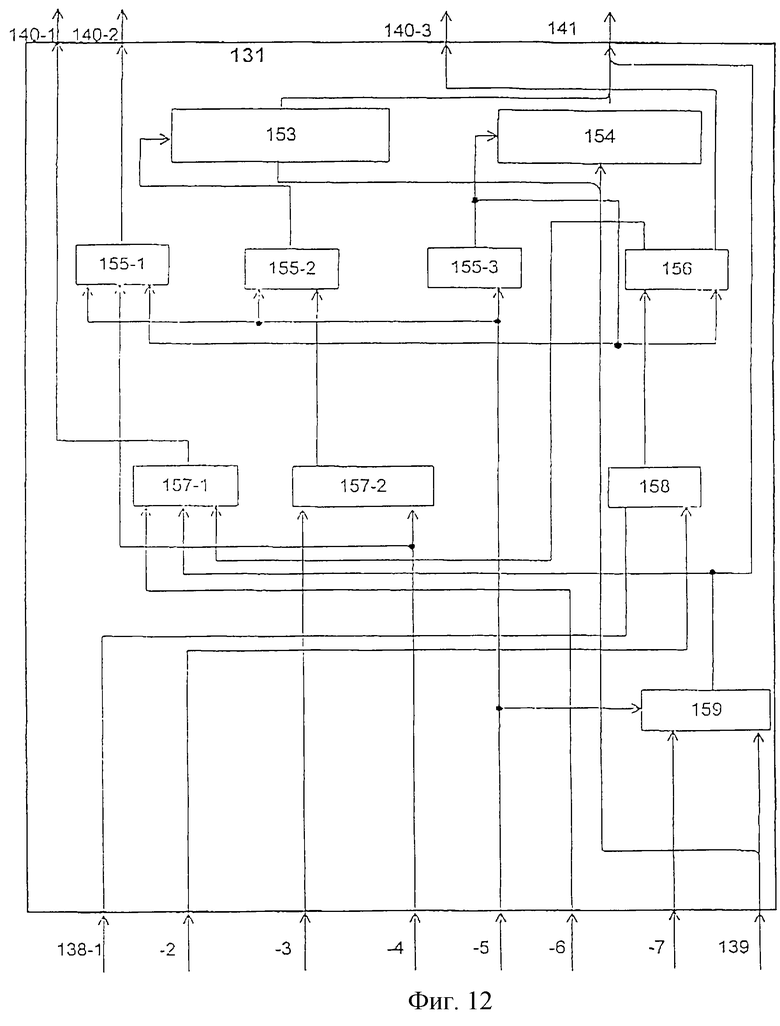

Фиг. 12 - функциональная схема блока выходного регистра процессора программы фрагмента.

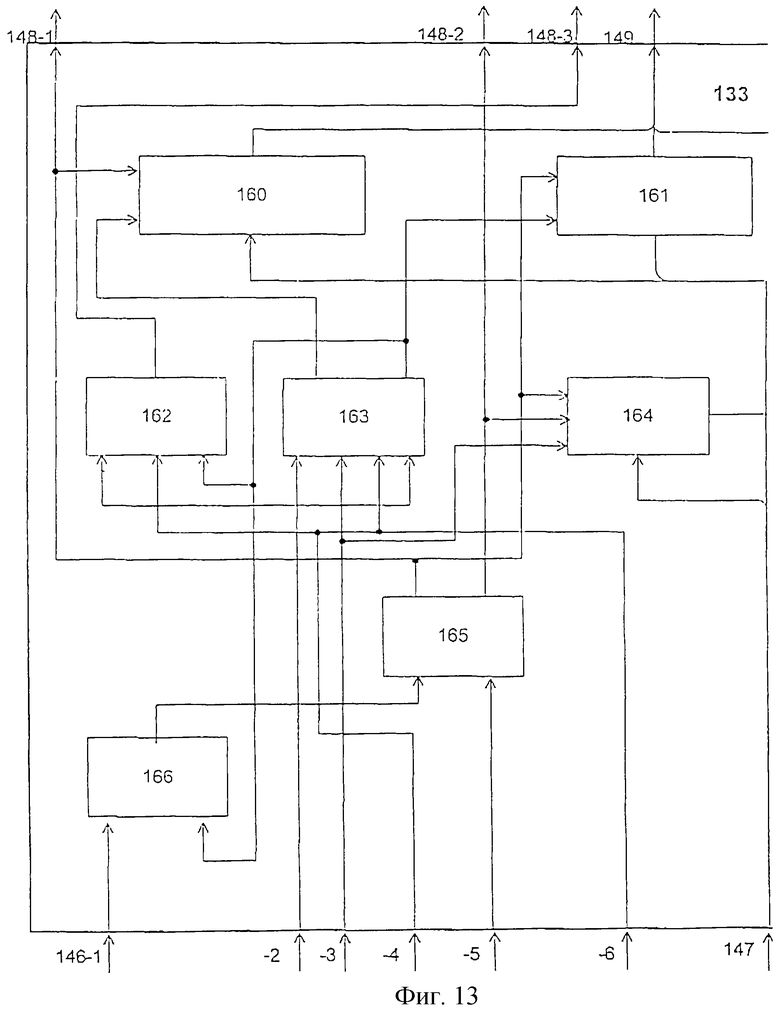

Фиг. 13 - функциональная схема блока входного регистра процессора программы фрагмента.

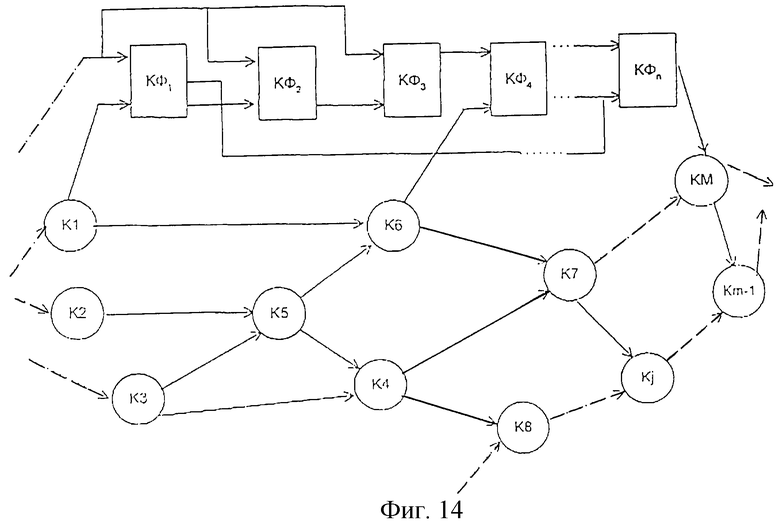

Фиг.14 - иллюстрация общего вида графа потоковых вычислений.

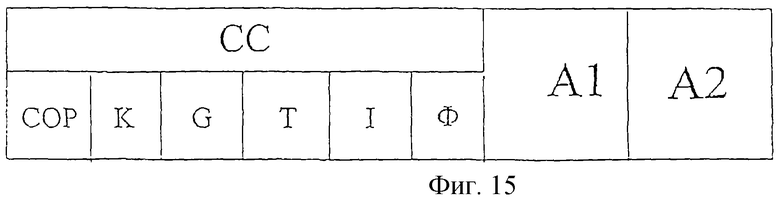

Фиг.15 - иллюстрация структуры пакета информации.

ПОДРОБНОЕ ОПИСАНИЕ НАСТОЯЩЕГО ИЗОБРЕТЕНИЯ

Схема программы системы потока данных описывается как граф, состоящий из узлов и связей, соединяющих узлы. Узлы представляют операции, а связи представляют путь маркеров через систему. Информация, представленная узлом, собирается в пакеты.

Маркеры информации являются словами, которые разделены на некоторое количество полей. Поля могут содержать поле кода операции для представления операции, выполняемой с данными, одно поле данных для представления информации, подлежащей обработке, одно или два поля адреса для представления адреса или узла, к которому направляются результаты обработки, а также другие поля для представления контекста выполнения программы, теги или ключи, используемые для идентификации в процессе обработки данных. Ключи или теги используются для идентификации номера фрагмента, итерации, подлежащей выполнению, отдельных маркеров пары, предназначенной для одного узла, и так далее.

Пакеты информации также являются словами, которые разделены на некоторое количество полей. Пакет может содержать одно или два поля данных.

Таким образом, программа, написанная в соответствии с графом потока данных, укажет направление, в котором данные передаются в процессе обработки. Каждый узел обрабатывает входные данные и выдает один или более результатов, направляемых к одному или более других узлов.

Компьютер, описываемый в этой заявке, содержит центральный процессор и процессор программы фрагмента. Центральный процессор обрабатывает данные, соответствующие принципу потока данных. Процессор программы фрагмента для обработки данных использует принцип фон Неймана.

Компьютер, описываемый в этой заявке, содержит центральный процессор 1, переключатель 2 ввода-вывода, переключатель 3 загрузки команд, память 4 для хранения команд, блок 5 доступа к данным и процессор 6 программы фрагмента.

Блок 5 доступа к данным содержит ассоциативную память 109, первый буфер 106 и второй буфер 107. Первый буфер 106 предназначен для хранения данных, направляемых в центральный процессор 1, а второй буфер 107 предназначен для хранения данных, направляемых в процессор 6 программы фрагмента. Процессор 6 программы фрагмента содержит исполнительный блок 130. Исполнительный блок 130 содержит оперативную память 151.

Набор команд, предназначенный для обработки данных основной программы, то есть программы, подлежащей выполнению, загружают в память 4 для хранения команд. Набор команд и данные программ фрагмента загружают в процессор 6 программы фрагмента, в частности в оперативную память 151.

Пакеты и маркеры, предназначенные для обработки в основном процессоре, направляют через блок 5 прямого доступа к данным в центральный процессор 1.

Пакеты, принимаемые в центральном процессоре 1, подвергают обработке и получают результаты обработки. Если полученный результат является конечным результатом, то есть если он не предназначен для другого узла, то результат направляется к выходу системы. Если результат является результатом разового ввода, то есть он предназначен либо для разового ввода в последующий узел схемы потока данных, либо для ввода в процессор программы фрагмента, то результат посылается непосредственно в блок прямого доступа к данным для дополнительной обработки.

Блок 5 доступа к данным направляет информацию, готовую для дополнительной обработки, к соответствующему устройству. Информация, направляемая для дополнительной обработки в соответствии с принципом потока данных, направляется к центральному процессору 1, информация, предназначенная для обработки в соответствии с принципом фон Неймана, направляется в процессор 6 программы фрагмента. Информация, предназначенная для обработки в процессоре программы фрагмента, идентифицируется как фрагменты. Фрагмент может состоять из одного или более команд и соответствующих операндов.

Данные, предназначенные для ввода в схему потока данных, направляются к первому буферу 106 для дальнейшего направления к центральному процессору 1 либо немедленно, либо после хранения в первом буфере 106. Данные, предназначенные для введения в схему фон Неймана, направляются во второй буфер 107 для дальнейшего направления в процессор 6 программы фрагмента либо немедленно, либо после хранения во втором буфере 107.

Если результат является результатом двойного ввода, то есть результат предназначен быть одним из двух вводов в последующий узел, то результат посылается непрямо к ассоциативной памяти 109, расположенной в блоке 5 прямого доступа к данным, через переключатель 2 ввода-вывода для дополнительной обработки.

Каждый маркер, принимаемый переключателем 2 ввода-вывода, должен быть согласован со своей парой для дальнейшей обработки. Переключатель 2 ввода-вывода считывает ключ на каждом маркере, принимаемом для определения того, хранится ли уже пара маркера в ассоциативной памяти 109. Если эта пара обнаружена, то эти два маркера соединяются вместе в пакете.

Если принимаемая пара маркера не обнаружена, то маркер направляется в ассоциативную память 109 и хранится там для ожидания поступления его пары.

Спаренные данные (или пакет), предназначенные для ввода в схему потока данных, направляются в первый буфер 106 для дальнейшего направления в центральный процессор 1 либо немедленно, либо после хранения в первом буфере 106. Данные, предназначенные для введения в схему фон Неймана, направляются во второй буфер 107 для дальнейшего направления в процессор 6 программы фрагмента либо немедленно, либо после хранения во втором буфере 107.

Таким образом, для подготовки информации для дальнейшей обработки переключатель ввода-вывода и ассоциативная память функционально работают вместе. Как было указано выше, информация, готовая для дальнейшей обработки, направляется с помощью блока доступа к данным в соответствующее устройство для дальнейшей обработки.

Наилучший вариант осуществления настоящего изобретения

Как показано на фиг.1, компьютер содержит центральный процессор 1, переключатель 2 ввода-вывода, переключатель 3 загрузки команд, память 4 для хранения команд, блок 5 доступа к данным и процессор 6 программы фрагмента.

Компьютер содержит также первый информационный выход 7, второй информационный выход 8, обнуляющий вход 9, первый информационный вход 10 и второй информационный вход 11.

Центральный процессор 1 содержит первый управляющий вход 12, второй управляющий вход 13, первый информационный вход 14, третий управляющий вход 15, четвертый управляющий вход 16, пятый управляющий вход 17, второй информационный вход 18, первый управляющий выход 19, второй управляющий выход 20, третий управляющий выход 21, четвертый управляющий выход 22, первый информационный выход 23, второй информационный выход 24 и третий информационный выход 25.

Процессор 6 программы фрагмента содержит первый управляющий вход 26, первый информационный вход 27, второй управляющий вход 28, третий управляющий вход 29, второй информационный вход 30, первый управляющий выход 31, второй управляющий выход 32 и информационный выход 33.

Память 4 для хранения команд содержит управляющий вход 34, информационный вход 35, адресный вход 36, информационный выход 37 и управляющий выход 38.

Блок 5 доступа к данным содержит первый управляющий вход 39, второй управляющий вход 40, третий управляющий вход 41, четвертый управляющий вход 42, пятый управляющий вход 43, обнуляющий вход 44, первый информационный вход 45, второй информационный вход 46, третий информационный вход 47, первый управляющий выход 48, второй управляющий выход 49, первый информационный выход 50, второй информационный выход 51, третий управляющий выход 52, четвертый управляющий выход 53 и третий информационный выход 54.

Переключатель 3 загрузки команд содержит первый информационный вход 55, второй информационный вход 56, первый управляющий вход 57, второй управляющий вход 58, управляющий выход 59 и информационный выход 60.

Переключатель ввода-вывода содержит первый управляющий вход 61, второй управляющий вход 62, третий управляющий вход 63, четвертый управляющий вход 64, первый информационный вход 65, второй информационный вход 66, первый управляющий выход 67, второй управляющий выход 68 и информационный выход 69.

Как показано на фиг. 2, центральный процессор 1 содержит управляющее устройство 70, переключатель 71, блок 72 выходного регистра, арифметико-логическое устройство 73 и блок 74 входного регистра.

Управляющее устройство 70 содержит вход 75-1 установки нуля, первый управляющий вход 75-2 передачи результата, второй управляющий вход 75-3 передачи результата, начальный управляющий вход 75-4, вход 75-5 битов типа команды, вход 75-6 сигнала готовности памяти, вход 75-7 сигнала значимости бита данных, вход 75-8 сигнала готовности, первый управляющий выход выходного переключения 76-1, второй управляющий выход выходного переключения 76-2, управляющий выход 76-3 передачи, управляющий выход 76-4 приема, начальный управляющий выход 76-5, первый управляющий выход, соединенный с выходом 19 центрального процессора 1, второй управляющий выход, соединенный с выходом 21 центрального процессора 1, и третий управляющий выход, соединенный с выходом 22 центрального процессора 1.

Блок 72 выходного регистра содержит управляющие входы 77-1, 77-2 и 77-3, информационный входы 77-4, 77-5 и 77-6 и информационные выходы 78-1, 78-2 и 78-3.

Переключатель 71 содержит информационный выход, соединенный с выходом 24 центрального процессора 1, первый управляющий вход, соединенный с выходом 76-1 управляющего устройства 70, первый информационный вход, соединенный с выходом 78-2 блока 72 выходного регистра, и второй информационный вход, соединенный с выходом 78-3 блока 72 выходного регистра.

Блок 74 входного регистра содержит управляющий вход 79-1, информационный вход 79-2 и информационные выходы 80-1...80-5.

Арифметико-логическое устройство 73 (выполненное в аналоговом виде для устройства, описанного в патенте СССР 1367012, выданном в 1985 году) содержит управляющий операциями вход, соединенный с выходом 80-2 блока 74 входного регистра, вход первого операнда, соединенный с выходом 80-3 блока 74 входного регистра, вход второго операнда, соединенный с выходом 80-4 блока 74 входного регистра, начальный управляющий вход, соединенный с выходом 76-5 управляющего устройства 70, первый информационный выход, соединенный с выходом 25 центрального процессора 1, второй информационный выход, соединенный со входом 75-7 управляющего устройства 70 и входом 77-4 блока 72 выходного регистра, и управляющий выход, соединенный с входом 75-8 управляющего устройства 70.

Как показано на фиг.3, управляющее устройство 70 содержит элементы 81-1 и 81-2 "ИЛИ", элементы 82-1. . .82-4, 83-1 и 83-2 "И", элемент 84 "ИЛИ", элементы 85-1, 85-2 "И", элемент 86 "ИЛИ", кодер 87 приоритета, элементы 88-1, 88-2 и 89 "ИЛИ", триггеры 90-1...90-3, триггеры 91-1...91-3, элементы 92-1...92-6 "И", элемент 93 "ИЛИ" и элемент 94 "И".

Как показано на фиг. 4, блок 74 входного регистра содержит регистр 95 слова состояния, регистр 96-1 первого операнда и регистр 96-2 второго операнда.

Как показано на фиг.5, блок 72 выходного регистра содержит регистр 97 результата, первый и второй регистры 98-1 и 98-2 номера команды соответственно и регистр 99 индикации состояния.

Как показано на фиг.6, переключатель 2 ввода-вывода содержит элементы 100-1...100-4 "ИЛИ", элементы 100-1...100-2 "И", кодер 102 приоритета, триггеры 103-1, 103-2, переключающее устройство 104, входные регистры 105-1,105-2.

Переключающее устройство 104 может состоять из двух элементов "И" и одного элемента "ИЛИ" или из логического элемента, например из логического элемента "ИЛИ-НЕ".

Как показано на фиг.7, блок 5 доступа к данным содержит первый и второй буферы 106 и 107 соответственно, регистр 108 и ассоциативную память 109.

Первый буфер 106 содержит первый и второй управляющие входы 110-1 и 110-2, первый и второй информационные входы 110-3 и 110-4, третий и четвертый управляющие входы 110-5 и 110-6, вход 110-7 внешнего обмена, первый и второй управляющие входы передачи, соединенные соответственно с выходами 49 и 52 блока 5, информационный выход, соединенный с выходом 50 блока 5 и выход внешнего обмена, соединенный с выходом 51 блока 5.

Второй буфер 107 содержит первый и второй управляющие входы 111-1 и 111-2 соответственно, первый и второй информационные входы 111-3 и 111-4, третий и четвертый управляющие входы 111-5 и 111-6 соответственно и управляющий и информационный входы, соединенные соответственно с выходами 53 и 54 блока 5.

Ассоциативная память 109, выполненная аналогично устройству, описанному в патенте Российской Федерации 2035069, выданном в 1995 году, содержит первый и второй управляющие входы 112-1 и 112-2 соответственно, первый информационный вход 112-3, третий управляющий вход 112-4, второй информационный вход 112-5, первый информационный выход 115-6, первый управляющий выход 113-2, второй информационный выход 113-3 и второй управляющий выход 113-4.

Как показано на фиг.8, первый буфер 106 содержит элементы 114-1...114-5 "ИЛИ", выходной переключатель 115, элементы 116-1...116-4 "И", блок 117 запоминающего регистра, управляющее устройство 118, входной переключатель 119 и первый и второй входные регистры 120-1 и 120-2 соответственно.

Второй буфер выполнен аналогично первому.

Управляющее устройство 118 содержит управляющие выходы 121-1...121-12, вход 122-1 настройки, вход 122-2 кода первого пакета, первый приемный управляющий вход 122-3, второй вход 122-4 кода пакета, второй и третий приемные управляющие входы 122-5 и 122-6 соответственно и первый... пятый управляющие входы 123-1...123-5.

Как показано на фиг. 9, управляющее устройство 118 содержит кодер 124 приоритета, счетчики 125-1...125-2, логические элементы 126-1...126-4 "И", триггеры 127-1...127-3, элемент 128 "ИЛИ" и декодеры 129-1...129-3.

Как показано на фиг.10, процессор 6 программы фрагмента содержит исполнительный блок 130, блок 131 выходного регистра, блок 132 регистра загрузки и блок 133 входного регистра.

Исполнительный блок 130 содержит первый. .. третий управляющие входы 134-1. .134-3, информационный вход 135, информационный выход 136 и первый... пятый управляющие выходы 137-1...137-5.

Блок 131 выходного регистра содержит первый... седьмой управляющие входы 138-1. ..138-7, информационный вход 139, первый... третий управляющие выходы 140-1...140-3 и информационный выход 141.

Блок 132 регистра загрузки содержит первый... пятый управляющие входы 142-1. . .142-5, информационный вход 143, первый и второй управляющие выходы 144-1 и 144-2 и информационный выход 145.

Блок 133 выходного регистра содержит первый... шестой управляющие входы 146-1. ..146-6, информационный вход 147, первый... третий управляющие выходы 148-1...148-3 и информационный выход 149.

Как показано на фиг.11, исполнительный блок 130 содержит микропроцессор 150, оперативную память 151 и шину 152 обмена. Вместо этих элементов может быть использован стандартный микропроцессорный комплект, например комплект на основе элементов типа Intel 80386.

Как показано на фиг.12, блок 131 выходного регистра содержит первый и второй регистры 153 и 154 соответственно, элементы 155-1...155-3 "И", триггер 156, декодеры 157-1 и 157-2, элемент 158 "ИЛИ" и регистр 159.

Как показано на фиг.13, блок 133 входного регистра содержит регистры 160 и 161, элемент 162 "И", декодер 163, регистр 164, триггер 165 и элемент 166 "ИЛИ".

Блок 132 регистра загрузки имеет аналогичную структуру.

Принципы организации вычисления при управлении потоком данных допускают, что алгоритм решения задачи представлен как граф процесса вычисления. Граф содержит операторы (команды) на данных (операндах) и указатели (направления), следуя которым данные (результаты) передаются от команды к команде, как показано на фиг.14.

В соответствии с графом обработка данных выполняется при поступлении подготовленных данных для обработки на входы команд. Завершение пар данных, относящихся к конкретной команде, выполняется в ассоциативной памяти 109, используя ключ при поиске и образовании пар данных. Ключ, как правило, представляет собой код, который содержит биты номера команды, индекс, итерацию и так далее.

Каждая команда имеет номер N-i, который может быть использован для размещения ее в памяти 4 для хранения команд, код команды - COI-i, и номер N-j "присвоенного адреса", представляющий команду, к которой относится результат обработки данных. Кроме того, команда имеет атрибуты, определяющие условия ее обработки или ее тип. Команда может быть двухвходовой или одновходовой командой, что определяется кодом операции в зависимости от того, как много (один или два) входа обрабатывает команда. Команда может быть двухадресной или одноадресной командой в зависимости от числа адресов передачи результата (результатов) выполнения команды. Например, как показано на фиг.14, команда N1 является одновходовой двухадресной командой, а команда N2 - одновходовой одноадресной командой.

Для организации работы графа команды и данные представлены как информационные объекты, состоящие из многобитовых слов, где соответствующие группы битов образуют поля с необходимыми функциональными назначениями (фиг.15).

В общем, информация вводится в центральный процессор 1 в виде пакета данных, содержащего слово (команду) состояния и два слова данных. Пакет одновходной команды содержит только одно информационное слово.

Слово состояния содержит следующие основные группы функциональных битов (полей):

COI - код команды;

N - номер команды;

G - номер генерации;

Т - номер итерации;

I - индекс;

F - номер фрагмента.

Функциональные поля слова состояния могут быть использованы разными способами. В частности, основная группа битов для поиска данных в ассоциативной памяти 109 ограничена полями N, G, Т, I. Поле F вводится в том случае, если для фрагментов необходимо найти входные данных. Поле COI может содержать биты, указывающие тип команды (одноадресная, двухадресная, одновходовая, двухвходовая).

Если команда имеет два выхода (адреса назначения для результатов обработки), то результат ее выполнения будет содержать два слова состояния, соответствующих двум адресам передачи.

Битовые группы слова состояния хранятся в памяти 4 для хранения команд.

Команды и данные, которые являются частью отмеченных фрагментов (фиг. 14), хранятся в оперативной памяти 151 исполнительного блока 130 процессора 6 программы фрагмента и не занимают ассоциативную память 109.

Входы синхронизации всех блоков компьютера соединены с внешним входом синхронизации (не показано).

Основные рабочие программы и отмеченные программы фрагмента загружаются через первый информационный вход 10 и выполняются компьютером (фиг.1), который выдает результаты обработки данных через второй информационный выход 8.

Компьютер использует управление потоком данных для процесса вычисления в соответствии с основной программой и в соответствии с принципами фон Неймана обработки данных для выполнения отмеченных фрагментов. Все команды основной исполнительной программы вводятся в память 4 для хранения команд, а все команды и данные для фрагментов вводятся в оперативную память 151 (фиг.11). Вычисление инициализируется загрузкой начальных пакетов операндов из внешней системы (не показана) через второй информационный вход 11.

Начальные пакеты вместе с соответствующими управляющими сигналами вводятся через второй информационный вход 46 блока 5 доступа к данным и затем через вход 110-7 внешнего обмена первого буфера 106, из которого они передаются к информационному (например, четвертому) входу выходного переключателя 115. В этом случае управление связью осуществляется через четвертый управляющий вход, причем соответствующий управляющий сигнал из управляющего выхода 121-12 управляющего устройства 118 поступает через элемент 116-4 "И". Указанный управляющий сигнал формируется на выходе декодера 129-3. Группа битов кода, определяющего тип начального пакета, поступает через вход декодера 129-3.

Биты пакета из выхода 50 буфера 106 передаются ко второму информационному входу 18 центрального процессора 1 через соответствующий выход блока 5 доступа к данным.

Информация, передаваемая через выход 50 блока 5 доступа к данным, сопровождается стробом передачи на выходе 52. Строб передачи на выходе 52 представляет собой управляющий сигнал для запуска центрального процессора 1, поступающий через пятый управляющий вход 17 и затем через вход 75-4 управляющего устройства 70. Биты пакета операнда передаются к информационному входу 79-2 блока 74 входного регистра.

Прием функциональных полей пакета операнда регистром 95 слова состояния и регистрами 96-1 и 96-2 операндов управляется путем ввода приемного управляющего сигнала на входе 79-1 блока 74 входного регистра. Биты номера команды передаются из выхода 80-1 блока 74 входного регистра через первый информационный выход 23 центрального процессора 1 на первый информационный вход 55 переключателя 3 загрузки команд. Управляющий сигнал из второго управляющего выхода 20 центрального процессора 1 поступает на первый информационный вход 57 блока 3 загрузки команд. Управляющий сигнал, соответствующий коду считывания, и информационный сигнал, соответствующий адресу, формируются соответственно на управляющем и информационном выходах 59 и 60 переключателя 3 для передачи к соответствующим управляющему и адресному входам памяти 4 для хранения команд. Код битов операции и битов операнда из выходов 80-2, 80-3 и 80-4 блока 74 входного регистра сопровождаются начальным управляющим сигналом из выхода 76-5 управляющего устройства 70 и передаются на соответствующие входы арифметико-логического блока 73. Биты G, Т, I функционального поля передаются на вход 77-6 блока 72 выходного регистра. Биты функционального поля из информационного выхода 37 памяти 4 для хранения команд передаются через вход 14 центрального процессора 1 на вход 77-5 блока 72 выходного регистра. Биты функционального поля, переданные на вход 77-5, содержат код операции и номер команды, для которого предназначен результат вычисления, поступающий на вход 77-4 блока 72.

Входы 77-1, 77-2 и 77-3 блока 72 выходного регистра принимают соответствующие сигналы, которые управляют приемом результата регистром 97, битовых полей N и COI следующей команды регистрами 98-1 и 98-2 и битовых полей G, Т, I регистром 99. Функциональные поля результата выполнения текущей команды (полупакета) формируются на выходах 78-1, 78-2 и 78-3 блока 72 выходного регистра. Эти поля отражают принципы вычисления, представленные с помощью графа процесса вычисления, и передаются, соответственно, на выход 24 центрального процессора 1 и информационные входы переключателя 71. Управляющие сигналы передаются из выходов 76-1 и 76-2 управляющего устройства 70 на управляющие входы переключателя 71. Работа переключателя 71 зависит от наличия двухадресных команд, то есть от команд, результат выполнения которых является входным операндом для двух последующих команд (имеющих разные номера и разные коды команд). Это условие выполняется при наличии двух выходных регистров 98-1 и 98-2 номера команды, содержимое которых последовательно передается через переключатель 71 и сопровождается результатом, передаваемым на выход 24 центрального процессора 1.

Управляющие сигналы для выходного переключателя 71 формируются при приеме на входах 75-5 и 75-6 управляющего устройства 70 функциональных полей типа команды и строба передачи соответственно из информационного и управляющего выходов 37 и 38 памяти для хранения команд через входы 14 и 15 центрального процессора 1 и при приеме на входе 75-7 сигнала значимости результата из арифметико-логического блока 73.

Функциональные поля типа команды содержат следующие атрибуты: 1А (одноадресная команда), 2А (двухадресная команда) и 2I (двухвходовая команда), которые передаются к триггерам 92-2...92-5. Состояние триггера определяет формирование управляющих сигналов на выходах 76-1 и 76-2 блока 70. Стробы передачи, соответствующие режимам одновходовой или двухвходовой команды, формируются на выходах 22 и 19 центрального процессора 1, а биты функциональных полей полупакета - на выходе 24.

Если выполняется одновходовая команда и результат выполнения не требует поиска пары в ассоциативной памяти 109, то биты полупакета и строба передачи передаются из выходов 24 и 22 центрального процессора 1 соответственно на входы 47 и 43 блока доступа к данным и на входы 110-3 и 110-5 буфера 106. При поступлении битов на вход 110-3 результат принимается первым входным регистром 120-1 и через первый информационный выход входного переключателя 119 передается на первый информационный вход переключателя 115. Второй информационный выход переключателя 119 используется для передачи результатов вычисления на внешнюю систему управления. В этом случае на первом выходе декодера 129-1 управляющего устройства 118 формируется соответствующий управляющий сигнал. Биты кода, определяющие тип полупакета, поступают на вход декодера 129-1. Информация из второго информационного выхода переключателя 119 вместе со стробом передачи из выхода 121-7 управляющего устройства 118 поступает на выход 51 буфера 106 и передается через соответствующий выход блока 5 доступа к данным на второй информационный выход 8 компьютера.

Если результат (операнд) на выходе 24 центрального процессора 1 относится к двухвходовой команде, то в ассоциативной памяти 109 в блоке 5 доступа к данным выполняется поиск парного операнда. Этот результат из выхода 24 передается на вход 65 переключателя 2 ввода-вывода и через переключатель 2 ввода-вывода - в блок 5 доступа к данным.

Сигнал строба передачи и биты функциональных полей полупакета передаются из выходов 19 и 24 центрального процессора 1 соответственно на входы 61 и 65 переключателя 2 ввода-вывода.

В переключателе 2 полупакет передается из входа 65 через регистр 105-1 на первый информационный вход переключающего устройства 104. Строб передачи передается из входа 61 на вход настройки триггера 103-1. Выход триггера 103-1 соединен с первым управляющим входом кодера 102 приоритета. Код управления переключающего устройства 104 формируется на первом и втором управляющих выходах кодера 102 приоритета. Конечным результатом является то, что в переключателе 2 биты функциональных полей полупакета передаются из входа 65 на выход 69, а на выходе 67 генерируется соответствующие управляющий сигнал и строб передачи.

Биты функциональных полей и строба передачи передаются из выходов 69 и 67 переключателя на входы 45 и 39 блока 5 доступа к данным. Битовые поля слова состояния (как ключа ассоциативного поиска), операнда и строба передачи поступают соответственно на входы 112-3, 112-5 и 112-4 ассоциативной памяти 109.

Битовые поля слова состояния также поступают на информационный вход регистра 108. Строб передачи из входа 39 блока 5 доступа к данным поступает на управляющий вход регистра 108.

Полупакет, к которому не найдена пара, остается в ассоциативной памяти 109. Если соответствующая пара операнда найдена, то на выходах 113-1 и 113-3 формируются битовые поля первого и второго операндов. Эти битовые поля передаются вместе с битовыми полями слова состояния из выхода регистра 108 на вторые информационные входы 110-4 и 111-4 буферов 106 и 107 соответственно. Строб передачи передается из выхода 113-2 ассоциативной памяти 109 на входы 110-6 и 111-6 буферов 106 и 107 соответственно.

Если результирующий пакет представляет собой пакет операндов основной программы, то биты его функционального поля принимаются на регистре 120-2 буфера 106, а на выходе 121-9 управляющего устройства 118 формируется соответствующий управляющий сигнал приема.

Битовые поля пакета передаются из выхода регистра 120-2 на второй информационный вход переключателя 115, а соответствующий управляющий сигнал переключения передается из выхода элемента 116-1 "И" на соответствующий управляющий вход переключателя 115. Переключатель 115 передает битовые поля на первый выход переключателя 115, который выполняет функцию строба передачи, который в конечном счете образуется на выходе элемента 114-1 "ИЛИ".

Если блок 74 выходного регистра центрального процессора 1 свободен, то вся информация из выхода переключателя 115 буфера 106 передается в центральный процессор 1 и цикл обработки данных повторяется.

Если блок 74 центрального процессора 1 занят, то из выхода 21 центрального процессора 1 через вход 41 блока 5 доступа к данным на вход 110-1 буфера 106 передается сигнал блокировки передачи. После этого сигнал передается из входа 110-1 на вход 123-2 управляющего устройства 118 и на вход элемента 114-5 "ИЛИ". На выходе элемента 114-5 "ИЛИ" формируется управляющий сигнал, который передается на пятый управляющий вход переключателя 115. Информация из второго информационного входа переключателя 115 передается через второй выход переключателя 115 и затем, сопровождаемый сигналом записи из выхода 121-11 управляющего устройства 118, передается на вход блока 117 запоминающего регистра. Запись информации будет сделана в блоке 117 перед выведением сигнала блокировки из выхода 21 центрального процессора 1. При отсутствии информации в регистрах 120-1 и 120-2 и на четвертом информационном выходе переключателя 115 выведение сигнала блокировки приводит к передаче битов пакета из блока 117 через третий информационный вход переключателя 115 и соответствующие выход буфера 106 и выход 50 блока 5 доступа к данным на вход 18 центрального процессора 1.

Если пакет, сформированный на выходе регистра 108 и выходах 113-1 и 113-2 ассоциативной памяти 109, является начальным пакетом локальной программы, указанной фрагментом F, то биты его функциональных полей принимаются буфером 107.

В других случаях передача начального пакета фрагмента F на вход 30 процессора 6 программы фрагмента осуществляется аналогично вышеуказанной передаче пакетов операндов через буфер 106.

Биты функциональных полей начального пакета фрагмента и строба передачи, сформированные соответственно на выходах 54 и 53 блока 5 доступа к данным, поступают соответственно на входы 30 и 29 процессора 6 программы фрагмента. В противоположность центральному процессору 1, где после выполнения каждого пакета осуществляется доступ к ассоциативной памяти 109, в процессоре 6 программы фрагмента осуществляется выполнение отмеченных фрагментов (частей) основной программы и конечные результаты передаются в ассоциативную память.

В начале загрузки компьютера осуществляется загрузка программ (соответствующих принципам обработки фон Неймана) через первый информационный вход 10.

В этом случае и команды и данные поступают через вход 27 процессора 6 программы фрагмента, откуда они передаются на вход 143 блока регистра загрузки.

Биты функциональных полей команд (соответствующие системе команд исполнительного блока 130) и данных передаются из выхода 145 блока 132 на информационный вход 135 блока 130. Передача из выхода 145 на вход 135 сопровождается передачей соответствующих сигналов прерывания и готовности из выходов 144-1 и 144-2 блока 132 на входы 134-2 и 134-3, соответственно, блока 130.

Через шину 152 обмена под управлением микропроцессора 150 в оперативную память 151 осуществляется загрузка команд и данных фрагментов рабочих программ.

При поступлении начальных пакетов фрагмента на вход 147 блока 133 и соответствующего строба передачи на вход 146-5 блока 133 операнды принимаются регистрами 160 и 161, а поле F слова состояния принимается регистром 164. Наличие строба передачи на входе 146-5 подготавливает к работе триггер 165 и на выходе 148-2 формируется сигнал прерывания. Сигнал прерывания поступает на вход 134-2 блока 130 вместе с битовым полем, которое поступает на информационный вход 135 блока 130 из выхода 149 блока 133. Битовое поле на выходе 149 принимается из регистра 164 под управлением выхода сигнала "считывания" из триггера 165. Микропроцессор 150 "идентифицирует" битовое поле, передаваемое через шину 152 обмена из входа 135 блока 130, и обеспечивает выход группы управляющих сигналов на выходах 137-1, 137-2, 137-3 и 137-4. Эта группа управляющих сигналов передается на входы 146-2, 146-2, 146-4 и 146-6 блока 133, где через выход 149 на информационном входе 135 блока 130 формируются соответствующие сигналы последовательного считывания и передачи данных из регистров 160 и 161. Микропроцессор 150 в соответствии с номером и параметрами фрагмента F начинает соответствующее выполнение программы. Завершение выполнения программы сопровождается прерыванием микропроцессора 150. Благодаря такому прерыванию микропроцессор 150 формирует "вектор выхода", который соответствует текущему номеру, присвоенному регистру 159 блока 131. "Вектор выхода" передается через шину 152 обмена и выход 136 на вход 139 блока 131. Передача "вектора выхода" сопровождается передачей управляющего сигнала из выхода 137-5 блока 130 на вход 138-7 блока 131. Информация записывается в регистр 159. Информация из регистра 159 передается на вход декодера 157-1. На выходе декодера 157-1 формируется сигнал прерывания и передается через выход 140-1 на вход 134-2 блока 130. При приеме микропроцессором 150 сигнала прерывания формируется группа управляющих сигналов, которая передается через выходы 137-1...137-4 блока 130 на входы 138-3... 138-6 блока 131. Сигналы, принимаемые на входах 138-3...138-6, управляют приемом (на входах регистров 153 и 154) битовых полей, которые образуются в результате обработки фрагмента F. Битовые поля, принимаемые на входах регистров 153 и 154, передаются из выхода 136 блока 130 через вход 139 блока 131.

Формат данных в регистрах 153 и 154 соответствует формату полупакета, получаемому в результате выполнения команд центральным процессором 1. То есть формат результатов обработки процессором программы фрагмента и формат результатов обработки центральным процессором одинаковы и результаты обработки этими двумя устройствами могут быть скомбинированы в ассоциативной памяти (или где-либо еще в зависимости от конкретной конфигурации системы).

Строб передачи формируется на выходе 140-3 блока 131 и передается на выход 32 процессора 6 программы фрагмента. Строб передачи передается из выхода 32 на вход 63 переключателя 2. Функциональные битовые поля полупакета, которые образуются в результате выполнения программы фрагмента, передаются из выхода 33 процессора 6 на вход 66 переключателя 2.

Битовые поля полупакета передаются из выхода 69 переключателя 2 на вход блока 5 доступа к данным. Результаты выполнения программы фрагмента и выполнения основной программы комбинируются посредством общего поля.

Таким образом, введение в систему процессора программы фрагмента и организация соответствующих связей уменьшают количество данных, хранимых в ассоциативной памяти.

Уменьшение объема ассоциативной памяти повышает скорость ее обмена и увеличивает быстродействие в процессе выполнения основных рабочих программ при использовании управления потоком данных вычисления.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1997 |

|

RU2130198C1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| СПОСОБ КОДИРОВАНИЯ И ИСПОЛНЕНИЯ КОНТЕКСТНО-ЗАВИСИМОЙ ПРОГРАММЫ МУЛЬТИКЛЕТОЧНЫМ ПРОЦЕССОРОМ, МУЛЬТИКЛЕТОЧНЫЙ ПРОЦЕССОР, КЛЕТКА И КОММУТАЦИОННОЕ УСТРОЙСТВО МУЛЬТИКЛЕТОЧНОГО ПРОЦЕССОРА ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА | 2013 |

|

RU2530690C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1998 |

|

RU2148857C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1995 |

|

RU2110089C1 |

| СРАВНЕНИЕ И ЗАМЕНА ПОЗИЦИИ ТАБЛИЦЫ ДИНАМИЧЕСКОЙ ТРАНСЛЯЦИИ АДРЕСА | 2012 |

|

RU2550558C2 |

| КОНФИГУРАЦИЯ АРХИТЕКТУРНОГО РЕЖИМА В ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЕ | 2015 |

|

RU2664413C2 |

| Ассоциативный матричный процессор | 1981 |

|

SU1005065A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

Изобретение относится к вычислительной технике, в частности к вычислительным устройствам, в которых для обработки информации используют управление потоком данных. Технический результат заключается в повышении быстродействия путем уменьшения объема ассоциативной памяти посредством применения процессора программы фрагмента для выполнения сегментов программы. Устройство содержит центральный процессор, переключатель ввода-вывода, переключатель загрузки команд, память для хранения команд и блок доступа к данным, в котором используется принцип вычисления потока данных. 1 з.п. ф-лы, 15 ил.

| ПЕРСОНАЛЬНАЯ КОМПЬЮТЕРНАЯ СИСТЕМА | 1991 |

|

RU2072553C1 |

| ПЕРСОНАЛЬНАЯ КОМПЬЮТЕРНАЯ СИСТЕМА | 1991 |

|

RU2068578C1 |

| US 5226131 A, 06.07.1997. | |||

Авторы

Даты

2003-11-10—Публикация

1998-08-06—Подача