Изобретение относится к вычислительной технике, в частности, к вычислительным устройствам, использующим управление процессом вычислений от потока данных, и может быть использовано в цифровых вычислительных системах высокой производительности.

Известно устройство для обработки данных, содержащее процессор, память команд, прямоадресную память данных, блок сопряжения, блок выборки команд, блок распечатки команд и процессор присвоения номера регистра (см. например, Патент США N 4675806, кл. 364-200).

Однако это устройство имеет относительно невысокую производительность, что свойственно всему классу вычислительных устройств, использующих управление вычислениями от потока данных, а в качестве аппаратных средств хранения данных - прямоадресную оперативную память.

Усложненная организация аппаратных средств управления в таких вычислительных системах и дополнительные затраты времени на процессы динамического распределения памяти (работу операционной системы) приводят к снижению производительности.

Известно устройство обработки данных, содержащее процессор, коммутатор ввода-вывода, коммутатор загрузки команд, память команд, устройство выборки данных, первый и второй информационные выходы, вход обнуления, первый и второй информационные входы, при этом первый управляющий выход процессора подключен к первому управляющему входу коммутатора ввода-вывода, первый управляющий вход которого соединен с первым управляющим входом устройства выборки данных, первый информационный вход которого соединен с информационным выходом коммутатора загрузки команд, первый управляющий вход которого подключен ко второму управляющему выходу процессора, первый и второй информационные выходы которого соединены, соответственно с первым информационным входом коммутатора загрузки команд и первым информационным входом коммутатора ввода-вывода, третий информационный выход процессора подключен к первому информационному выходу вычислительной машины, к выходу обнуления которой подключен вход обнуления устройства выборки данных, информационный вход памяти команд и информационный вход коммутатора загрузки команд соединены с первым информационным входом вычислительной машины (см. например, Патент РФ N 2029359, кл. G 06 F 15/00).

Это устройство также использует для управления процессом вычислений поток данных, а в качестве аппаратных средств хранения данных результатов - ассоциативную память (блок выборки данных), которая одновременно выполняет функцию аппаратных средств управления. При этом отсутствуют дополнительные аппаратные средства управления и нет потери времени на процессы распределения памяти, за счет чего возрастает производительность.

Однако использование в известном устройстве ассоциативной памяти (в блоке выборки данных) определяет прямую зависимость производительности устройства от темпа выдачи данных ассоциативной памятью (число готовых к исполнению операндов в единицу времени N = 1/T ап, где T ап - время работы ассоциативной памяти от момента запроса до выдачи данных.

Величина T ап находится в прямой зависимости от объема ассоциативной памяти, что определяет существенный недостаток устройства в целом требования со стороны рабочих программ к увеличению ее объема приводят к соответствующему снижению производительности устройства.

Указанные недостатки не позволяют реализовать в известном устройстве высокую производительность при условии обработки больших объемов рабочих программ.

Техническим результатом является повышение производительности путем соответствующего снижения объема ассоциативной памяти за счет локального введения в процесс вычислений традиционного принципа (фон Неймана) обработки данных без нарушения общей концепции управления вычислениями от потока данных.

Достигается это тем, что в вычислительную машину, содержащую процессор, коммутатор ввода-вывода, коммутатор загрузки команд, память команд, устройство выборки данных, первый и второй информационные выходы, вход обнуления, первый и второй информационные входы, при этом первый управляющий выход процессора подключен к первому управляющему входу коммутатора ввода-вывода, первый управляющий выход которого соединен с первым управляющим входом устройства выборки данных, первый информационный вход которого подключен к информационному выходу коммутатора ввода-вывода, адресный вход памяти команд соединен с информационным выходом коммутатора загрузки команд, первый управляющий вход которого подключен ко второму управляющему выходу процессора, первый и второй информационные выходы которого соединены, соответственно с первым информационным входом коммутатора загрузки команд и первым информационным входом коммутатора ввода-вывода, третий информационный выход процессора подключен к первому информационному выходу вычислительной машины, к входу обнуления которой подключен вход обнуления устройства выборки данных, информационный вход памяти команд и второй информационный вход коммутатора загрузки команд соединены с первым информационным входом вычислительной машины, введено устройство обработки фрагментов программ, причем его первый управляющий выход соединен со вторым управляющим входом устройства выборки данных, первый управляющий выход которого подключен ко второму управляющему входу коммутатора ввода-вывода, второй управляющий выход которого соединен с первым управляющим входом процессора и первым управляющим входом устройства обработки фрагментом программ, второй управляющий выход которого подключен к третьему управляющему входу коммутатора ввода-вывода, второй информационный вход которого соединен с информационным выходом устройства обработки фрагментов программ, второй управляющий выход устройства выборки данных подключен ко второму управляющему входу процессора, первый информационный вход которого соединен с информационным выходом памяти команд, управляющий вход которой подключен к управляющему выходу коммутатора загрузки команд, второй управляющий вход которого и первый информационный вход устройства обработки фрагментов программ соединены с первым информационным входом вычислительной машины, управляющий выход памяти команд подключен к третьему управляющему входу процессора, третий управляющий выход которого соединен с третьим управляющим входом устройства выборки данных, второй информационный вход которого подключен ко второму информационному входу вычислительной машины, вход обнуления которой соединен со вторым управляющим входом устройства обработки фрагментов программ, с четверым управляющим входом устройства выборки данных, с четвертым управляющим входом коммутатора ввода-вывода и с четвертым управляющим входом процессора, четвертый управляющий выход которого подключен к пятому управляющему входу устройства выборки данных, третий информационный вход которого соединен со вторым информационным выходом процессора, пятый управляющий вход которого подключен к третьему управляющему выходу устройства выборки данных, первый информационный вход которого соединен со вторым информационным входом процессора, второй информационный выход устройства выборки данных подключен ко второму информационному выходу вычислительной машины, третий управляющий вход устройства обработки фрагментов программ соединен с четвертым управляющим выходом устройства выборки данных, а третий информационный выход подключен ко второму информационному входу устройства обработки фрагментом программ, кроме того, устройство обработки фрагментов программ содержит исполнительный блок, блок выходных регистров, блок регистров загрузки и блок входных регистров, причем информационный выход исполнительного блока соединен с информационным входом блока выходных регистров, первый управляющий вход которого подключен к первому управляющему входу устройства, второй управляющий вход которого соединен с первым управляющим входом исполнительного блока, вторым управляющим входом блока выходных регистров, первым управляющим входом блока регистров загрузки и с первым управляющим входом блока входных регистров, первый управляющий выход которого подключен к первому управляющему выходу устройства, первый информационный вход которого соединен с информационным входом блока регистров загрузки, информационный выход которого и информационный выход блока входных регистров подключены к информационному входу исполнительного блока, второй управляющий вход которого соединен с первым управляющим выходом блока выходных регистров, первым управляющим выходом блока регистров загрузки и вторым управляющим выходом блока входных регистров, третий управляющий выход которого, второй управляющий выход блока регистров загрузки, второй управляющий выход блока выходных регистров подключены к третьему управляющему входу исполнительного блока, первый управляющий выход которого соединен со вторым управляющим входом блока регистров загрузки, вторым управляющим входом блока входных регистров и третьим управляющим входом блока выходных регистров, третий управляющий выход которого подключен ко второму управляющему выходу устройства, второй информационный вход которого соединен с информационным входом блока входных регистров, третий управляющий вход которого, третий управляющий вход блока регистров загрузки и четвертый управляющий вход блока выходных регистров подключены ко второму управляющему выходу исполнительного блока, третий управляющий выход которого соединен с четвертым управляющим входом блока регистров загрузки и с пятым управляющим входом блока выходных регистров, информационный выход которого подключен к информационному выходу устройства, третий управляющий вход которого соединен с пятым управляющим входом блока входных регистров, шестой управляющий вход которого подключен к пятому управляющему входу блока регистров загрузки, шестому управляющему входу блока выходных регистров и четвертому управляющему выходу исполнительного блока, пятый управляющий выход которого соединен с седьмым управляющим входом блока выходных регистров.

Сущность изобретения заключается в том, то введение блока обработки фрагментов и организации соответствующих связей обеспечивает повышение производительности устройства при обработке основных программ за счет повышения темпа обмена ассоциативной памяти определяемого снижениями ее рабочего объема.

При этом обеспечивается управление процессом вычислений от потока данных для основного объема рабочих программ.

В рабочих программах производится выделение фрагментов, имеющих выраженный локальный характер вычислений и обладающих слабым параллелизмом. Сюда же относятся фрагменты, имеющие характер тригонометрических или иных функций, не связанные напрямую с другими аналогичными фрагментами.

Вычисление указанных фрагментов производится без участия ассоциативной памяти.

Сравнение предлагаемого устройства с прототипом позволяет утверждать о соответствии критерию "новизна", а отсутствие отличительных признаков в аналогах - говорит о соответствии критерию "изобретательский уровень".

Предварительные испытания подтверждают возможность промышленного применения.

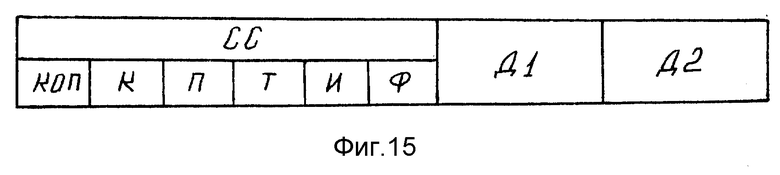

На фиг.1 представлена блок-схема вычислительной машины;

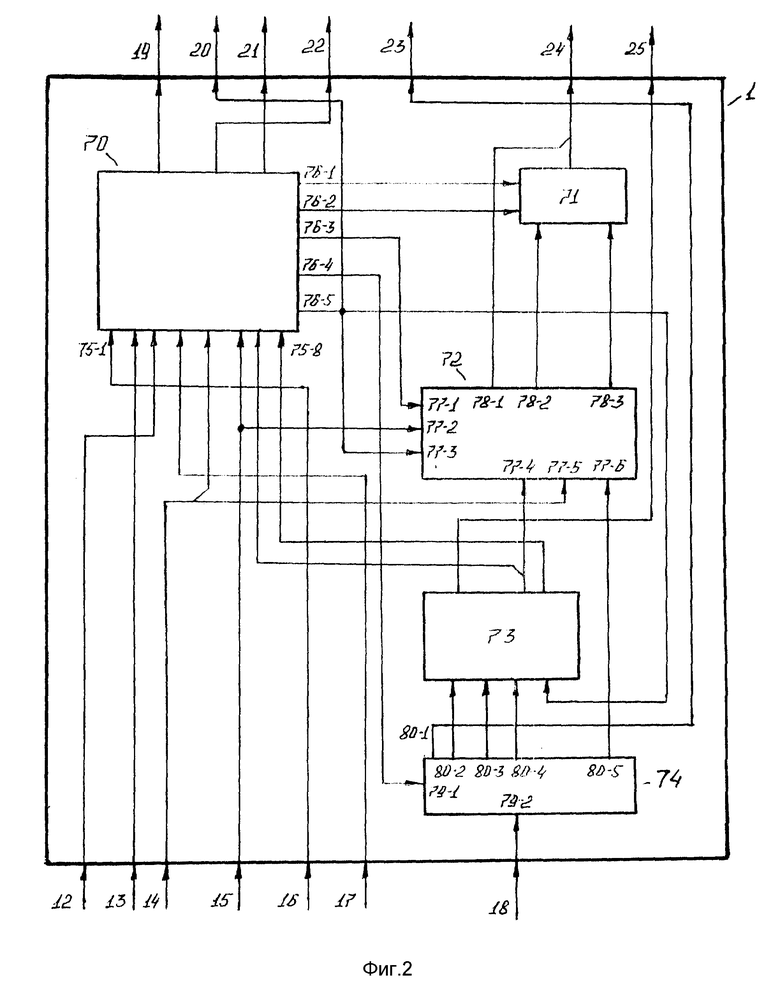

на фиг.2 - функциональная схема процессора;

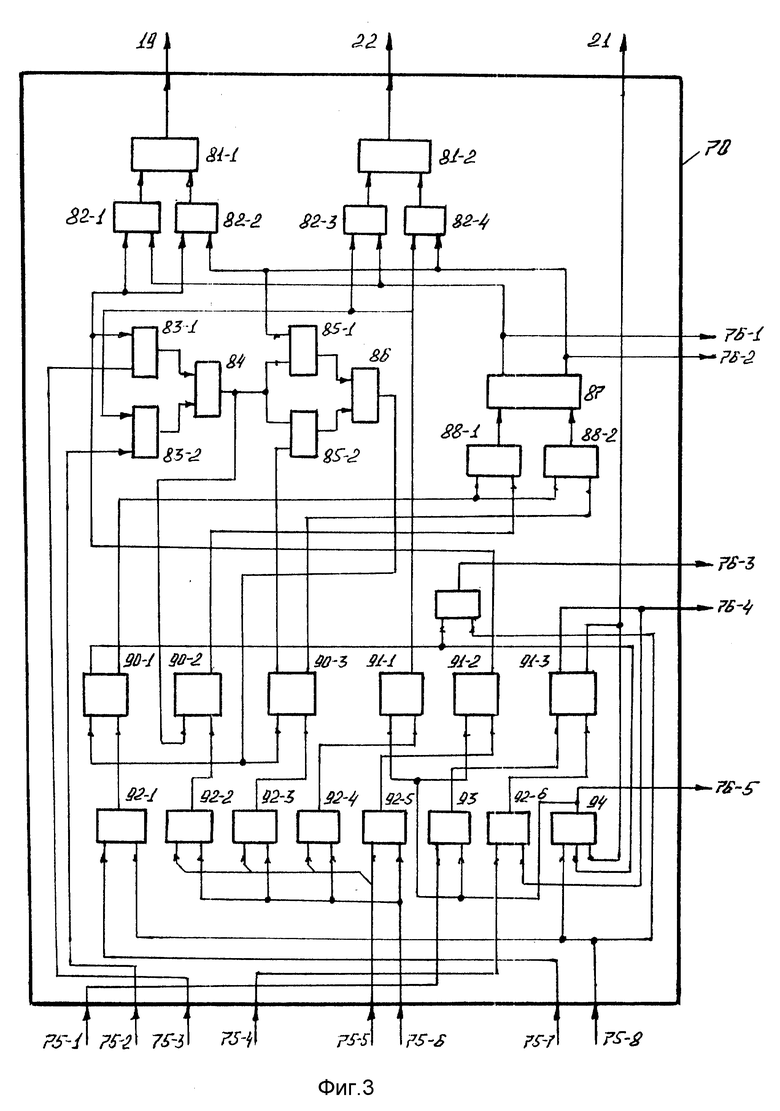

на фиг.3 - функциональная схема узла управления процессора;

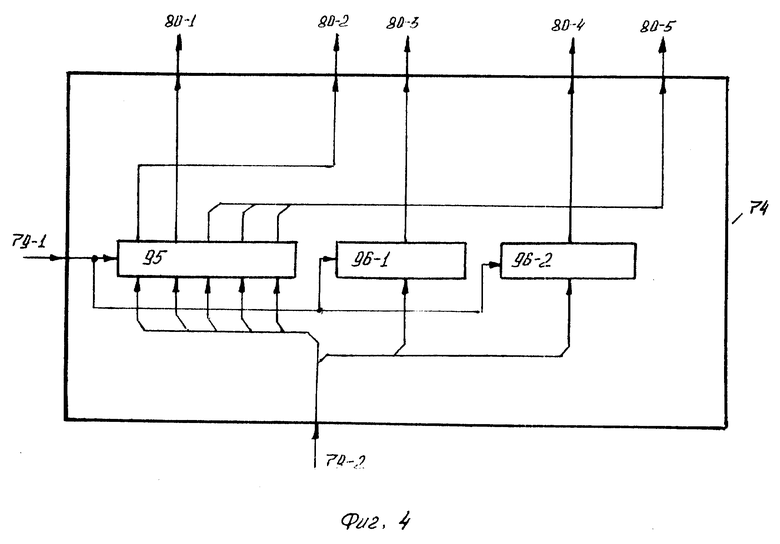

на фиг.4 - функциональная схема узла входных регистров процессора;

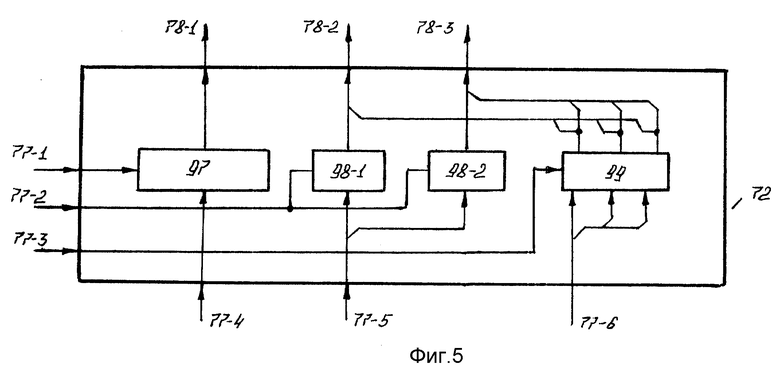

на фиг.5 - функциональная схема узла выходных регистров процессора;

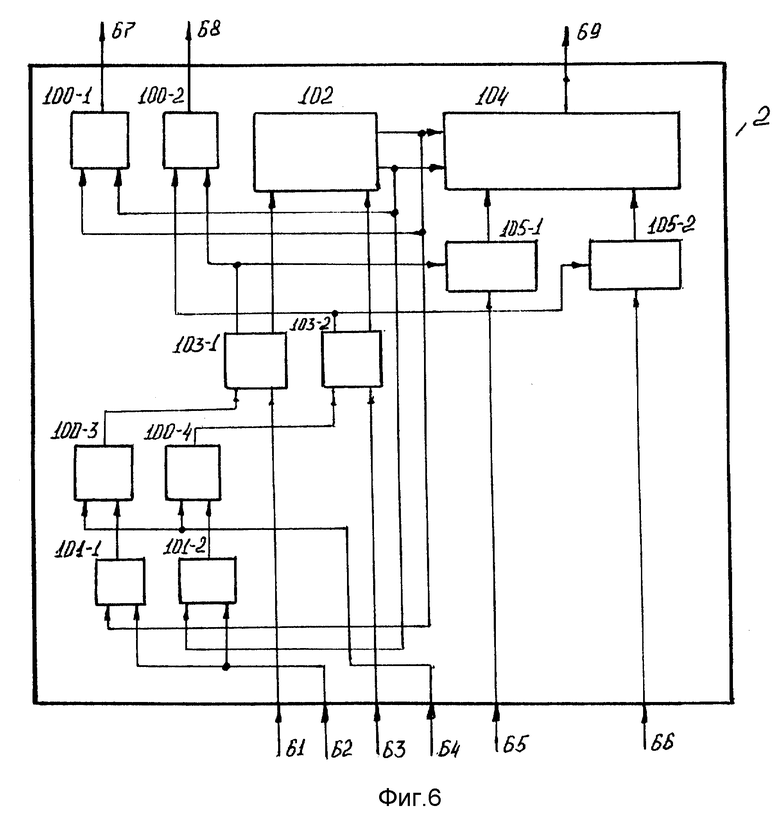

на фиг.6 - функциональная схема коммутатора ввода-вывода;

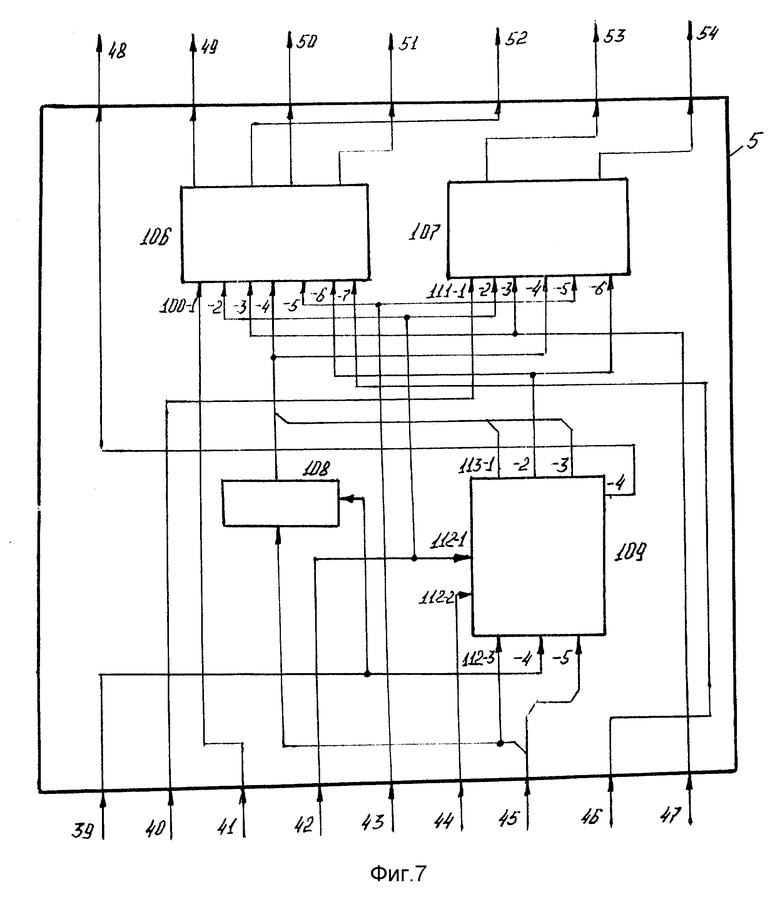

на фиг.7 - функциональная схема устройства выборки данных вычислительной машины;

на фиг.8 - функциональная схема буфера устройства выборки данных;

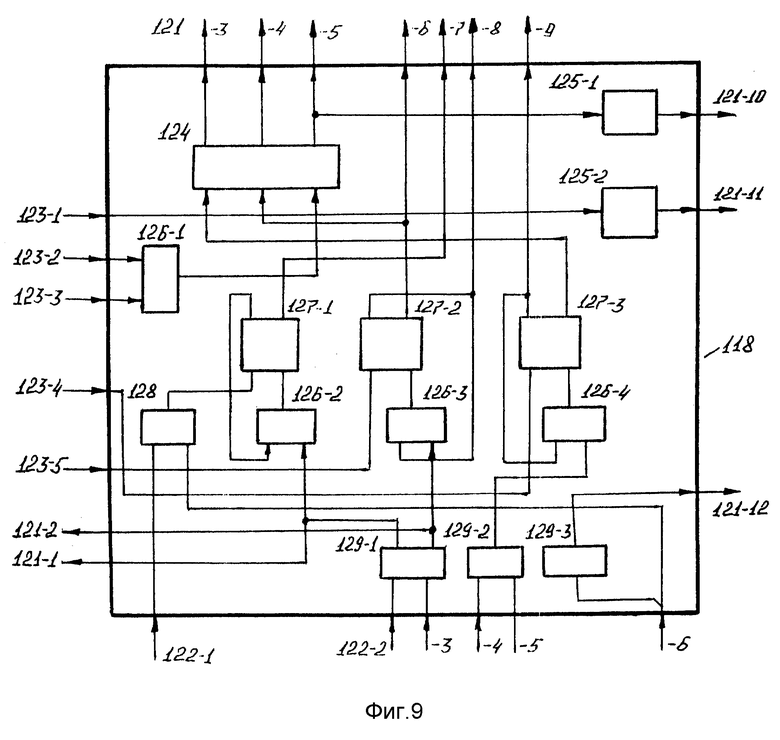

на фиг.9 - функциональная схема узла управления буфером;

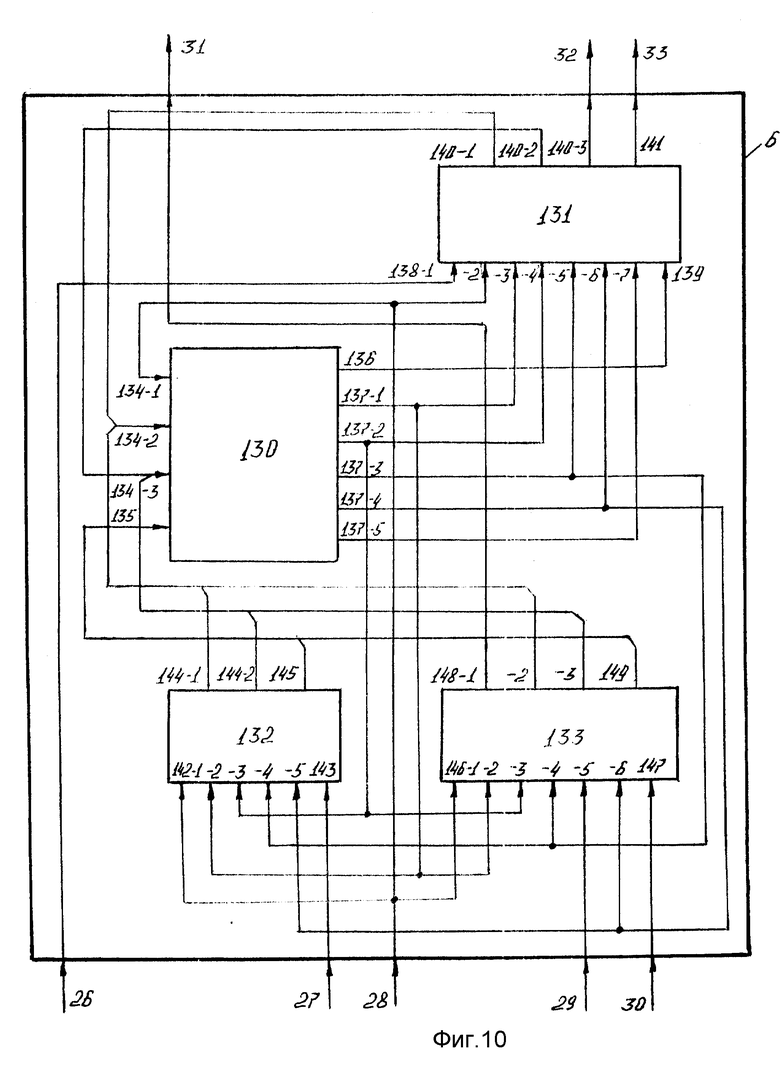

на фиг.10 - функциональная схема устройства обработки фрагментов программ;

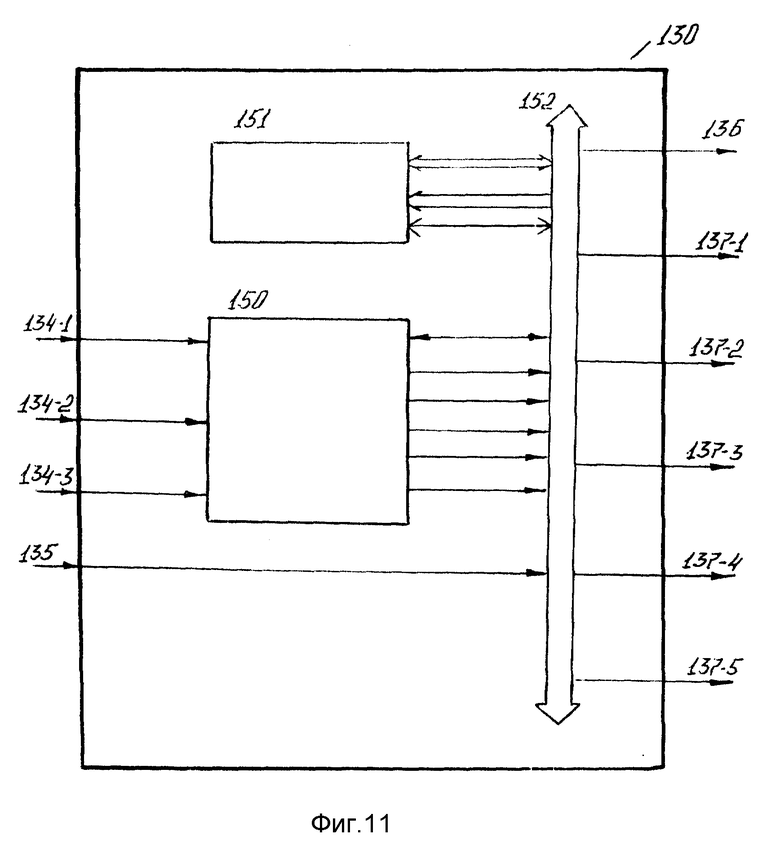

на фиг.11 - функциональная схема исполнительного блока;

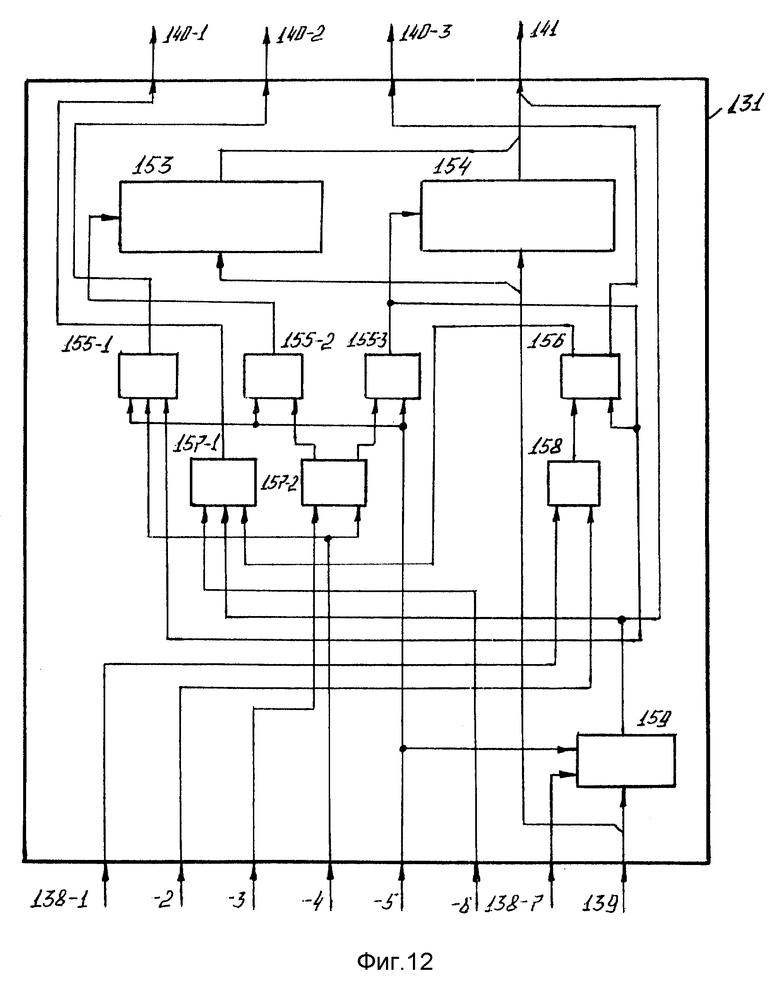

на фиг.12 - функциональная схема узла выходных регистров;

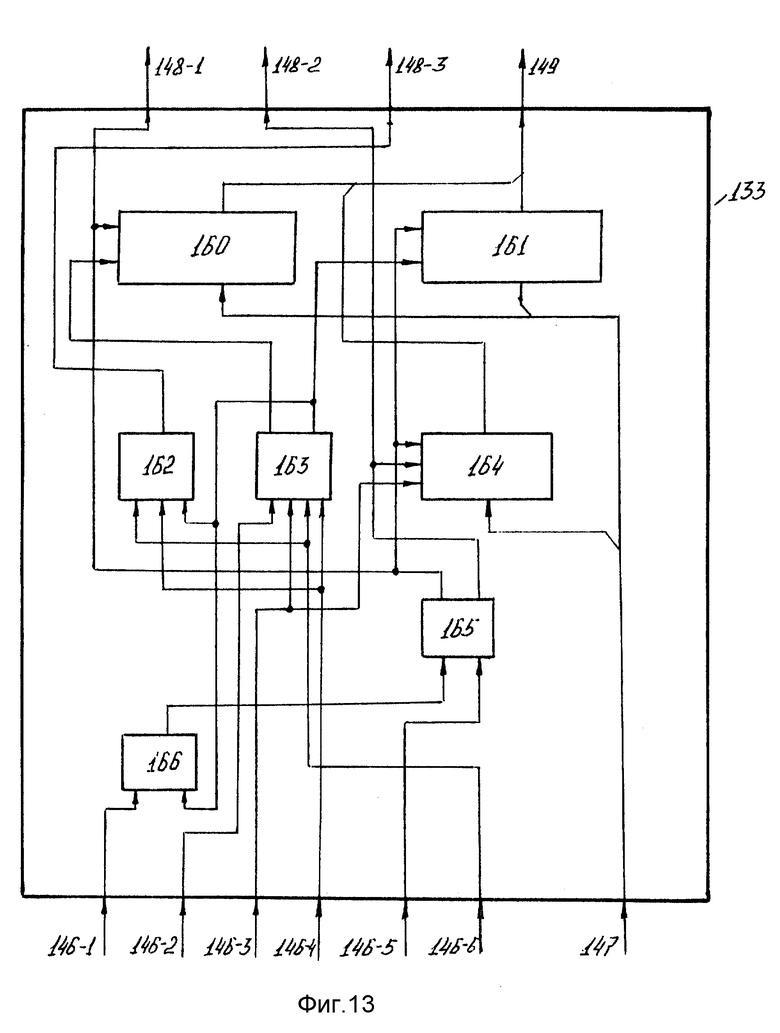

на фиг.13 - функциональная схема узла входных регистров;

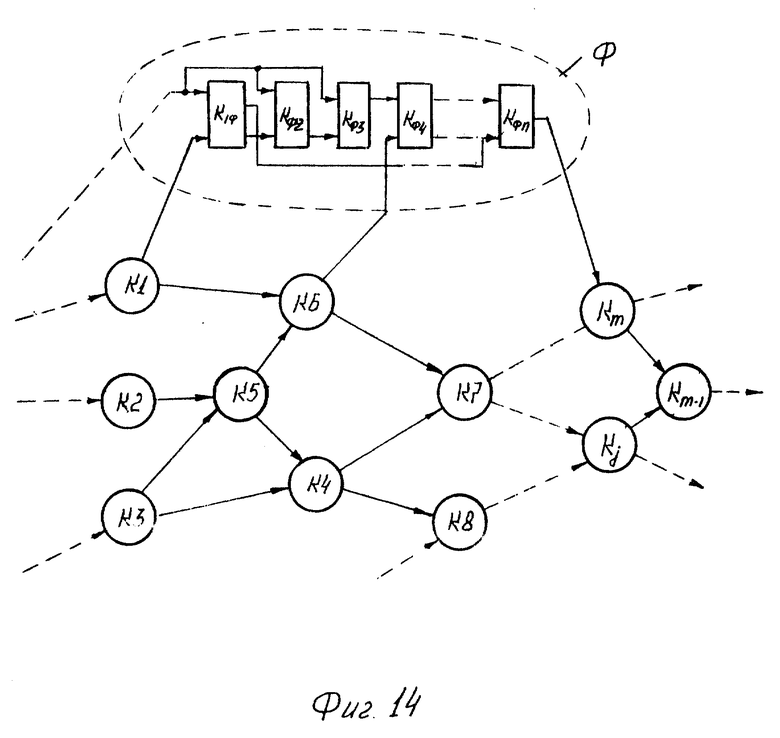

на фиг.14 - общий вид графа вычислений;

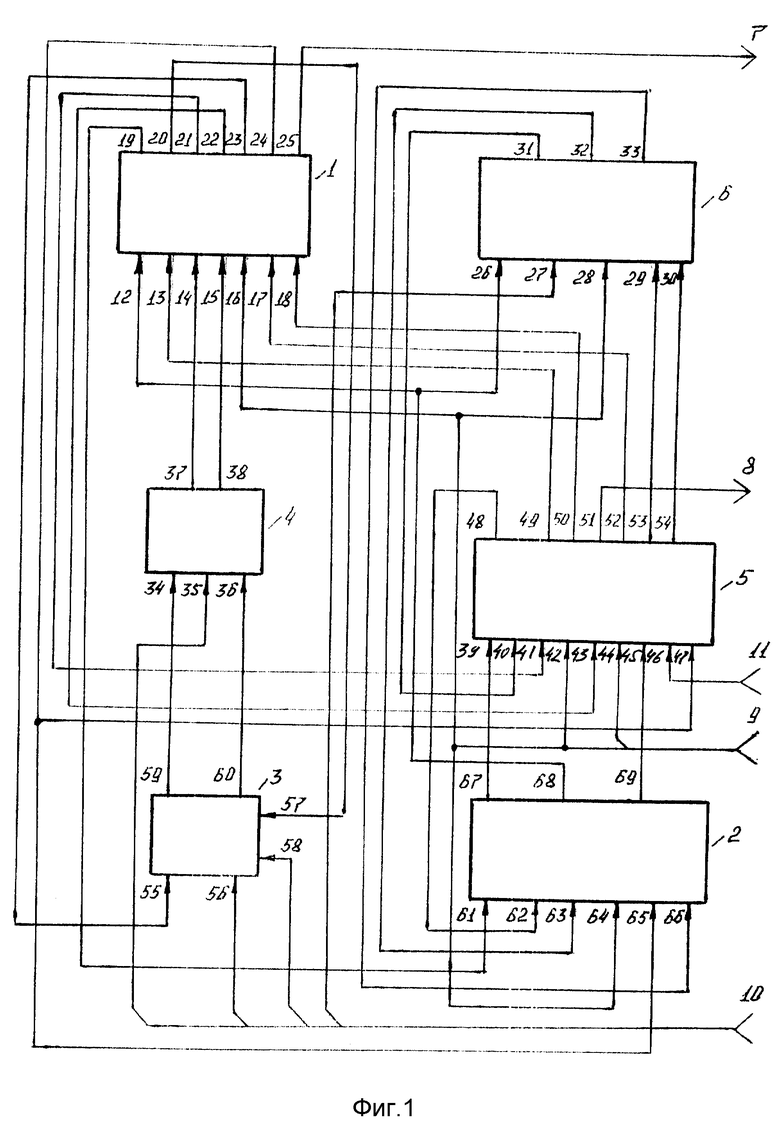

на фиг.15 - структура информационного пакета.

Вычислительная машина (фиг. 1) содержит процессор 1, коммутатор 2 ввода-вывода, коммутатор 3 загрузки команд, память 4 команд, устройство 5 выборки данных и устройство 6 обработки фрагментов программ.

Кроме того, вычислительная машина содержит первый и второй информационные выходы 7 т 8, вход 9 обнуления и первый и второй информационные входы 10 и 11. соответственно.

Процессор 1 содержит первый и второй управляющие входы 12 и 13, первый информационный вход 14, третий, четвертый и пятый управляющие входы 15, 16 и 17, второй информационный вход 18, первый, второй, третий и четвертый управляющие выходы 19, 20, 21 и 22 и с первого по третий информационные выходы 23, 24 и 25 соответственно.

Устройство 6 обработки фрагментов программ содержит первый управляющий вход 26, первый информационный вход 27, второй и третий управляющие входы 28 и 29, второй информационный вход 30, первый и второй управляющие выходы 31 и 32 и информационный выход 33.

Память 4 команд содержит управляющий вход 34, информационный вход 35, адресный вход 36, информационный выход 37 и управляющий выход 38.

Устройство 5 выборки данных содержит с первого по пятый управляющие входы 39...43, вход 44 обнуления, с первого по третий информационные входы 45.. . 47, первый и второй управляющие выходы 48 и 49, первый и второй информационные выходы 50 и 51, третий и четвертый управляющие выходы 52 и 53 и третий информационный выход 54.

Коммутатор 3 загрузки команд содержит первый и второй информационные входы 55 и 56, первый и второй управляющие входы 57 и 58, управляющий выход 59 и информационный выход 60.

Коммутатор 2 ввода-вывода содержит с первого по четвертый управляющие входы 61...64, первый и второй информационные входы 65 и 66, первый и второй управляющие выходы 67 и 68 соответственно и информационный выход 69.

Процессор 1 (фиг. 2) содержит узел 70 управления, коммутатор 71, узел 72 выходных регистров, арифметико-логическое устройство 73 и узел 74 входных регистров.

Узел 70 управления содержит вход 75-1 установки нуля, первый и второй входы 75-2 и 75-3 управления передачей результата, вход 75-4 управления пуском, вход 75-5 разрядов типа команды, вход 75-6 сигнала готовности памяти, выход 75-7 сигнала значимости данных, выход 75-8 сигнала готовности, первый и второй выход 76-1 и 76-2 управления коммутацией выхода, выход 76-3 управления передачей, выход 76-4 управления приемом, выход 76-5 управления пуском, первый, второй и третий управляющие выходы, подключенные к выходам 19, 20 и 21 процессора 1.

Узел 72 выходных регистров содержит управляющие входы 77-1...77-3, информационные входы 77-4...77-6 и информационные выходы 78-1...78-3 соответственно.

Коммутатор 71 содержит информационный выход, подключенный к выходу 24 процессора 1, первый и второй управляющие входы, подключенные к выходам 76-1 и 76-2 узла 70 управления, первый и второй информационные входы, подключенные к выходам 78-2 и 78-3 узда 72 выходных регистров.

Узел 74 входных регистров содержит управляющий и информационный входы 79-1 и 79-2 и информационные выходы 80-1...80-5.

Арифметико-лигическое устройство 73 (выполнено аналогично устройству по авт. св. N 1367012, кл. G 06 F 7/36 от 1985 г.) содержит вход управления операциями, первый и второй входы операндов, подключенные, соответственно, к выходам 80-2, 80-3 и 80-4 узла 74 входных регистров, вход управления пуском, подключенный к выходу 76-6 узла 70 управления, первый информационный выход, подключенный к выходу 25 процессора 1, второй информационный выход, подключенный ко входу 75-7 узла 70 управления и входу 77-4 узла 72 выходных регистров, и управляющий выход, подключенный ко входу 75-8 узла 70 управления.

В состав узла 70 управления (фиг. 3) входят элементы ИЛИ 81-1, 81-2 элементы И 82-1...82-4, 83-1, 83-2, элемент ИЛИ 84, элементы И 85-1, 85-2, элемент ИЛИ 86, приоритетный шифратор 87, элементы И 88-1, 88-2 и 89, триггеры 90-1. ..90-3, 91-1...91-3, элементы И 92-2...92-6, элемент ИЛИ 93, элемент И 94.

В состав узла 74 входных (фиг. 4) регистров входят регистр 95 слова состояний и регистры 96-1, 92-2 первого и второго операндов соответственно.

В состав узла 72 выходных регистров (фиг. 2) входят регистр 97 результата, первый и второй регистры 98-1, 98-2 номера команды и регистр 99 признака состояний.

В состав коммутатора 2 ввода-вывода (фиг. 6) входят элементы ИЛИ 100-1.. .100-4, элементы И 101-1...101-2, приоритетный шифратор 102, триггеры 103-1, 103-2, узел 104 коммутации, входные регистры 105-1, 105-2.

Узел 104 может быть выполнен на элементах 2И-НЕ.

Устройство 5 выборки данных (фиг. 7) содержит первый и второй буферы 106 и 107, регистр 108, ассоциативную память 109.

Первый буфер 106 содержит первый и второй управляющие входы 110-1 и 110-2, первый и второй информационные входы 110-3 и 110-4, третий и четвертый управляющие входы 110-5 и 110-6, вход 110-7 внешнего обмена, первый и второй выходы управления передачей, подключенные соответственно к выходам 49 и 52 устройства 5, информационный выход, подключенный к выходу 50 устройства 5, и выход внешнего обмена, подключенный к выходу 51 устройства 5.

Второй буфер 107 содержит первый и второй управляющие выходы 111-1 и 111-2, первый и второй информационные входы 11-3 и 111-4, третий и четвертый управляющие входы 111-5 и 11-6, управляющий и информационный выходы, подключенные соответственно к выходам 53 и 54 устройства 5.

Ассоциативная память 109 выполнена аналогично устройству по патенту РФ N 2035069, G 11 C 13/04, от 10.05.1995 г. и содержит первый и второй управляющие входы 112-1 и 112-2, первый информационный вход 112-3, третий управляющий вход 112-4, второй информационный вход 112-5, первый информационный выход 113-1, первый управляющий выход 113-2, второй информационный выход 113-3 и второй управляющий выход 113-4.

Первый буфер 106 (фиг. 8) содержит элементы ИЛИ 114-1...114-5, выходной коммутатор 115, элементы И 116-1...116-4, узел 117 хранящих регистров, узел 118 управления, входной коммутатор 119, первый и второй входные регистры 120-1 и 120-2.

Второй буфер выполнен аналогично первому.

Узел 118 управления содержит управляющие выходы 121-1...121-12, вход 122-1 установки, первый вход 122-2 кода пакета, первый вход 122-3 управления приемом, второй вход 122-4 кода пакета, второй и третий входы 122-5 и 122-6 управления приемом и с первого по пятый управляющие входы 123-1...123-5 соответственно.

В состав узла 118 управления (фиг. 9) входят приоритетный шифратор 124. счетчики 125-1. . . 125-2, логические элементы ИЛИ 126-1...126-4, триггера 127-1...127-3, элемент ИЛИ 128 и дешифраторы 129-1...129-3.

Устройство 6 обработки фрагментов программ (фиг. 10) содержит исполнительный блок 130, блок 131 выходных регистров, блок 132 регистров загрузки и блок 133 входных регистров.

Исполнительный блок 130 содержит с первого по третий управляющие входы 134-1. ..134-3, информационный вход 135, информационный выход 136, с первого по пятый управляющие выходы 137-1...137-5.

Блок 131 входных регистров содержит с первого по седьмой управляющие входы 138-1. ..138-7, информационный вход 139, с первого по третий управляющий выходы 140-1...140-3 и информационный выход 141.

Блок 132 регистров загрузки содержит с первого по пятый управляющие входы 142-1. ..142-5, информационный вход 143, первый и второй управляющие выходы 144-1 и 144-2 и информационный выход 145.

Блок 133 входных регистров содержит с первого по шестой управляющие входы 146-1. ..146-6, информационный вход 147, с первого по третий управляющие выходы 148-1...148-3 и информационный выход 149.

В состав исполнительного блока 130 (фиг. 1) входят микропроцессор 150, оперативная память 151 и шина 152 обмена. В качестве указанных узлов может быть использован стандартный микропроцессорный набор, например, на базе элементов типа Интел 80386.

Блок 131 выходных регистров (фиг. 12) содержит первый и второй регистры 153 и 154, элементы ИЛИ 155-1. ..155-3, триггер 156, дешифраторы 157-1, 157-2, элемент ИЛИ 158 и регистр 159.

Блок 133 входных регистров (фиг. 13) содержит регистры 160, 161, элемент И 162, дешифратор 163, регистр 164, триггера 165 и элемент ИЛИ 166.

Блок 132 регистров загрузки имеет аналогичную структуру.

Работа устройства.

Принципы организации вычислений с управлением от потока данных предполагают, что алгоритм решения задачи представляется в виде графа вычислительного процесса, состоящего из операторов (команд) над данными (операндами) и указателей (направлений), по которым данные (результаты) перемещаются от команды к команде (см. фиг. 14).

Обработка данных в соответствии с порядком, определяемым графом, ведется по мере того, как на входах команд образуются готовые к обработке данные. Поиск готовых подданных, относящихся к конкретной команде, производится в памяти объединений, реализованной на базе ассоциативной памяти 109, которая осуществляет поиск по ключу. Ключом, как правило, является код, состоящий из разрядов номера команды, индекса, итерации и т.п.

Каждая команда имеет номер К-1, который может быть использован для размещения ее в памяти 4 команд, код операции - КОП-1 и "адрес назначения" в виде номера К-j-той команды, к которой будет относится полученный результат обработки.

Кроме того, команда имеет признаки, определяющие условия ее обработки или ее тип. Команда может быть двухвходовой или одновходовой, в зависимости от того, над сколькими операндами (одним или двумя) производятся действия, определяемые кодом операции. Команда может быть двухадресной или одноадресной, в зависимости от того, по скольким направлениям (на вход скольких команд) передается результат ее исполнения (например, команда К1 является одновходовой двухадресной, команда К2 одновходовой одноадресной (фиг. 14).

Для организации процесса обработки графа используется соответствующая структура представления команд и данных в виде информационных объектов, состоящих их многоразрядных слов, где соответствующие группы разрядов образуют поля с необходимым функциональным назначением (фиг. 15).

В общем случае на вход обрабатывающего устройства - процессора 1 информации поступает в виде пакета данных, включающего слово состояний (команду) и два слова. При этом пакет одновходовой команды содержит только одно слово данных.

Слово состояний включает следующие базовые группы функциональных разрядов (поля):

КОП - код операции:

К - номер команды;

П - номер поколения;

Т - номер итерации;

И - индекс;

Ф - номер фрагмента.

Функциональные поля слова состояний, представляющие служебную информацию, могут использоваться по-разному. В частности, ключевая группа разрядов для поиска данных в ассоциативной памяти 109 определяется полями К, П, И. При поиске входных данных фрагмента к ним добавляется поле Ф. В состав поля КОП могут входить разряды, указывающие на тип команды (одноадресная, двухадресная, одновходовая, двухвходовая).

Если команда имеет два выхода, то результату ее обработки будут соответствовать два слова состояний, что соответствует двум направлениям его передачи.

Разрядные группы слова состояний хранятся в памяти 4 команд.

Команды и данные, входящие в состав выделяемых фрагментов (фиг. 14), хранятся в оперативной памяти 151 соответствующего обрабатывающего устройства - исполнительного блока 130 и не занимают объем ассоциативной памяти 109.

Входы синхронизации всех узлов вычислительной машины подключены к внешнему входу синхронизации (на фиг. 1 не показано).

Вычислительная машина (фиг. 1) обеспечивает выполнение основных рабочих программ и выделенных программных фрагментов, загружаемых по первому информационному входу 10, и выдает результаты обработки по второму информационному выходу 8.

Машина реализует вычислительный процесс, управляемый от потока данных, на основной программе, и процесс обработки данных по принципу фон Немана на выделенных фрагментах. При этом в память 4 команд помещаются все команды основной исполняемой программы, а в оперативную память 151 (фиг. 11) помещаются команды и данные ответствующих фрагментов.

Инициализация вычислений осуществляется подачей на второй информационный вход 11 стартовых пакетов операндов от внешней (на фиг. 1 не показано) системы.

Стартовые пакеты вместе с соответствующими управляющими сигналами поступают на второй информационный вход 46 устройства выборки данных и далее на вход 110-7 внешнего обмена буфера 106, откуда они подаются на четвертый информационный вход коммутатора 115. При этом управление коммутацией осуществляется по его четвертому управляющему входу, куда через элемент И 116-4 поступает соответствующий сигнал с управляющего выхода 121 -12 узла 118 управления. Указанный сигнал управления формируется на выходе дешифратора 129-3, на вход которого поступает кодовая группа разрядов, определяющая тип стартового пакета.

Разряды пакета поступают с выхода 50 буфера 106 через соответствующий выход устройства 5 выборки данных на второй информационный вход 18 процессора 1.

Информация на выходе 50 устройства 5 выборки данных сопровождается стробом передачи на выходе 52, который является управляющим сигналом запуска процессора 1 и поступает на его пятый управляющий вход 17.

При этом строб передачи поступает на вход 75-4 узла 70 управления, а разряды пакета операндов - на информационный вход 79-2 узла 74 входных регистров.

Прием функциональных полей пакета операндов на регистр 95 слова состояний и регистры 96-1 и 96-2 операндов производится по сигналу управления приемом на входе 79-1 узла 74 входных регистров, с выхода 80-1 которого разряды номера команды через первый информационный выход 23 процессора 1 поступают на первый информационный вход 55 коммутатора 3 загрузки команд, на первый управляющий вход 57 которого поступает управляющий сигнал со второго управляющего выхода 20 процессора 1. При этом на управляющем и информационном выходах 59 и 60 коммутатора 3 соответственно формируются управляющий сигнал, соответствующий коду чтения, и информационный, соответствующий адресу, которые поступают на соответствующие управляющий и адресный входы памяти 4 команд.

Разряды кода операций и разряды операндов с выходов 80-2 и 80-3, 80-4 узла 74 выходных регистров, сопровождаемые сигналом управления пуском с выхода 76-5 узла 70 управления, поступают на соответствующие входы арифметико-логического устройства 73, а разряды функциональных полей П, Т, И - на вход 77-6 узла 72 выходных регистров, на вход 77-5 которого через вход 14 процессора 1 поступают разряды функциональных полей с информационного выхода 37 памяти 4 команд, содержащие код операций и номер команды, для которой предназначен результат вычислений, в свою очередь поступающий на вход 77-4 узла 72.

При этом на входы 77-1...77-3 узла 72 выходных регистров поступают соответствующие сигналы, реализующие управление приемом результата на регистр 97, разрядных полей К и КОП очередной команды на регистры 98-1 и 98-2 и разрядных полей П, Т, И на регистр 99, а на выходах 78-1...78-3 узла 72 формируются функциональные поля результата обработки текущей команды (полупакета), отражающие принцип вычислений, представляемый графом вычислительного процесса, которые поступают соответственно на выход 24 процессора 1 и на информационные входы коммутатора 71, на управляющие входы которого поступают сигналы управления с выходов 76-1, 76-2 узла 70 управления.

Функции коммутатора 71 определяются условием наличия двухадресных команд, т.е. команд, результат обработки которых служит входным операндом для двух следующих команд (имеющих различные номера и различные коды операций).

Это условие реализуется наличием двух выходных регистров 98-1 и 98-2 номера команды, содержимое которых последовательно передается через коммутатор 71, сопровождая результат на выходе 24 процессора 1.

Сигналы управления выходным коммутатором 71 формируются при поступлении на выходы 75-5 и 75-6 узла 70 управления функциональных полей типа команды и строба передачи соответственно с информационного и управляющего выходов 37 и 38 памяти 4 команд через входы 14 и 15 процессора 1, а на вход 75-7 - при поступлении сигнала значимости результата с информационного выхода арифметико-логического устройства 73.

Функциональные поля типа команды включают признаки: 1А (одноадресная команда), 2А (двухадресная команда) и 2В (двухвходовая команда), которые поступают на триггеры 92-2...92-5, с учетом состояния которых происходит формирование управляющих сигналов на выходах 76-1 и 76-2 узла управления. При этом на выходах 22 и 19 процессора 1 формируются стробы передачи, соответствующие режимам одно- или двухвходовых команд, а на выходе 24 - разряды функциональных полей полупакета.

Если при этом выполняются условия одновходовой команды и результат на выходе процессора не требует поиска пары в ассоциативной памяти 109, то разряды полупакета и строб передачи с выходов 24 и 22 процессора 1 поступают соответственно на входы 47 и 43 узла 5 выборки данных и на входы 110-3 и 110-5 буфера 106. Поступивший на вход 110-3 результат принимается на первый входной регистр 120-1 и через первый информационный выход входного коммутатора 119 передается на первый информационный вход коммутатора 115. Второй информационный выход коммутатора 119 используется для передачи результатов вычислений на внешнюю управляющую систему. При этом соответствующий управляющий сигнал формируется на первом выходе дешифратора 129-1 узла 118 управления. На вход дешифратора 129-1 поступают разряды кода, определяющего тип полупакета, а информация со второго информационного выхода коммутатора 119, вместе со стробом передачи с выхода 121-7 узла 118 управления поступает на выход 51 буфера 106 и через соответствующий выход устройства 5 выборки данных передается на второй информационный выход 8 вычислительной машины.

В случае, когда результат (операнд) на выходе 24 процессора 1 относится к двухвходовой команде, поиск парного операнда осуществляется ассоциативной памятью 109 (входит в состав устройства 5 выборки данных), доступ к которому осуществляется через коммутатор 2 ввода-вывода.

При этом на первые управляющий и информационный входы 61 и 65 коммутатора 2 ввода-вывода поступает сигнал строба передачи и разряды функциональных поле полупакета с выходов 19 и 24 процессора 1 соответственно.

Входной полупакет со входа 65 коммутатора 2 поступает через регистр 105-1 на первый информационный вход узла коммутации 104. Строб передачи со входа 61 коммутатора 2 поступает на вход установки триггера 103-1, выход которого подключен к первому управляющему входу приоритетного шифратора 102, на первом и втором управляющих выходах которого формируется код управления узлом коммутации 104, в результате чего на выход 69 коммутатора 2 передаются разряды функциональных полей полупакета со входа 65. При этом на выходе 67 формируется соответствующий управляющий сигнал - строб передачи.

Разряды функциональных полей и строб передачи с выходов 69 и 67 коммутатора 2 поступают на входы 45 и 39 устройства 5 выборки данных, при этом разрядное поле слова состояния (в качестве ключа ассоциативного поиска), разрядное поле операнда и строб передачи доступа - соответственно на входы 112-3, 112-5 и 112-4 ассоциативной памяти 109.

Разрядное поле слова состояний, кроме того, поступает на информационный вход регистра 108. на управляющий вход которого поступает строб передачи со входа 39 устройства 5 выборки данных.

Полупакет, которому не находится пары, остается в памяти 109. При наличии же там соответствующего парного операнда на выходах 113-1 и 113-3 формируются разрядные поля первого и второго операндов, которые вместе с разрядным полем слова состояний с выхода регистра 108 поступают на вторые информационные входы 110-4 и 111-4 буферов 106 и 107 соответственно. Строб передачи с выхода 113-2 ассоциативной памяти 109 поступает на выходы 110-6 и 111-6 указанных буферов.

При этом, если поступивший пакет является пакетом операндов основной программы, то разряды его функциональных полей принимаются на регистр 120-2 буфера 106, а соответствующий сигнал управления приемом формируется на выходе 121-9 узла 118 управления.

С выхода регистра 120-2 разрядные поля пакета поступают на второй информационный вход коммутатора 115, на соответствующий управляющий вход которого поступает сигнал управления коммутацией с выхода элемента И 116-1, который, кроме того, передается вместе с разрядными полями на первый выход коммутатора 115, выполняя функцию строба передачи, который окончательно формируется на выходе элемента ИЛИ 114-1.

При этом, если свободен узел 74 выходных регистров процессора 1, то вся информация с выхода коммутатора 115 буфера 106 предается в процессор 1, и повторяется очередной цикл обработки.

В том случае, когда занят узел 74 процессора 1, на вход 110-1 буфера 106 поступает сигнал блокировки передачи с выхода 21 процессора через вход 41 устройства 5 выборки данных, откуда передается на вход 123-2 узла 118 управления и вход элемента ИЛИ 114-5, на выходе которого формируется сигнал управления, поступающий на пятый управляющий вход коммутатора 115. При этом информация со второго информационного входа коммутатора 115 поступает на его второй выход, откуда передается на вход узла 117 хранящих регистров, сопровождаемая сигналом записи с выхода 121-11 узла 118 управления. Запись информации будет производиться в узел 117 для снятия сигнала блокировки на выходе 21 процессора 1. В случае снятия этого сигнала и при отсутствии информации на регистрах 120-1, 120-2 и на четвертом информационном выходе коммутатора 115, производится передача разрядов пакета из узла 117 через третий информационный вход коммутатора 115 и соответствующий выход буфера 106 и выход 50 устройства 5 выборки данных на вход 18 процессора 1.

Если сформированный на выходе регистра 108 и выходах 113-1, 113-3 ассоциативной памяти 109 пакет является стартовым пакетом локальной части программы, определяемой фрагментом Ф, то разряды его функциональных полей принимаются на буфер 107.

Во всем остальном работа по передаче стартового пакета фрагмента Ф на вход 30 устройства 6 обработки фрагментов программ производится аналогично изложенной выше передаче пакета операндов через буфер 106.

Разряды функциональных полей стартового пакета фрагмента и строб передачи, сформированные соответственно на выходах 54 и 53 устройства 5 выборки данных, поступают соответственно на входы 30 и 29 устройства 6 обработки фрагментов программ. При этом в отличие от процессора 1, где после обработки каждого пакета производится обращение в ассоциативную память 109, в устройстве 6 обработки фрагментов осуществляется полная обработка выделенной части (частей) основной программы и в ассоциативную память 109 передается лишь конечный результат.

Загрузка программ (соответствующих принципу обработки по фон Нейману) осуществляется при начальной загрузке машины через первый информационный вход 10.

При этом и команды, и данные поступают на вход 27 устройства 6, откуда передаются на вход 143 блока 132 регистров загрузки.

При этом разряды функциональных полей команд (соответствующих системе команд исполнительного блока 130) и данных поступают с выхода 145 блока 132 на информационный вход 153 блока 130, сопровождаемые сигналами прерывания и готовности с выходов 144-1 и 144-2, поступающих соответственно на входы 134-2 и 134-3 блока 130.

Через шину обмена 152 под управлением микропроцессора 150 осуществляется загрузка команд и данных фрагментов рабочих программ в оперативную память 151.

При поступлении на вход 147 блока 133 стартового пакета фрагмента, а на вход 146-5 соответствующего строба передачи осуществляется прием операндов на регисторы 160 и 161, а поля Ф слова состояний - на регистр 164. При наличии на входе 146-5 строба передачи производится установка триггера 165, и на выходе 148-2 формируется сигнал прерывания, который поступает на вход 134-2 блока 130 вместе с разрядным полем, поступающим с выхода регистра 164 по сигналу "чтение" с выхода триггера 165 через выход 149 блока 133 на информационный вход 135 блока 130. Микропроцессор 150 "опознает" разрядное поле, переданное на шину 152 обмена с выхода 135 блока 130 и выдает группу сигналов управления на выходы 137-1, 137-2, 137-3 и 137-4, которые передаются на входы 146-2, 143-3, 146-4 и 146-6 блока 133, где формируются соответствующие сигналы последовательного чтения и передачи данных из регистров 160 и 161 через выход 149 на информационный вход 135 блока 130. При этом микропроцессор 150 в соответствии с номерами и параметрами фрагмента Ф запускает соответствующую программу обработки, окончание которой сопровождается прерыванием микропроцессора 150. По этому прерыванию микропроцессор 150 формирует "вектор выхода", соответствующий текущему номеру, присвоенному регистру 159 блока 131, который в сопровождении управляющего сигнала с выхода 137-5 блока 130, поступающего на вход 138-7 блока 131, через шину обмена 152 и выход 136 блока 130 передается на вход 139 блока 131. Осуществляется запись информации в регистр 159, откуда она передается на вход дешифратора 157-1, на выходе которого формируется сигнал прерывания и через вывод 140-1 передается на вход 134-2 блока 130. По сигналу прерывания микропроцессор 150 формирует группу управляющих сигналов, которые передаются через выходы 137-1... 137-4 блока 130 на выходы 138-3...138-6 блока 131, в результате чего осуществляется прием разрядных полей результата обработки фрагмента Ф на входы регистров 153 и 154 через вход 139 блока 131 выхода 136 блока 130.

При этом формат данных на регистрах 153 и 154 соответствует плупакету результата при обработке команд в процессоре 1.

На выходе 140-3 блока 131 формируется строб передачи, поступающий на выход 32 устройства 6 обработки фрагментов программ, откуда передается на вход 63 коммутатора 2, на вход 66 которого поступают разряды функциональных полей выходного полупакета фрагмента программы с выхода 33 устройства 6.

С выхода 69 коммутатора 2 разрядные поля полупакета поступают на вход устройства 5 выборки данных, в результате чего данные результата обработки фрагмента объединяются с общим полем рабочей программы.

Таким образом, введение в состав вычислительной машины устройства обработки фрагментов программ и организация соответствующих связей позволяют снизить количество данных, хранящихся в ассоциативной памяти.

Полученное в результате этого сокращение объема ассоциативной памяти позволяет поднять ее быстродействие и увеличить производительность вычислений при обработке основных рабочих программ с использованием управления вычислениями от потока данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1998 |

|

RU2148857C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1995 |

|

RU2110089C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

| СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ НА ОСНОВЕ ПОТОКА ДАННЫХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2005 |

|

RU2281546C1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| КОМПЬЮТЕР | 1998 |

|

RU2216033C2 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Реконфигурируемый вычислительный модуль | 2018 |

|

RU2686017C1 |

| Ассоциативный матричный процессор | 1981 |

|

SU1005065A1 |

Изобретение относится к области вычислительной техники, в частности к вычислительным системам, использующим управление процессом вычислений от потока данных, и может быть использовано в цифровых вычислительных системах высокой производительности. Техническим результатом является повышение производительности путем соответствующего снижения объема ассоциативной памяти за счет локального введения в процесс вычислений традиционного принципа обработки данных без нарушения общей концепции управления вычислениями от потока данных. Устройство содержит процессор, коммутатор ввода-вывода, коммутатор загрузки команд, память команд, устройство выборки данных, устройство обработки фрагментов программ. 1 з.п.ф-лы, 15 ил.

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

| US 46758016 A, 23.06.87 | |||

| Операционное устройство | 1985 |

|

SU1367012A1 |

| ОПТИЧЕСКОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2035069C1 |

Авторы

Даты

1999-05-10—Публикация

1997-08-06—Подача