Сведения о родственных заявках

Настоящая заявка является заявкой с частичным продолжением заявки США с серийным номером 09/102887, поданной 23 июня 1998 г.

Область техники, к которой относится изобретение

Данное изобретение относится в общем к программируемым элементам памяти и, в частности, к стираемым элементам памяти, которые нашли свое воплощение в таких прикладных задачах как хранение данных, многозначная логика и вычислительные операции в нейронных сетях/системах искусственного интеллекта, а также к способам и устройству для считывания, записи и программирования подобных элементов. Элементы памяти программируются путем подвода энергии любого одного или множества следующих видов: например, электрической, оптической, энергии давления и/или тепловой. В одном варианте осуществления изобретения информация может запоминаться в элементах памяти в зашифрованном виде, то есть может извлекаться только путем использования специально запрограммированных устройств и специальных способов. Таким образом, данное изобретение может быть использовано для хранения информации в зашифрованном или секретном формате. В другом варианте изобретение находит свое воплощение в системе нейронной сети.

Уровень техники

Основная концепция использования материалов с фазовыми переходами, в которых имеется возможность электрической записи и стирания (т. е. материалов, которые могут электрически переключаться из в основном аморфного состояния в основном в кристаллическое состояние и обратно), для систем электронной памяти хорошо известна специалистам в данной области техники, что раскрыто, например, в патенте США 3271591, выданном Овшинскому 6 сентября 1966 г. и патенте США 3530441, выданном Овшинскому (Ovshinsky) 22 сентября 1970 г., права на которые принадлежат правопреемнику настоящего изобретения и содержание которых включено сюда в качестве ссылки (далее - "патенты Овшинского").

Как раскрыто в патентах Овшинского, структурное состояние материалов с фазовыми переходами может изменяться, переходя из в основном амфорного состояния местного порядка в основном в кристаллическое состояние местного порядка и обратно, либо может быть установлено в одном из отличных друг от друга обнаруживаемых состояний местного порядка во всем спектре между полностью аморфным и полностью кристаллическим состояниями. Первые материалы, описанные в патентах Овшинского, могли находиться в одном из двух обнаруживаемых структурных состояний: в основном аморфном и в основном кристаллическом местного порядка, и переходить из одного в другое, обеспечивая запоминание и извлечение единичных бит закодированных двоичных данных, либо в этих материалах могут быть установлены промежуточные обнаруживаемые уровни местного порядка во всем спектре между полностью аморфным и полностью кристаллическим состояниями.

То есть в патентах Овшинского говорится, что электрическое переключение между полностью аморфным и полностью кристаллическим состояниями для указанных материалов не требуется, но, что во всем диапазоне местного порядка между полностью аморфным и полностью кристаллическим состояниями может быть на любом уровне установлена определенная обнаруживаемая характеристика, к примеру сопротивление. Эта характеристика изменяющегося местного порядка обеспечивает "серую шкалу", представляемую спектром между полностью аморфным и полностью кристаллическим состояниями. Указанная серая шкала может быть использована в качестве фактически неограниченного (бесконечного) переменного параметра, к примеру фактически неограниченного переменного сопротивления, изменяющегося от максимального до минимального уровней, либо может быть использована для установки значений приращений выбранного параметра, к примеру сопротивления на отдельных обнаруживаемых шагах между максимальным и минимальным уровнями.

Способность переменного параметра, такого как сопротивление, регулируемого во всем диапазоне серой шкалы, позволяет применять эти устройства, например, в нейронной сети и системах искусственного интеллекта, как описано в патентах Овшинского. При другом применении указанных устройств, как описано в патентах Овшинского, использование элемента памяти для установки ступенчато наращиваемых и избирательно обнаруживаемых уровней параметра может обеспечить запоминание в одном элементе памяти многобитовых данных.

Сущность изобретения

Настоящее изобретение относится к недавно открытым и совершенно неожиданным свойствам указанных материалов с фазовыми переходами и устройствам, позволяющим создавать универсальные элементы памяти, использующие указанные свойства, а также к способам и устройствам для программирования таких элементов памяти, и к системам запоминания данных, многозначной логики и нейронным сетям/искусственному интеллекту, где воплощаются указанные устройства с универсальными элементами памяти.

В одном варианте реализации изобретения указанные универсальные элементы памяти используются в виде и формате, при которых информация запоминается путем подачи одного или нескольких последовательных электрических импульсов выбранной амплитуды и длительности в элементы памяти, которые изначально установлены в состояние с высоким сопротивлением. Амплитуда и длительность каждого импульса выбираются таким образом, что подача одного начального импульса не способна вызвать переключение элемента памяти из состояния с высоким сопротивлением в состояние с низким сопротивлением. Однако амплитуда и длительность каждого импульса выбираются таким образом, что каждый импульс вызывает приращение, но на этом этапе структурное изменение в элементе памяти не может быть обнаружено. Эти уникально структурированные импульсы определяются здесь как "подинтервальные импульсы", а когда они подаются в определенной последовательности для записи и/или считывания, они называются "программирующими импульсами". Хотя характеристики этих подинтервальных импульсов более детально рассматриваются в нижеследующем подробном описании, далее дается краткое объяснение сущности настоящего изобретения.

То, что раскрыто в настоящем изобретении и на что действительно следует обратить особое внимание в связи с универсальными элементами памяти Овшинского, - это тот факт, что установочный токовый импульс для установки элемента памяти из состояния с высоким сопротивлением в состояние с низким сопротивлением может быть разделен на подинтервальные импульсы, и при подаче каждого подинтервального импульса сопротивление устройства памяти фактически не изменяется до тех пор, пока общая накопленная длительность подинтервальных импульсов не станет равной или превысит "установочную длительность". Как только с последним подинтервальным импульсом поступило последнее приращение энергии, устройство переходит в состояние с низким сопротивлением.

Таким образом, "установочная длительность" установочного токового импульса может быть разделена на требуемое количество подинтервалов. Количество подинтервалов соответствует общему количеству многозначных цифровых состояний программирования элемента. (В одном варианте реализации изобретения общее количество состояний программирования больше количества подинтервалов). Как только будет подано заданное количество подинтервальных токовых импульсов, считывается текущее состояние элемента памяти путем подачи дополнительных подинтервальных программирующих импульсов, пока элемент памяти не перейдет из состояния с высоким сопротивлением в состояние с низким сопротивлением. Количество дополнительных импульсов может определяться и сравниваться с количеством всех состояний программирования путем считывания сопротивления элемента между каждым из дополнительно подаваемых подинтервальных импульсов. Разность представляет собой текущее состояние элемента памяти. Подинтервальные импульсы определяются здесь также как "программирующие импульсы". В каждом случае подинтервальных импульсов или программирующих импульсов недостаточно для изменения материала с фазовыми переходами, но достаточно в сочетании с накопленными дополнительными подинтервальными или программирующими импульсами, чтобы заставить материал с фазовыми переходами переключиться из состояния с высоким сопротивлением в состояние с низким сопротивлением.

В процессе считывания текущего состояния элемента памяти его текущее состояние изменяется и, следовательно, здесь имеет место "считывание с разрушением". Поэтому после считывания элемента памяти он должен быть "перепрограммирован". Это выполняется путем первой установки устройства в исходное состояние с высоким сопротивлением с помощью токового импульса большой амплитуды, определяемого здесь как "токовый импульс сброса", а затем подачи ряда подинтервальных токовых импульсов, необходимых для возврата элемента в "текущее состояние", имевшее место перед операцией считывания. Таким образом, информация, которая была считана из элемента памяти, восстанавливается при перепрограммировании данного элемента.

В одном варианте реализации изобретения универсальный элемент памяти по настоящему изобретению воплощается в системе запоминания данных, где в каждом единичном элементе памяти запоминается множество бит. Это резко увеличивает плотность запоминания в памяти, поскольку в каждом универсальном элементе памяти может запоминаться множество бит. В этом варианте данные также запоминаются в необнаруживаемом виде, и такие данные не могут быть считаны или извлечены, кроме как путем использования способов и устройств согласно изобретению, что будет раскрыто в нижеследующем подробном описании. Таким образом, данный вариант позволяет запоминать информацию в засекреченном виде, то есть совершенно не обнаруживаемом никакими средствами, кроме как с помощью устройств и способов согласно настоящему изобретению.

В другом варианте реализации изобретения универсальный элемент памяти согласно настоящему изобретению реализуется в системе нейронной сети и/или искусственного интеллекта, где элемент памяти формирует, а также корректирует функцию связности между узлами или между строками и столбцами нейронного процессора. В указанном втором варианте реализации, когда элемент памяти, подключенный между узлами или между столбцами и строками нейронного процессора, получает выбранное количество подинтервальных импульсов с выбранными присвоенными весами, при этом выбранное количество и распределение весов подинтервальных импульсов определяется, например, стратегией программирования и управления нейронной сетью, элемент памяти переходит в состояние с низким сопротивлением для обеспечения максимальной связности между выбранными узлами или между строками и столбцами нейронного процессора. Этот вариант также будет более детально рассмотрен в нижеследующем подробном описании изобретения.

В частности, согласно настоящему изобретению предложен способ запоминания и извлечения информации в элементе памяти с фазовыми переходами, содержащем материал памяти с фазовыми переходами, имеющий по меньшей мере состояние с высоким сопротивлением и обнаруживаемое отличное состояние с низким сопротивлением, причем материал с фазовыми переходами выполнен с возможностью установки из состояния с высоким сопротивлением в состояние с низким сопротивлением с помощью установочного энергетического импульса, причем указанный способ содержит следующие этапы, на которых запоминают информацию в элементе памяти путем подачи по меньшей мере одного программного энергетического импульса в материал памяти с фазовыми переходами, причем по меньшей мере один программный энергетический импульс недостаточен для установки материала памяти из состояния с высоким сопротивлением в обнаруживаемое отличное состояние с низким сопротивлением, но достаточен для изменения материала памяти, так что накопление по меньшей мере одного программного энергетического импульса вместе с по меньшей мере одним дополнительным программным энергетическим импульсом устанавливает материал памяти из состояния с высоким сопротивлением в обнаруживаемо отличное состояние с низким сопротивлением, и

извлекают информацию, запомненную в элементе памяти, путем подачи в элемент памяти дополнительных программных энергетических импульсов до тех пор, пока элемент памяти не будет вынужден переключиться в обнаруживаемое отличное состояние с низким сопротивлением, и подсчитывают количество дополнительных программных энергетических импульсов, поданных для того, чтобы вызвать переключение элемента памяти в состояние с низким сопротивлением.

Кроме того, согласно настоящему изобретению, предложен способ управления элементом взаимосвязи для изменения связности в нейронной сети, причем элемент взаимосвязи содержит единичную ячейку, включающую в себя материал с фазовыми переходами, имеющий по меньшей мере состояние с высоким сопротивлением и состояние с низким сопротивлением, при этом материал с фазовыми переходами выполнен с возможностью установки из состояния с высоким сопротивлением в состояние с низким сопротивлением с помощью установочного энергетического импульса и из состояния с низким сопротивлением в состояние с высоким сопротивлением с помощью энергетического импульса сброса, причем указанный способ содержит следующие этапы, на которых:

подают энергетический импульс сброса в единичную ячейку для установки материала с фазовыми переходами в исходное состояние с высоким сопротивлением, и

подают в единичную ячейку программные энергетические импульсы с выбранными весами и длительностями на основе стратегии управления нейронной сетью, причем по меньшей мере нескольких программных энергетических импульсов в отдельности недостаточно для установки материала памяти из состояния с высоким сопротивлением в состояние с низким сопротивлением, но достаточно для изменения материала с фазовыми переходами, так что накопление по меньшей мере нескольких программных энергетических импульсов вместе с по меньшей мере одним или несколькими дополнительными программными энергетическими импульсами устанавливает материал с фазовыми переходами из состояния с высоким сопротивлением, формирующего первый уровень связности, в состояние с низким сопротивлением, формирующее второй уровень связности, отличный от первого уровня для состояния с высоким сопротивлением.

В дополнение к указанным способам, согласно настоящему изобретению, предложено устройство управления уровнем связности между узлами в узловой сети системы нейронной сети, содержащее:

единичную ячейку, содержащую материал с фазовыми переходами, имеющий по меньшей мере состояние с высоким сопротивлением и состояние с низким сопротивлением, причем материал с фазовыми переходами выполнен с возможностью установки из состояния с высоким сопротивлением в состояние с низким сопротивлением с помощью установочного энергетического импульса и из состояния с низким сопротивлением в состояние с высоким сопротивлением с помощью энергетического импульса сброса,

первый и второй электроды, электрически соединенные с материалом с фазовыми переходами для (1) подачи электрической энергии в материал с фазовыми переходами с целью переключения материала с фазовыми переходами из состояния с высоким сопротивлением в состояние с низким сопротивлением и обратно, и (2) для установки канала проведения сигнала через материал с фазовыми переходами, когда материал с фазовыми переходами находится в состоянии с низким сопротивлением,

вывод для управления и вывод для сигналов, которые оба электрически соединены с первым электродом,

общий вывод для управления и сигналов, соединенный со вторым электродом,

причем вывод для сигналов электрически соединен с первым узлом узловой сети, а общий вывод управления и сигналов электрически соединен со вторым узлом узловой сети для управления уровнем связности между первым и вторым узлами, и

систему управления нейронной сетью, электрически соединенную с выводом для управления и с общим выводом для управления и сигналов, для подачи взвешенных импульсов управления в материал с фазовыми переходами, чтобы заставить материал с фазовыми переходами переключиться из состояния с высоким сопротивлением в состояние с низким сопротивлением и тем самым увеличить уровень связности между первым и вторым узлами, когда кумулятивное действие импульсов управления превысит уровень порога переключения материала с фазовыми переходами.

Эти и различные другие варианты и применения настоящего изобретения, а также другие важные признаки и принципы настоящего изобретения будут изложены ниже в подробном описании изобретения.

Краткое описание чертежей:

фиг. 1 - графическое представление универсального элемента памяти согласно настоящему изобретению, где сопротивление устройства отложено по ординате, а амплитуда приложенного токового импульса отложена по абсциссе, при этом на графике показаны разные режимы программирования универсального элемента памяти;

фиг. 2 - блок-схема, иллюстрирующая воплощение (вариант реализации) способа согласно изобретению для записи данных в универсальный элемент памяти по изобретению;

фиг. 3 - блок-схема, иллюстрирующая воплощение способа согласно изобретению для считывания данных из универсального элемента памяти по изобретению;

фиг. 4 - блок-схема, иллюстрирующая еще одно воплощение способа согласно изобретению для считывания данных из универсального элемента памяти по изобретению;

фиг.5 - блок-схема воплощения устройства согласно изобретению для записи данных в и считывания данных из универсального элемента памяти по изобретению;

фиг.6 - поперечное сечение элемента памяти согласно настоящему изобретению, имеющего первый и второй контакт, каждый из которых примыкает к объему материала памяти;

фиг.7 - матричная схема части нейронного процессора, в котором воплощено изобретение и в состав которого включены универсальные элементы памяти по изобретению;

фиг. 8 - схематическое изображение единичной ячейки структуры нейронной сети согласно принципам настоящего изобретения;

фиг. 9 - схематическое изображение участка, состоящего из двух расположенных друг над другом плоскостей единичных ячеек структуры нейронной сети согласно принципам настоящего изобретения;

фиг. 10 - схематическое изображение другого воплощения единичной ячейки структуры нейронной сети согласно принципам настоящего изобретения, включая шины запрета и возбуждения;

фиг. 11 - схематическое изображение еще одной единичной ячейки структуры нейронной сети согласно принципам настоящего изобретения, включая отдельную шину управления;

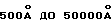

фиг. 12 - схематическое изображение еще одной единичной ячейки структуры нейронной сети согласно принципам настоящего изобретения, включая шины возбуждения и запрета, управляемые по общей входной шине;

фиг. 13 - вид сверху на возможную компоновку множества элементов памяти, которые могут быть использованы для запоминания данных согласно принципам настоящего изобретения, где, в частности, показано, каким образом могут быть подсоединены элементы памяти к набору адресных шин Х-Y;

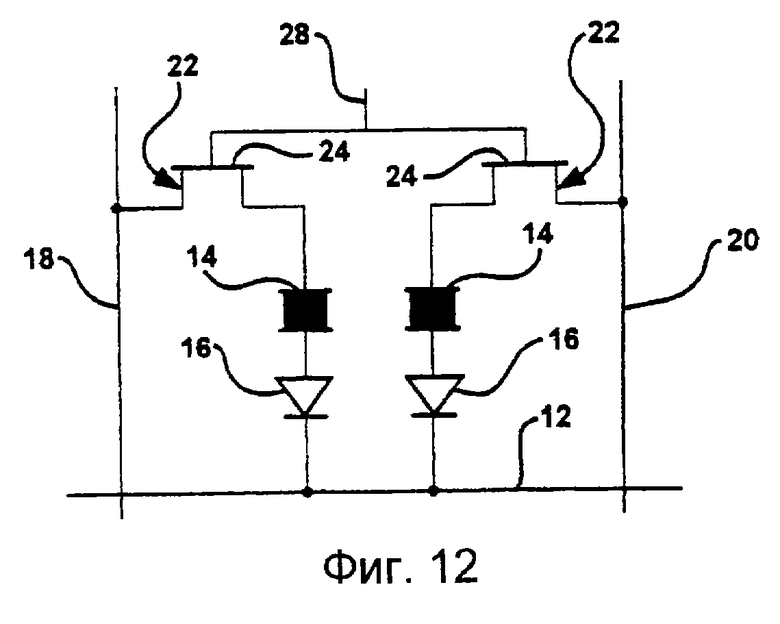

фиг.14 - схема матрицы элементов памяти, которые могут быть использованы для запоминания данных согласно принципам настоящего изобретения, где, в частности, показано, как изолирующие элементы, к примеру, диоды, последовательно соединены с элементами памяти для электрической изоляции элементов памяти друг от друга;

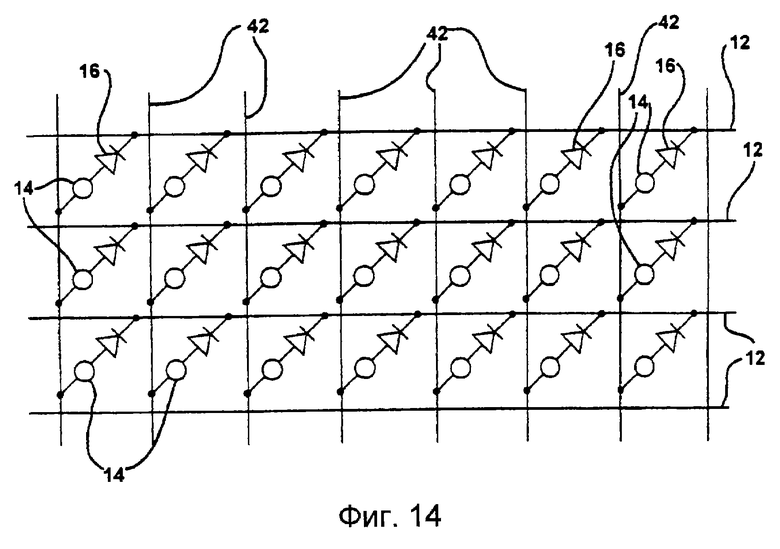

фиг. 15 - схематическое представление монокристаллической полупроводниковой подложки с интегрированной матрицей памяти согласно принципам настоящего изобретения, имеющей электрическую связь с интегральной микросхемой, к которой оперативно присоединены адресные формирователи/декодеры; и

фиг.16 - схема воплощения настоящего изобретения, используемого для управления связностью между узлами узловой сети в системе нейронной сети.

Подробное описание изобретения

На фиг. 1 представлен график зависимости между амплитудой приложенного токового импульса и сопротивлением устройства для универсального элемента памяти по настоящему изобретению. На фиг.1 показаны разные режимы программирования. В левой части кривой сопротивление устройства остается практически постоянным (то есть в состоянии с высоким сопротивлением), пока устройство не будет установлено в исходное состояние путем подачи импульса сброса с достаточной энергией. Затем устройство вновь переходит из состояния с высоким сопротивлением в состояние с низким сопротивлением.

При дальнейшем возрастании амплитуды приложенного токового импульса сопротивление устройства увеличивается при его переходе из состояния с низким сопротивлением в состояние с высоким сопротивлением. Это увеличение является постепенным и обратимым, что показано стрелками, указывающими направление вверх, либо вниз на правой части кривой. В этом режиме элемент памяти Овшинского может быть запрограммирован на любое сопротивление внутри динамического диапазона значений сопротивления путем подачи токового импульса соответствующей амплитуды. Этот тип схемы программирования обеспечивает аналоговое запоминающее устройство для данных с множеством состояний и прямой перезаписью и представляет собой режим программирования, описанный в патентах Овшинского.

В способе программирования согласно настоящему изобретению используется левая часть кривой на фиг.1. В этом режиме важны как амплитуды, так и длительности токовых импульсов, используемых для программирования устройства. Переход, происходящий на этой части кривой, не является обратимым, что показано одной стрелкой на левой части этой кривой. То есть как только устройство переведено из состояния с высоким сопротивлением в состояние с низким сопротивлением, оно не может быть вновь установлено в состояние с высоким сопротивлением путем подачи программирующего импульса с уменьшенной величиной тока. Вместо этого устройство может быть вновь установлено в состояние с высоким сопротивлением с помощью импульса тока большой амплитуды (то есть "импульса сброса"), который поднимает сопротивление по правой части кривой. Как было описано выше и более подробно описывается ниже, цифровая многозначность устройства при программировании в этом режиме возникает из способности устройства памяти Овшинского "аккумулировать" или "интегрировать" энергию каждого программирующего токового импульса, поданного на устройство.

Универсальный элемент памяти согласно изобретению может запоминать множество информационных бит в одном элементе памяти и, как более подробно описано ниже, может быть использован для создания различных соединений, обеспечивающих взаимосвязь между "нейронами" или узлами нейронной сети искусственного интеллекта.

Обращаясь к фиг.1, предположим, что устройство находится в состоянии с высоким сопротивлением в крайне левом положении на левой части характеристической кривой на фиг.1. Как объяснялось выше, если на устройство подается один импульс сброса с достаточной энергией, оно будет установлено в состояние с низким сопротивлением. Как дополнительно объяснялось выше, то, что раскрыто в настоящем изобретении и на что действительно следует обратить особое внимание в связи с универсальными элементами памяти Овшинского, - это тот факт, что установочный токовый импульс для установки элемента памяти из состояния с высоким сопротивлением в состояние с низким сопротивлением может быть разделен на подинтервальные или программирующие импульсы, причем с подачей каждого программирующего импульса сопротивление устройства памяти фактически не изменяется, пока общая накопленная длительность программирующих импульсов не станет равной или не превысит вышеописанную "установочную длительность". Как только последний программирующий импульс доставит последнее приращение энергии, устройство переходит в состояние с низким сопротивлением.

Таким образом, установочный импульс может быть разделен на несколько подинтервальных импульсов с одинаковым интервалом, каждый из которых представляет бит запоминаемых данных. Например, если требуется запомнить в одном элементе памяти полный восьмибитный байт, то в одном варианте амплитуда и высота подинтервального импульса могут быть разделены таким образом, что для выполнения перехода к состоянию с низким уровнем потребуется восемь импульсов. Тогда восемь уровней запоминания будут представлять собой импульсы от 0 до 7 для запоминания десятичных значений от "0" до "7". Если, например, на элемент изначально подается 0 импульсов для запоминания "0", то тогда потребуется 8 импульсов для перехода элемента в состояние с низким сопротивлением, и это состояние может быть считано как "0" путем вычитания из числа 8 количества импульсов, необходимых для перехода. Таким образом, запомненное значение может быть в каждом случае определено посредством вычитания из числа 8 количества импульсов, необходимых для перевода элемента памяти в состояние с низким сопротивлением. Например, если запомнено число "7", то количество импульсов, необходимых для перевода элемента в состояние с низким сопротивлением, составит 1, и, следовательно, запомненное десятичное значение будет равно "7". Для запоминания и извлечения информации в универсальных элементах памяти по изобретению могут быть выбраны различные логические протоколы.

Для дальнейшего объяснения обратимся теперь к блок-схемам на фиг.2, 3 и 4. На фиг.2 представлена блок-схема, иллюстрирующая способ запоминания многобитовой информации согласно одному варианту изобретения. В этом способе на шаге S10 инициируется операция начала записи в памяти. На шаге S11 элемент памяти сначала устанавливается в состояние с высоким сопротивлением. Это делается для того, чтобы гарантировать полную установку элемента памяти в состояние с высоким сопротивлением до начала операции записи. На шаге S12 выбирается многобитовое значение или число, подлежащее запоминанию, а счетчик импульсов устанавливается на заданное эталонное значение, соответствующее количеству импульсов, которое должно быть подано в элемент памяти. В приведенном выше примере количество импульсов может представлять многобитовое двоичное число от "000" до "111" для обеспечения запоминания десятичных значений от "0" до "7". На шаге S13 в элемент памяти подается подинтервальный импульс. На шаге S14 в счетчик импульсов добавляется единица счета импульсов и считывается количество импульсов, которое было накоплено счетчиком импульсов.

На шаге S16 определяется, равно ли количество импульсов, аккумулированных в счетчике на данный момент, эталонному количеству импульсов, записанному в счетчике. Если количество импульсов, считанное из счетчика импульсов, равно эталонному количеству, запомненному в счетчике, то на шаге S16 выполнение операции прекращается. Если количество импульсов, считанных со счетчика, меньше эталонного количества, запомненного в счетчике, то в результате возвращения к шагу S13 в элемент памяти подается еще один подинтервальный импульс, и операция повторяется, пока количество подинтервальных импульсов не станет равным запомненному эталонному количеству, и в этот момент выполнение операции на шаге S16 прекращается.

На фиг. 3 представлена блок-схема конкретного логического протокола, соответствующего вышеописанному примеру для восьмиимпульсной системы для запоминания в одном элементе памяти двоичного числа от "000" до "111". При этом способе на шаге S20 инициируется операция считывания памяти. На шаге S21 в элемент памяти подается подинтервальный импульс, а затем на шаге S22 считывается сопротивление элемента памяти. Далее на шаге S23 определяется ниже ли сопротивление элемента памяти порогового значения, соответствующего состоянию с низким сопротивлением. Если элемент памяти еще не переключился в состояние с низким сопротивлением, то на шаге S24 в счетчике импульсов добавляется единица счета импульсов, и в результате возвращения к шагу S21 в элемент памяти подается еще один подинтервальный импульс.

Когда будет определено, что сопротивление элемента памяти ниже порогового значения, что указывает на выполненное переключение в состояние с низким сопротивлением, способ переходит к шагу S25, на котором в счетчик импульсов добавляется единица счета импульсов и инициируется перепрограммирование элемента памяти. Перепрограммирование элемента памяти может быть реализовано, например, путем применения способа, показанного на вышеописанной блок-схеме по фиг.2.

Затем на шаге S26 считывается подсчитанное количество из счетчика импульсов, а на шаге S27 количество импульсов, считанных из счетчика, вычитается из кодового числа, описанного в вышеуказанном примере, для получения запомненного двоичного значения, которое считывается на шаге S28. Например, если для перевода элемента памяти в состояние с низким сопротивлением требуется семь импульсов, то число семь вычитается из кодового числа восемь для получения запомненного двоичного значения "1". Если для перевода элемента памяти в состояние с низким сопротивлением требуется пять импульсов, то число пять вычитается из числа восемь, чтобы получить десятичное число три, соответствующее двоичному значению "011".

В воплощении по фиг.3 операция считывания из памяти всегда начинается с подачи подинтервального импульса. В этом воплощении максимальное количество подаваемых импульсов равно максимальному значению числа, запоминаемого в элементе памяти. Однако в другом воплощении максимальное количество подаваемых импульсов на один импульс меньше, чем максимальное значение запоминаемого числа. В этом варианте сопротивление элемента памяти может быть уже установлено на уровне низкого сопротивления, когда операция считывания из памяти началась.

Последовательность считывания для этого воплощения показана на блок-схеме по фиг.4. В этом воплощении операция считывания из памяти инициируется на шаге S31 и, поскольку элемент памяти возможно уже установлен в состояние с низким сопротивлением, сопротивление элемента памяти считывается на первом шаге S31. Если на шаге S32 определяется, что сопротивление элемента памяти ниже порогового значения, что указывает на пребывание элемента памяти в состоянии с низким сопротивлением, тогда запомненное двоичное значение немедленно считывается на шаге S33. Однако если на шаге S32 определяется, что сопротивление элемента памяти выше порогового значения, что указывает на пребывание элемента памяти в состоянии с высоким сопротивлением, то тогда на шаге S34 в элемент памяти подается подинтервальный импульс, а сопротивление памяти считывается на шаге S35. Если сопротивление элемента памяти все еще выше порога согласно определению на шаге S36, то на шаге S37 в счетчик импульсов добавляется единица счета импульсов, и на шаге S34 в элемент памяти подается еще один подинтервальный импульс.

Когда сопротивление элемента памяти переключается на значение, соответствующее состоянию с низким сопротивлением, как это определяется на шаге S38, к счетчику добавляется единица счета импульсов, и на шаге S38 производится перепрограммирование элемента памяти. Затем на шаге S39 выполняется считывание счетчика импульсов, и считанное количество вычитается из кодового числа на шаге S40, чтобы на шаге S33 получить запомненное двоичное число. В этом варианте применительно к вышеуказанному примеру запоминания восьмибитового байта, выбранное кодовое число равно 7. Таким образом, вычитание нулевых импульсов из кодового числа семь дает десятичное число семь, соответствующее запомненному двоичному значению "111", а вычитание семи импульсов из кодового числа семь дает десятичный ноль, соответствующий запомненному двоичному значению "000".

В каждом случае логический протокол для записи значения, запоминаемого в соответствии со способом по фиг.2, выбирается так, чтобы он соответствовал протоколу считывания любого из выбранных вариантов по фиг.3 или по фиг.4, либо соответствовал любому другому протоколу, который может быть выбран для запоминания информации на основе количества подинтервальных импульсов, подаваемых и считываемых в общем случае так, как это было описано выше.

На фиг.5 показано устройство для реализации на практике способов записи и считывания для памяти по настоящему изобретению. В воплощении на фиг.5 операции считывания и записи для памяти выполняются устройством, включающим логическое устройство 100 ввода/вывода и адресации памяти, которое управляется командами считывания и записи, подаваемыми на вход 102. Устройство 100 подсоединено к импульсному генератору и счетному устройству 104, которое, в свою очередь, соединено с системой 106 адресации считывания и записи для памяти и с матрицей 108 памяти, включающей универсальные элементы памяти по настоящему изобретению. Состояние каждого элемента памяти адресуется и определяется и подается обратно системой 110 адресации состояния памяти и обратной связи в импульсный генератор и счетное устройство 104.

Команды считывания и записи для памяти, подаваемые на вход 102, реализуются с использованием описанных выше способов. Например, команда считывания на входе 102 устройства 100 ввода/вывода и адресации памяти для считывания выбранного многобитового значения из выбранной ячейки памяти приводит к реакции устройства 100, устанавливающего импульсный генератор и счетное устройство 104 на создание эталонного значения счета, и реакции по цепи обратной связи от системы 110, чтобы определить, когда будет достигнуто эталонное значение счета. Система адресации считывания и записи памяти адресует конкретную ячейку памяти, на которую должна быть подана команда считывания.

Устройство 110 адресации состояния памяти, обратной связи и вывода определяет состояние элемента памяти в адресуемой ячейке памяти и либо подает сигнал обратно для подачи дополнительных субинтервальных импульсов из устройства 104, либо считывает запомненный результат в устройство вывода 112. Операция записи действует тем же путем, реализуя вышеописанные способы.

Как упоминалось выше, многобитовая информация, запоминаемая в универсальном элементе памяти по изобретению в соответствии с изложенными здесь способами, запоминается в необнаруживаемом и, следовательно, недоступном виде, так что она не может быть извлечена, кроме как путем использования способов по настоящему изобретению с применением такого устройства, какое показано в варианте по фиг.5. Это позволяет обеспечивать эффективное шифрование данных, запоминаемых в универсальных элементах памяти.

Для того чтобы извлечь запомненные данные, должны быть известны как амплитуда, так и длительность уникального подинтервального импульса. Любая попытка определить это экспериментально либо не даст никакого результата вообще, если амплитуда импульса ниже порогового значения, либо приведет к полному стиранию запомненных данных, если амплитуда импульса слишком велика. Даже если бы амплитуда и длительность импульса были известны, необходимо знать также кодовое число и протокол, выбранный для запоминания данных, для того, чтобы получить возможность правильно считать запомненные данные. Например, если бы протокол запомненных данных требовал проведения считывания так, как показано в воплощении по фиг. 3, а попытка считывания была бы предпринята с использованием протокола, показанного в воплощении по фиг.4, произошло бы ошибочное считывание. Аналогично, если бы кодовое число было равно, например, шести, а не восьми, то также произошло бы ошибочное считывание. Эти дополнительные уровни защиты дополняют защиту, обеспечиваемую характеристиками уникальных подинтервальных импульсов, которые должны удовлетворяться в первом примере, для того, чтобы избежать либо полной неудачи при восстановлении либо полного разрушения данных без восстановления.

Также могут быть введены и различные другие протоколы для обеспечения еще нескольких дополнительных уровней защиты. Например, конфигурация устройства по фиг.5 может быть выполнена таким образом, что перед разрешением считывания запомненной информации в устройстве вывода 112 потребуется правильное перепрограммирование каждого элемента памяти для правильной замены каждого запомненного многобитового значения. В этом варианте, если данные из матрицы памяти 108 считываются с ошибками и затем, уже будучи считанными, перепрограммируются с ошибками, устройство вывода 112 не выдаст запомненную информацию и исходные данные будут уничтожены.

В рассмотренных воплощениях используются подинтервальные импульсы с одинаковыми амплитудами и длительностями. В других воплощениях изобретения эти импульсы отличаются друг от друга по разным параметрам. Более полное обсуждение параметров, которые влияют на уникальные характеристики подинтервальных импульсов, и программирования энергетических импульсов в целом следует ниже.

Универсальный элемент памяти по настоящему изобретению содержит некоторый объем материала для памяти с фазовыми переходами, причем этот материал имеет, по меньшей мере, состояние с высоким сопротивлением и отдельное состояние с низким сопротивлением, которое можно обнаружить. Состояние с высоким сопротивлением характеризуется высоким электрическим сопротивлением, а состояние с низким сопротивлением характеризуется низким электрическим сопротивлением, которое можно обнаружить и отличить от состояния с высоким электрическим сопротивлением.

По меньшей мере часть объема материала памяти способна переходить из состояния с высоким сопротивлением в состояние с низким сопротивлением в ответ на ввод одного энергетического импульса, который определяется здесь как "установочный энергетический импульс". Установочный энергетический импульс имеет амплитуду и длительность, достаточные для перевода части объема материала памяти из состояния с высоким сопротивлением в состояние с низким сопротивлением. Амплитуда установочного энергетического импульса определяется здесь как "установочная амплитуда", а длительность установочного энергетического импульса определяется здесь как "установочная длительность". Акт перевода объема материала памяти из состояния с высоким сопротивлением в состояние с низким сопротивлением определяется здесь как "установка" (или "установить" и т.п.) объема материала памяти из состояния с высоким сопротивлением в состояние с низким сопротивлением.

В общем случае здесь считается, что "энергия", подаваемая в объем материала памяти, может быть любого вида, включая (но не ограничиваясь этим) электрическую энергию, энергию пучка частиц, оптическую энергию, тепловую энергию, электромагнитную энергию, акустическую энергию и энергию давления. Электрическая энергия может принимать вид электрического тока или напряжения. Предпочтительно, чтобы электрическая энергия имела вид электрического тока, а установочный энергетический импульс представлял собой установочный токовый импульс с амплитудой, равной "установочной амплитуде", и длительностью, равной "установочной длительности", которые необходимы и достаточны для установки объема материала памяти из состояния с высоким сопротивлением в состояние с низким сопротивлением.

Не перегружая текст описания теоретическими выкладками, можно считать, что энергия, подаваемая в материал памяти с помощью установочного энергетического импульса, изменяет местный порядок, по меньшей мере, части объема материала памяти. В частности, поданная энергия заставляет, по меньшей мере, часть объема материала памяти изменить свое состояние от менее упорядоченного "аморфного" состояния в более упорядоченное "кристаллическое" состояние. Заметим, что используемый здесь термин "аморфный" относится к состоянию, которое структурно относительно менее упорядочено, или более беспорядочно, чем монокристалл, и имеет обнаруживаемое свойство, к примеру высокое электрическое сопротивление. Используемый здесь термин "кристаллический" относится к состоянию, которое с точки зрения структуры относительно более упорядочено, чем аморфное, и имеет, по меньшей мере, одно, отличное от аморфного состояния, обнаруживаемое свойство, к примеру низкое электрическое сопротивление. Предпочтительно, чтобы низкое электрическое сопротивление кристаллического состояния обнаруживалось и отличалось от высокого электрического сопротивления аморфного состояния. Один установочный энергетический импульс - это энергетический импульс с амплитудой и длительностью, достаточными для того, чтобы вызвать кристаллизацию материала памяти до необходимой степени, так чтобы он перешел из состояния с высоким сопротивлением в состояние с низким сопротивлением. Заметим, что действительная амплитуда и длительность, выбранные в качестве установочной амплитуды и установочной длительности, зависят от конкретных факторов, включающих (но не ограничиваясь ими) размер объема материала памяти, используемый материал памяти, используемый вид энергии и средство подачи указанной энергии в материал памяти и т.д.

Как было описано выше, элементы памяти Овшинского могут быть установлены из состояния с высоким сопротивлением в состояние с низким сопротивлением с помощью одного энергетического импульса, определенного здесь как "установочный энергетический импульс". Элемент памяти по изобретению также может быть установлен из состояния с высоким сопротивлением в состояние с низким сопротивлением с помощью множества энергетических импульсов, определенных здесь как "программные энергетические импульсы" (чтобы отличать их от установочного энергетического импульса). В отличие от установочного энергетического импульса каждый из множества программных энергетических импульсов недостаточен для того, чтобы вызвать установку материала памяти из состояния с высоким сопротивлением в состояние с низким сопротивлением. Однако каждого программного энергетического импульса достаточно, чтобы изменить, по меньшей мере, часть материала так, что накопление множества программных энергетических импульсов достаточно, чтобы вызвать переход из состояния с высоким сопротивлением в состояние с низким сопротивлением.

Не перегружая текст описания теорией, можно считать, что каждый из множества программных энергетических импульсов, подаваемых в объем материала памяти, "вносит изменения" в материал, вызывая некоторую степень кристаллизации (то есть образование активных центров и/или рост кристаллов), по меньшей мере, в части материала. Степень кристаллизации, вызываемая каждым из программных энергетических импульсов, сама по себе недостаточна, чтобы вызвать изменение состояния элемента памяти из состояния с высоким сопротивлением в состояние с низким сопротивлением. Однако "накопленная" кристаллизация, вызванная совместным действием множества программных энергетических импульсов, достаточна для установки элемента памяти из состояния с высоким сопротивлением в состояние с низким сопротивлением. По существу часть объема материала памяти "накапливает" изменения (то есть кристаллизацию), вызываемые каждым отдельным программным энергетическим импульсом, подаваемым в устройство.

В общем случае все амплитуды и длительности каждого из множества подинтервальных или программных энергетических импульсов могут быть различными. В одном варианте все амплитуды одинаковые и предпочтительно устанавливаются равными амплитуде установочного энергетического импульса (то есть "установочной амплитуде"). Длительности каждого программного энергетического импульса выбираются путем деления временного интервала установочного энергетического импульса, "установочной длительности" на множество подинтервалов. (Следовательно, суммарная длительность всех подинтервалов равна "установочной длительности"). Длительность каждого программного энергетического импульса устанавливается равной уникальной длительности подинтервалов.

Следовательно, множество подинтервальных или программных энергетических импульсов может быть использовано для установки элемента памяти из состояния с высоким сопротивлением в состояние с низким сопротивлением, где каждый программный энергетический импульс имеет амплитуду, равную амплитуде установочного энергетического импульса, и каждый программный энергетический импульс имеет длительность, равную уникальной длительности подинтервалов. Как обсуждалось выше, сопротивление элемента памяти фактически не изменяется, оставаясь соответствующим состоянию с высоким сопротивлением, пока в объем материала памяти не будет подан последний программный энергетический импульс. Как только последний программный энергетический импульс подан, устройство переходит в состояние с низким сопротивлением.

Снова следует заметить, что энергия, подаваемая в объем материала памяти, может представлять собой импульсы электрического тока. Следовательно, элемент памяти может быть установлен из состояния с высоким сопротивлением в состояние с низким сопротивлением с помощью множества "программных токовых импульсов", где каждый программный токовый импульс сам по себе недостаточен для установки устройства. В одном воплощении длительность, определяемая длительностью "установочного токового импульса", может быть разделена на подинтервалы. Множество программных токовых импульсов может быть подано в материал памяти, причем каждый программный токовый импульс имеет амплитуду, равную амплитуде установочного токового импульса, и каждый программный токовый импульс имеет длительность, равную уникальной длительности подинтервалов. Установка в устройстве произойдет после подачи последнего программного токового импульса.

В одном воплощении данные могут быть записаны в элемент памяти путем подачи одного или нескольких программных энергетических импульсов в объем материала памяти. В общем случае все амплитуды и длительности используемых программных энергетических импульсов могут быть разными. Амплитуда каждого программного энергетического импульса может быть выбрана равной "установочной амплитуде" установочного энергетического импульса, описанного выше. Длительность каждого программного энергетического импульса такова, что каждый импульс сам по себе недостаточен для установки объема материала памяти из состояния с высоким сопротивлением в состояние с низким сопротивлением, и суммарная длительность всех программных энергетических импульсов меньше или равна установочной длительности установочного энергетического импульса.

Как обсуждалось выше, энергия в объем материала памяти может подаваться в виде токовых импульсов. Вновь обратимся к фиг.1, где показано, что когда амплитуда приложенного токового импульса возрастает до достаточной величины, устройство переключается из состояния с высоким сопротивлением в состояние с низким сопротивлением. Один токовый импульс, достаточный для установки материала памяти из состояния с высоким сопротивлением в состояние с низким сопротивлением, определяется здесь как "установочный токовый импульс", имеющий амплитуду, определяемую как "установочная амплитуда", и длительность, определяемую как "установочная длительность".

Данные могут записываться в элемент памяти путем подачи в объем материала памяти одного или нескольких "программных токовых импульсов", причем каждый программный токовый импульс недостаточен для установки устройства. В общем случае все амплитуды и длительности программных токовых импульсов могут быть разными. В одном воплощении амплитуда каждого программного токового импульса выбирается равной установочной амплитуде, определенной выше. Кроме того, длительность каждого программного токового импульса выбирается (1) так, что каждый импульс сам по себе недостаточен, чтобы вызвать изменение состояния материала из состояния с высоким сопротивлением в состояние с низким сопротивлением и (2) так, что суммарная длительность всех программных токовых импульсов меньше или равна "установочной длительности", определенной выше.

В одном воплощении данного способа программирования, описанного выше, длительность, определяемая "установочной длительностью", делится на подинтервалы. Количество подинтервалов выбирается на единицу меньше требуемого количества всех возможных состояний программирования. Например, если требуется всего пять состояний программирования, то временной интервал "установочная длительность" делится на четыре подинтервала (так, что суммарная длительность всех четырех подинтервалов равна "установочной длительности"). Предпочтительно, чтобы все подинтервалы были одинаковыми (однако возможны другие варианты реализации, где используются неравные подинтервалы).

Элемент может быть запрограммирован в требуемое "запрограммированное состояние" путем подачи одного или нескольких программных токовых импульсов, где каждый программный токовой импульс имеет длительность, равную длительности подинтервала, и амплитуду, равную "установочной амплитуде" установочного токового импульса. В примере, где используется всего пять состояний, если программный токовой импульс не подан, то элемент памяти остается в состоянии I, если подан один программный токовой импульс, то элемент памяти будет находиться в состоянии II, если подано два программных токовых импульса, то элемент памяти будет находиться в состоянии III, если подано три подинтервальных импульса, то элемент памяти будет находиться в состоянии IV, а если подано четыре подинтервальных токовых импульса, то элемент памяти будет находиться в состоянии V.

Заметим, что сопротивление материала памяти фактически не изменяется, пока общая суммарная длительность подинтервальных импульсов не станет равной либо превысит "установочную длительность". В вышеуказанном примере сопротивление фактически не изменяется, пока не будет подан четвертый

подинтервальный импульс. После подачи четвертого импульса сопротивление элемента памяти изменяется из состояния с высоким сопротивлением в состояние с низким сопротивлением.

Запрограммированное состояние элемента памяти может быть считано путем подачи дополнительных программных токовых импульсов, пока материал памяти установлен в состояние с низким сопротивлением и идет подсчет количества подаваемых дополнительных импульсов. В вышеприведенном примере, если для записи данных в элемент памяти изначально был подан один программный токовый импульс, то запрограммированным состоянием будет состояние II. В этом случае для того, чтобы установить элемент памяти в состояние с низким сопротивлением, необходимо будет подать три дополнительных программных энергетических импульса. Запрограммированное состояние может быть определено путем вычитания количества необходимых дополнительных импульсов (в данном случае 3) из общего количества возможных состояний (в данном случае 5). Следовательно, запрограммированным состоянием будет 5-3=2 (то есть состояние II).

Следовательно, как было описано в связи с выше представленными вариантами воплощения изобретения, в устройстве может быть выполнено считывание путем определения сначала того, находится ли часть объема материала памяти в состоянии с низким сопротивлением. Если это не так, то тогда подается дополнительный программный энергетический импульс, и вновь оценивается сопротивление устройства. Если элемент памяти все еще не находится в состоянии с низким сопротивлением, то тогда подается еще один дополнительный программный энергетический импульс, и вновь определяется сопротивление устройства. Эта процедура повторяется до тех пор, пока не будет определено, что устройство находится в состоянии с низким сопротивлением. Подсчитывается количество дополнительных программных токовых импульсов, необходимых для установки устройства (то есть с каждым требуемым дополнительным программным энергетическим импульсом состояние счетчика может шаг за шагом возрастать), и это число используется для определения запрограммированного состояния.

Способ программирования может дополнительно включать шаг стирания данных из элемента памяти путем подачи "энергетического импульса сброса" в объем материала памяти. Энергетический импульс сброса - это энергетический импульс, достаточный для изменения сопротивления объема материала памяти из состояния с низким сопротивлением в состояние с высоким сопротивлением. Предпочтительно это энергетический импульс, достаточный для изменения, по меньшей мере, части объема материала памяти из более упорядоченного кристаллического состояния в менее упорядоченное аморфное состояние. Заметим, что вышеописанный программный энергетический импульс (или программный токовый импульс) недостаточен для изменения сопротивления объема материала памяти из состояния с низким сопротивлением в состояние с высоким сопротивлением. Как было отмечено выше, энергия может представлять собой электрический ток. Следовательно, "токовый импульс сброса" является импульсом электрического тока, достаточным для изменения сопротивления объема элемента памяти из состояния с низким сопротивлением в состояние с высоким сопротивлением.

Хотя вышеприведенное обсуждение по большей части велось в терминах токовых импульсов, следует заметить, что для реализации способа программирования по настоящему изобретению может быть использован любой вид энергии. Эти виды энергии включают электрическую энергию, оптическую энергию, энергию пучка электронов, тепловую энергию, электромагнитную энергию, акустическую энергию и энергию давления. Как обсуждалось выше, в одном варианте настоящего изобретения в описанном здесь способе программирования используются импульсы электрического тока для программирования элемента памяти путем подачи токовых импульсов, при этом элемент памяти по настоящему изобретению дополнительно включает средство для доставки электрической энергии, по меньшей мере, в часть объема материала памяти. В общем случае "ток" определяется как поток электрических зарядов. Примерами электрических зарядов являются электроны, протоны, положительные и отрицательные ионы и заряженные частицы любого другого типа. Поток электрических зарядов может возникнуть из-за пучка заряженных частиц, к примеру пучка электронов или пучка протонов.

В одном воплощении настоящего изобретения средствами для доставки (энергических импульсов) являются первый контакт и второй контакт. Каждый из контактов примыкает к объему материала памяти. Используемый здесь контакт "примыкает" к объему материала памяти, если, по меньшей мере, часть контакта действительно касается материала памяти.

В другом воплощении изобретения первый и второй контакты представляют собой пару пространственно разнесенных плоских контактов, примыкающих к объему материала памяти. Каждый контакт может содержать один или несколько тонкопленочных контактных слоев. На фиг.6 показано поперечное сечение варианта элемента памяти, выполненного на монокристальной кремниевой полупроводниковой подложке 10. Элемент памяти включает материал памяти 36, первый пространственно разнесенный контакт 6, примыкающий к объему материала памяти, и второй пространственно разнесенный контакт 8А, примыкающий к объему материала памяти. В показанном воплощении изобретения первый и второй контакты 6, 8А являются плоскими контактами. По меньшей мере, один из контактов 6, 8А может содержать один или несколько тонкопленочных слоев. Пример элемента памяти, где первый и второй контакты 6, 8А имеют два тонкопленочных слоя, был описан в патентной заявке США 08/739080, принадлежащей настоящему заявителю, которая упомянута в качестве ссылки.

Слой материала памяти 36 наносится толщиной предпочтительно от около  до около

до около  более предпочтительно от около

более предпочтительно от около  до около

до около  а наиболее предпочтительно от около

а наиболее предпочтительно от около  до около

до около

Элемент памяти, показанный на фиг.6, может быть выполнен в ходе многошагового процесса. Сначала напыляются контактный слой 8А и изолирующий слой 46, а затем выполняется травление изолирующего слоя 46, с тем чтобы получить зону контакта между материалом памяти 36 и контактным слоем 8А. Затем напыляются слой памяти 36 и контактный слой 6, и весь набор слоев 8А, 46, 36 и 6 подвергается травлению до выбранных размеров. На верхнюю часть всей структуры напыляется слой из изолирующего материала 39. Примерами изолирующих материалов являются SiO2, Si3N4 и оксисульфид теллура (например, TeOS). Слой изолирующего материала 39 подвергается травлению и напыляется слой алюминия 42 для создания сеточной структуры 42 второго электрода, которая располагается в перпендикулярном направлении по отношению к проводникам 12, и завершает соединение сетки XY с отдельными элементами памяти. Законченная интегральная структура покрывается сверху герметизирующим слоем из подходящего герметика, к примеру Si3N4, или пластмассы, к примеру полиамида, который защищает данную структуру от проникновения влаги и других внешних элементов, которые могут вызвать старение материала и ухудшение рабочих характеристик. Герметик Si3N4 может наноситься, например, в процессе низкотемпературного плазменного напыления. Полиамидный материал может быть нанесен центрифугированием и подвергнут отжигу после напыления в соответствии с известными способами для образования герметизирующего слоя.

Еще в одном воплощении изобретения средство для подачи импульса включает, по меньшей мере, один "конусообразный" контакт. Конусообразный контакт - это контакт, который сужается к вершине, примыкающей к объему материала памяти. Вариант элемента памяти, где используется конусообразный контакт, описан в патенте США 5687112, выданном Овшинскому и др., который упомянут в качестве ссылки.

Средство для подачи может также представлять собой, по меньшей мере, один излучатель поля. Излучатели поля рассматриваются в патенте США 5557596, выданном Гибсону (Gibson) и др., который упомянут в качестве ссылки. Излучатель поля сужается к вершине, которая расположена в непосредственной близости от объема материала памяти. Используемая здесь терминология "в непосредственной близости" означает, что излучатель поля в действительности не находится в контакте с объемом материала памяти. Предпочтительно, чтобы излучатель поля находился на расстоянии примерно от  до примерно

до примерно  от объема материала памяти. Более предпочтительно, чтобы излучатель поля находился на расстоянии примерно от

от объема материала памяти. Более предпочтительно, чтобы излучатель поля находился на расстоянии примерно от  от объема материала памяти. Излучатель поля генерирует пучок электронов из своей конической вершины. Как обсуждается в патенте '596, пучок электронов может выводиться из излучателя поля множеством различных способов. Вокруг излучателя поля может быть расположен кольцевой затвор и создана разность электрических потенциалов между излучателем поля и затвором. В альтернативном варианте разность электрических потенциалов может быть создана между излучателем поля и действительным объемом материала памяти. Еще в одном варианте контакт (к примеру, плоский контакт) может быть расположен так, что он будет примыкать к объему материала памяти и находиться на расстоянии от излучателя поля. Разность электрических потенциалов может быть создана между излучателем поля и плоским контактом, так что электронный пучок направляется в объем материала памяти и бомбардирует материал памяти. Может быть также использовано несколько излучателей поля.

от объема материала памяти. Излучатель поля генерирует пучок электронов из своей конической вершины. Как обсуждается в патенте '596, пучок электронов может выводиться из излучателя поля множеством различных способов. Вокруг излучателя поля может быть расположен кольцевой затвор и создана разность электрических потенциалов между излучателем поля и затвором. В альтернативном варианте разность электрических потенциалов может быть создана между излучателем поля и действительным объемом материала памяти. Еще в одном варианте контакт (к примеру, плоский контакт) может быть расположен так, что он будет примыкать к объему материала памяти и находиться на расстоянии от излучателя поля. Разность электрических потенциалов может быть создана между излучателем поля и плоским контактом, так что электронный пучок направляется в объем материала памяти и бомбардирует материал памяти. Может быть также использовано несколько излучателей поля.

Излучатели поля могут быть созданы несколькими способами. Один способ обсуждается в работе Спинда (Spindt) и др. "Physical Properties of Thin-Film Field Emission Cathodes With Molybdenum Cones", опубликованной в Journal of Applied Physics Vol. 47, No 12, декабрь 1976. Другой способ обсуждается в статье Бетсуи (Betsui) "Fabrication and Characteristics of Si Field Emitter Arrays", опубликованной в Tech. Digest IV-th Int. Vacuum Microelectronics Conf., Nagahama, Japan, page 26, 1991.

Между излучателем поля и объемом материала памяти может существовать частичный вакуум. Как обсуждается в патенте '596, частичный вакуум может составлять, по меньшей мере, 133, 322•10-5 Па (10-5 Торр). Способы изготовления излучателей поля в вакуумных камерах известны специалистам в данной области техники. Технологии обсуждаются в работе Джоунса (Jones) "Silicon Field Emission Transistors and Diodes", опубликованной в IEEE Transactions on Components, Hybrids and Manufacturing Technology, 15, page 1051, 1992. В альтернативном воплощении между излучателем поля и объемом материала памяти может находиться газ.

Еще в одном воплощении настоящего изобретения средство для подачи электрического тока представляет собой туннельный контакт, который расположен в непосредственной близости от объема материала памяти. Туннельный контакт может быть подобен излучателю поля. Он может сужаться к вершине, которая располагается в непосредственной близости от объема материала памяти. Туннельный контакт в действительности не касается материала памяти, однако он располагается в пределах ширины квантово-механического потенциального барьера. Предпочтительно, чтобы это расстояние было меньше  .

.

Примеры материалов с фазовыми переходами предложены в патенте США 3271591 и патенте США 3530441, которые упомянуты в качестве ссылки. Другие примеры материалов с фазовыми переходами можно найти в патентах США 5166758, 5206716, 5534711, 5536947, 5596522 и 5687112, упомянутых в качестве ссылки и принадлежащих настоящему заявителю.

Материал с фазовыми переходами предпочтительно должен быть "энергонезависимым". Используемый здесь термин "энергонезависимый" означает, что материал с фазовыми переходами будет поддерживать целостность информации, запомненной в ячейке памяти (с выбранным пределом ошибок), без необходимости ее периодического обновления.

Объем материала памяти может содержать смесь диэлектрического материала и вышеописанного материала с фазовыми переходами. "Смесь" может быть либо гетерогенной смесью, либо гомогенной смесью. Предпочтительно, чтобы смесь была гетерогенной. Материал памяти, содержащий смесь материала с фазовыми переходами и диэлектрического материала, раскрыт в патентной заявке США 09/063174, упомянутой в качестве ссылки и принадлежащей настоящему заявителю.

Используемый здесь термин "материал с фазовыми переходами" определяется как материал, способный переключаться из отличающихся друг от друга обнаруживаемых состояний с большим местным порядком (более кристаллические состояния) в состояния с меньшим местным порядком (менее упорядоченные или более аморфные состояния) и обратно путем подачи энергии в электрическом либо другом виде. Материалы с фазовыми переходами по этому изобретению дополнительно проявляют свойства, заключающиеся в способности воспринимать порции энергии, находящиеся ниже уровня, требующегося для возникновения обнаруживаемого изменения в местном порядке, но которые тем не менее вызывают изменения в структуре материала, которые накапливаются и приводят к обнаруживаемому изменению в местном порядке после подачи нескольких порций энергии.

Предпочтительно, чтобы материал с фазовыми переходами согласно изобретению включал один или несколько элементов, которые выбираются из группы, состоящей из Те, Se, Ge, Sb, Bi, Pb, Sn, As, S, Si, P, О и их смесей или сплавов. Материал с фазовыми переходами предпочтительно включает, по меньшей мере, один халькогенидный элемент и может включать, по меньшей мере, один элемент из металлов переходной группы. Предпочтительно, чтобы халькогенидный элемент выбирался из группы, состоящей из Те, Sе и их смесей или сплавов. Более предпочтительно, чтобы халькогенидный элемент представлял собой смесь Те и Se.

Используемый здесь термин "металл переходной группы" относится к элементам с 21 по 30, с 39 по 48, 57 и с 72 по 80. Предпочтительно, чтобы элемент из металлов переходной группы выбирался из группы, состоящей из Cr, Fe, Ni, Nb, Pd, Pt и их смесей или сплавов. Наиболее предпочтительно, чтобы металлом из переходной группы был Ni. Конкретные примеры таких многоэлементных систем излагаются далее применительно к системе Te:Ge:Sb с или без Ni и/или Se.

Дополнительно будем считать, что размер кристаллов, которые существуют в массе полупроводника и материала памяти, относительно мал, предпочтительно порядка менее  , более предпочтительно между порядка

, более предпочтительно между порядка  наиболее предпочтительно примерно

наиболее предпочтительно примерно

Многие материалы с фазовыми переходами по настоящему изобретению имеют тенденцию к образованию больших или меньших кристаллов на единицу объема. Установлено, что размеры кристаллов, лежащие в наиболее широком предпочтительном диапазоне материалов, воплощающих настоящее изобретение, гораздо меньше примерно  и в общем случае меньше диапазона значений порядка

и в общем случае меньше диапазона значений порядка  который был характерен для материалов известного уровня техники. Размер кристалла определяется здесь как диаметр кристаллов или "характеристический размер", который эквивалентен диаметру, когда кристаллы не имеют сферическую форму.

который был характерен для материалов известного уровня техники. Размер кристалла определяется здесь как диаметр кристаллов или "характеристический размер", который эквивалентен диаметру, когда кристаллы не имеют сферическую форму.

Было определено, что состав в состоянии с высоким сопротивлением для материалов класса TeGeSb, которые удовлетворяют критериям настоящего изобретения, обычно характеризуются фактически пониженными концентрациями Те по отношению к известным существующим материалам для электрически стираемой памяти. Примеры материалов TeGeSb приведены в патентах США 5534711, 5536947 и 5596522, принадлежащих настоящему заявителю. В одном составе, который обеспечивает существенно улучшенные рабочие характеристики электрического переключения, средняя концентрация Те в напыленных материалах ниже 70%, обычно ниже порядка 60% и в основном лежит в диапазоне примерно от 23% до примерно 58% Те, а наиболее предпочтительным является диапазон примерно от 48% до 58% Те. Концентрации Ge выше примерно на 5% и лежат в диапазоне в среднем от примерно 8% до примерно 30% в материале, где в основном концентрация остается ниже 50%. Наиболее предпочтительно, чтобы концентрации Ge лежали в диапазоне примерно от 8% до 40%. Другим основным составным элементом в этом составе являлась Sb. Данные процентные соотношения являются атомными (процентными) концентрациями, которые составляют в сумме 100% атомов составляющих элементов. Таким образом, этот состав может быть описан как ТеаGеbSb100-(а+b). Эти трехкомпонентные сплавы Те-Ge-Sb являются полезными исходными материалами для разработки дополнительных материалов с фазовыми переходами, имеющих лучшие электрические характеристики.

Материалы с фазовыми переходами согласно настоящему изобретению предпочтительно включают, по меньшей мере, один халькогенидный элемент и могут включать один или несколько металлов переходной группы. Материалы с фазовыми переходами, которые включают металлы переходной группы, элементарно модифицируются в формы материалов в трехкомпонентной системе Te-Ge-Sb. To есть элементарно модифицированные материалы с фазовыми переходами образуют модифицированные формы сплавов Te-Ge-Sb с фазовыми переходами. Эта элементарная модификация достигается путем включения металлов переходной группы в базовую трехкомпонентную систему Te-Ge-Sb с либо без дополнительного халькогенидного элемента, к примеру Se. В общем случае элементарно модифицированные материалы с фазовыми переходами разбиваются на две категории.

Первая категория материалов с фазовыми переходами включает Те, Ge, Sb и металл переходной группы при соотношении (TeaGebSb100-(a+b))сТМ100-c где индексы выражены в атомных процентных концентрациях, которые в сумме составляют 100% составляющих элементов, а ТМ - это один или несколько металлов переходной группы, а и b были пояснены выше для трехкомпонентной системы Te-Ge-Sb, а с лежит в диапазоне примерно от 90% до 99,99%. Металлы переходной группы предпочтительно включают Cr, Fe, Ni, Nb, Pd, Pt и их смеси или сплавы.

Ко второй категории материалов с фазовыми переходами относятся Те, Ge, Sb, Se и металл переходной группы при соотношении (TeaGebSb100-(a+b))cTMdSe100-(c+d), где индексы выражены в атомных процентных концентрациях, которые в сумме составляют 100% составляющих элементов, где ТМ - это один или несколько металлов переходной группы, а и b были пояснены выше для трехкомпонентной системы Te-Ge-Sb, с лежит в диапазоне примерно от 90% до 99,5%, a d - в диапазоне примерно от 0,01% до 10%. Металлы переходной группы могут предпочтительно включать Cr, Fe, Ni, Pd, Pt, Nb и их смеси или сплавы.

Материал с фазовыми переходами обладает по существу энергонезависимыми установочными значениями сопротивления. Однако, если значение сопротивления материала с фазовыми переходами не отклоняется ("дрейфует") от изначально установленного значения, для компенсации такого изменения может быть использована "композиционная модификация", описанная ниже. Используемый здесь термин "энергонезависимый" относится к состоянию, при котором установленное значение сопротивления остается фактически постоянным в течение интервалов времени хранения. Конечно, для обеспечения полного отсутствия "дрейфа", приводящего к превышению допустимого предела ошибок, могут быть использованы программные средства (в том числе рассмотренная выше система обратной связи).

Определенное здесь понятие "композиционная модификация" включает любое средство модификации состава материала с фазовыми переходами для обеспечения практически стабильных значений сопротивления, включая добавление элементов, растягивающих ширину запрещенной зоны, для увеличения собственного сопротивления материала. Одним из примеров композиционной модификации является постепенное включение композиционных неоднородностей по толщине. Например, в объеме материала с фазовыми переходами может быть выполнено постепенное изменение от первого сплава Te-Ge-Sb ко второму сплаву Te-Ge-Sb с другим составом. Постепенное композиционное изменение может принимать любую форму, которая уменьшает дрейф установленного значения сопротивления. Например, плавное композиционное изменение нет необходимости ограничивать первым и вторым сплавом из системы одинаковых сплавов. Постепенное изменение также может быть выполнено с количеством сплавов больше двух. Постепенное изменение может быть однородным и непрерывным либо неоднородным или ненепрерывным. Конкретный пример постепенного композиционного изменения, которое приводит к уменьшению дрейфа значения сопротивления, включает однородное и непрерывное постепенное превращение Ge14Sb29Te57 на одной поверхности в Ge22Sb22Te56 на противоположной поверхности.

Другим способом использования композиционной модификации для уменьшения дрейфа сопротивления является расслоение объема материала с фазовыми переходами. То есть объем материала с фазовыми переходами может быть сформирован из множества отдельных относительно тонких слоев разного состава. Например, объем материала с фазовыми переходами может включать одну или несколько пар слоев, каждый из которых выполнен из разного сплава Te-Ge-Sb. Опять, как в случае с постепенно изменяющимися по составу композициями, может быть использована любая комбинация слоев, которая приводит к существенному уменьшению дрейфа значения сопротивления. Слои могут иметь одинаковую толщину либо могут быть разной толщины. Может быть использовано любое количество слоев, и в объеме материала памяти может быть множество слоев из одинакового сплава, либо соприкасающиеся, либо отделенные друг от друга. Также могут быть использованы слои из любого количества разных сплавов. Конкретным примером композиционного расслоения является объем материала памяти, который содержит чередующиеся пары слоев Gе14Sb29Те57 и Ge22Sb22Te56.

Еще один вид композиционной неоднородности для уменьшения дрейфа сопротивления выполняется путем сочетания постепенного композиционного изменения и композиционного расслоения. В частности, вышеупомянутое постепенное композиционное изменение может выполняться в сочетании с любым видом вышеописанного композиционного расслоения для формирования объема материала памяти со стабильным сопротивлением. Примерами объемов материала с фазовыми переходами, где используется такое сочетание, являются: (1) объем материала с фазовыми переходами, который включает дискретный слой из Ge22Sb22Te56, за которым следует постепенно изменяющаяся композиция из Ge14Sb29Te57 и Ge22Sb22Te56 и (2) объем материала с фазовыми переходами, который содержит отдельный слой Ge14Sb29Te57 и постепенно изменяющуюся композицию Ge14Sb29Te57 и Ge22Sb22Te56.

Материал памяти может быть выполнен с помощью таких способов, как распыление, испарение или химическое осаждение из паровой фазы (ХОПФ), которые могут быть усовершенствованы с помощью плазменных технологий, к примеру радиочастотного тлеющего разряда. Наиболее предпочтительно создавать материал памяти радиочастотным распылением или испарением. Он может быть выполнен с применением технологий распыления из множества источников при использовании множества мишеней - обычно мишени из материала с фазовыми переходами и мишени из диэлектрического материала. При расположении этих мишеней на подложке друг против друга распыление выполняется, когда подложка поворачивается относительно каждой мишени. Также может быть использована мишень, содержащая как материал с фазовыми переходами, так и диэлектрический материал. Кроме того, для управляемого изменения морфологии материала с фазовыми переходами внутри композиционного материала памяти, сформированного благодаря эффекту роста кристаллов, а также агрегирования кристаллов благодаря перемещениям поверхности, может быть использован нагрев подложки.

Другим важным применением универсального элемента памяти по настоящему изобретению является сеть параллельной обработки, к примеру сеть, которая может быть использована в нейронных сетях и в вычислительных системах искусственного интеллекта. Сеть параллельной обработки содержит взаимосвязанный по вертикали набор для параллельной распределенной обработки данных, который включает множество уложенных друг на друга матриц из единичных ячеек. Каждая единичная ячейка имеет связь для передачи данных, по меньшей мере, с одной другой единичной ячейкой на соседней плоскости. Предпочтительно, чтобы единичные ячейки на данной плоскости были также до некоторой степени связаны между собой. Таким образом может быть установлена высокая степень связности между отдельными единичными ячейками набора. Сети параллельной обработки раскрыты в патенте США 5159661, упомянутом в качестве ссылки и принадлежащем настоящему заявителю.

Нейронные вычислительные операции основаны на подражании способу вычисления, который используется нейронами у животных. Нейрон воспринимает электрические сигналы от большого количества других нейронов. Каждому из этих сигналов нейрон присваивает вес или важность. Присвоенные веса "узнаются" системой опытным путем. Когда сумма взвешенных входных сигналов превысит пороговое значение, нейрон возбуждается. Это возбуждение создает электрический сигнал, посылаемый на входы большого количества других нейронов.

Универсальные элементы памяти по настоящему изобретению могут быть включены в системы нейронных сетей для того, чтобы они вели себя во многом аналогичным образом. В указанном воплощении в универсальный элемент памяти подается некоторое количество взвешенных импульсов, пока не будет достигнут порог и элемент не включится или "возбудится". Дополнительное преимущество настоящего изобретения заключается в том, что импульсы не должны подаваться одновременно. Воздействие каждого импульса запоминается в энергонезависимой форме и остается в памяти, пока не будет подан следующий импульс вдобавок к уже запомненным импульсам. Таким образом может поддерживаться поведение нейрона, использующего последовательные импульсы, подаваемые в любом порядке во времени.

Это обеспечивает простую регулярную структуру в виде набора элементов памяти для выполнения логических функций нейронов. Одно воплощение настоящего изобретения, включенное в состав процессора нейронной сети, показано на фиг.7. В этом воплощении набор универсальных элементов памяти 200 по настоящему изобретению формируется с изолирующими диодами 202. Как показано на фигуре, от выходов столбцов набора к входам строк набора через чувствительные усилители 208 и токовые возбудители 210 установлены каналы обратной связи 204 и 206.

Когда отдельный элемент памяти 200 находится в состоянии с высоким сопротивлением, степень связности между строкой и столбцом, к которому он подсоединен, является низкой из-за высокого сопротивления.

Взвешенные импульсы подаются токовыми возбудителями в универсальные элементы памяти 200 через изолирующие диоды 202 с использованием стратегии управления, согласно которой принимается решение, когда подавать импульсы и какие веса им присвоить. Воздействие этих импульсов кумулятивно запоминается в каждом элементе памяти. Когда в любом данном элементе памяти будет достигнут выбранный пороговый уровень, этот элемент переключается или "возбуждается", переходя в состояние с низким сопротивлением, чтобы увеличить уровень связности между строкой и столбцом, к которому он подсоединен, по причине низкого сопротивления установленного канала.

Единичная ячейка, которая может быть использована в этом воплощении, а также в других воплощениях, показана на фиг.8, иллюстрирующей типичную единичную ячейку, которая может быть использована в настоящем изобретении. Единичная ячейка включает шину 10 ввода данных и шину 12 вывода данных. Связь между двумя шинами 10, 12 устанавливается через универсальный элемент памяти 14 настоящего изобретения. На фиг.9 схематически изображена часть набора, состоящего из двух уложенных друг на друга матриц 140, 142, каждая из которых включает единичные ячейки, соединенные через вертикальный межслойный переход 44. Предполагается, что аналогичные уложенные друг на друга матрицы входят в объем настоящего изобретения для других показанных здесь единичных ячеек.

Единичная ячейка дополнительно включает изолирующий прибор, к примеру диод 16. Обычно единичные ячейки располагаются в наборе, где шины 10 ввода данных и шины 12 вывода данных содержат ряд строк и столбцов, и в этом варианте изолирующий прибор 16 предназначен для предотвращения перекрестных помех между соседними единичными ячейками. Изолирующий прибор изображен в виде диода 16 и как таковой может включать тонкопленочный диод, к примеру поликристаллический кремниевый диод, хотя подобным же образом здесь могут быть использованы аморфные, поликристаллические или кристаллические диоды из разных других материалов, а также другие приборы, к примеру транзисторы. При изготовлении структур, содержащих халькогенидные элементы и поликристаллические диоды, диоды обычно выполняются посредством напыления в виде аморфных приборов с использованием тонкопленочной технологии, а затем эти диоды кристаллизуются. Согласно настоящему изобретению, установлено, что кристаллизация материала диодов посредством использования коротких световых импульсов от лазера либо аналогичного источника имеет преимущество, состоящее в высокой скорости кристаллизации материала диодов без разрушения халькогенидного материала.

Ячейка на фиг.8 является частью матрицы в общем случае идентичных ячеек, расположенных по строкам и столбцам. Процессор по настоящему изобретению включает набор таких уложенных друг на друга матриц, причем, по меньшей мере, несколько ячеек в первой матрице соединены с ячейками во второй матрице, так что выход данных ячейки на первой плоскости 140 связан с входом ячейки на второй плоскости 142.