Область техники, к которой относится изобретение

Настоящее раскрытие относится к уменьшению разрушения током считывания массива памяти с узлами пересечения.

Уровень техники

Запоминающее устройство на фазовых переходах представляет собой устройство памяти, в котором обычно используется халькогенидный материал для элементов памяти. Элемент памяти представляет собой модуль, в котором фактически содержится информация. Во время работы память на фазовых переходах хранит информацию в элементе памяти путем изменения фазы элемента памяти между аморфной и кристаллической фазами. Халькогенидный материал может представлять либо кристаллическую, или аморфную фазу, проявляя низкую или высокую электропроводность. В общем, аморфная фаза имеет низкую электропроводность (высокий импеданс) и ассоциирована с состоянием сброса (логический ноль), и кристаллическая фаза имеет высокую электропроводность (низкий импеданс) и ассоциируется с установленным состоянием (логическая единица). Элемент памяти может быть включен в ячейку памяти, которая также включает в себя селектор, то есть устройство выбора, соединенное с элементом памяти. Устройства выбора выполнены с возможностью способствовать комбинированию множества элементов памяти в массив.

Элементы памяти на фазовых переходах могут быть размещены в виде массива памяти с узлами пересечения, включающими в себя адресные линии ряда и адресные линии столбца, размещенные в виде сетки. Адресные линии ряда и адресные линии столбца, называемые линиями слова (WL) и линиями битов (BL) соответственно, пересекаются при формировании сетки, и каждая ячейка памяти соединена между WL и BL, где WL и BL пересекаются (то есть в узлах пересечения). Следует отметить, что ряды и столбцы представляют собой термины, используемые для удобства, для обеспечения качественного описания размещения WL и BL в памяти с узлами пересечения.

Во время операции программирования фаза элемента памяти может изменяться при приложении первого напряжения смещения к WL и второго напряжения смещения к BL, в результате чего, возникает дифференциальное напряжение смещения на ячейке памяти, что может вызвать протекание тока в элементе памяти. Дифференциальное напряжение смещения может поддерживаться на ячейке памяти в течение первого периода времени, достаточного для того, чтобы элемент памяти быстро "выполнил скачкообразный переход", и затем поддерживается в течение второго периода времени для перехода элемента памяти из аморфного состояния в кристаллическое состояние или из кристаллического состояния в аморфное состояния. Скачкообразный переход представляет собой свойство композитного элемента памяти, который приводит к резкому изменению электропроводности и ассоциированному резкому изменению напряжения на элементе памяти.

При операции считывания целевую ячейку памяти выбирают путем приложения первого напряжения смещения к WL и второго напряжения смещения к BL, которые пересекаются в целевой ячейке памяти в течение определенного интервала времени. Получаемое в результате дифференциальное напряжение смещения на элементе памяти конфигурируют так, чтобы оно было выше, чем максимальное напряжение установки, и ниже, чем минимальное напряжение сброса для элемента памяти. В ответ на это целевой элемент памяти может выполнять скачкообразный переход или может не выполнять скачкообразный переход, в зависимости от того, находится ли элемент памяти в кристаллическом состоянии (установленном состоянии) или аморфном состоянии (сброшенном состоянии). Цепи опроса (включая в себя узел опроса), соединенные с элементом памяти, выполнены с возможностью детектирования присутствия или отсутствия скачкообразного перехода в течение интервала времени опроса. Наличие скачкообразного перехода может затем быть интерпретировано как логическая единица и отсутствие скачкообразного перехода как логический ноль.

Краткое описание чертежей

Свойства и преимущества заявленного предмета изобретения будут понятны из следующего подробного описания вариантов осуществления, последовательно изложенных здесь, и это описание следует рассматривать со ссылкой на приложенные чертежи, на которых:

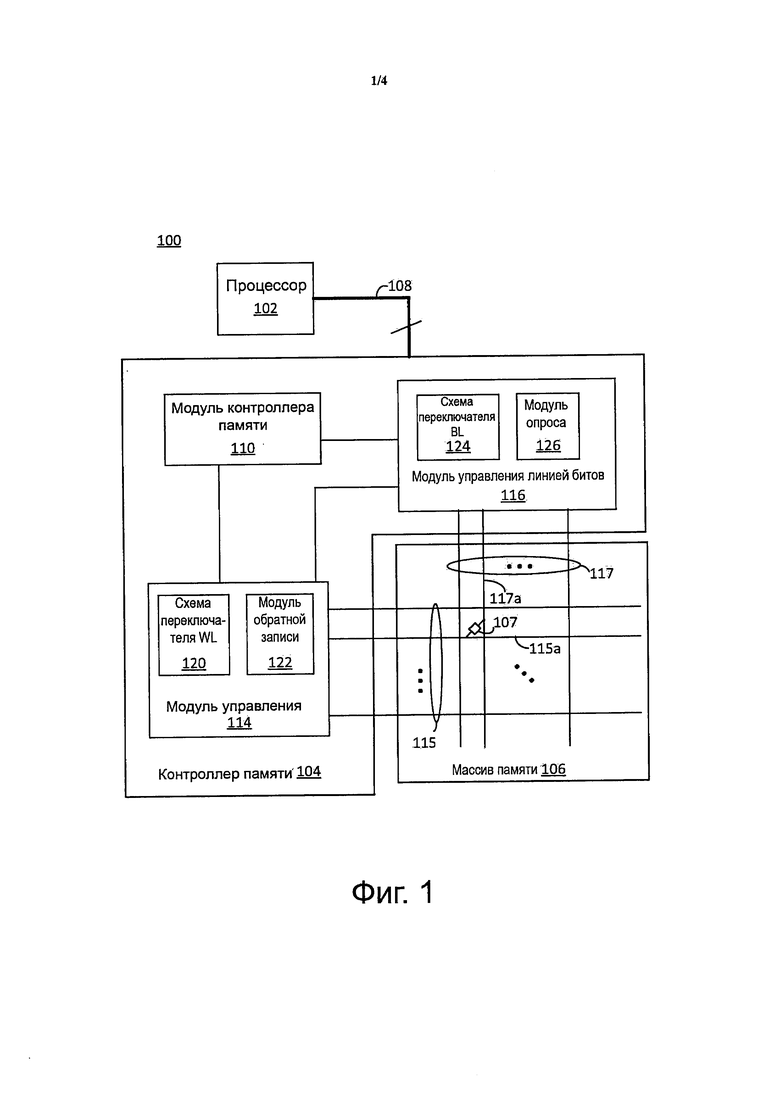

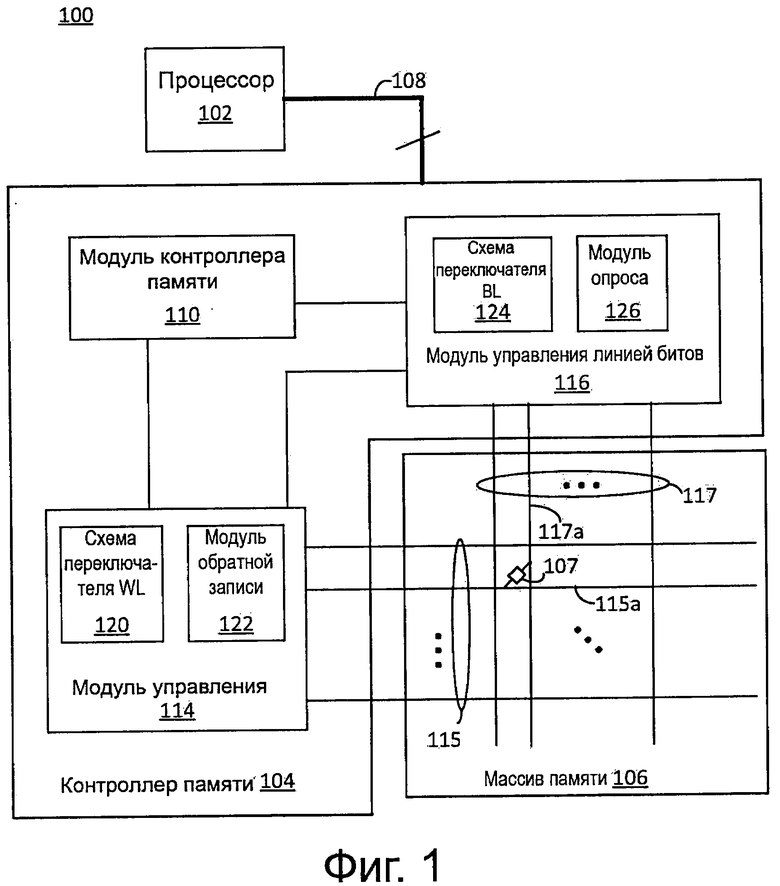

на фиг. 1 показана блок-схема системы в соответствии с несколькими вариантами осуществления настоящего раскрытия;

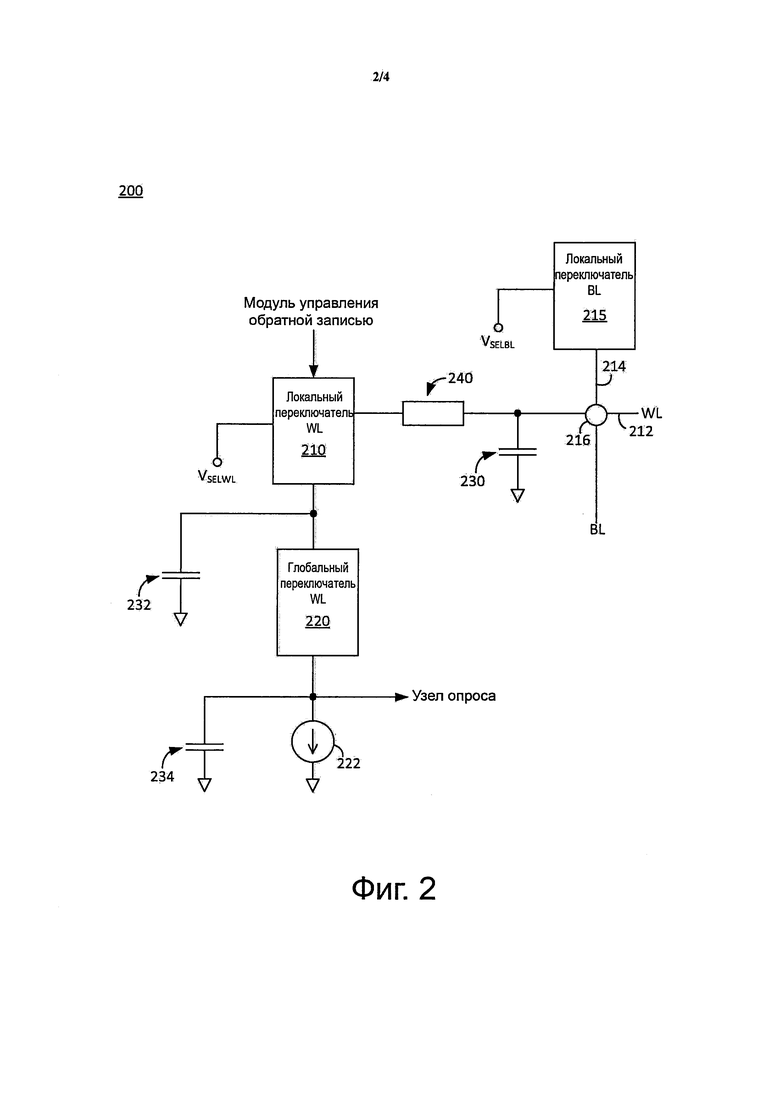

на фиг. 2 показана часть системы памяти с узлами пересечения в соответствии с одним вариантом осуществления настоящего раскрытия;

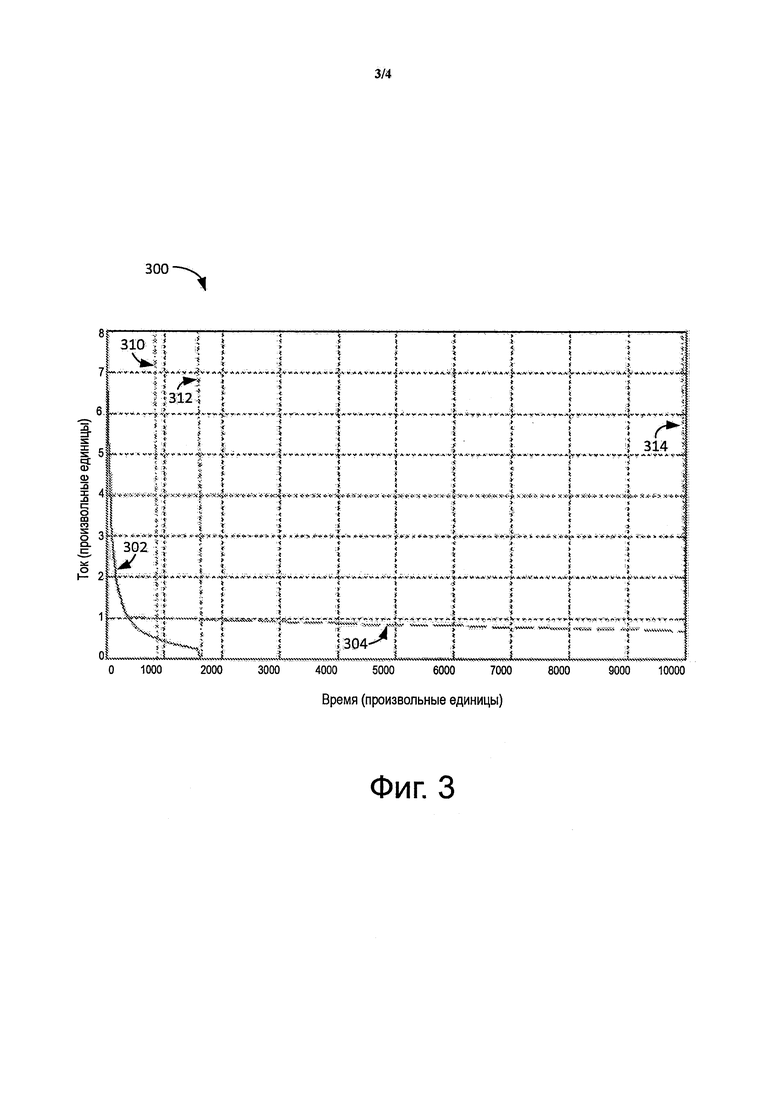

на фиг. 3 представлен график, поясняющий сравнение профилей тока ячейки памяти для ячейки памяти в установленном состоянии; и

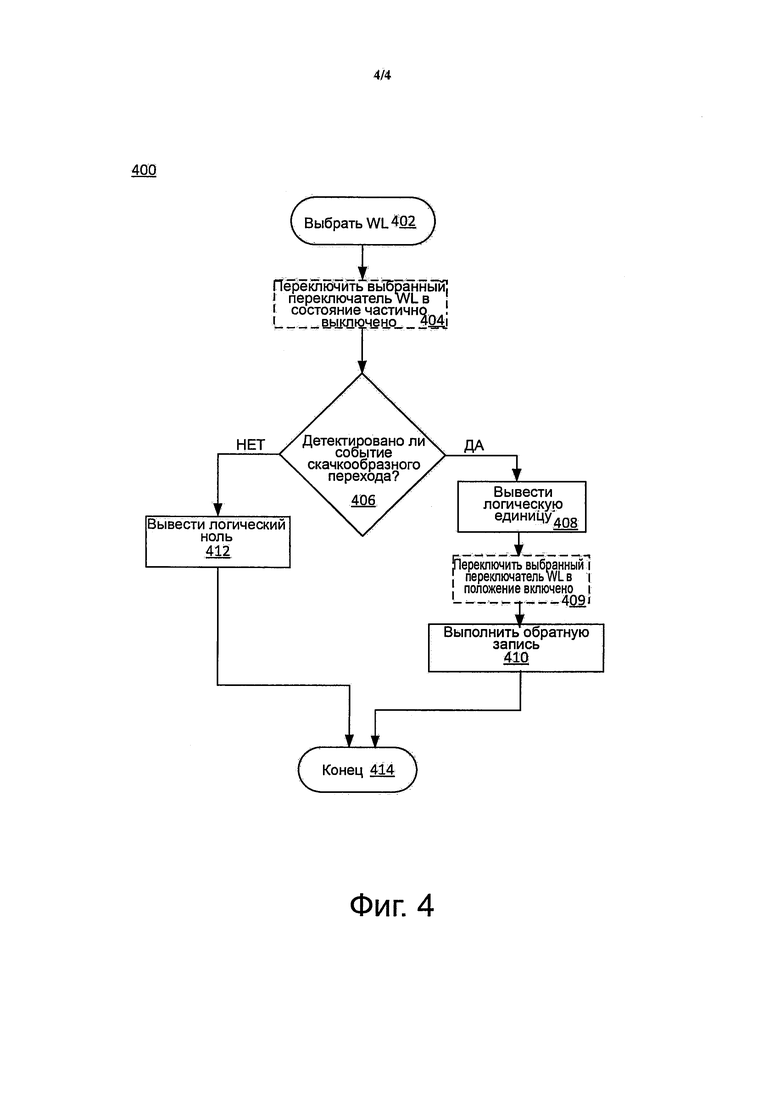

на фиг. 4 показана блок-схема последовательности операций для уменьшения разрушения током считывания в соответствии с различными вариантами осуществления настоящего раскрытия.

Хотя следующее подробное описание изобретения будет представлено со ссылкой на иллюстративные варианты осуществления, множество альтернатив, модификаций и их вариантов будут понятными для специалиста в данной области техники.

Подробное описание изобретения

Во время операции считывания элемента памяти в установленном состоянии скачкообразный переход может привести к "разрушению током считывания", то есть к неустойчивому программированию элемента памяти из установленного состояния в состояние сброса. Резкое изменение напряжения, связанное со скачкообразным переходом, в комбинации с эффективной емкостью, ассоциированной со схемой памяти (например, электроды, линии битов, линии слова и т.д.) приводит к выбросу тока со скоростью затухания (то есть с постоянной времени RC), которая связана с эффективной емкостью. Ток может затем привести к нагреву элемента памяти и неустойчивому программированию. Такое разрушение током считывания может быть уменьшено при уменьшении эффективной емкости элемента памяти путем, например, отсоединения целевого WE от источника (источников) напряжения во время интервала опроса. Однако, по мере продолжения масштабирования массива ячеек памяти, эффективная емкость может увеличиваться из-за увеличения размера ячеек, для поддержания эффективности массива, и/или из-за уменьшения шага ячеек, ассоциированного с масштабированием.

Граница опроса также связана с эффективной емкостью. Узел опроса может быть соединен с целевой ячейкой памяти во время интервала опроса. Сигнал опроса, то есть напряжение и/или ток, детектируемый в узле опроса, может быть затем связан с состоянием ячейки памяти. Например, в вначале интервала опроса напряжение на ячейке памяти может соответствовать дифференциальному напряжению смещения, прикладываемому к ячейке памяти для операции считывания. Для того чтобы ячейка памяти находилась в состоянии сброса, такое напряжение должно оставаться без изменения в течение интервала опроса и сигнал, детектируемый в узле опроса, также может оставаться без изменения. Когда ячейка памяти находится в установленном состоянии, ячейка памяти может восстанавливаться во время интервала опроса, что приводит к относительно значительным изменениям напряжения на ячейке памяти, в то время как ток протекает через ячейку памяти. Дифференциальное напряжение на ячейке памяти может затем уменьшиться, и такое изменение напряжения можно детектировать в узле опроса. Таким образом, изменение напряжения соответствует событию скачкообразного перехода (состояние ячейки памяти: установлено), и отсутствие изменения напряжения соответствует отсутствию события скачкообразного перехода (состояние ячейки памяти: сброшено). Запас опроса представляет собой разность между сигналом опроса, который соответствует ячейке памяти в состоянии сброса, и сигналом опроса, который соответствует ячейке памяти в установленном состоянии.

Напряжение (V) на ячейке памяти, вырабатываемое во время события скачкообразного перехода, связано с эффективной емкостью (С), и заряд (Q) соответствует VC=Q, если предполагать, что напряжение не зависит от емкости. Напряжение, вырабатываемое во время события скачкообразного перехода, может быть независимым от емкости, когда, по меньшей мере, одна из BL и WL не является неподсоединенной. Сигнал опроса может затем соответствовать передаче заряда Q из ячейки памяти в узел опроса. Заряд Q пропорционален емкости С, так если С относительно велика, тогда заряд Q относительно большой для того же напряжения V. Увеличенный заряд Q может затем привести к относительно большому запасу опроса и уменьшенной чувствительности к шумам в системе опроса. В случае разрушения током считывания, увеличенный заряд Q вырабатываемый во время скачкообразного перехода, соответствует увеличенному току через ячейку памяти и повышенной вероятности разрушения током считывания. Ухудшение эффективной емкости также уменьшает зазор опроса, что приводит к компромиссу между уменьшением эффективной емкости для уменьшения разрушения током считывания и поддержанием эффективной емкости для поддержания зазора опроса.

В общем, в данном раскрытии описаны система и способ, выполненные с возможностью уменьшения разрушения током считывания (то есть неустойчивого программирования) во время скачкообразного перехода, ассоциированного со считыванием элемента памяти, который находится в установленном состоянии (то есть содержит логическую единицу). Способ и система выполнены с возможностью вывода логической единицы и обратной записи логической единицы в элемент памяти в ответ на скачкообразный переход. Способ и система дополнительно выполнены с возможностью поддержания соединения (то есть выбора) выбранной WL (линии слова) с источником напряжения выбора WL во время интервала опроса. Например, локальным переключателем выбора WL, выполненным с возможностью соединения выбранной WL с источником напряжения выбора WL, можно управлять для его включения, или частичного отключения во время, по меньшей мере, части интервала опроса. Если локальный переключатель выбора WL частично отключен, он может быть включен в ответ на детектирование скачкообразного перехода. Частично отключенный локальный переключатель выбора WL выполнен с возможностью уменьшения интервала времени обратной записи (то есть длительности времени операции обратной записи) и, таким образом, ассоциированного интервала времени завершения считывания. Интервал времени завершения считывания начинается в начале интервала опроса и заканчивается при завершении операции обратной записи. Локальный переключатель выбора WL в состоянии включено выполнен с возможностью уменьшения задержки при считывании (то есть интервала времени, начиная с инициирования операции считывания и заканчивая, когда готовы считанные датчиком данные). Если детектируется скачкообразный переход, после скачкообразного перехода напряжение локального источника WL может перейти к импульсу типа SET (установки), для перекристаллизации элемента памяти и исключения любого разрушения током считывания (то есть аморфизации), которое могло возникнуть во время операции считывания.

Способ и система дополнительно выполнены с возможностью поддержания зазора опроса путем поддержания эффективной емкости. Эффективная емкость включает в себя паразитную емкость, емкость связи и/или емкость электрода, ассоциированную с целевой WL (или линией битов (BL)).

В дальнейшем технологии для смягчения разрушения током считывания описаны со ссылкой на линии слова. Аналогичные технологии могут использоваться для смягчения разрушения током считывания в памяти с узлами пересечения для линий битов, в соответствии с настоящим раскрытием.

На фиг. 1 иллюстрируется блок-схема системы 100 в соответствии с несколькими вариантами осуществления настоящего раскрытия. Система 100 включает в себя процессор 102, контроллер 104 памяти и массив 106 памяти. Процессор 102 соединен с контроллером памяти 104 по шине 108. Процессор 102 может предоставлять запросы считывания и/или записи, включая в себя адрес (адреса) памяти, и/или ассоциированные данные в контроллер 104 памяти и может принимать считанные данные из контроллера 104 памяти. Контроллер 104 памяти выполнен с возможностью выполнения операции доступа к памяти, например считывания целевой ячейки памяти и/или записи в целевую ячейку памяти. Следует отметить, что система 100 представлена упрощенной для простоты иллюстрации и описания.

Массив 106 памяти соответствует, по меньшей мере, части памяти с узлами пересечения на фазовых переходах и включает в себя множество линий 115 слова, множество линий 117 битов и множество ячеек памяти, например ячеек памяти 107. Каждая ячейка памяти соединена между линией слова ("WL") и линией битов ("BL") в узле пересечения WL и BL. Каждая ячейка памяти включает в себя элемент памяти, выполненный с возможностью сохранения информации, и может включать в себя устройство выбора ячейки памяти (то есть селектор), соединенный с элементом памяти. Устройства могут включать в себя аморфно-полупроводниковые пороговые переключатели, диоды, транзисторы с биполярными переходами, полевые транзисторы и т.д. Массив 106 памяти выполнен с возможностью сохранения двоичных данных, и в нем можно выполнять запись (то есть программировать) или считывать из него данные.

Контроллер 104 памяти включает в себя модуль 110 контроллера памяти, модуль WL управления 114 и модуль 116 управления BL. Модуль 110 контроллера памяти выполнен с возможностью выполнения операций, ассоциированных с контроллером 104 памяти. Например, модуль 110 контроллера памяти может администрировать обменом данными с процессором 102. Модуль 110 контроллера памяти может быть выполнен с возможностью идентификации одной или больше целевых WL, ассоциированных с каждым принятым адресом памяти. Модуль 110 контроллера памяти может быть выполнен с возможностью администрирования работой модуля 114 управления WL и модуля 116 управления BL на основе, по меньшей мере, частично, идентификаторов целевых WL.

Модуль 114 управления WL включает в себя схему 120 переключения WL и модуль 122 обратной записи. В некоторых вариантах осуществления модуль 114 управления WL может включать в себя модуль опроса, например модуль 126 опроса, показанный в модуле 116 управления BL. Модуль 114 управления WL выполнен с возможностью приема целевого адреса (адресов) WL из модуля 110 контроллера памяти и выбора одной или больше WL для операций считывания и/или записи. Модуль 114 управления WL может быть выполнен с возможностью выбора целевой WL путем подключения напряжения смещения выбора WL VSELWL к целевой WL и может быть выполнен с возможностью отмены выбора WL путем соединения напряжения смещения отмены выбора WL VDESWL к WL. Модуль 114 управления WL может быть соединен с множеством WL 115, включенных в массив 106 памяти. Каждая WL может быть соединена с множеством ячеек памяти, соответствующих количеству BL 117.

Схема 120 переключения WL может включать в себя множество переключателей, каждый переключатель выполнен с возможностью подключения (или отсоединения), соответствующей WL, например WL 115а, к VSELWL, для выбора соответствующей WL 115а. Например, схема 120 переключения может включать в себя множество транзисторов. В некоторых вариантах осуществления схема 120 переключения WL может включать в себя переключатели, которые выполнены с возможностью иметь полное состояние включено, полное состояние выключено и/или состояние частично выключено. Полное состояние включено соответствует очень низкому импедансу (например, короткому замыканию), и полное состояние выключено соответствует очень высокому импедансу (например, разрыву цепи). Состояние частично выключено соответствует состоянию проводимости между разомкнутым и замкнутым состояниями.

Модуль 126 опроса выполнен с возможностью детектировать событие скачкообразного перехода, например, во время операции считывания и передачи события скачкообразного перехода, например, в контроллер 110 памяти и/или в модуль 122 обратной записи. Модуль 122 обратной записи выполнен с возможностью управления схемой 120 переключения WF для поддержания выбранной ячейки памяти, например ячейки памяти 107, соединенной с VSELWL в течение интервала времени достаточной длительности для того, чтобы запрограммировать ячейку 107 памяти обратно в установленное состояние. Модуль 122 обратной записи выполнен с возможностью управления схемой 120 отключения в ответ на событие скачкообразного перехода во время операции считывания.

Модуль 116 управления BF включает в себя схему 124 переключения BF. Модуль 116 управления BF может включать в себя модуль 126 опроса. В некоторых вариантах осуществления модуль 116 управления BF может включать в себя модуль обратной записи, например модуль 122 обратной записи. В некоторых вариантах осуществления модуль 114 управления WF может включать в себя модуль 126 опроса. Модуль 116 управления BF выполнен с возможностью выбора одной или больше BF для операций считывания и/или записи. Модуль 116 управления BF может быть выполнен с возможностью выбора целевого BF путем подключения напряжения смещения выбора BF VSELBL к целевому BF и может быть выполнен с возможностью отмены выбора BF путем соединения напряжения смещения отмены выбора BF VDESBL от BF. Схема 124 переключения BF аналогична схеме 120 отключения WF, кроме схемы коммутатора BF 124, которая выполнена с возможностью подключения VSELBL к целевому BL.

Например, в ответ на сигнал из модуля 110 контроллера памяти, модуль 114 управления WL и модуль 116 управления BL могут быть выполнены с возможностью выбора целевой ячейки памяти, например ячейки памяти 107, для операции считывания путем подключения WL 115а к VSELWL и BL 117а к VSELBL. Модуль 126 опроса может быть затем выполнен с возможностью отслеживания WL 115а и/или BL 117а для интервала опроса, для определения, возникло или нет событие скачкообразного перехода. Если модуль 126 опроса детектирует событие скачкообразного перехода, тогда ячейка 107 памяти может находиться в установленном состоянии, и модуль 122 обратной записи может быть выполнен с возможностью программировать ячейку 107 памяти в установленное состояние. Если модуль 126 опроса не детектирует событие скачкообразного перехода в интервале опроса, тогда ячейка 107 памяти может находиться в состоянии сброса, и ячейка 107 памяти не может быть запрограммирована модулем 122 обратной записи в ответ на ассоциированную операцию считывания.

Таким образом, модуль 114 управления WL и/или модуль 116 управления BL могут быть выполнены с возможностью выбора целевой ячейки памяти для операции считывания, инициирования операции считывания, отслеживания выбранной ячейки памяти в отношении события скачкообразного перехода в течение интервала опроса и программирования выбранной ячейки памяти, если детектируется событие скачкообразного перехода во время интервала опроса. Таким образом, разрушение током считывания может быть уменьшено с помощью операции обратной записи.

На фиг. 2 иллюстрируется часть 200 системы памяти с узлами пересечения, в соответствии с одним вариантом осуществления настоящего раскрытия. Часть 200 включает в себя локальный переключатель 210 WL, локальный переключатель 215 BL, глобальный переключатель 220 WL, токовое зеркало 222 и WL 212, и BL 214, которые пересекаются в и соединены с ячейкой 216 памяти. Часть 200 дополнительно включает в себя множество емкостей 230, 232, 234. Глобальный переключатель 220 WL в состоянии включено выполнен с возможностью обеспечивать пути опроса между ячейкой 216 памятии узлом опроса, когда локальный переключатель 210 WL также находится в состоянии включено (или частично выключено).

Емкости 230, 232, 234 соответствуют паразитным емкостям, ассоциированным с частью 200 системы памяти с узлами пересечения. Емкость 230 соответствует емкости WL 212, от ячейки 216 памяти до локального переключателя 210 WL. Емкость 232 соответствует емкости цепи между локальным переключателем 210 WL, и глобальным переключателем 220 WL. Емкость 234 соответствует емкости, ассоциированной с центральным узлом цепи, который соединен с множеством глобальных WL (не показана). Таким образом, емкости 230, 232, 234 относятся к направлению, устройствам и/или локальным соединениям, ассоциированным с системами памяти, с узлами пересечения.

В некоторых вариантах осуществления часть 200 может включать в себя сопротивление 240. Сопротивление 240 может быть добавлено последовательно между локальным переключателем 210 WL и WL 212, для изоляции других емкостей, соединенных с ячейкой 216 памяти. Эти другие емкости могут заряжаться в ответ на протекание тока, но их токи заряда могут быть ограничены сопротивлением 240, в соответствии с постоянной времени RC, где R представляет собой значение сопротивления для сопротивления 240, и С представляет собой значение емкости, ассоциированное с каждой из других емкостей.

Токовое зеркало 222 выполнено с возможностью способствовать обработке обратной записи после события скачкообразного перехода в течение операции считывания, как описано здесь. Токовое зеркало 222 выполнено с возможностью подачи тока, сконфигурированного для установки ячейки 216 памяти (другими словами, обратной записи), если был детектирован скачкообразный переход.

Локальный переключатель 210 WL выполнен с возможностью соединения 212 WL с напряжением VSELWL выбора WL, и локальный переключатель 215 BL выполнен с возможностью соединения BL 214 с напряжением VSELBL выбора BL. Например, VSELWL может быть соединено с WL 212, и VSELBL может быть соединено с BL 214, в ответ на запрос считывания, который включает в себя ячейку 216 памяти. Первоначально, глобальный переключатель 220 WL, локальный переключатель 210 WL и локальный переключатель 215 BL могут быть выключены, и WL 212 может быть соединена с напряжением VDESWL отмены выбора WL (не показано) и BL 214 может быть соединена с напряжением VDESBL отмены выбора BL (не показано). В ответ на запрос считывания глобальный переключатель 220 WL может быть включен для соединения узла опроса с локальным переключателем 210 WL, локальный переключатель 215 BL может быть включен для соединения BL 214 с VSELBL, и локальный переключатель 210 WL может быть включен для соединения WL 212 с VSELWL и глобальным переключателем 220 WL. После интервала времени, сконфигурированного так, чтобы обеспечить возможность достижения установления в емкостях 230, 232, 234 динамического равновесия (то есть их заряда), может начаться интервал опроса. В варианте осуществления локальный переключатель 210 WL может оставаться в положении включено (то есть в состоянии низкого импеданса) во время интервала опроса. В другом варианте осуществления локальным переключателем 210 WL можно управлять так, чтобы он находился в состоянии частично выключено (то есть в контролируемом промежуточном состоянии импеданса) во время или близко к началу интервала опроса, и поддерживать частично состояние выключено в течение интервала опроса, если не происходит скачкообразный переход (то есть сброс состояния ячейки памяти) или он может быть полностью включен в ответ на событие скачкообразного перехода. Управление локальным переключателем 210 WL так, чтобы он находился в состоянии частично выключено, сконфигурировано для уменьшения эффективной емкости во время интервала опроса (и события скачкообразного перехода, если происходит). Управление локальным переключателем 210 WL так, чтобы он находился в состоянии частично выключено, дополнительно сконфигурировано для уменьшения времени обратной записи (по сравнению с полностью отключенным локальным переключателем 210 WL во время интервала опроса) и, таким образом, времени окончания считывания. Частично выключенный локальный переключатель 210 WL соответствует повышенному эффективному сопротивлению переключателя 210 (по сравнению с относительно низким импедансом переключателя в состоянии полностью отключено). Повышенное эффективное сопротивление управляет (ограничивает) максимальным током, который может протекать через локальный переключатель 210 WL. Другими словами, локальный переключатель 210 WL в состоянии частично выключено действует, как сопротивление ограничения тока. Таким образом, хотя относительно большие емкости, ассоциированные с цепью, соединены с локальным переключателем 210 выбора WL, пиковый ток, который может протекать через ячейку, ограничен частично выключенным переключателем 210. Период времени, ассоциированный с зарядом относительно большей емкости с протекающим ограниченным током, может быть относительно длинным. Состояние ячеек памяти с узлами пересечения, в соответствии с настоящим раскрытием, может быть нарушено относительно высокими токами, таким образом, ограничивая ток в течение продленного периода времени, что позволяет ограничить разрушение током считывания.

Поддержание локального переключателя 210 WL в состоянии включено во время интервала опроса конфигурируют для уменьшения задержки считывания (то есть готовности считывания данных датчика). Поддержание локального переключателя 210 WL в состоянии включено способствует разработке сигнала опроса в узле опроса, когда локальный переключатель 210 WL, находящийся в состоянии включено, позволяет протекать току через него, и этот ток может быть детектирован схемой опроса, например модулем 126 опроса. Если детектируется скачкообразный переход, определяющий результат считывания, тогда может быть инициирована обратная запись, как описано здесь.

Модуль опроса, например, модуль 126 опроса на фиг. 1, может быть соединен с узлом опроса и может быть выполнен с возможностью определения, возникло или нет событие скачкообразного перехода во время интервала опроса. Если был детектирован скачкообразный переход, тогда ячейка 216 памяти может находиться в состоянии установлено, и модуль управления обратной записью выполнен с возможностью управления локальным переключателем WL 210, для записи (то есть программирования) логической единицы в ячейку 216 памяти. Одно событие скачкообразного перехода может привести только к частичному разрушению током считывания таким образом, что модуль управления обратной записью может быть выполнен с возможностью подачи менее чем полного импульса SET (частичный импульс SET) в ячейку 216 памяти. Подача менее чем полного импульса SET выполняется так, чтобы уменьшить и/или минимизировать эффект задержки считывания, ассоциированный с обратной записью. Длительность полного импульса SET может повлиять на задержку считывания и может повлиять на полосу пропускания считывания (количество считываний, которые могут быть выполнены в интервале времени). Длительность частичного импульса SET меньше, чем длительность полного импульса SET. Частичный импульс SET сформирован так, чтобы установить ячейку 216 памяти после события скачкообразного перехода, ассоциированного с операцией считывания, выполненной так, чтобы уменьшить разрушение током считывания, в соответствии с настоящим раскрытием. Эффекты задержки считывания могут быть дополнительно уменьшены путем передачи данных о состоянии ячейки памяти (то есть логической единицы), как только детектируют скачкообразный переход и обеспечения возможности продолжения обратной записи в фоновом режиме. Если скачкообразный переход не был детектирован в течение интервала опроса, тогда ячейка 216 памяти может находиться в состоянии сброса и обратная запись может не быть инициирована. В этом случае, может быть выведен логический ноль.

На фиг. 3 показан график 300, иллюстрирующий сравнение профилей тока ячеек памяти для ячейки памяти в установленном состоянии. График 300 составлен так, чтобы иллюстрировать относительные уровни тока и относительное время между системой, сконфигурированной для разрыва (то есть для полного отключения) соответствующего локального переключателя WL, например локального переключателя 210 WL, во время интервала опроса, и система выполнена для поддержания локального переключателя WL в состоянии включено или частично выключено, как описано здесь. Таким образом, вертикальная ось соответствует току в произвольных единицах (а.u), и горизонтальная ось соответствует времени в произвольных единицах (а.u). Форма 302 колебаний представляет событие скачкообразного перехода, ассоциированное с операцией считывания, когда соответствующий локальный переключатель WL полностью выключен. Форма 304 колебаний иллюстрирует текущий профиль, следующий после события скачкообразного перехода, когда локальный переключатель WL поддерживает состояние включено, или им управляют, чтобы он был частично выключен во время события скачкообразного перехода, и поддерживают в состоянии включено до тех пор, пока не закончится обратная запись. Время 310 соответствует задержке считывания (то есть считанные датчиком данные готовы), и операция считывания заканчивается для формы 302 колебаний. Время 312 соответствует задержке для способа и системы, в соответствии с настоящим раскрытием, и время 314 соответствует времени завершения считывания (то есть операция считывания завершена). Следует отметить, что время 314 включает в себя интервал времени, ассоциированный с операцией обратной записи, как описано здесь. Таким образом, логическая единица могла быть выведена перед временем 314, например во время или близко ко времени 312.

Время 310 соответствует готовому считыванию данных датчика, когда ячейка памяти, например ячейка памяти 107 на фиг. 1 и/или ячейка памяти 216 на фиг. 2, находится в состоянии сброса (то есть содержит логический ноль), независимо от того, включен или выключен соответствующий локальный переключатель WL. Другими словами, когда ячейка памяти находится в состоянии сброса, ячейка памяти остается в состоянии высокого импеданса и дифференциальное напряжение смещения (то есть VSELBL минус VSELWL) недостаточно для вызова скачкообразного перехода, таким образом, ток может не протекать через ячейку памяти.

На фиг. 4 иллюстрируется блок-схема 400 последовательности операций для операций уменьшения разрушения током считывания в памяти с узлами пересечения, в соответствии с различными вариантами осуществления настоящего раскрытия. Операции могут быть выполнены, например, контроллером памяти, например контроллером 104 памяти, включающим в себя модуль 114 управления WL и модуль 116 управления BL. В блок-схеме 400 последовательности операций представлены примеры операций, выполненные так, чтобы уменьшить разрушение током считывания. В частности, в блок-схеме 400 последовательности операций представлены примерные операции для выполнения обратной записи логической единицы в ячейку памяти, если был детектирован скачкообразный переход (это значит, что ячейка памяти находится в установленном состоянии), как описано здесь.

Операции, в соответствии с блок-схемой 400 последовательности операций, могут начаться с выбора WL во время операции 402. Например, WL может быть выбрана путем соединения WL с напряжением выбора WL через локальный переключатель WL. Например, локальный переключатель WL может представлять собой транзистор, и он может переходить из состояния выключено в состояние включено для соединения WL с напряжением выбора WL. В некоторых вариантах осуществления выбранный переключатель WL может переходить в состояние частично выключено при операции 404. Переход выбранного переключателя WL из состояния включено в состояние частично выключено конфигурируют так, чтобы уменьшить эффективную емкость WL во время интервала опроса, как описано здесь. Было ли детектировано событие скачкообразного перехода, можно определять в ходе операции 406. Возникновение события скачкообразного перехода конфигурируют так, чтобы оно обозначало, что состояние ассоциированной ячейки памяти представляет собой логическую единицу. Если детектируется событие скачкообразного перехода, логическая единица может быть выведена во время операции 408. В вариантах осуществления, которые включают в себя операцию 404, выбранный переключатель WL может быть включен в ходе операции 409. Обратная запись логической единицы может выполняться во время операции 410. Например, обратная запись может включать в себя переход локального переключателя WL в состояние полностью включено, если он частично выключен, когда происходит скачкообразный переход. В другом примере, обратная запись может включать в себя поддержание локального переключателя WL в состоянии полностью включено до тех пор, пока не будет закончена обратная запись. Поток обработки программы может затем закончиться во время операции 414. Если событие скачкообразного перехода не было детектировано, логический ноль может быть выведен в ходе операции 412. Поток программы может затем заканчиваться во время операции 414.

Таким образом, операции, в соответствии с блок-схемой 400 последовательности операций, выполнены так, чтобы инициировать операцию считывания для целевой ячейки памяти и вывод логической единицы и обратную запись логической единицы, если было детектировано событие скачкообразного перехода. Можно приспособиться к разрушению током считывания в результате события скачкообразного перехода (то есть оно может быть уменьшено) путем обратной записи логической единицы в ячейку памяти.

В то время как на фиг. 4 иллюстрируются различные операции, в соответствии с одним вариантом осуществления, следует понимать, что не все из операций, представленных на фиг. 4, являются необходимыми для других вариантов осуществления. Действительно, здесь совершенно понятно, что в других вариантах осуществления настоящего раскрытия, операции, представленные на фиг. 4, и/или другие операции, описанные здесь, могут быть скомбинированы таким образом, как, в частности, не представлено на любом из чертежей, но все еще в полном соответствии с настоящим раскрытием. Таким образом, пункты формулы изобретения, направленные на свойства и/или операции, которые точно не показаны на одном чертеже, рассматриваются как находящиеся в пределах объема и содержания настоящего раскрытия.

Используемый в любом варианте осуществления, представленном здесь, термин "модуль" может относиться к программному приложению, программному обеспечению, встроенному программному обеспечению и/или схеме, сконфигурированной для выполнения любой из упомянутых выше операций. Программное обеспечение может быть воплощено, как программный пакет, код, инструкции, наборы инструкций и/или данные, записанные на непереходном считываемом компьютером носителе информации. Встроенное программное обеспечение может быть воплощено как код, инструкции или набор инструкций, и/или данные, которые жестко закодированы (например, являются энергонезависимыми) в запоминающих устройствах.

"Схема", используемая в любом из представленных здесь вариантов осуществления, может содержать, например, одну или любую комбинацию из соединенных проводами схем, программируемых схем, таких как компьютерные процессоры, содержащие один или больше индивидуальных ядер для обработки инструкций, схема конечного автомата, и/или встроенное программное обеспечение, которое содержит инструкции, выполняемые программируемой схемой. Модули могут быть совместно или индивидуально внедрены, как схема, которая формирует часть более крупной системы, например интегральная схема (IC), система на кристалле (SoC), настольные компьютеры, переносные компьютеры, планшетные компьютеры, серверы, смартфоны и т.д.

В некоторых вариантах осуществления язык описания аппаратных средств может использоваться для установления схемного и/или логического варианта (вариантов) осуществления для различных модулей и/или схем, описанных здесь. Например, в одном варианте осуществления язык описания аппаратных средств может соответствовать или может быть совместим с языком (VHDL) описания аппаратных средств с высокоскоростными интегральными схемами (VHSIC), которые могут обеспечивать изготовление полупроводников в виде одной или больше схем и/или модулей, описанных здесь. VHDL может соответствовать или может быть совместим со стандартом IEEE 1076-1987, стандартом IEEE 1076.2, IEEE1076.1, проектом 3.0 IEEE для VHDL 2006, проектом 4.0 IEEE для VHDL 2008 и/или другими версиями стандартов VHDL IEEE и/или другими стандартами описания аппаратных средств.

Таким образом, система и способ, сконфигурированные для смягчения разрушения током считывания (то есть неустойчивое программирование) в результате скачкообразного перехода, ассоциированного со считыванием элемента памяти, который находится в состоянии установлено (то есть содержит логическую единицу), были описаны выше. Способ и система сконфигурированы для вывода логической единицы и обратной записи логической единицы в ячейку памяти, в ответ на скачкообразный переход. Способ и система дополнительно выполнены с возможностью поддержания соединения выбранной WL (линии слова) с источником напряжения выбора WL во время, по меньшей мере, части интервала опроса.

В соответствии с одним аспектом, предусмотрено устройство. Устройство включает в себя модуль контроллера памяти, выполненный с возможностью выбора целевой ячейки памяти для операции доступа к памяти. Контроллер памяти включает в себя модуль опроса, выполненный с возможностью определения, происходит ли событие скачкообразного перехода во время интервала опроса; и модуль обратной записи, выполненный с возможностью обратной записи логической единицы в ячейку памяти, если детектируется событие скачкообразного перехода.

В соответствии с другим аспектом, предусмотрен способ. Способ включает в себя выбирают, с помощью контроллера памяти, целевую ячейку памяти для операции доступа к памяти; определяют, с помощью модуля опроса, произошло ли событие скачкообразного перехода в течение интервала опроса; и выполняют обратную запись, с помощью модуля обратной записи, логической единицы в ячейку памяти, если детектировано событие скачкообразного перехода.

В соответствии с другим аспектом, предусмотрена система. Система включает в себя процессор; массив памяти с узлами пересечения, включающий в себя целевую ячейку памяти, целевую линию слова (WL) и целевую линию бита (BL), целевая ячейка памяти соединена между целевой WL и целевой BL; и контроллер памяти, соединенный с процессором и массивом памяти с узлами пересечения. Контроллер памяти выполнен с возможностью выбора целевой ячейки памяти для операции доступа к памяти. Контроллер памяти включает в себя модуль опроса, выполненный с возможностью определения, произошло ли событие скачкообразного перехода во время интервала опроса; и модуль обратной записи, выполненный с возможностью обратной записи логической единицы в ячейку памяти, если детектировано событие скачкообразного перехода.

Различные свойства, аспекты и варианты осуществления были описаны здесь. В отношении свойств, аспектов и вариантов осуществления могут быть выполнены комбинации друг с другом, а также их вариации и модификации, как будет понятно для специалиста в данной области техники. Настоящее раскрытие следует, поэтому, рассматривать, как охватывающее такие комбинации, вариации и модификации.

Изобретение относится к вычислительной технике. Технический результат заключается в уменьшении эффективной емкости элемента памяти. Устройство определения события скачкообразного перехода содержит контроллер памяти, выбирающий целевую ячейку памяти для операции доступа к памяти и содержащий: модуль опроса для определения, происходит ли событие скачкообразного перехода во время интервала опроса интервала времени завершения считывания; и модуль обратной записи для обратной записи логической единицы в ячейку памяти во время интервала времени завершения считывания, в ответ на детектирование события скачкообразного перехода во время интервала времени завершения считывания; и схему переключателя, содержащую переключатель линии слова (WL) для подключения целевой WL к источнику напряжения выбора WL и переключатель линии битов (BL) для подключения целевой BL к источнику напряжения выбора BL; в котором контроллер памяти выполнен с возможностью управления схемой переключателя для частичного выключения, по меньшей мере, одного из переключателя WL и переключателя BL во время или близко к началу интервала опроса и для включения, по меньшей мере, одного из переключателя WL и переключателя BL, в ответ на детектирование события скачкообразного перехода во время интервала времени завершения считывания. 3 н. и 9 з.п. ф-лы, 4 ил.

1. Устройство определения события скачкообразного перехода, содержащее:

контроллер памяти, выполненный с возможностью выбора целевой ячейки памяти для операции доступа к памяти, контроллер памяти, содержащий:

модуль опроса, выполненный с возможностью определения, происходит ли событие скачкообразного перехода во время интервала опроса интервала времени завершения считывания; и

модуль обратной записи, выполненный с возможностью обратной записи логической единицы в ячейку памяти во время интервала времени завершения считывания, в ответ на детектирование события скачкообразного перехода во время интервала времени завершения считывания; и

схему переключателя, содержащую переключатель линии слова (WL), выполненный с возможностью подключения целевой WL к источнику напряжения выбора WL, и переключатель линии битов (BL), выполненный с возможностью подключения целевой BL к источнику напряжения выбора BL;

в котором контроллер памяти выполнен с возможностью управления схемой переключателя для частичного выключения, по меньшей мере, одного из переключателя WL и переключателя BL во время или близко к началу интервала опроса и для включения, по меньшей мере, одного из переключателя WL и переключателя BL, в ответ на детектирование события скачкообразного перехода во время интервала времени завершения считывания.

2. Устройство по п. 1, в котором контроллер памяти выполнен с возможностью управления схемой переключателя для включения переключателя WL и переключателя BL перед началом интервала опроса.

3. Устройство по п. 1, в котором контроллер памяти выполнен с возможностью вывода логической единицы, если детектировано событие скачкообразного перехода.

4. Устройство по п. 1, в котором контроллер памяти выполнен с возможностью вывода логического нуля, если событие скачкообразного перехода не детектировано.

5. Способ определения события скачкообразного перехода, содержащий:

выбирают, с помощью контроллера памяти, целевую ячейку памяти для операции доступа к памяти;

определяют, с помощью модуля опроса, произошло ли событие скачкообразного перехода в течение интервала опроса интервала времени завершения считывания;

выполняют обратную запись, с помощью модуля обратной записи, логической единицы в ячейку памяти, при детектировании события скачкообразного перехода во время интервала времени завершения считывания;

управляют, с помощью контроллера памяти, схемой переключателя для частичного выключения, по меньшей мере, одного из переключателя WL и переключателя BL во время или близко к началу интервала опроса; и

управляют, с помощью контроллера памяти, схемой переключателя для включения, по меньшей мере, одного из переключателя WL и переключателя BL, в ответ на детектирование события скачкообразного перехода во время интервала времени завершения считывания.

6. Способ по п. 5, дополнительно содержащий:

управляют, с помощью контроллера памяти, схемой переключателя для включения переключателя линии слова (WL) и линии битов (BL) перед началом интервала опроса.

7. Способ по п. 5, дополнительно содержащий:

выводят, с помощью контроллера памяти, логическую единицу, если детектировано событие скачкообразного перехода.

8. Способ по п. 5, дополнительно содержащий:

выводят, с помощью контроллера памяти, логический ноль, если событие скачкообразного перехода не было детектировано.

9. Система определения события скачкообразного перехода, содержащая:

процессор;

массив памяти с узлами пересечения, включающий в себя целевую ячейку памяти, целевую линию слова (WL) и целевую линию бита (BL), целевая ячейка памяти соединена между целевой WL и целевой BL;

контроллер памяти, соединенный с процессором и массивом памяти с узлами пересечения, контроллер памяти выполнен с возможностью выбора целевой ячейки памяти для операции доступа к памяти, контроллер памяти, содержащий:

модуль опроса, выполненный с возможностью определения, произошло ли событие скачкообразного перехода во время интервала опроса интервала времени завершения считывания; и

модуль обратной записи, выполненный с возможностью обратной записи логической единицы в ячейку памяти во время интервала времени завершения считывания, в ответ на детектирование события скачкообразного перехода во время интервала времени завершения считывания; и

схему переключателя, содержащую переключатель линии слова (WL), выполненный с возможностью подключения целевой WL к источнику напряжения выбора WL, и переключатель линии битов (BL), выполненный с возможностью подключения целевой BL к источнику напряжения выбора BL;

в котором контроллер памяти выполнен с возможностью управления схемой переключателя для частичного выключения, по меньшей мере, одного из переключателя WL и переключателя BL во время или близко к началу интервала опроса и для включения, по меньшей мере, одного из переключателя WL и переключателя BL, в ответ на детектирование события скачкообразного перехода во время интервала времени завершения считывания.

10. Система по п. 9, в которой контроллер памяти выполнен с возможностью управления схемой переключателя для установки переключателя WL и переключателя BL в состояние включено перед началом интервала опроса.

11. Система по п. 9, в которой контроллер памяти выполнен с возможностью вывода логической единица, если детектировано событие скачкообразного перехода.

12. Система по п. 9, в которой контроллер памяти выполнен с возможностью вывода логического нуля, если не детектировано событие скачкообразного перехода.

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| US 6222787 B1, 24.04.2001 | |||

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| НЕРАЗРУШАЮЩЕЕ СЧИТЫВАНИЕ | 2002 |

|

RU2263359C2 |

Авторы

Даты

2018-05-07—Публикация

2015-03-09—Подача