Изобретение относится к способу и устройству согласно ограничительной части пункта 1 и, соответственно, 7 формулы изобретения.

Транспортные сети синхронной цифровой иерархии (SDH (в США SONET) (см., например, [5]) отличаются тем, что все используемые элементы сети в обычном режиме работают с единой, централизованно выработанной частотой синхронизации, которая выделяется элементом сети из потока данных выбираемого входного сигнала. Благодаря этому на основе сети передачи данных любой структуры может быть построена древовидная частотно распределенная сеть. На основании передаваемой в сигнале информации, которая указывает качество частоты соответствующего потока данных, при появлении помех можно автоматически переключаться на лучший запасной источник частоты. В точках перехода от транспортных SDH-сетей к сетям плезиохронной цифровой иерархии (PDH) предусмотрены мультиплексоры (например, терминальный мультиплексор, мультиплексор ввода/вывода), которые, при известных условиях, обеспечиваются системным тактовым сигналом посредством единственного соединения для передачи данных. Если это соединение для передачи данных прерывается, то соответствующий мультиплексор продолжает работать с вырабатываемой внутри него тактовой частотой. В этом случае частота передаваемого от мультиплексора в транспортную SDH-сеть сигнала не совпадает с другими имеющимися в этом диапазоне тактовыми частотами. Поэтому расхождение между тактовыми частотами должно быть устранено посредством специально предусмотренных для этого мероприятий, которые описаны в [1]-[5].

Плезиохронная цифровая иерархия (PDH) не позволяет выделять отдельный канал непосредственно из потока данных; каждый раз необходимо последовательно проходить все уровни иерархии системы мультиплексирования, на которых каналы объединяют в системы с более высоким количеством каналов. На приемной стороне эти уровни иерархии проходят в обратной последовательности для того, чтобы обеспечить возможность дальнейшего распределения отдельных каналов. Синхронная цифровая иерархия (SDH), в противоположность этому, дает возможность прямого доступа к сигналам определенной полосы частот многоканальной системе для передачи их абоненту или в точку коммутации. Может быть также обеспечен доступ к широкополосному потоку сигналов для замены определенных сигналов другими без необходимости прохождения всей мультиплексной иерархии. Этот доступ осуществляют по управляемой вычислительной машиной сети связи (см. [6], с.48-55 или [5], с.283).

Структура передаваемых в синхронной цифровой иерархии (SDH) потоков данных подробно описана в [2] и [5]. Синхронная цифровая иерархия (SDH) основана на синхронной передаче транспортных модулей (STM-n), в которые введена полезная информация. Базовый транспортный модуль (STM-1), который состоит из кадра с 9 строками и 270 столбцами или, соответственно, 2430 полями емкостью по 8 бит данных, содержит максимум 19440 бит данных. STM-1-модуль передают с тактовой частотой 8000 Гц, вследствие чего создается канал передачи с пропускной способностью 155,52 Мбит/с.

Как показано на фиг.1, ряды 1-3 RSOH и ряды 5-9 MSOH первых 9 столбцов синхронного транспортного модуля STM-1 образуют заголовок секции (SОН). Ряд 4 первых 9 столбцов содержит указатель административного блока AU-4 PTR, который указывает поле, в котором начинается относящийся к административному блоку сигнал или, соответственно, первое поле (J1) виртуального контейнера (например, VC-4). Оставшиеся 261 столбцов синхронного транспортного модуля STM-1, которые предусмотрены для приема виртуального контейнера VC-4, образуют поле полезной нагрузки, которое имеет различную структуру в зависимости от структуры и скорости передачи передаваемых данных. Виртуальный контейнер VC-4, который имеет трактовый заголовок (РОН), может содержать, например, три канала скорости 34 Мбит/с или 63 канала скорости 2 Мбит/с или даже непрерывную последовательность АТМ-пакетов. Определенная структура мультиплексирования показана на фиг.6-1 и фиг.6-2 из [2]. Виртуальный контейнер VC-4 наряду с трактовым заголовком РОН может содержать С-4-контейнер, три компонентных блока TU-3 с виртуальными контейнерами VC-3 или 63 компонентных блока TU-12 с виртуальными контейнерами VC-12, которые имеют по одному контейнеру С-3 или, соответственно, С-12, а также одному трактовому заголовку РОН. Виртуальные контейнеры VC-3 и VC-12 с возможностью сдвига содержатся в компонентном блоке TU-3 или, соответственно, TU-12, которые при временном мультиплексировании в первом байте имеют сопровождающий указатель административного блока, который указывает на первое поле виртуального контейнера VC-3 и VC-12. Компонентные блоки TU-3 или, соответственно, TU-12 объединены в группы компонентных блоков TUG-3 или, соответственно, TUG-2 и TUG-3. Группа компонентных блоков TUG-3 содержит один компонентный блок TU-3 или семь групп компонентных блоков TUG-2, каждая из которых содержит по три компонентных блока TU-12. Посредством полей заголовка РОН полезная информация может быть идентифицирована вплоть до уровня контейнера. Поэтому отдельные полезные каналы могут извлекаться из транспортного модуля STM-1 или добавляться в него без необходимости разложения всего синхронного модуля STM-1. Начало передачи в полезном поле указывается посредством содержащихся в соответствующих структурах кадра (AU-4, TU-4, TU-12) указателей RTR. Отдельные контейнеры могут быть, таким образом, идентифицированы и, посредством элементов синхронной цифровой иерархии (SDH), могут по-разному группироваться и пересылаться через сеть. Согласно пункту 2.7 и пункту 2.11 из [1] , для виртуальных контейнеров VC-n высокого порядка (n-3 или n=4) и для виртуальных контейнеров VC-m низкого порядка (m=11, 12 или 2) предусмотрены ступени коммутации и, соответственно, коммутационные поля (НРС-n) или соответственно (LPC-n)).

Для осуществления коммутации каналов в ступенях коммутации и, соответственно, в коммутируемых сетях, согласно например, [4], стр. 5 или [5], стр. 282, все сигналы соответствующего уровня иерархии должны быть синхронными друг другу и, соответственно, согласованными по фронтам тактового сигнала. Кроме того, кадры коммутируемых сигналов должны быть синфазными. Согласно пункту 2.4 из [1] в ступени адаптации, которая включена перед ступенью коммутации (НРС-n) используется адаптация каскада мультиплексирования (МСА), а перед (LPC-n) использована адаптация ступени коммутации (НРА-n), осуществляется синхронизация с тактовым сигналом.

Дрейф и плезиохронное смещение в принятом сигнале корректируют в предварительно включенной ступени адаптации посредством функции обработки указателя. Согласно пункту 2.5.3 из [1] функцию обработки указателя осуществляют с помощью буфера данных, в который данные записывают с тактом подводимого сигнала и из которого данные вновь считывают с системным тактом (ТО). В зависимости от смещения между тактом записи и тактом считывания изменяется уровень заполнения буфера данных. Если уровень заполнения виртуального контейнера VC-n не достигает предусмотренного порогового значения, то смещение кадра увеличивают на 3 поля (для VC-4), вследствие чего три цикла считывания пропускают. Если уровень заполнения виртуального контейнера VC-n превышает предусмотренное пороговое значение, то смещение кадра уменьшают на 3 поля (для VC-4), благодаря чему считывают соответствующее количество байт из буфера данных. Для этого в цикл считывания добавляют дополнительные тактовые импульсы. В связи с процессом синхронизации такого рода в каждом случае осуществляют еще одну соответствующую коррекцию положения указателя. Описанный процесс синхронизации подробно разъяснен в [2] в разделе "Frequency justification" (см. также с.5 из [3] и особенно главу 4 из [5]).

Несмотря на то, что коммутация синхронного потока данных в ступени коммутации и, соответственно, коммутационном поле может быть осуществлена с низкими издержками, т. е. без разложения всего STM-1 модуля, из блок-схемы терминального мультиплексора, представленной на фиг.2-1 из [1], видно, что адаптацию (каскада мультиплексирования, ступени коммутации и коммутационного поля) и коммутацию (соединения ступени коммутации и коммутационного поля) осуществляют с большими издержками.

Поэтому задачей настоящего изобретения является создание способа адаптации и коммутации каналов данных и устройства, которые могут быть осуществлены с низкими издержками.

Эта задача решается посредством признаков, указанных в отличительной части пунктов 1 и, соответственно, 7 формулы изобретения. Предпочтительные варианты осуществления изобретения охарактеризованы в других пунктах.

Благодаря соответствующему изобретению способу адаптацию и коммутацию содержащихся в синхронном модуле STM каналов данных осуществляют в процессе работы. Ступень адаптации и ступень коммутации или, соответственно, коммутационное поле объединяют и реализуют с единственным модулем памяти, который имеет несколько эластичных буферов данных. Благодаря этому снижают издержки на аппаратные средства, что благоприятно сказывается на стоимости и габаритах. Кроме того, на несколько тактовых циклов снижается требуемое время обработки.

Изобретение более подробно пояснено на примерах, иллюстрируемых чертежами, на которых показано следующее:

фиг.1 - варианты структуры кадра STM-1,

фиг.2 - ступени адаптации 100а, 100b с последовательно подключенным коммутационным полем 200,

фиг. 3 - модуль 30 для одновременной адаптации и коммутации STM-1 модулей,

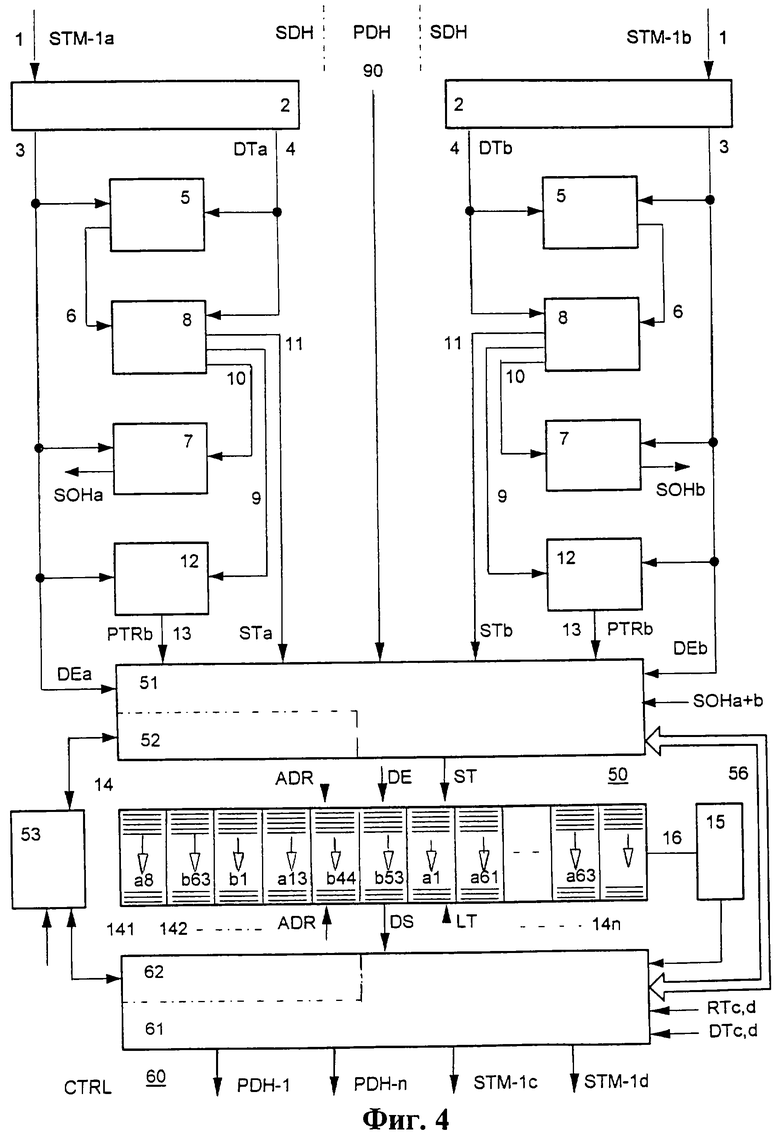

фиг. 4 - схема для одновременной адаптации и коммутации STM-1 модулей с адресуемым эластичным буфером данных и

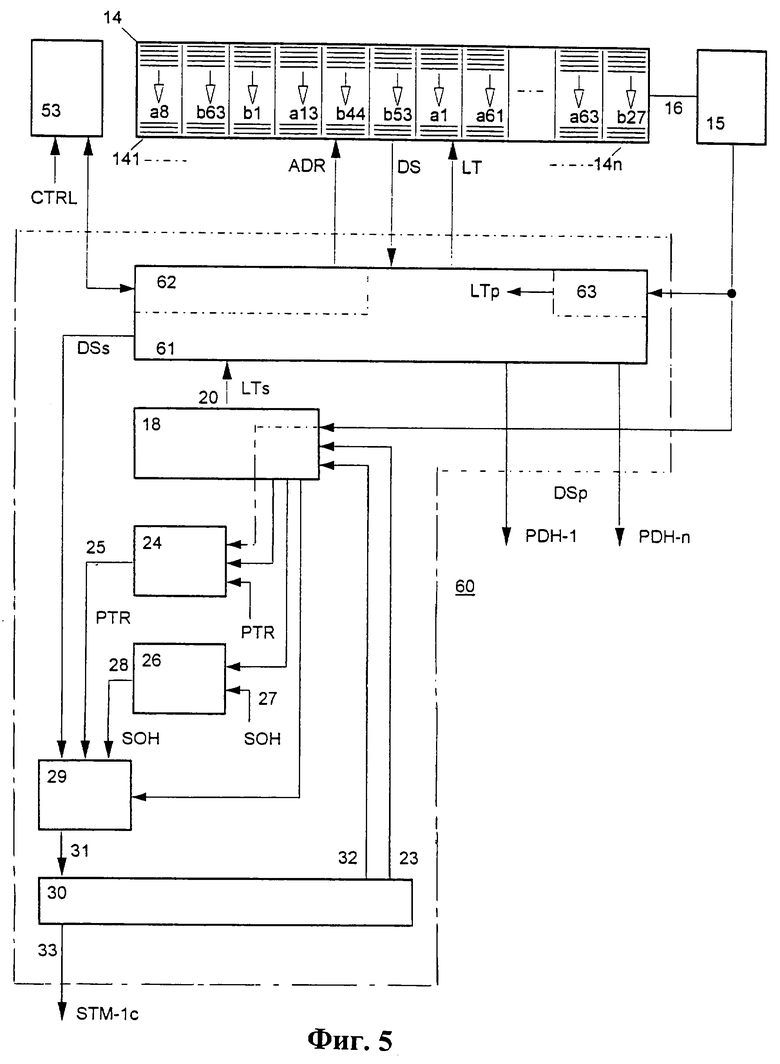

фиг. 5 - подключенные после эластичного буфера данных модули, которые предназначены для дальнейшей обработки синхронизированных и связанных данных,

фиг.6 - схема, соответствующая фиг.4 и фиг.5, в упрощенном варианте осуществления.

На фиг. 1 показана структура синхронного транспортного модуля STM-1. На фиг. 2 показана известная, например, из [1] и [4] компоновка для адаптации и коммутации двух SDH-потоков данных. Адаптацию SDH-потоков данных осуществляют в модулях 100а и 100b, которые описаны в [3] и [4]. Коммутацию каналов данных осуществляют в модуле 200, который имеет коммутационное поле, как показано на фиг. 7.35 из [5]. На фиг.3 показан соответствующий изобретению модуль 30 для одновременной адаптации и коммутации STM-1 модулей. На фиг.4 показан возможный вариант осуществления модуля, изображенного на фиг.3. Обработка SDH-потока данных посредством соответствующих функциональных блоков известна из [1] и [2]. В [3] описана возможная схема для адаптации потока данных. Выбранные там условные обозначения в значительной степени позаимствованы для фиг.4. На ней показана схема, посредством которой разлагают синхронные транспортные модули STM-1a, STM-1b, и содержащиеся в них каналы или, соответственно, соответствующие виртуальные контейнеры VC-n или контейнеры С-n согласовывают с тактовой частотой и с учетом положения во времени и пространстве коммутируют на предусмотренные выходы. Если виртуальные контейнеры VC-n из синхронных транспортных модулей STM-1a, STM-b перемещаются в синхронные модули STM-1с, STM-d, то осуществляется адаптация к новой частоте посредством перемещения виртуального контейнера. VC-n в соответствующий компонентный блок TU-n и отслеживания соответствующего указателя административного блока. Если контейнеры С-n передают в сеть PDH, то осуществляется согласование с предусмотренной для этого тактовой частотой.

На фиг. 4 показаны два канала обработки синхронных транспортных модулей STM-1a и STM-1b, которые, к примеру, должны быть преобразованы в синхронные модули STM-1c и STM-1a или каналы данных которых должны передаваться в сети плезиохронной цифровой иерархии PDH. Соответствующая изобретению схема может, однако, иметь также и только один канал обработки синхронного модуля STM-1a, контейнеры С-n которого должны передаваться в сеть плезиохронной цифровой иерархии PDH. Кроме того, изобретение может быть использовано для перевода данных в той же самой сети на более высокий или более низкий уровень иерархии.

На фиг. 4 показаны приемный интерфейс 2, устройство 5 кадровой синхронизации, счетчик 8 кадров (также, например, счетчик числа строк, столбцов или байт), устройство 7 приема заголовка секции, устройство 12 приема указателя административного блока, первый управляющий модуль 50, модуль 14 памяти, измеритель 15 уровня заполнения, накопитель 53, а также второй управляющий модуль 60. На вход 1 приемного интерфейса 2 поступает "входящий" STM-1 модуль. В приемном интерфейсе 2 его предварительно обрабатывают таким образом, что на его выходе 3 данных в двоичном формате (предпочтительно параллельно по 8 бит) получают данные DEa, а на тактовом выходе 4 данных - соответствующий такт данных DTa. Устройство 5 кадровой синхронизации проверяет данные DE на появление слова опознавания кадра или, соответственно, определенного двоичного эталона, который периодически передают в потоке данных с каждым синхронным модулем STM-1а. С каждым появлением слова опознавания кадра устройство 5 кадровой синхронизации устанавливает счетчик 8 кадров посредством его установочного входа 6 в определенное значение. Счетчик 8 кадров, кроме того, с каждым тактовым импульсом такта данных DTa получает приращение на единицу. Поэтому по состоянию счетчика можно определить, какую позицию занимает поступивший на вход данных бит в соответствующем STM-1-кадре (при параллельной передаче байта (двоичной передаче) счетчик кадров считает поля или, соответственно, байты). Так как начало STM-1-кадра известно, то он может быть разложен по своим полям и обработан. Далее может быть определено, приложен ли бит из заголовка секции (SОН) или из виртуального контейнера VC-n. Счетчик 8 кадров через выход 9 выдает такт приема административного указателя на устройство 12 приема административного указателя, через выход 10 - такт приема заголовка секции на устройство 7 приема заголовка секции и через выход 11 - такт записи STa на первый управляющий модуль 50, по которому содержащуюся в синхронном транспортном модуле STM-1 полезную нагрузку (строки 1-9, столбцы 10-261) записывают в управляющий модуль 50 и там обрабатывают дальше.

Считыванием бит заголовка секции (SОН или, соответственно, RSOH и MSOH) управляет такт приема заголовка секции, который выдается счетчиком 8 кадра через выход 10 в устройство 7 приема заголовка секции. В устройстве 7 приема заголовка секции биты промежуточно запоминают и после передачи на управляющий модуль 50 обрабатывают далее, предпочтительно согласно процедуре, описанной в [1] . Считыванием бит указателя административного блока AU-4 управляет такт приема административного указателя, который через выход 10 передается на устройство приема 7 заголовка секции. При помощи указателя административного блока (PTR) управляющий модуль 50, который содержит мультиплексор 51 и соединенную с накопителем 53 адресную логику 52, определяет начало виртуального контейнера VC-4 внутри полезной нагрузки синхронного транспортного модуля STM-1, после чего виртуальный контейнер VC-4, например, как описано в [1] и [2] разлагают на предназначенные для адаптации и коммутации компонентные блоки TU-3 или, соответственно, TU-12, на виртуальные контейнеры VC-3 или, соответственно, VC-12 или на контейнеры С-3 или, соответственно, С-12.

Кроме того, на управляющий модуль 50 может быть подан по меньшей мере один плезиохронный поток 90, который, при известных условиях, после обработки в интерфейсе для плезиохронного сигнала полностью или частично записывают в, по меньшей мере, одну из зон памяти 141, ..., 14n и затем, как описано выше, перераспределяемый в выходящий поток данных. Соответствующее изобретению решение может быть использовано для обработки данных, которые переходят от плезиохронной к синхронной цифровой иерархии, от синхронной к плезиохронной цифровой иерархии или на более высокий или более низкий уровень внутри синхронной цифровой иерархии. Поэтому изобретение, предпочтительно, может быть использовано для гибкого мультиплексора, мультиплексора ввода/вывода, или мультиплексора с кроссовой коммутацией, которые описаны в [6] на страницах 53-55. Возможно также его использование и в несинхронных передающих системах, в которых адаптируют и коммутируют только лишь плезиохронные потоки данных.

Поэтому перед управляющим модулем 50 стоит задача после процесса временного мультиплексирования записывать в соответствующие зоны 141, ..., 14n памяти модуля 14 памяти подведенные компонентные модули TU-n или, при определенных условиях, содержащиеся в них виртуальные контейнеры VC-n. Сопоставление зон 141, . . . , 14n памяти, которые служат в качестве буфера данных для отдельных каналов данных, осуществляют через адресную логику 52, которую программируют при помощи управляющего сигнал CTRL. Изменение направлений обмена для отдельных каналов (коммутация в сети связи, см. главу 2.3.1.1 из [7] ) осуществляют путем изменения соответствия зонам 141, ..., 14n памяти компонентных блоков TU-n, виртуальных контейнеров VC-n или, при известных условиях, содержащихся в них контейнеров С-n. Этим способом каналы синхронных модулей STM-1a и SТМ-2b можно по-разному смешивать во времени и пространстве, а также ставить в соответствие с любыми входами подсоединяемой сети плезиохронной цифровой иерархии (PDH). Последнее имеет, конечно, силу также и для случая, когда в наличии имеется только один транспортный канал для синхронного модуля STM-n. Само собой разумеется, только некоторые каналы могут быть сопоставлены также PDH-сети, а другие каналы - одному или нескольким синхронным модулям STM-n (Аdd-/Drop-мультиплексор). В отличие от рассмотренной в [4] схемы, которая позволяет осуществлять за определенный системный такт только лишь одну адаптацию SDH-потока данных, благодаря соответствующему изобретению решению могут быть реализованы все функции Add-/Drop-мультиплексора.

Поэтому первый управляющий модуль 50, в котором благодаря прилагаемым тактам кадра RT и, при известных условиях, тактам данных DT известны позиции приложенных бит внутри находящегося в обработке STM-1 модуля, а также местоположение компонентных блоков TU, виртуальных контейнеров VC или контейнеров С, а также соответствующие им зоны 141, ..., 14n памяти модуля 14 памяти, имеет возможность в режиме временного мультиплексирования загружать компонентные блоки TU или, соответственно, контейнеры VC, С в соответствующие зоны 141, ..., 14n памяти, которые играют роль буфера данных для соответствующих каналов. Если не существует отклонений частот "входящих" и "выходящих" сигналов, компонентный блок TU или, соответственно, контейнер VC, С проходит соответствующую зону 141, ..., 14n памяти за то количество тактов считывания, которое соответствует числу блоков памяти зоны 141, ..., 14n памяти. На основании указателя (PTR), определенного устройством 12 приема административного указателя, времени прохода через соответствующую зону 141, ..., 14n памяти и возможных смещений с целью адаптации "входящего" потока данных к новой тактовой частоте могут быть рассчитаны значения указателя административного блока для вновь формируемого синхронного модуля STM-n.

Для контроля уровня заполнения отдельной зоны 141, ..., 14n памяти предусмотрен, предпочтительно, один работающий в режиме временного мультиплексирования измеритель 15 уровня заполнения (способы временного мультиплексирования, предназначенные для устранения дублирования аппаратных средств, описаны, в частности, в [4]), который выдает соответствующие данные на второй управляющий модуль 60, который имеет адресную логику 62 и мультиплексор 61. Так как частоты "входящих" и "выходящих" сигналов совпадают, как правило, не точно, возникает различие между скоростями, с которыми зоны 141, .. . , 14n памяти заполняют и, соответственно, очищают, вследствие чего зоны 141, ..., 14n памяти могут быть либо полностью очищены, либо полностью заполнены. Для компенсации этого расхождения в главе 8 из [2] в разделе "Freguency justification" предусмотрены соответствующие процедуры (для AU-n указателя в главе 8.1.3, для TU-3 указателя в главе 8.2.3 и для TU-2 указателя в главе 8.3.3). При этом положение указателя выходящего "сигнала" рассчитывается с учетом положения указателя "входящего" сигнала и проведенной коррекции, которую осуществляют следующим образом. Если уровень наполнения зоны 141, . . ., 14n памяти слишком низок, то работающий в режиме мультиплексирования управляющий модуль 60 прерывает в нескольких строго определенных разрядах кадра цикл считывания LT, вследствие чего уровень заполнения соответствующих зон 141, ..., 14n памяти повышается. Если уровень заполнения зон 141, ..., 14n памяти слишком высок, то управляющий модуль 60 вставляет в некоторые строго определенные позиции кадра дополнительные такты считывания LT, вследствие чего уровень заполнения соответствующих зон 141, ..., 14n памяти падает. Для того чтобы обеспечить возможность компенсации наибольшего диапазона колебаний, уровень заполнения, предпочтительно, всегда удерживают в области 50%.

Для передаваемых в плезиохронную цифровую иерархию потоков данных PDH1, ..., PDHn, которые состоят из контейнеров С-n, в зависимости от уровня заполнения зон 141, ..., 14n памяти осуществляют адаптацию частоты, с которой эти потоки данных считывают. Если уровень заполнения зон 141, ..., 14n памяти слишком низок, управляющий модуль 60 снижает тактовую частоту соответствующего PDH-потока данных, который передается на один из выходов PDH1, . .., PDHn, вследствие чего уровень заполнения соответствующих зон 141, ..., 14n памяти поднимается. Если уровень заполнения зон 141, ..., 14n памяти слишком высок, то управляющий модуль 60 повышает тактовую частоту соответствующего PDH-потока данных, благодаря чему уровень заполнения соответствующей зоны 141, ..., 14n памяти падает.

Несмотря на то, что оба управляющих модуля 50, 60, накопитель 53 и измеритель 15 уровня заполнения на фиг.4 представлены отдельными друг от друга, их функции объединяются, предпочтительно, в едином унифицированном конструктивном узле, например в процессоре, который управляет записью и считыванием данных отдельных каналов в режиме мультиплексирования. Кроме того, эти функции могут быть реализованы в ходе управляемого программными средствами процесса и, соответственно, при помощи соответствующих программных модулей. В компоновке схемы по фиг.4 протекающие в управляющих модулях 50 и 60 процессы согласуют друг с другом посредством связи 56 по данным. При помощи передаваемой в заголовке секции SOHa; SOHb информации, первым управляющим модулем 50, кроме того, может быть реализована функция защиты. Дополнительно к защите секции мультиплексирования может быть также реализована защита соединения субсети (см. [5], стр. 36). Поскольку синхронные транспортные модули STMa, STMb переносят эти полезные данные, в определенный момент может быть реализовано переключение на более качественный канал (см. [5], стр. 34).

На фиг. 5 показаны подключенные после модуля 14 памяти модули, которые предназначены для дальнейшей обработки синхронизированных и связанных данных и которые, как, например, показано на фиг.4, являются интегрированной составной частью второго управляющего модуля 60, процесс функционирования которого согласован с процессом функционирования первого управляющего модуля 50. Далее, основываясь на [3], функции этих модулей кратко пояснены. С выходов 23 и 32 SDH-точки доступа на второй счетчик 18 кадра поступают такт данных DTc, d и такт кадра RTc. В устройстве 24 передачи указателя административного блока рассчитывают, как описано выше, указатель административного блока, который под управлением второго счетчика 18 кадров через мультиплексор 29 вводится в "выходящий" поток данных. В устройстве 26 передачи заголовка секции обрабатывают пришедшие от точки доступа биты заголовка секции (SОН), которые под управлением второго счетчика 18 кадров через мультиплексор 29 вводятся в "выходящий" поток данных и передаются к SDH-точке доступа. Для считывания данных из модуля 14 памяти с выхода 20 второго счетчика 18 кадров цикл считывания LTs передается на управляющий модуль 60. В зависимости от уровня заполнения зон 141, ..., 14n памяти в цикле считывания LTs в определенные позиции кадра дополнительно добавляют либо удаляют такты. Для считывания данных, которые передаются в плезиохронную цифровую иерархию (PDH), во втором модуле 60 управления предусмотрен генератор 63 тактов, который для каждого PDH-канала вырабатывает тактовый сигнал LTp, который изменяют в зависимости от уровня заполнения соответствующей зоны 141, ..., 14n памяти. Предусмотренный во втором модуле 60 памяти мультиплексор 61 поэтому заботится о том, чтобы адресованные зоны памяти поочередно считывались с предусмотренными тактами считывания LTs, LTp.

На фиг.6 показана известная по фиг.4 и фиг.5 компоновка схемы в упрощенной форме реализации. На ней показан один соединенный с процессором 80, а также модулем 14 памяти управляющий модуль 70, который имеет только один мультиплексор 71, только одну соединенную с накопителем 53 адресную логику 72, а также один измеритель 15 уровня заполнения. Счетчик 8 кадров с выходов 9, 10 или, соответственно, 11 выдает непосредственно на управляющий модуль 70 такт приема административного указателя, такт приема заголовка секции и такт записи для ввода полезных данных, так что заголовок секции, административный указатель и полезные данные считывают непосредственно в управляющий модуль 70, где они описанным выше способом могут быть обработаны с помощью процессора 80. Считывание данных, кроме того, может быть осуществлено при помощи такта данных DTa (пунктирная линия), после чего при помощи сигналов, переданных на выходы 9, 10, или, соответственно, 11 счетчика 8 кадров, могут быть различены биты данных административного указателя, заголовка секции и поля полезных данных. При этом для записи и считывания данных в или, соответственно, из зон 141, ..., 14n памяти используют только один мультиплексор 71 и только одну адресную логику 72, которыми управляет процессор 80. Фиг.6 позволяет сделать заключение о том, что для реализации соответствующего изобретению решения возможны различные варианты осуществления. Например, необходимые функции, как уже упоминалось, могут быть реализованы посредством программно-управляемого процесса и, соответственно, при помощи соответствующих программных модулей.

Соответствующая изобретению адаптация и коммутация каналов данных может происходить в системе передачи плезиохронной или синхронной цифровой иерархии. Соответствующее изобретению устройство, кроме того, может быть использовано в качестве мультиплексора ввода/вывода, который служит для адаптации и коммутации входящих и выходящих каналов другой плезиохронной или синхронной системы передачи.

Источники информации

1. ITU-TRecommendation G.783 (Fassung 01/94).

2. ITU-TRecommendation G.707 (Fassung 03/96, заменяет более ранние Recommendation G.707, G.708 и G.709).

3. DE-PS 4018687 С2.

4. WO 93/25029.

5. M. Sexton, A. Reid, Transmission Networking-SONET and the Synchronous Digital Hierarchy, Artech House 1992.

6. G. Siegmund, ATM - Die Technik des Breitband-ISDN, v. Decker's Verlag, Heidelberg 1994, 2.Auflage.

7. G. Altehage, Digitale Vermittlungssysteme fur Fernsprechen und ISDN, R.v. Decker's Verlag, Heidelberg 1991.

Изобретение относится к технике связи и может использоваться в системах сети синхронной цифровой иерархии при помощи транспортных модулей. Технический результат заключается в повышении качества адаптации и коммутации при работе системы. Для этого внутри сети синхронной цифровой иерархии передают при помощи траспортных модулей каналы данных. В системе предусмотрен модуль памяти с зонами памяти, в которые в режиме мультиплексирования при помощи управляющего модуля записывают упакованные в транспортные блоки определенного уровня иерархии данные входящих каналов и в процессе адаптации к частоте выходящего канала вновь считывают данные. 2 с. и 9 з.п.ф-лы, 6 ил.

| WO 9429994 А2, 22.12.1994 | |||

| СПОСОБ ДЕПАРАФИНИЗАЦИИ НЕФТЕПРОДУКТОВ | 2005 |

|

RU2288942C1 |

| Способ селекции признаков сигналов объектов | 1990 |

|

SU1765838A1 |

Авторы

Даты

2003-11-10—Публикация

1998-07-01—Подача