Настоящее изобретение относится к устройству восстановления синхронизации для использования в синхронной цифровой иерархической (SDH) системе передачи данных. В частности, изобретение касается создания устройства, посредством которого третьи стороны, желающие использовать SDH-линию связи, которая находится под управлением другого оператора, могут передавать сигналы собственной синхронизации и другую информацию в такой сети.

Синхронизация третьей стороны устанавливается, когда сигналы синхронизации, которые должны быть переданы в сигнале основной скорости передачи, исходят от источника, который не синхронизирован с источником, используемым для синхронизации SDH-сети. Синхронизация третьей стороны является поэтому плезиохронной по отношению к тактовому сигналу широкополосного канала передачи данных.

В SDH-сети сигналы основной частоты отображаются в модули синхронной передачи (STM-N) с высокой скоростью передачи битов в точке ввода сети с использованием виртуальных накопителей (VC) и подчиненных блоков (TU), размер и тип которых зависит от скорости передачи данных передаваемого сигнала. Многие из этих подчиненных блоков объединяются вместе в единый модуль синхронной передачи. В точке выделения модуль синхронной передачи демультиплексируется и отображается обратно в сигналы основной скорости передачи. Однако сигналы подвержены фазовым и частотным искажениям, которые влияют на качество сигнала, который используется для передачи синхронизирующей информации. Ключевым компонентом в SDH-системах, используемым для уменьшения этих искажений, является так называемый десинхронизатор, или устройство восстановления синхронизации.

Настоящее изобретение направлено на усовершенствование системы, раскрытой в заявке на патент Великобритании 91148411, опубликованной под N GB 2257603A 13 января 1993. Задачей настоящего изобретения является обеспечить возможность третьим сторонам, использующим свой собственный источник синхронизации для основной скорости передачи, передавать синхронизирующую информацию по SDH-сети, которая используется первой стороной. В настоящее время это невозможно и, как показано на фиг. 1B упомянутого выше документа, требуется отдельный канал для передачи этой синхронизирующей информации.

В упомянутом выше документе для восстановления синхронизации используются как данные указателя, так и данные выравнивания битов или никакие из таких данных, причем синхронизация обеспечивается на выходе основной скорости передачи в предположении, что сигнал основной скорости передачи синхронизирован с широкополосным каналом передачи данных. Заявитель установил, что если данные выравнивания битов используются без данных указателя, то SDH-сеть может быть адаптирована для передачи такой синхронизирующей информации третьей стороны без предоставления отдельного канала.

Изобретение предлагает устройство восстановления синхронизации для синхронной цифровой иерархической (SDH) системы передачи данных, обеспечивающее возможность третьим сторонам использовать SDH-канал, содержащее вход (5) для приема мультиплексированного сигнала модуля синхронной передачи, схемы (20) восстановления синхронизации для восстановления синхронизирующего сигнала из сигнала модуля синхронной передачи, демультиплексор (21) для демультиплексирования сигнала модуля синхронной передачи на множество сигналов подчиненных блоков, процессор указателя (25) для считывания данных указателя из сигнала подчиненных блоков, устройство устранения битов выравнивания (28) для считывания данных выравнивания битов из сигнала подчиненных блоков, буферное запоминающее устройство (30) с монитором (34) запоминающего устройства. В указанном запоминающем устройстве (30) временно сохраняются данные процессора подчиненных блоков, прежде чем они будут синхронизированы с восстановленной частотой синхронизации, причем указанное устройство восстановления синхронизации отличается тем, что содержит средство (32) для генерирования сигнала восстановленной синхронизации (31), включающее в себя три входа подстройки фазы (φ1,φ2,φ3), которые соединены с процессором (25) указателя, устройством устранения битов выравнивания (28) и монитором запоминающего устройства (34) соответственно, при этом используются только считанные данные устранения битов выравнивания, сформированные устройством устранения битов выравнивания (28) (на входе φ2 подстройки фазы) для модификации восстановленного синхронизирующего сигнала (23) и генерирования восстановленного сигнала синхронизации (31).

Вариант осуществления изобретения будет описан с помощью примера со ссылкой на чертежи, на которых показано следующее:

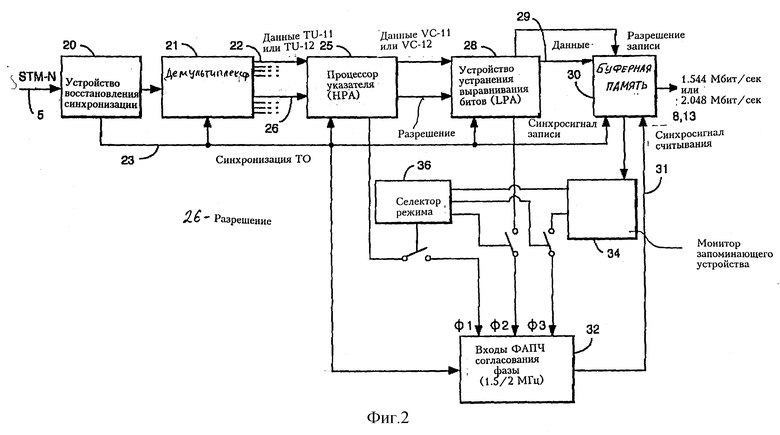

фиг. 1 - схематичное представление SDH-сети, которая может быть использована пользователем в качестве третьей стороны, и

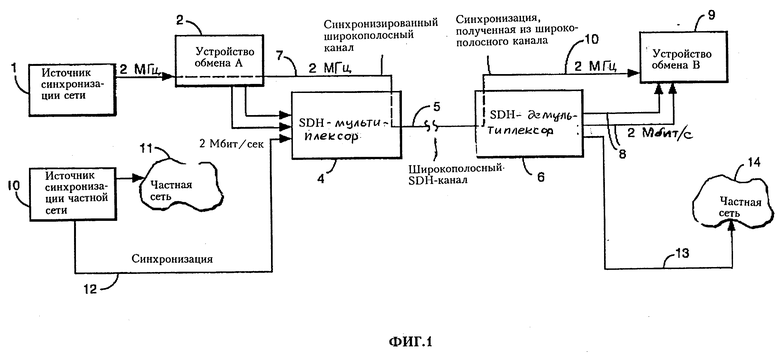

фиг. 2 - блок-схема, иллюстрирующая устройство восстановления синхронизации, выполненное в соответствии с изобретением.

SDH-сеть (фиг. 1) содержит источник синхронизации 1 сети, который подает сигнал, например, частотой 2 МГц, в устройство обмена АТС 2. Устройство обмена 2 подает сигнал со скоростью 2 Мбит/сек на N сигнальных выходов 3 (изображено два), связанных с SDH-мультиплексором 4. Мультиплексированный STM-N сигнал затем передают по широкополосному SDH-каналу 5 в SDH-демультиплексор 6. Устройство обмена 2 также подсоединено к SDH-мультиплексору 4 с помощью линии управления 7, которая синхронизирует широкополосный SDH-канал 5 с частотой синхронизации 2 МГц. В демультиплексоре 6 сигнал преобразуется обратно в формат основной скорости передачи 2 Мбит/сек и подается по линии 8 в устройство обмена 9. Линия 10, соответствующая линии 7, предназначена для получения синхронизирующей информации из широкополосного канала.

В дополнение к этому, используя устройство восстановления синхронизации, которое будет описано, пользователь третьей стороны может использовать SDH-сеть для передачи синхронизирующей информации и других данных от частной сети 11. Источник синхронизации 10 частной сети, который не синхронизирован с источником синхронизации 1 сети, передает синхронизирующие сигналы, т.е. сигналы основной скорости передачи 1.544 Мбит/сек или 2.048 Мбит/сек по каналу 12 в SDH-мультиплексор 4. После демультиплексирования синхронизирующие сигналы передаются по каналу 13 в частную сеть 14. Можно видеть, сравнивая фиг. 1 с фиг. 1В в вышеупомянутой заявке на патент Великобритании, что синхронизирующая информация от третьей стороны в устройстве, предшествующем настоящему изобретению, должна была передаваться по отдельному каналу.

На фиг. 2 более подробно изображен демультиплексор 6 вместе с устройством десинхронизации или устройством восстановления синхронизации. Мультиплексированный STM-N сигнал сначала подается на схему восстановления синхронизации 20, в котором так называемый синхронизирующий сигнал TО подается на линию 23. После этого объединенный сигнал поступает на демультиплексор 21, где он разделяется на N сигналов низкого порядка, обозначенные как данные TU-11 или TU-12 в зависимости от частоты следования битов сигналов основной скорости (1.544 Мбит/сек или 2.048 Мбит/сек соответственно). Каждый из N сигналов основной скорости 22 затем поступает на устройство восстановления синхронизации. Хотя изображено только одно такое устройство для одного демультиплексора, на практике должно существовать отдельное устройство для каждого из N каналов 22. Данные TU подчиненных блоков сначала поступают на процессор 25 указателя. Процессор указателя является частью средств адаптации канала высокого порядка, и его функция заключается в интерпретации разностей фаз и частот между сигналами синхронизации в точке входа и точке выхода SDH-сети, которые закодированы указателем подчиненных блоков. "Указатели" более подробно описаны в упомянутой выше заявке на патент Великобритании. По существу, каждый виртуальный накопитель или VC сигнал имеет возможность находиться в объединенном потоке байтов, так что начальная точка виртуального накопителя в общем SDH-сигнале может изменяться для следующих друг за другом кадров. Значение указателя определяет начальную точку конкретного виртуального накопителя. Процессор 25 указателя, кроме того, принимает сигнал разрешения по линии 26, который функционирует как динамический флаг для указания, являются ли данные в любом конкретном TU-сигнале истинными или действительными данными, или относятся к служебным (непроизводительным) данным.

После процессора указателя полученные данные виртуального накопителя передаются на устройство устранения битов выравнивания 28, которое образует часть служебных данных канала низкого порядка.

Битовое выравнивание определено стандартами МККТТ. В сущности, данные выравнивания битов обеспечивают средство для указания, где в виртуальном накопителе находится сигнал со скоростью передачи 2 Мбит/сек. Например, в точке входа в систему может быть больше данных трафика, чем это может быть размещено в байтовом пространстве, предназначенном для этой цели. Любые данные переполнения могут быть размещены в дополнительных байтах выравнивания. Выравнивание битов используется для получения средства указания, что данные трафика размещены в дополнительных байтах выравнивания и что их необходимо отыскать прежде, чем сигнал может быть послан на дальнейшую обработку. После устранения битов выравнивания оставшиеся данные подаются в "эластичное" запоминающее устройство 30, в котором поглощаются временные фазовые переходные процессы, обусловленные промежутками, вызванными выделением служебных (дополнительных) байтов и байтов выравнивания. Сигнал основной скорости 29 с восстановленной синхронизацией с помощью средства, которое будет описано, затем считывается из "эластичного" запоминающего устройства по линиям 8 или 13 (фиг. 1).

Схема фазовой автоподстройки частоты (ФАПЧ) 32 получает в качестве входного опорный сигнал синхронизации TО широкополосного канала, восстановленный устройством 20, и выдает модифицированный сигнал синхронизации считывания для использования в данных восстановленной синхронизации из "эластичного" запоминающего устройства 30. Сигнал синхронизации считывания 31 может быть получен любым из множества способов. Схема фазовой автоподстройки частоты 32 имеет три входа подстройки фазы φ1, φ2 и φ3. Они подсоединены к процессору 25 указателя, устройству устранения выравнивания битов 28 и монитору 34 запоминающего устройства, соответственно. Выбор конкретной комбинации для использования регулируется посредством селектора режима 36, который управляет соответствующими переключателями для каждого из входов подстройки фазы.

Работа схемы сначала будет описана в нормальном режиме работы, т.е. без участия третьей стороны. В первом режиме выбирается вход φ1, и монитор запоминающего устройства 34 регулируется так, чтобы гарантировать, что "эластичное" запоминающее устройство 30 остается заполненным наполовину, так что скорость данных, выдаваемых из запоминающего устройства, была равна скорости, с которой они поступают в запоминающее устройство. Таким образом, синхронизирующий сигнал для основной скорости передачи может быть воспроизведен точно.

Во втором режиме выбираются входы φ1 и φ2, а вход φ3 блокируется. В этом режиме сигнал восстановленной синхронизации широкополосного канала на линии 23 используется непосредственно с фазовой регулировкой, осуществленной процессором 25 указателя и устройством устранения битового выравнивания 28.

Когда указанная выше схема должна быть использована для восстановления синхронизации основной скорости для пользователя третьей стороны, ни один из приведенных выше режимов не может быть использован. Работа упомянутого выше устройства десинхронизации производит регулировку указателя подчиненных блоков, приводя к фазовому переходному процессу, приблизительно равному 3,5 мксек на один указатель, на выходе SDH-сети. При надлежащей конструкции десинхронизатора будет иметь место ограничение скорости "ухода" этой фазы за счет ограничения соответствующего сдвига частоты устройства ФАПЧ десинхронизатора. Это ограничение обычно принимает фазовую форму сужения полосы пропускания ФАПЧ, приводя к близко расположенным настройкам указателя противоположной полярности, взаимно компенсирующимся и не оказывающим результирующего воздействия на конечный выходной сигнал. Однако настройки указателя противоположной полярности, не разделенные большим промежутком (больше, чем постоянная времени RC схемы ФАПЧ) не будут взаимно скомпенсированы.

В синхронизированных SDH-сетях изменения указателя TU-1 будут иметь место в результате медленно меняющихся факторов, например, температурных эффектов в оптических волокнах и в мультиплексоре.

Хотя оборудование в основном допускает такие скачки фазы, вводимые в сигналы основной скорости, существуют некоторые системы, предназначенные для плезиохронной цифровой иерархической (PDH) передачи, которая использует только способы выравнивания битов, имеющие допустимое отклонение менее 1 мксек. Изобретение предлагает средство, посредством которого влияние изменений указателя TU-1 может быть исключено, приводя к выходному фазовому отклику десинхронизатора, сравнимому с фазовым откликом устройства устранения выравнивания битов.

В третьем режиме работы для использования при восстановлении синхронизации для основной скорости для третьих сторон, селектор 36 режима работает так, что при нормальном режиме работы третьей стороны задействуется только вход φ2, так что используются только данные устранения битов выравнивания для настройки частоты синхронизации TО. Хотя на чертеже вход φ1 изображен как выключенный, в альтернативном варианте схема ФАПЧ может работать в ответ на сигналы настройки φ1, но компенсируя каждое появление сигналом настройки равной величины и противоположной полярности. Таким образом, работа аналогична работе PDH-демультиплексора. В качестве меры предосторожности вход φ3 также может быть задействован, но монитор 34 запоминающего устройства и "эластичное" запоминающее устройство работают различно, как будет описано ниже.

До тех пор пока SDH-сеть остается синхронизированной, игнорирование указателей не будет иметь длительного влияния на синхронизацию, выполняемую для сигнала основной скорости. Фактически, любые временные потери синхронизации или большие значения дрейфа в сети SDH будут урегулированы в "эластичном" запоминающем устройстве 30. Это допускается в относительно больших пределах, обычно более 40 мксек, для урегулирования максимально допустимого дрейфа в SDH-канале. Если синхронизация SDH-сети потеряна в течение длительного периода времени, то в результате возможно будет иметь место незаполнение или переполнение "эластичного" запоминающего устройства 30. Монитор 34 запоминающего устройства будет затем инициировать "уход" фазы для восстановления емкости "эластичного" запоминающего устройства 32. Таким образом, монитор 34 запоминающего устройства работает отличным способом по сравнению со способом, описанным для нормального режима, или без использования третьей стороны. В качестве альтернативы, емкость может быть восстановлена посредством временной замены операции десинхронизации на один из первых двух режимов, т. е. использование только монитора запоминающего устройства на входе φ3 или настройка с использованием φ1 и φ2 в течение ограниченного периода времени.

Устройство восстановления синхронизации предназначено для применения в устройстве разделения в системе передачи SDH-данных и использует данные битового выравнивания, а не данные указателя для модификации восстановленного сигнала синхронизации и генерирования сигнала синхронизации для восстановления синхронизации. При реализации изобретения достигается технический результат, заключающийся в обеспечении возможности пользователей третьей стороны, использующих свой собственный источник синхронизации для основной скорости, передавать данные синхронизации основной частоты по SDH-сети. 3 з. п. ф-лы, 2 ил.

| СПОСОБ ВЫДЕЛЕНИЯ ЦИКЛОВОГО СИНХРОНИЗИРУЮЩЕГО СИГНАЛА В СИСТЕМАХ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2010438C1 |

| Флюс для электрошлакового переплава металлов | 1975 |

|

SU522748A1 |

| Огнетушитель | 0 |

|

SU91A1 |

Авторы

Даты

2000-08-27—Публикация

1996-05-03—Подача