Настоящее изобретение относится к полупроводниковому запоминающему устройству, выполненному на полупроводниковой подложке.

Полупроводниковые запоминающие устройства (ЗУ) обычно подразделяются на запоминающие устройства с произвольной выборкой (ЗУПВ) и постоянные запоминающие устройства (ПЗУ). К полупроводниковым ЗУ, которые в очень больших количествах используются для хранения информации в компьютерах, относятся динамические ЗУПВ, называемые в дальнейшем ДЗУПВ.

В ДЗУПВ ячейка памяти для хранения информации состоит из одного элемента памяти, выполненного в виде электрического конденсатора и транзистора для считывания зарядов, хранящихся в конденсаторе. Из ЗУПВ всех видов ДЗУПВ имеют минимальное количество элементов и наиболее пригодны для создания систем с высокой степенью интеграции. Такие полупроводниковые ЗУ производятся в большом количестве и имеют относительно низкую стоимость.

По истечении определенного промежутка времени ДЗУПВ теряет хранящуюся в нем информацию, поскольку заряды, хранящиеся в электрическом конденсаторе, стекают из него под действием зарядов, генерируемых в полупроводниковой подложке во время ее нагревания или под действием зарядов ударной ионизации, возникающих из-за наличия сильного электрического поля. Потери зарядов, связанные с тепловым возбуждением, а также потери, связанные с ударной ионизацией, определяют величину тока утечки. Поэтому во избежание полной потери хранящейся в ДЗУПВ информации и восстановления зарядов в конденсаторе его необходимо периодически регенерировать. Обычно регенерация выполняется с интервалами, приблизительно равными 100 мс. Именно по этой причине полупроводниковое ЗУ такого типа называют динамическим ЗУПВ.

В ДЗУПВ очень трудно установить на определенной или меньшей величине такой уровень хранящегося в конденсаторе заряда, который позволил бы избежать возникновения вышеупомянутого тока утечки, устранить собственные, возникающие при его работе шумы и искажения, связанные с воздействием α-частиц. Другими словами, в ДЗУПВ существует минимальное количество заряда сигнала, которое в зависимости от степени интеграции ЗУ и конфигурации матрицы памяти по расчетам эквивалентно приблизительно миллиону элементарных частиц - электронов для ДЗУПВ емкостью 16 Мбит и приблизительно сотне тысяч частиц для ДЗУПВ емкостью 16 Гбит, у которого степень интеграции более чем в 1000 раз превышает степень интеграции ДЗУПВ емкостью 16 Мбит.

Вышеупомянутый ток утечки генерируется, в частности, в р-n-переходе между истоком или стоком и полупроводниковой подложкой. Происходит это потому, что один электрод электрического конденсатора ЗУ соединен с истоком или стоком считывающего транзистора. Хотя в реальном ДЗУПВ ток ударной ионизации и подавляется электрическим полем благодаря очень небольшим размерам р-n-перехода и очень небольшому перепаду концентрации примесей, в нем тем не менее невозможно полностью устранить появление тока утечки, наличие которого определяется самой электронной структурой полупроводника.

Другая проблема, присущая ДЗУПВ, состоит в том, что оно не обладает усиливающим эффектом, что объясняется тем, что информация хранится в нем в виде количества зарядов, которые считываются при их появлении, и поэтому напряжение выходного сигнала в ДЗУПВ обычно мало, что определяет низкую скорость считывания.

К ЗУПВ относятся статические ЗУПВ (СЗУПВ) в сочетании с ДЗУПВ. Обычно СЗУПВ состоит из шести транзисторов или двух резисторов и четырех транзисторов. Все эти элементы вместе образуют триггер. СЗУПВ, которое управляется током, сравнительно долго сохраняет поступающую в него информацию и в отличие от ДЗУПВ не требует регенерации. СЗУПВ однако имеет размеры, превышающие в несколько раз размеры ДЗУПВ, поскольку оно состоит из нескольких элементов, что определяет его относительно высокую стоимость. Благодаря усилению в ячейке памяти и отсутствию необходимости в регенерации СЗУПВ может работать с высокой скоростью и обладает определенным преимуществом, заключающимся в очень небольшом потреблении мощности.

В то же время обычное энергонезависимое ПЗУ сохраняет поступающие в него заряды, образуемые в нем туннельным током, который попадает в узел памяти, окруженный изолятором. Количество хранящихся в таком ЗУ зарядов эквивалентно приблизительно ста тысячам электронов. Изолятор обычно имеет толщину около 10 нм или больше и обеспечивает хранение данных в ЗУ в течение 10 лет или больше. Энергонезависимое ПЗУ требует сравнительно большого времени записи по сравнению с ЗУПВ и поэтому не может использоваться как ЗУПВ. Кроме того, ток, который воздействует на изолятор при повторении операции записи, приводит к постепенному снижению качества изолятора, который со временем превращается в проводящий слой, не позволяющий в ЗУ хранить необходимую информацию. Поэтому в реальном энергонезависимом ПЗУ число операций записи ограничено сотней тысяч.

Таким образом, ДЗУПВ, СЗУПВ и энергонезависимое ПЗУ обладают и определенными преимуществами и определенными недостатками, от которых зависят возможности их конкретного применения.

Задачей настоящего изобретения является создание полупроводникового ЗУ, обладающего хорошей долговременной памятью и одновременно работающего устойчиво и с высокой скоростью, которые характерны для ЗУПВ.

Поставленная задача решается с помощью предложенного полупроводникового запоминающего устройства (ЗУ), имеющего узел ЗУ, образованный затвором транзистора, сформированного на полупроводниковой подложке, и многослойную структуру, которая состоит из полупроводниковых слоев и запирающих слоев в качестве изоляторов и которая сформирована на узле ЗУ, при этом запись информации в узел ЗУ или ее стирание из узла ЗУ осуществляется за счет инжекции зарядов в узел ЗУ через многослойную структуру, соответственно за счет удаления зарядов из узла ЗУ через многослойную структуру.

Предпочтительно полупроводниковое ЗУ выполнить так, чтобы узел ЗУ и многослойная структура, состоящая из полупроводниковых слоев и запирающих слоев в качестве изоляторов, были расположены друг на друге в направлении, перпендикулярном плоскости полупроводниковой подложки.

Предпочтительно также полупроводниковое ЗУ снабдить расположенным на узле ЗУ и отделенным от него изолятором электродом, который был бы предназначен для считывания из ячейки памяти хранящегося в ней сигнала.

Предпочтительно также полупроводниковое ЗУ, в котором бы множество таких устройств были объединены в матрицу памяти.

В одном из предпочтительных вариантов выполнения предложенное полупроводниковое ЗУ может иметь ячейку памяти, содержащую узел ЗУ, в котором хранятся заряды, шину передачи данных, соединенную с ячейкой памяти, словарную шину, соединенную с ячейкой памяти, шину считывания, соединенную с ячейкой памяти, записывающий элемент, расположенный между узлом ЗУ и шиной передачи данных и образующий путь, по которому заряды инжектируются в узел ЗУ или удаляются из него, и считывающий элемент, содержащий первый транзистор, который имеет исток/сток и пороговое напряжение которого меняется в зависимости от заряда, хранящегося в узле ЗУ, при этом шина считывания может быть соединена с истоком/стоком первого транзистора, а записывающий элемент может содержать второй транзистор, имеющий указанную многослойную структуру и первый электрод управления, который сформирован на боковой стороне этой многослойной структуры и отделен от нее изолятором и с которым соединена словарная шина.

При этом первый транзистор может быть сформирован на подложке, а второй транзистор расположен на первом транзисторе, и первый транзистор целесообразно выполнить в виде полевого транзистора, затвор которого служит узлом ЗУ.

В полупроводниковом ЗУ может быть предусмотрен также второй электрод управления, расположенный на боковой стороне указанного затвора и отделенный от него изолятором.

Задача также решается с помощью предложенного полупроводникового ЗУ, имеющего МДП-транзистор, который сформирован на полупроводниковой подложке, и многослойную структуру, которая состоит из полупроводниковых слоев и запирающих слоев в качестве изоляторов и которая сформирована на затворе МДП-транзистора, при этом информация записывается или стирается инжекцией зарядов в затвор через многослойную структуру, соответственно, их удалением из затвора через многослойную структуру, а считывается по шине считывания, которая соединена с истоком/стоком МДП-транзистора.

Таким образом, в настоящем изобретении предлагается, как сказано выше, запоминающее устройство, обладающее особенностями обычного ЗУПВ и энергонезависимого ЗУ. Суть настоящего изобретения состоит в том, что записываемая информация попадает в узел ЗУ через туннельный изолятор и считывается из него через транзистор, в качестве затвора которого используется узел ЗУ. Такая конфигурация позволяет создать ЗУ, в котором сохранение информации происходит как в обычном энергонезависимом ЗУ и в котором так же, как и в обычном СЗУПВ, происходит усиление сигнала.

Для достижения этого в предлагаемой в изобретении ячейке памяти используются записывающий транзистор, который соединен с узлом ЗУ, и считывающий транзистор, затвором которого служит узел ЗУ. Подробно предлагаемое в изобретении ЗУ рассмотрено ниже на примере предпочтительных вариантов его выполнения. В предлагаемом ЗУ первая словарная, или числовая, шина может быть соединена с узлом ЗУ. Записывающий транзистор может быть выполнен в виде транзистора с многослойной подложкой, состоящей из нескольких несущих и нескольких барьерных слоев, при этом вторая словарная шина используется в качестве затвора транзистора.

Поскольку при таком исполнении ЗУ его узел не соединен с кремниевой подложкой, ток утечки не может протекать из кремниевой подложки в узел ЗУ, что принципиально отличает предлагаемое ЗУ от обычного ДЗУПВ. Кроме того, поскольку между узлом ЗУ и истоком транзистора, который соединен с шиной передачи данных записывающего транзистора, имеются запирающие слои в качестве изоляторов, в отличие от ячейки памяти обычного ДЗУПВ в предлагаемом ЗУ протекающий между истоком и стоком транзистора при считывании записанных зарядов ток, имеющий величину ниже пороговой, можно подавить.

Кроме того, в ДЗУПВ ток утечки и токи, имеющие величину ниже пороговой, снижают эффективность происходящего в нем процесса запоминания. По этой причине, как уже сказано выше, ДЗУПВ требует периодической регенерации. Обычно регенерация должна периодически повторяться с интервалом около 100 мс.

В предлагаемом в изобретении ЗУ после отключения источника питания словарная шина, шина передачи данных, шина считывания и шина управления обесточиваются и напряжение на них становится равным 0 В. Поэтому в предлагаемом в изобретении ЗУ, в котором не происходит утечки тока из подложки, заряды в узле ЗУ можно удерживать за счет выполнения запирающего слоя достаточно толстым или за счет достаточно высокого порогового напряжения записывающего транзистора. Предлагаемое в настоящем изобретении ЗУ можно использовать как энергонезависимое полупроводниковое ЗУ. С целью сделать пороговое напряжение записывающего транзистора достаточно высоким концентрация легирующей примеси в его запирающей подложке должна быть достаточно высокой.

Для обеспечения нормальной работы ЗУ и предотвращения стирания зарядов в узле ЗУ необходимо соответствующим образом выбрать зависимость между напряжением на невыбранной словарной шине и пороговым напряжением записывающего транзистора. В этом случае предлагаемое ЗУ будет работать аналогично обычному СЗУПВ.

В зависимости от степени подавления во время работы тока утечки и тока, имеющего величину ниже пороговой, предлагаемое ЗУ может быть выполнено в виде полупроводникового устройства с характеристикой, меняющейся от характеристики полностью энергонезависимого ЗУ до характеристики обычного ДЗУПВ. При отсутствии запирающего слоя предлагаемое ЗУ требует регенерации подобно ДЗУПВ в случае, когда запирающий слой имеет толщину, сравнимую с толщиной аналогичного слоя флэш-памяти, которая является одним из видов энергонезависимого ЗУ, предлагаемое ЗУ может быть выполнено в виде энергонезависимого ЗУ. Поэтому предлагаемое в изобретении ЗУ имеет существенное преимущество, заключающееся в том, что за счет выбора материала запирающего слоя и его толщины, а также выбора материала запирающей подложки и концентрации примесей в нем можно реализовать тот или иной характер его работы.

Если, например, запирающий слой в предлагаемом ЗУ выполнить тонким, ток, имеющий величину ниже пороговой, будет протекать через него, однако величина протекающего тока будет при этом меньше, чем в ДЗУПВ, так как в предлагаемом ЗУ ток, имеющий величину ниже пороговой, может быть в определенной степени подавлен, и поэтому предлагаемое ЗУ может работать как обычное ДЗПУВ с относительно большим интервалом между регенерациями при пониженной величине потребляемой мощности. Снижение потребляемой мощности позволяет использовать резервный аккумулятор или другое аналогичное устройство, и поэтому предлагаемое ЗУ в его полной конфигурации, включая аккумулятор, можно рассматривать как псевдоэнергонезависимое ЗУ.

С другой стороны, изобретение позволяет путем изготовления матрицы из большого количества ячеек памяти, соединенных одна с другой шиной управления, шиной считывания, шиной передачи данных, первой словарной шиной, второй словарной шиной и т.п., создать достаточно большое ЗУ.

Примером одного из основных вариантов изобретения является ЗУ, в котором имеется ячейка памяти и соединенные с ней шина передачи данных, словарная шина и шина считывания.

Ячейка памяти имеет предназначенный для сохранения зарядов узел ЗУ, элемент записи, выполненный в виде пути для инжекции зарядов в узел ЗУ или для удаления зарядов из узла ЗУ, а также элемент считывания хранящегося в узле ЗУ заряда. Элемент считывания содержит первый транзистор, пороговое напряжение которого меняется в зависимости от заряда, хранящегося в узле ЗУ, и шину считывания, которая соединена с истоком/стоком первого транзистора. Записывающий элемент расположен между узлом ЗУ и шиной передачи данных и представляет собой второй транзистор, который имеет многослойную структуру из изоляторов и полупроводниковых слоев, и электрод управления, выполненный на боковой стороне многослойной структуры. В ЗУ имеется также словарная шина, которая соединена с электродом управления.

В таком ЗУ первый транзистор может быть выполнен на многослойной подложке, а второй транзистор может быть расположен на первом транзисторе. Иначе говоря, в таком ЗУ, если смотреть на подложку сверху вниз, первый и второй транзисторы частично или полностью перекрывают друг друга, что позволяет соответствующим образом уменьшить площадь всей микросхемы.

В таком ЗУ первый транзистор выполнен в виде полевого транзистора, затвор которого может служить узлом ЗУ. На боковой стороне электрода затвора через изолятор можно разместить второй электрод управления. В этом случае электрод управления можно выполнить на боковой стороне узла ЗУ или транзистора. При этом электрод управления может располагаться в плоскости, перпендикулярной плоскости подложки, или в плоскости, пересекающей плоскость подложки.

В другом варианте изобретения предлагается устройство, содержащее МДП-транзистор (полевой транзистор со структурой металл-диэлектрик-полупроводник) и многослойную структуру, состоящую из полупроводниковых слоев и запирающих слоев в качестве изоляторов и сформированную на затворе указанного МДП-транзистора. В этом ЗУ информация записывается или стирается инжекцией в затвор или удалением из затвора зарядов через вышеупомянутую многослойную структуру, и считывается с помощью шины считывания, которая соединена с истоком/стоком МДП-транзистора. Указанный МДП-транзистор является транзистором обнаружения и его затвор служит узлом ЗУ. Многослойная структура, которая соединена с узлом ЗУ, действует как барьер, контролирующий инжекцию зарядов в узел ЗУ или удаление зарядов из узла ЗУ.

Ниже изобретение более подробно поясняется на примере предпочтительных вариантов его выполнения со ссылкой на прилагаемые чертежи, на которых показаны:

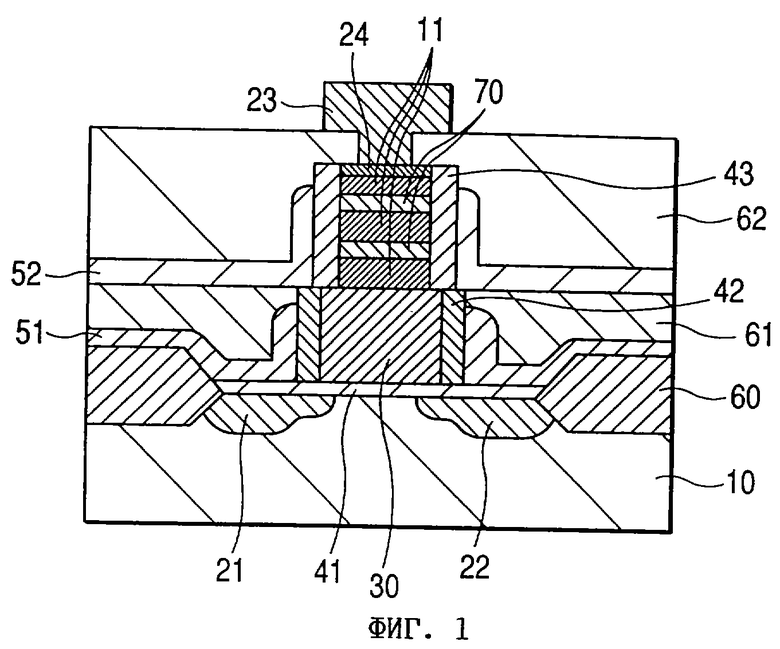

на фиг. 1 - поперечное сечение ЗУ, выполненного по первому варианту настоящего изобретения,

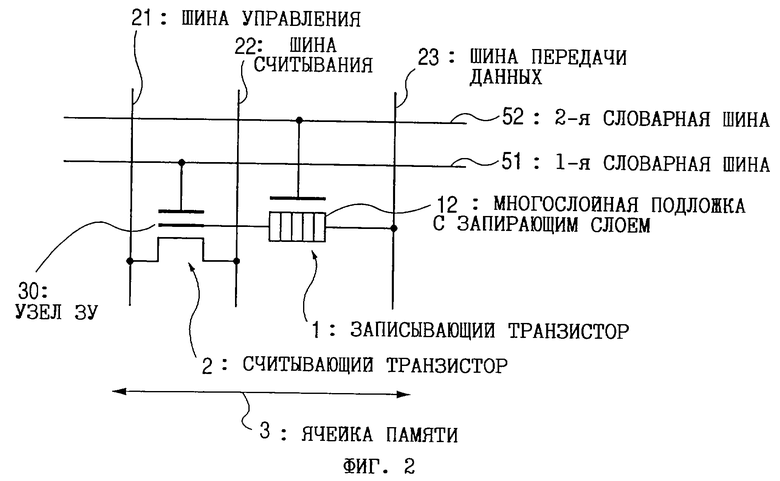

на фиг. 2 - электронная схема ЗУ, выполненного по первому варианту настоящего изобретения,

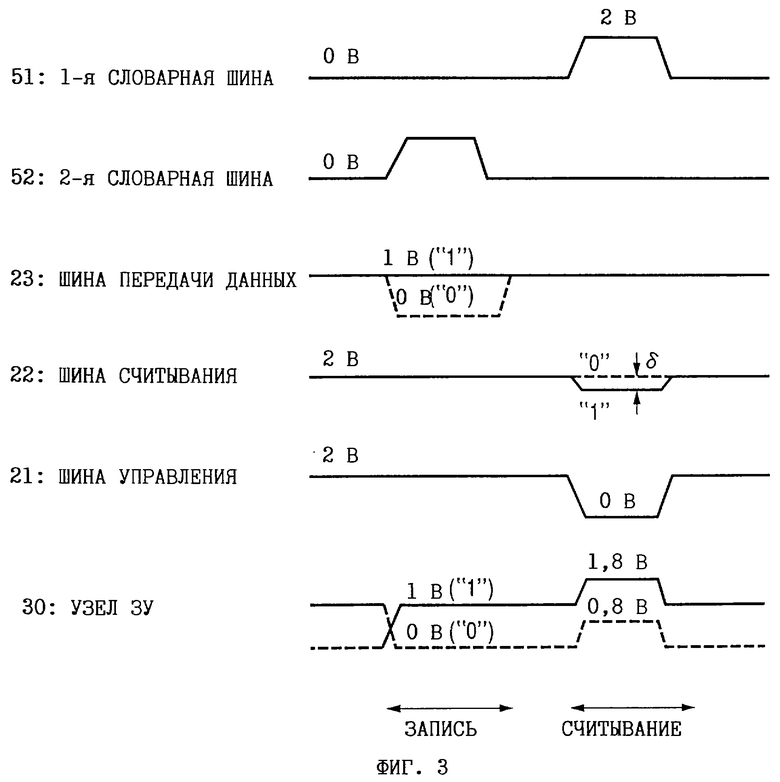

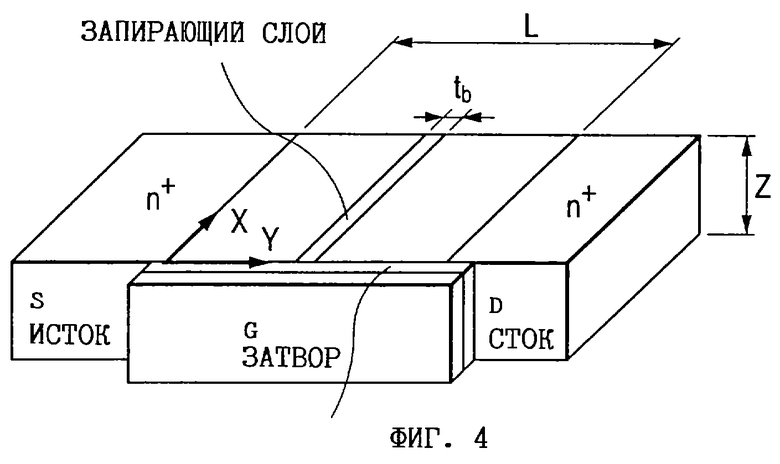

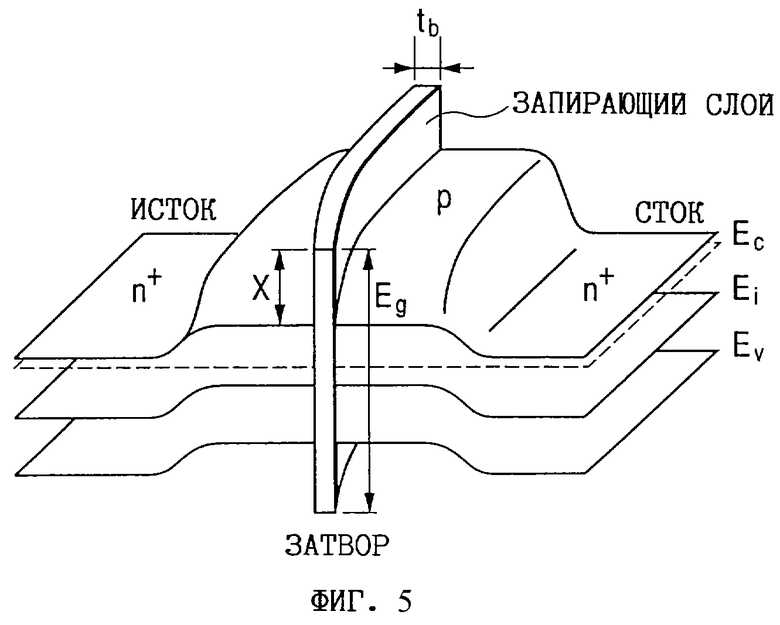

на фиг. 3-9 - чертеж, иллюстрирующий работу одного из вариантов настоящего изобретения,

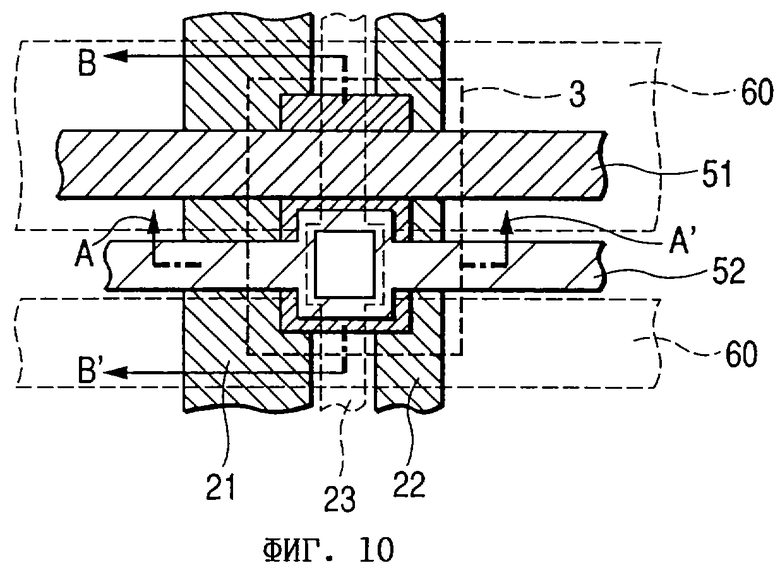

на фиг. 10 - вид сверху ЗУ, выполненного по второму варианту настоящего изобретения,

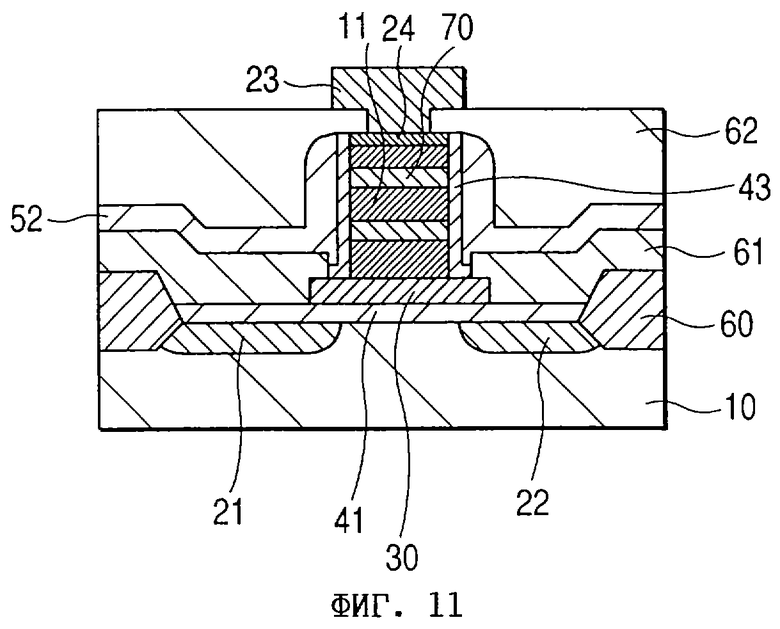

на фиг.11 - поперечное сечение ЗУ, выполненного по второму варианту настоящего изобретения,

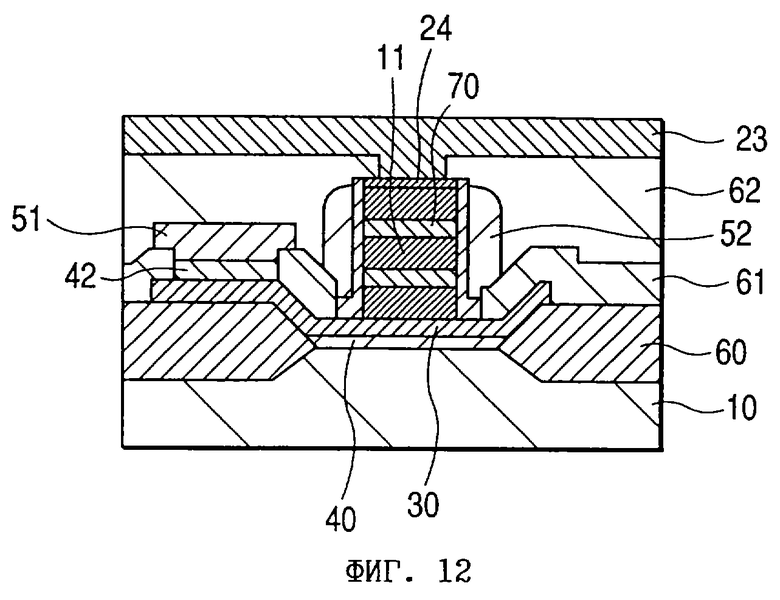

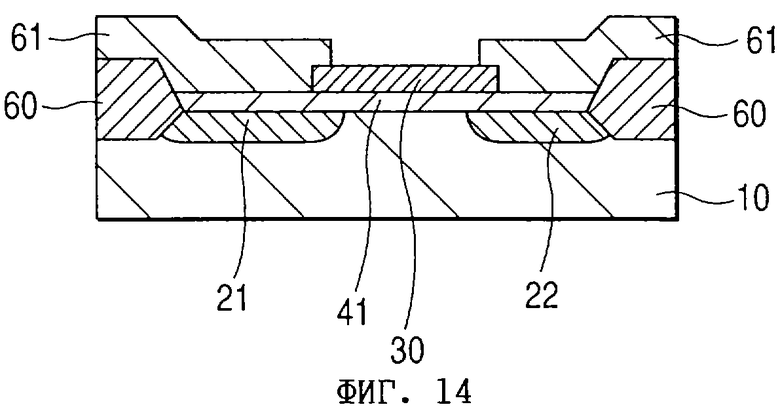

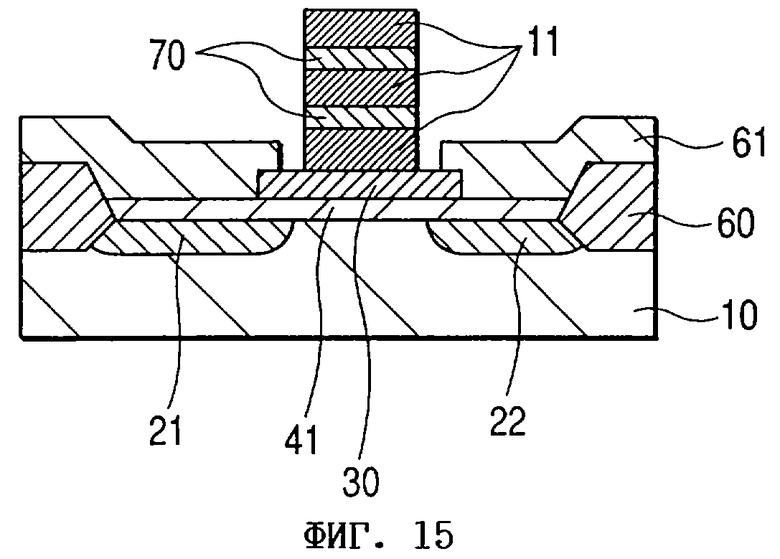

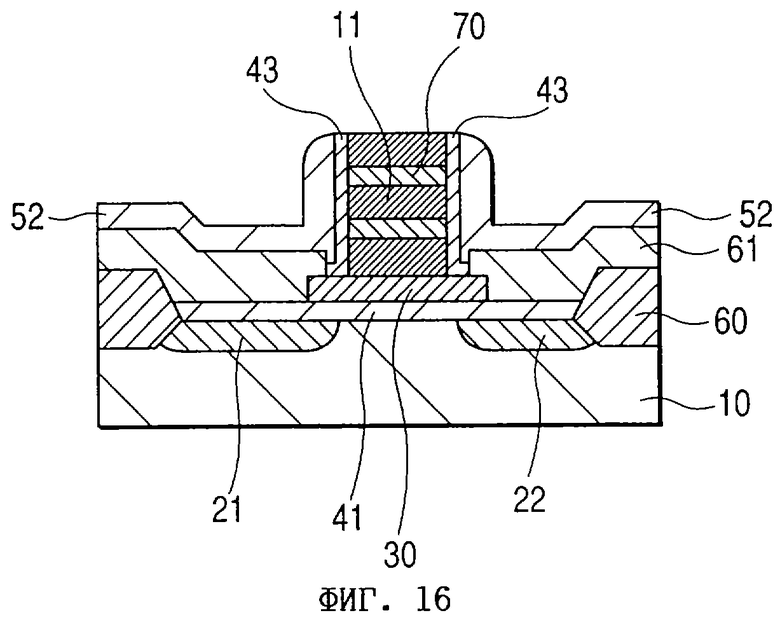

на фиг. 12-16 - чертежи, иллюстрирующие последовательность операций по изготовлению ЗУ, выполненного по второму варианту настоящего изобретения,

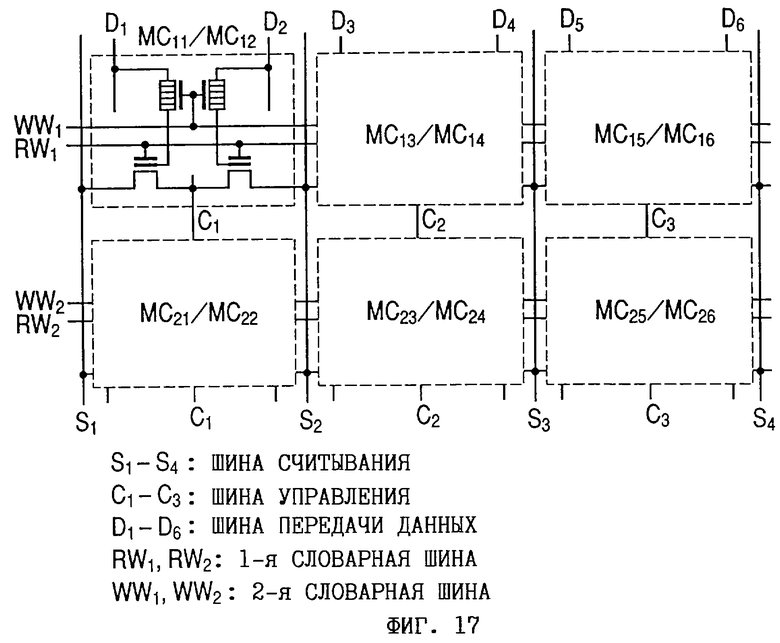

на фиг.17 - схема предлагаемой в настоящем изобретении матрицы памяти,

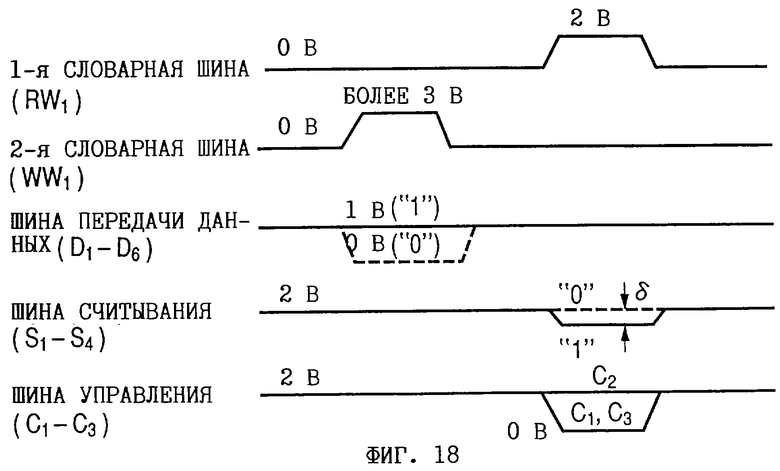

на фиг.18 - временная диаграмма, иллюстрирующая последовательность операций работы предлагаемой в изобретении матрицы памяти,

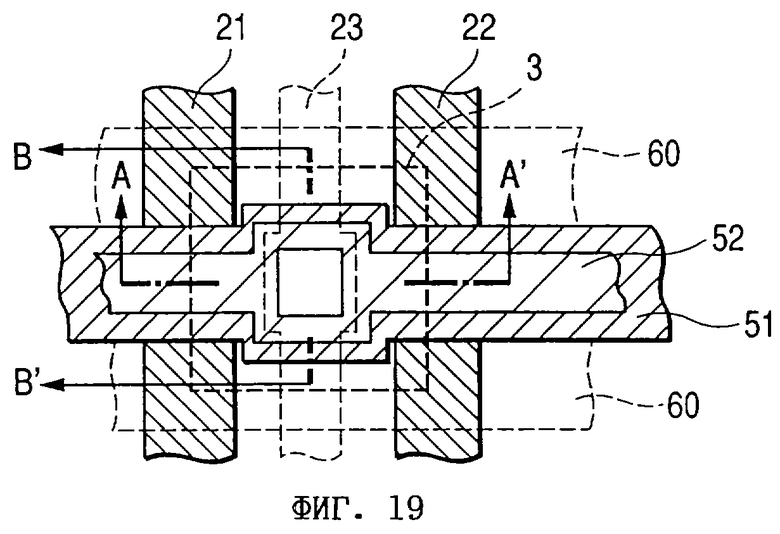

на фиг. 19 - вид сверху ЗУ, выполненного по первому варианту настоящего изобретения,

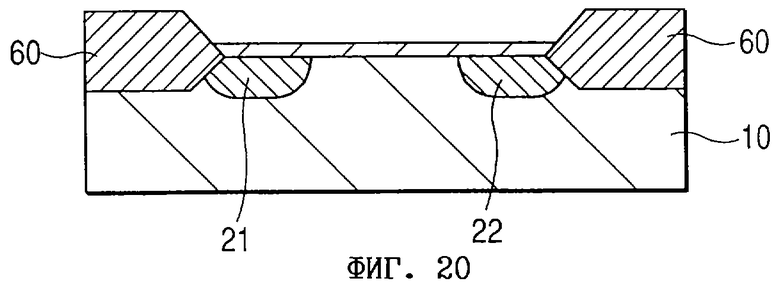

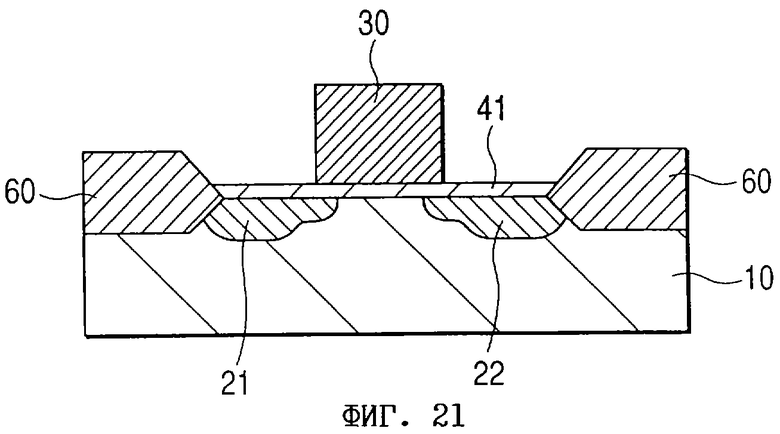

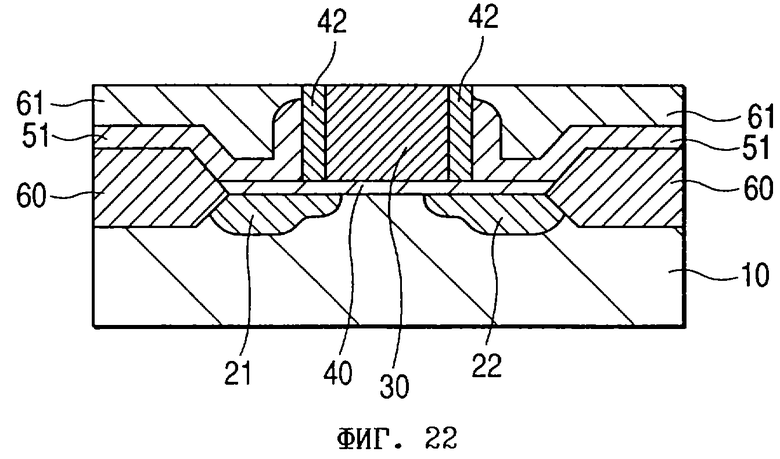

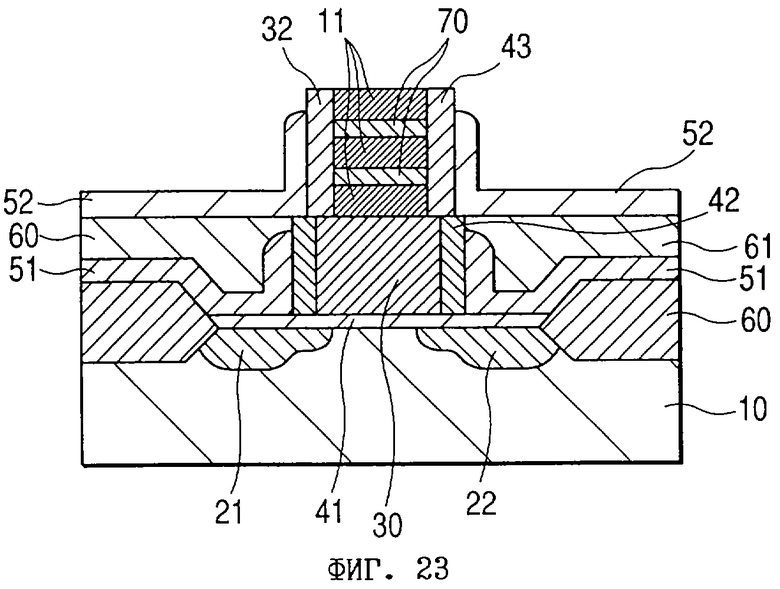

на фиг. 20-23 - чертежи, иллюстрирующие последовательность операций по изготовлению ЗУ, выполненного по первому варианту настоящего изобретения,

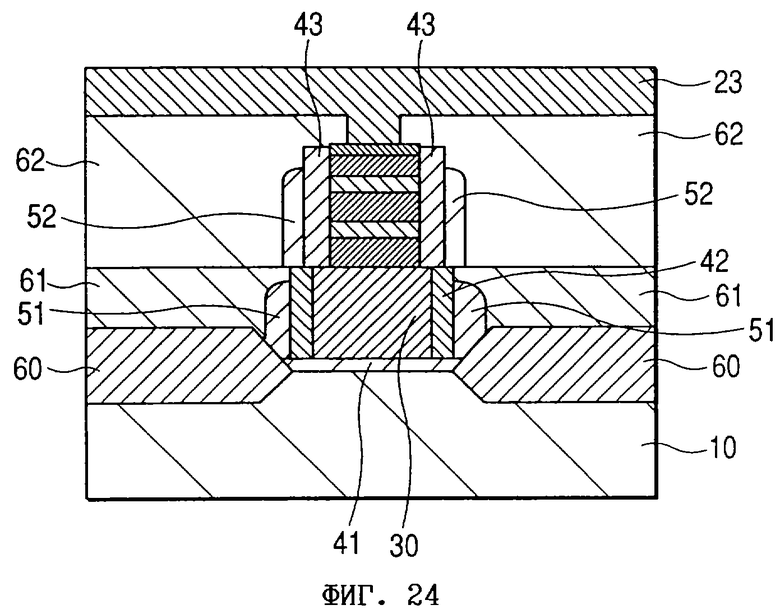

на фиг.24 - поперечное сечение ЗУ, выполненного по первому варианту настоящего изобретения,

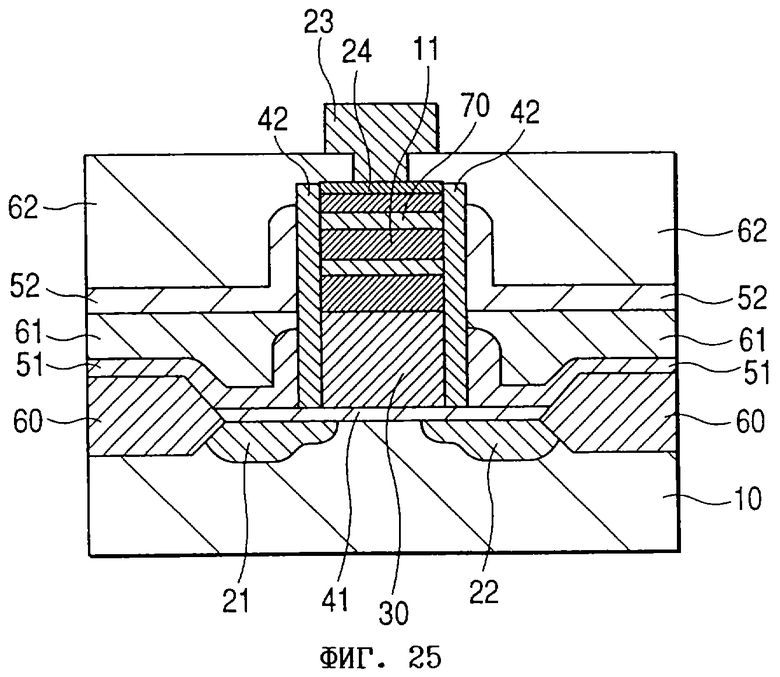

на фиг. 25 - поперечное сечение ЗУ, выполненного по третьему варианту настоящего изобретения,

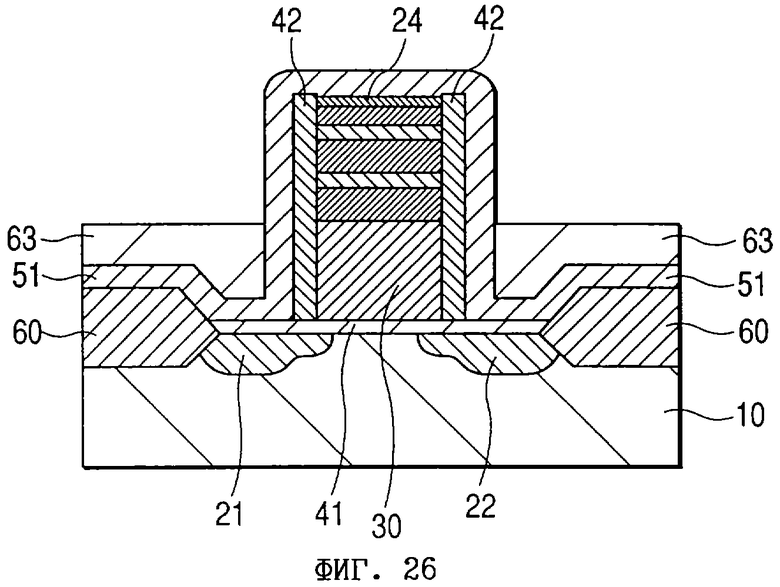

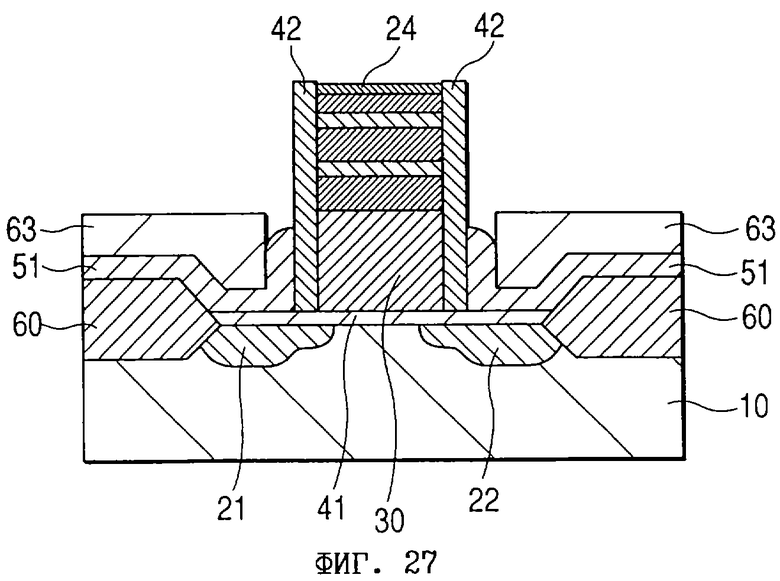

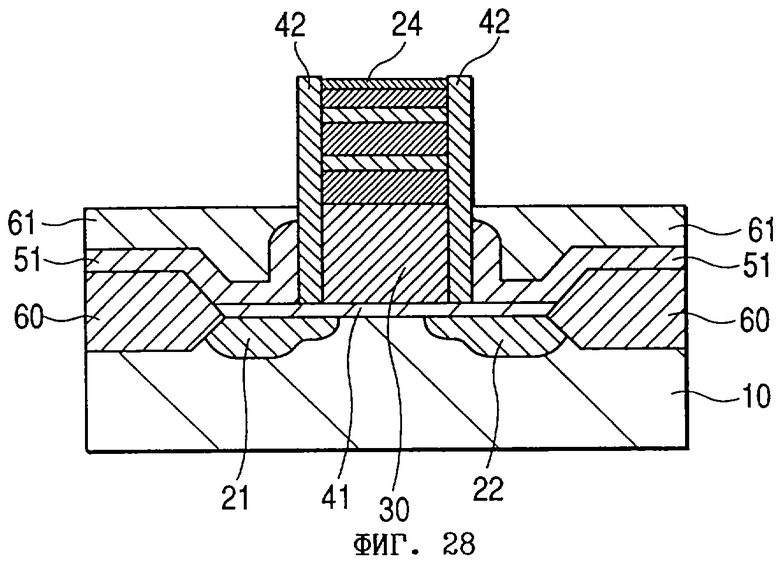

на фиг. 26-28 - чертежи, иллюстрирующие последовательность операций по изготовлению ЗУ, выполненного по третьему варианту настоящего изобретения,

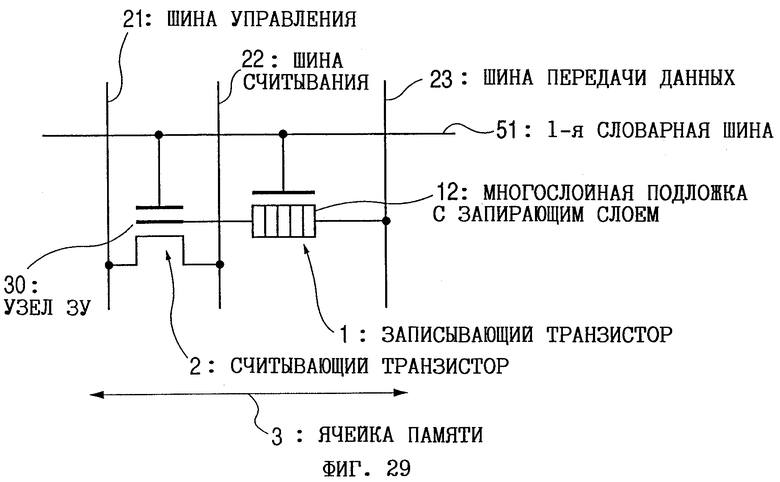

на фиг.29 - электрическая схема ЗУ, выполненного по четвертому варианту настоящего изобретения,

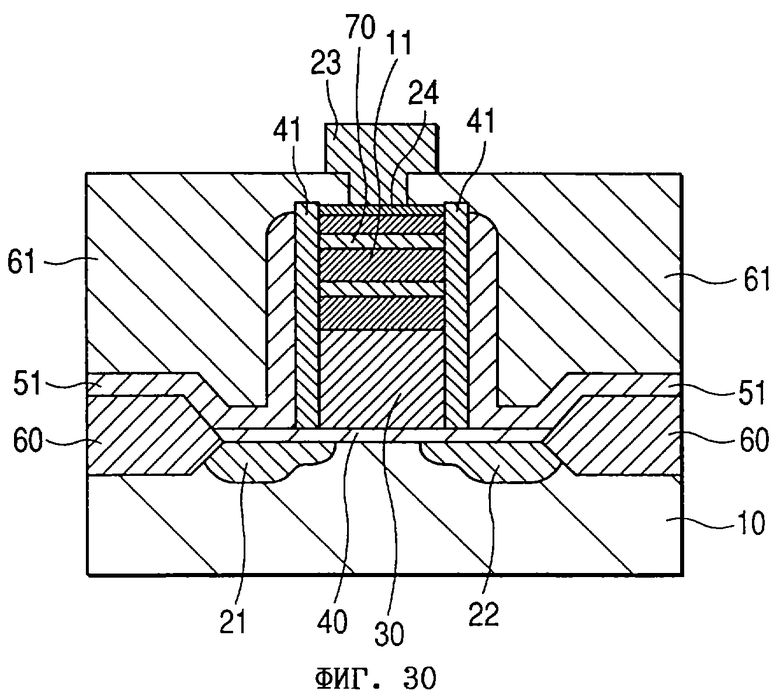

на фиг. 30 - поперечное сечение ЗУ, выполненного по четвертому варианту настоящего изобретения,

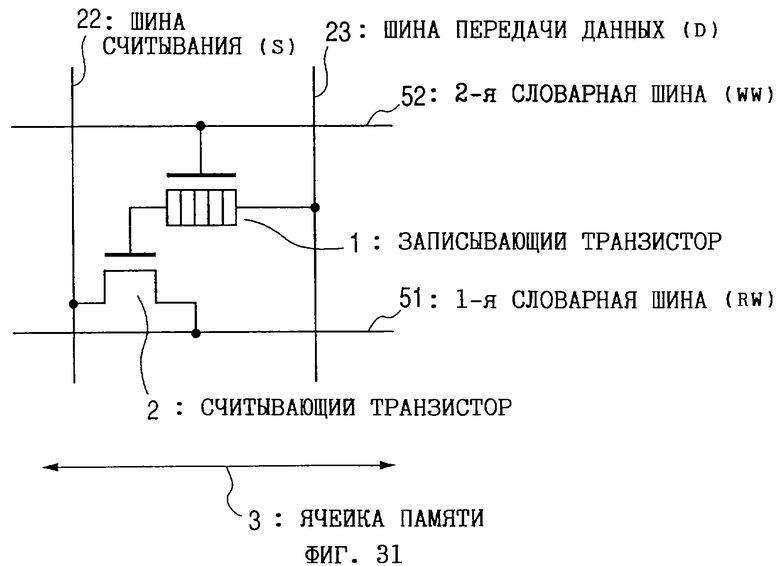

на фиг. 31 - схема ячейки памяти, выполненной по пятому варианту настоящего изобретения,

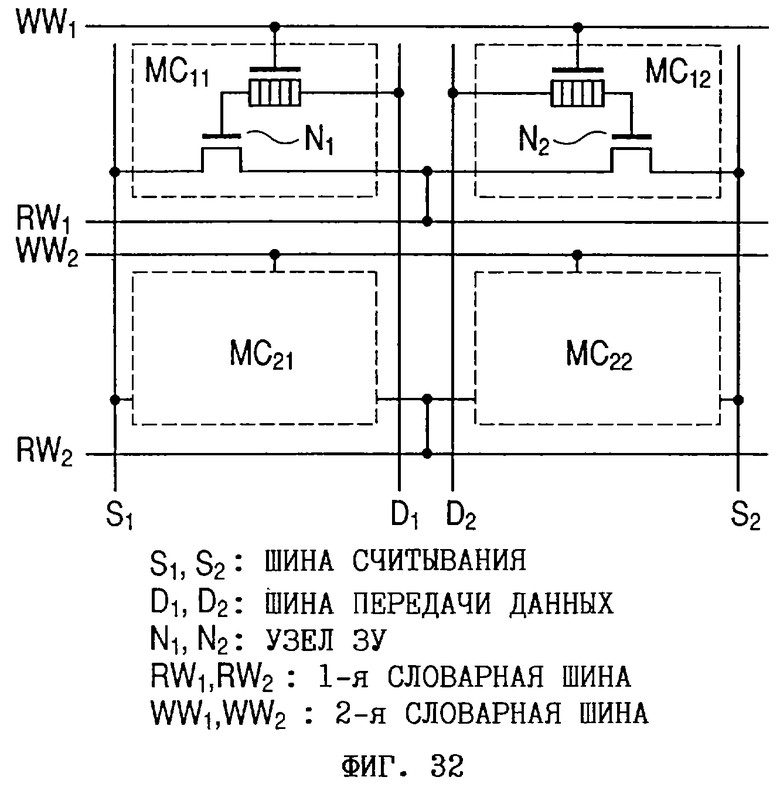

на фиг.32 - схема матрицы памяти, состоящей из ячеек памяти, выполненных по пятому варианту настоящего изобретения,

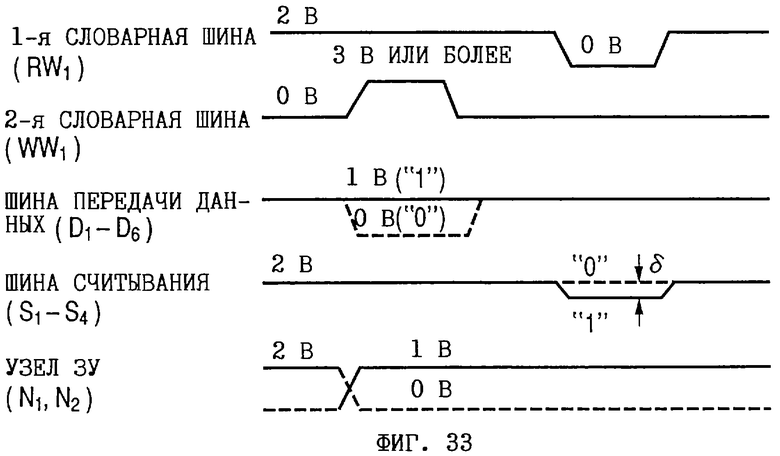

на фиг. 33 - временная диаграмма, иллюстрирующая работу ячейки памяти, выполненной по пятому варианту настоящего изобретения,

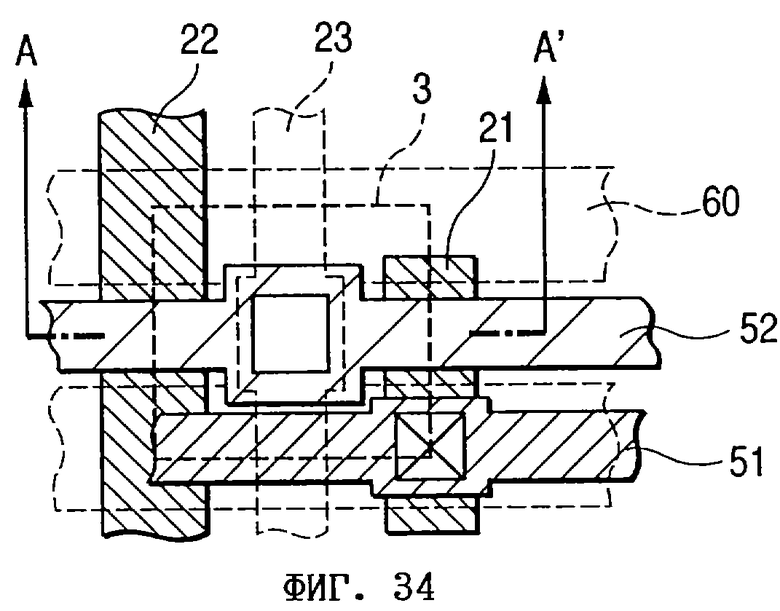

на фиг. 34 - вид сверху ячейки памяти, выполненной по пятому варианту настоящего изобретения, и

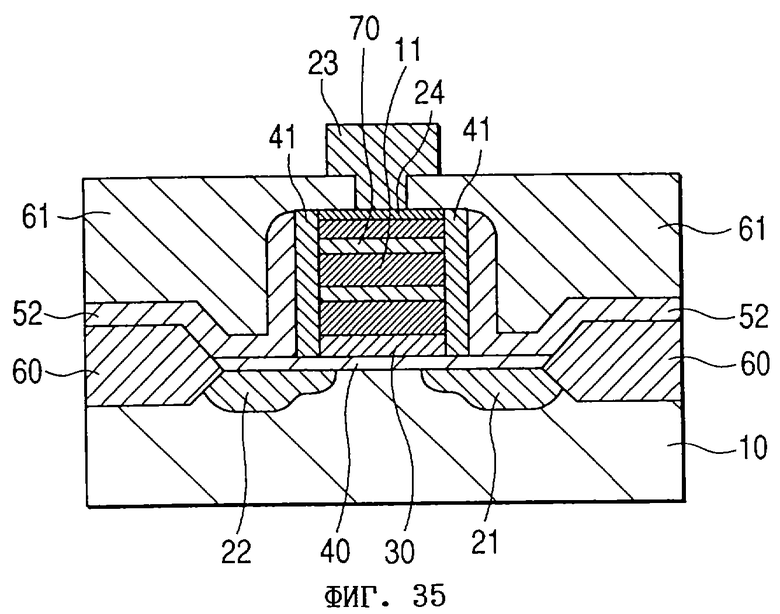

на фиг.35 - поперечное сечение ячейки памяти, выполненной по пятому варианту настоящего изобретения.

На фиг. 1 и 2 показаны соответственно выполненное по первому варианту изобретения ЗУ и его электрическая схема.

На фиг. 1 показан основной вариант конструкции предлагаемого в изобретении ЗУ. Позицией 10 обозначена кремниевая подложка с проводимостью р-типа, имеющая удельное сопротивление порядка 10 Ом•см, позицией 60 обозначен полевой изолятор, позицией 21 обозначена шина управления, которая образована обладающей проводимостью n+-типа областью подложки, и позицией 22 обозначена шина считывания, которая также образована обладающей электронной проводимостью областью подложки. Первый подзатворный изолятор 41 сформирован на поверхности кремниевой подложки 10, а узел 30 ЗУ сформирован на первом подзатворном изоляторе 41. Второй подзатворный изолятор 42 сформирован вокруг боковой стороны узла 30 ЗУ, а первая словарная, или числовая, шина 51 закрывает второй подзатворный изолятор 42. Между первой словарной шиной 51 и узлом 30 ЗУ в том месте, где расположен второй подзатворный изолятор 42, образован электрический конденсатор. На узле 30 ЗУ сформирована многослойная подложка 12 (фиг. 2) с запирающими слоями, которая состоит из подложек 11 из поликристаллического кремния или аморфного кремния и запирающих слоев 70, которые выполнены из оксида кремния, нитрида кремния или их смеси, т.е. оксида/нитрида кремния. Третий подзатворный изолятор 43 сформирован вокруг боковой поверхности подложек 11 и запирающих слоев 70. Вторая словарная шина 52, которая используется как затвор транзистора, имеет подложку 12 и образована на боковой поверхности третьего подзатворного изолятора 43. В верхней части подложки 12 расположены обладающая проводимостью n+-типа область 24 истока и шина 23 передачи данных, которая соединена с обладающей проводимостью n+-типа областью 24 истока.

На фиг.2 показана электрическая схема описанной выше ячейки памяти, состоящей из перечисленных слоев и подложек. Располагая такие ячейки памяти в матрицу, состоящую из m-столбцов и n-строк, можно изготовить ЗУ большого размера. Например, для создания ЗУ емкостью 1 Мбит необходимо из отдельных ячеек памяти сформировать матрицу из 1024 столбцов и 1024 строк.

Как показано на фиг.1 и 2, предлагаемая ячейка памяти состоит из записывающего транзистора 1, который соединен с узлом 30 ЗУ, и считывающего транзистора 2, затвором которого служит узел 30 ЗУ. На фиг.1 также показано, что записывающий транзистор 1 представляет собой транзистор, подложкой которого служит многослойная подложка 12, состоящая из подложек 11 и запирающих слоев 70, а его затвором служит вторая словарная шина 52.

В таком ЗУ в отличие от ячейки памяти обычного ДЗУПВ узел ЗУ не связан с кремниевой подложкой, а ток из кремниевой подложки не течет в узел ЗУ. Кроме того, имеющиеся в таком ЗУ запирающие слои служат изоляторами между узлом ЗУ и истоком записывающего транзистора, который соединен с шиной передачи данных, что создает возможность для подавления тока, величина которого ниже пороговой и который, как описано выше, протекает в ячейке памяти обычного ДЗУПВ между истоком и стоком считывающего транзистора при записи поступающих в ЗУ и подлежащих хранению в нем зарядов.

В предлагаемом в изобретении ЗУ после полного отключения источника питания словарная шина, шина передачи данных, шина считывания и шина управления обесточиваются, и напряжение на них становится равным 0 В, и в этом случае из кремниевой подложки в узел ЗУ ток не течет, а электрические заряды в узле ЗУ могут храниться достаточно долго, если при этом запирающие слои выполнить достаточно толстыми или задать достаточно высоким пороговое напряжение записывающего транзистора. При соблюдении этих условий предлагаемое в изобретении ЗУ представляет собой по существу энергонезависимое ЗУ. Пороговое напряжение записывающего транзистора может быть сделано достаточно высоким за счет увеличения концентрации примеси, содержащейся в подложках 11 запирающих слоев.

Одним из условий работоспособности ЗУ является отсутствие потерь зарядов, хранящихся в узле ЗУ, во время прохождения тока через ЗУ; в предлагаемом ЗУ это условие достигается соответствующим выбором зависимости между напряжением невыбранной словарной шины и пороговым напряжением записывающего транзистора. При выполнении этого условия предлагаемое ЗУ может работать как обычное СЗУПВ.

В зависимости от изменения степени подавления тока утечки и тока, имеющего величину ниже пороговой, предлагаемое в изобретении ЗУ может работать как по характеристике полностью энергонезависимого ЗУ, так и по характеристике обычного ДЗУПВ. Если предлагаемое ЗУ не имеет запирающего слоя 70, то оно регенерируется аналогично обычной ячейке ДЗУПВ. С другой стороны, если предлагаемое ЗУ имеет запирающий слой 70 большой толщины, сравнимой с толщиной такого же слоя флэш-памяти, которая является одним из видов энергонезависимого ЗУ, то предлагаемое ЗУ может работать как энергонезависимое ЗУ. Следовательно, предлагаемое в изобретении ЗУ обладает существенным преимуществом, заключающимся в том, что, выбрав соответствующим образом материал запирающего слоя 70 и его толщину, а также материал подложки 11 барьера и концентрацию примесей в ней, можно обеспечить его работу по любой из двух указанных выше характеристик.

В частности при малой толщине запирающего слоя через ЗУ может протекать ток, величина которого ниже пороговой. Однако в предлагаемом ЗУ величина этого тока меньше, чем в обычном ДЗУПВ, поскольку ток, имеющий величину ниже пороговой, в предлагаемом ЗУ так или иначе подавлен, и при этом предлагаемое ЗУ может работать как обычное ДЗУПВ с достаточно большим интервалом времени между регенерациями при меньшем потреблении мощности. Уменьшение потребляемой мощности позволяет использовать резервный аккумулятор или другое аналогичное устройство, и поэтому в полной конфигурации с аккумулятором предлагаемое ЗУ может рассматриваться как псевдоэнергонезависимое ЗУ.

С другой стороны, путем объединения большого количества ячеек памяти в матрицу и подключения каждой из них к шине 21 управления, шине 22 считывания, шине 23 передачи данных, первой словарной шине 51, второй словарной шине 52 и т.п. можно реально создать большое по степени интеграции ЗУ.

На фиг.3 показана временная диаграмма работы предлагаемого в изобретении ЗУ при записи в ячейку памяти и считывания из нее. В этой временной диаграмме принято, что пороговые напряжения записывающего транзистора и считывающего транзистора равны соответственно 2 В и 1,2 В, а напряжение, приложенное к узлу 30 ЗУ через первый подзатворный изолятор 41 от электрического конденсатора, который образован первой словарной шиной 51 и узлом 30 ЗУ, равно 0,8 В.

Операция записи выполняется подачей импульсов на вторую словарную шину и воздействием на узел ЗУ по шине передачи данных напряжением записи информации, равным 1 В (соответствующим информации "1") или 0 В (соответствующим информации "0"). Поскольку напряжение словарной шины достаточно велико (3 В или больше), напряжение шины передачи данных записывается в узле ЗУ без превышения в это время порогового напряжения (2 В) записывающего транзистора.

Операция считывания выполняется подачей импульсов на первую словарную шину и шину управления с распознаванием состояния считывающего транзистора, который в это время должен быть открыт. Точнее говоря, упомянутое распознавание заключается в определении "1" или "0" информации на основе наличия или отсутствия тока в шине считывания или наличия или отсутствия на ней микронапряжения. Например, при подаче импульсов по первой словарной шине напряжение узла ЗУ повышается до 1,8 В или 0,8 В и в этом случае, поскольку напряжение шины управления будет равно 0 В, а пороговое напряжение считывающего транзистора составляет 1,2 В, если в узле ЗУ содержится информация "1", считывающий транзистор откроется, а если в узле ЗУ содержится информация "0", считывающий транзистор закроется. При подключении к другому концу шины считывания сопротивления (МОП-транзистора или резистора), рассчитанного на 2 В, при считывании информации "1" напряжение шины считывания снизится от 2 В на малую величину δ (приблизительно 200 мВ), а при считывании информации "0" напряжение шины считывания останется равным 2 В. Такая разность напряжений легко распознается соединенной с шиной считывания специальной детекторной схемой.

Необходимо отметить, что операции считывания не препятствуют остальные невыбранные элементарные ячейки памяти, соединенные с той же самой шиной считывания и шиной управления и расположенные в направлении шины считывания. Объясняется это тем, что, поскольку на первые словарные шины не выбранных элементарных ячеек памяти не поступают импульсы, узел ЗУ каждой из невыбранных элементарных ячеек памяти будет находиться под напряжением 1 В или 0 В, которое ниже порогового напряжения считывающего транзистора, и соответственно считывающий транзистор каждой из невыбранных элементарных ячеек памяти будет находиться в запертом состоянии.

Предлагаемая в изобретении и описанная выше ячейка памяти отличается небольшим током утечки через р-n-переход и высоким сопротивлением к случайным сбоям, обусловленным влиянием α-частиц. Однако в зависимости от величины порогового напряжения записывающего транзистора информационные заряды могут попадать в шину передачи данных через записывающий транзистор и вносить тем самым определенную погрешность в работу ЗУ. Если пороговое напряжение транзистора достаточно велико и составляет, например, приблизительно 2 В, то даже при отключении источника питания и обесточивания словарной и других шин, на которых в этот момент напряжение становится равными 0 В, предлагаемое ЗУ может работать как энергонезависимое, поскольку в это время ток через записывающий транзистор не течет; кроме того, заряды в невыбранных элементарных ячейках памяти не попадают в шину передачи данных даже при их случайных срабатываниях во время переноса тока. Таким образом, применение транзистора с высоким пороговым напряжением позволяет создать ЗУ, которое в отличие от обычного СЗУПВ не требует периодической регенерации.

Однако при определенной конфигурации запирающего слоя или при работе с пониженным напряжением на второй словарной шине неизбежно возникают ситуации, когда пороговое напряжение транзистора необходимо уменьшить. При слишком малом пороговом напряжении транзистора заряды в узле ЗУ стекают в шину передачи данных через записывающий транзистор. В этом случае аналогично обычному ДЗУПВ для сохранения накопленной информации ЗУ необходимо регенерировать. Операция регенерации выполняется считыванием хранящейся в ЗУ информации специальной детекторной схемой, соединенной с шиной считывания, преобразованием полученного результата в напряжение записи на шине передачи данных и перезаписью этих данных в ячейку памяти. Очевидно, что предлагаемая ячейка памяти имеет в этом отношении определенное преимущество, заключающееся в том, что из-за небольшого тока утечки через р-n-переход время хранения информации в ней может быть увеличено по сравнению с обычной ячейкой ДЗУПВ соответственно.

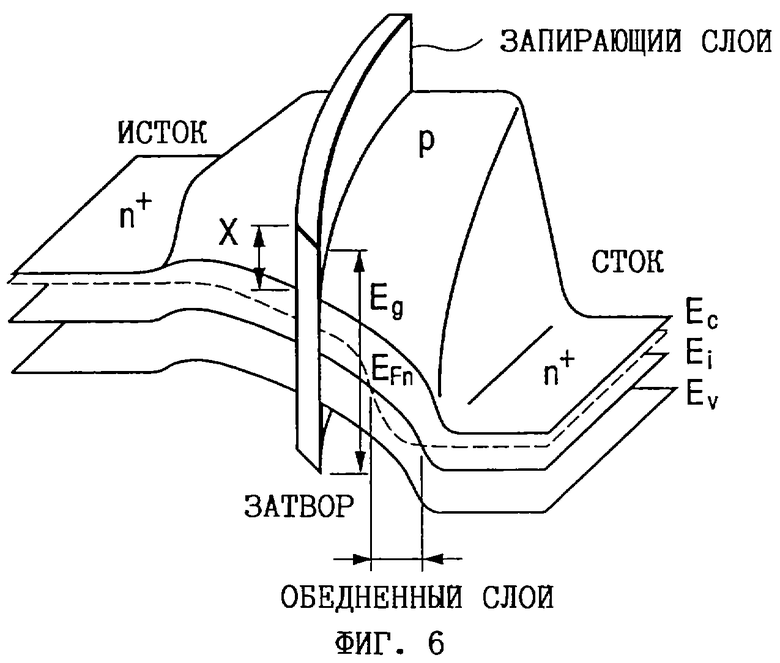

Работа транзисторов, которые имеют подложку с одним или несколькими запирающими слоями, иллюстрируется фиг.4-9.

На фиг. 4 показана структура транзистора с подложкой, имеющей один запирающий слой толщиной tb, выполненный внутри подложки обычного n-канального транзистора между истоком и стоком.

На фиг. 5 показана структура энергетической зоны транзистора, изображенного на фиг.4. Обычно запирающий слой представляет собой изолятор и имеет запрещенную энергетическую зону шириной Еg. Для n-канального транзистора, подложка которого имеет один запирающий слой, существует зона проводимости, уровень которой превышает уровень "с" электронного сродства, который превышает Еc проводника.

В состоянии, показанном на фиг.5, напряжение на затворе отсутствует, и для прохождения тока между истоком и стоком транзистора необходимо, чтобы либо запирающий слой был достаточно тонким для возможности непосредственного прохождения через него туннельного тока, либо энергия электронов была достаточно большой для того, чтобы они могли преодолеть уровень электронного сродства "с". Фактически протекание тока в зависимости от толщины запирающего слоя происходит как за счет небольшой толщины слоя, так и за счет достаточно высокой энергии электронов.

На фиг. 6 показано положение и структура энергетических зон при подаче положительного напряжения на затвор транзистора, изображенного на фиг.5. Ток, текущий между истоком и стоком транзистора, может, как показано на фиг. 6, контролироваться затвором G. В предлагаемом транзисторе, как и в обычном транзисторе при положительном напряжении, большем порогового напряжения транзистора, энергетическая зона в плоскости затвора оказывается в значительной степени уменьшенной, в результате чего ток, текущий между истоком и стоком, возрастает. Кроме того, в рассматриваемом транзисторе энергия зоны проводимости запирающего изолятора ниже энергетического уровня истока, и при постоянном уровне электронного сродства "с" ток легко проходит через запирающий слой. По такому принципу работает и транзистор предлагаемой в изобретении ячейки памяти, в которой сток транзистора используется как узел ЗУ.

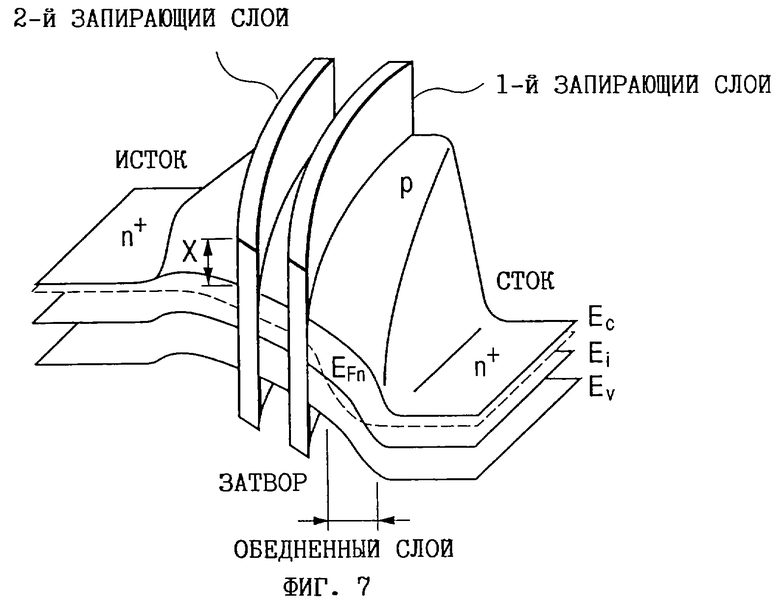

На фиг. 7 показано положение энергетических зон транзистора, подложка которого имеет два слоя запирающих изоляторов. В принципе при наличии многослойных изоляторов вероятность туннельного прохождения электронов через многослойные изоляторы равна вероятности туннельного прохождения электронов через один изолятор, толщина которого равна суммарной толщине многослойных изоляторов. Поэтому в тех случаях, когда при формировании одного толстого запирающего изолятора возникают те или иные трудности, можно использовать многослойные запирающие изоляторы, имеющие в сумме необходимую толщину.

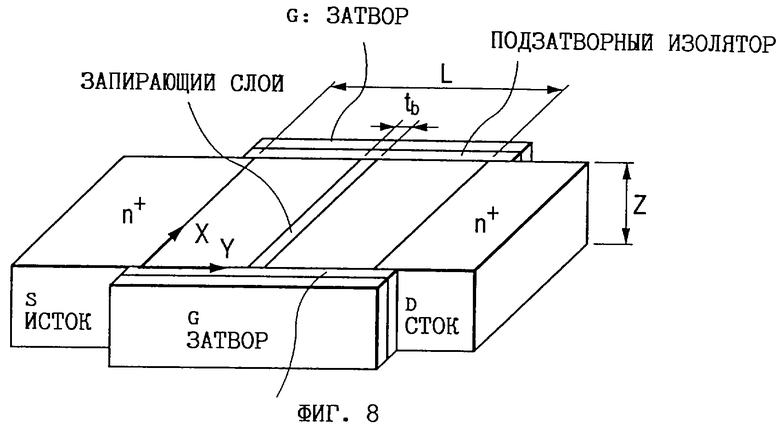

На фиг. 8 показана другая структура предлагаемого в изобретении ЗУ, в которой подложка, имеющая запирающий слой, расположена между двумя затворами. При отсутствии внешнего напряжения на подложке, имеющей такой же запирающий слой, как и структура, показанная на фиг.1, эта подложка находится в так называемом плавающем состоянии.

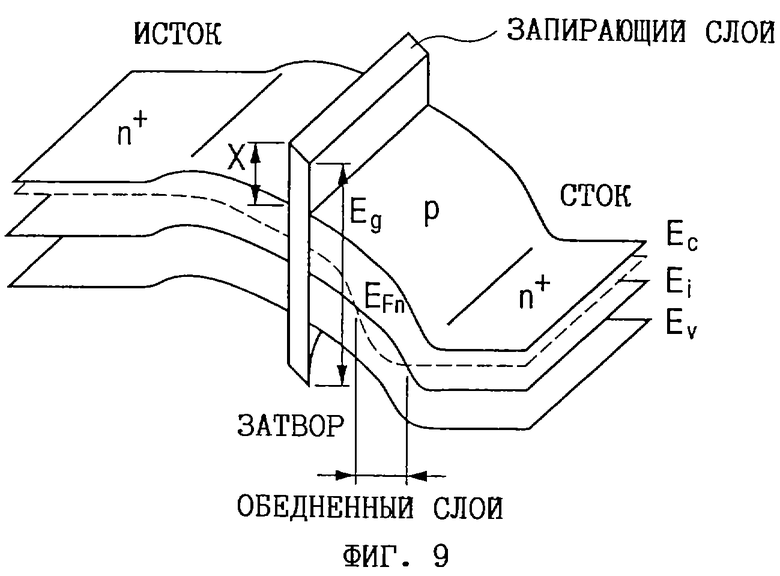

На фиг.9 показано положение энергетических зон транзистора, подложка которого имеет запирающий слой, показанный на фиг.8. Поскольку подложка, имеющая запирающий слой, находится в плавающем состоянии, при одинаковой концентрации примеси, легирующей подложку, в направлении, параллельном направлению от истока к стоку, как показано на фиг.9, в этом направлении никакого электрического поля создаваться не будет, и поэтому энергетическая зона в направлении, параллельном направлению от истока к стоку, будет оставаться плоской. В этом случае ток, текущий между истоком и стоком, уравнивается над подложкой, и в таком транзисторе по сравнению с показанным на фиг.6 транзистором, в котором электрические токи на поверхности подложки текут непосредственно под элементами затвора, подвижность носителей снижается, а количество электронов, образующихся в транзисторе с электронной проводимостью, становится меньше. В результате характеристика транзистора приобретает существенную крутизну.

Как подробно описано ниже при рассмотрении другого варианта предлагаемого в изобретении ЗУ, в показанных на фиг.8 и 9 структурах не требуется электрод для подачи внешнего напряжения к подложке, имеющей запирающий слой, в результате чего такое ЗУ обладает определенными преимуществами, связанными с тем, что оно имеет более простую структуру и занимает меньшую площадь.

Структура подложки с двумя запирающими слоями, показанная на фиг.7, может быть использована в транзисторе, показанном на фиг.8 и 9. Работа транзистора с такой подложкой ничем не отличается от работы рассмотренных выше транзисторов.

Следует подчеркнуть, что хотя в показанных на фиг.3-9 ЗУ для простоты описан n-канальный транзистор, образованный на подложке с проводимостью р-типа, изобретение не ограничено подложкой с таким типом проводимости, поскольку ток, текущий между истоком и стоком, по существу можно контролировать с помощью затвора. Иначе говоря, в предлагаемом в изобретении ЗУ могут использоваться различные по типу проводимости подложки, например, очень слабо легированная подложка с электронной проводимостью, обладающая собственной проводимостью подложка с очень высоким удельным сопротивлением и подложка с дырочной проводимостью. При необходимости можно управлять подложкой, подавая на нее низкое напряжение, и в этом случае концентрация примесей в подложке должна быть такой же, как и в подложке, обладающей собственной проводимостью.

С другой стороны, в запирающей подложке с дырочной проводимостью р-n-переход формируется между стоком и подложкой, и в этом случае при наличии обедненного слоя в нем образуются тепловые заряды возбуждения, которые вызывают потерю хранящейся в ЗУ информации. Поэтому при использовании подложек с дырочной проводимостью вид примеси и ее концентрацию выбирают, исходя из необходимости минимизировать заряды, возникающие при тепловом возбуждении.

На фиг. 10 показана в виде сверху ячейка памяти, выполненная по второму варианту настоящего изобретения. Эта ячейка памяти отличается тем, что узел 30 ЗУ выполнен плоским, а первая словарная шина 51 не расположена непосредственно под второй словарной шиной 52. По сравнению с ЗУ, выполненным по первому варианту изобретения, эта ячейка имеет меньшую высоту и более проста в изготовлении. На фиг.11 показано сечение плоскостью А-А' ячейки памяти по фиг. 10, а на фиг.12 показано сечение плоскостью В-В' ячейки памяти по фиг. 10. На этих чертежах элементы, аналогичные элементам, показанным на фиг.1, обозначены теми же самыми позициями, что и на фиг.1.

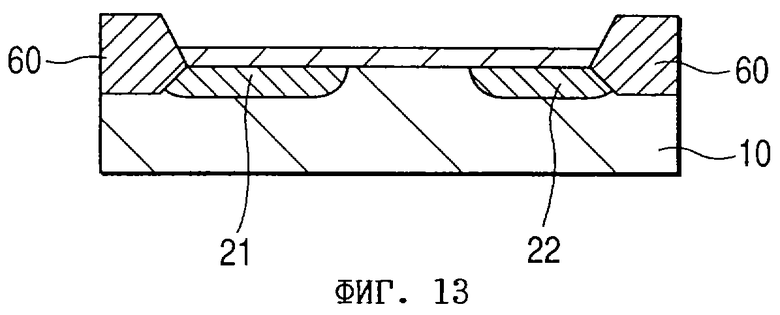

На фиг. 13-16 показана последовательность операций по изготовлению ЗУ, выполненного по второму варианту изобретения.

Как показано на фиг.13, обладающие проводимостью n+-типа области 21 и 22 сформированы в подложке из кремния с проводимостью р-типа, имеющей удельное сопротивление приблизительно 10 Ом•см, обычным способом фототравления и способом ионного легирования. Затем по технологии LOCOS (технология МОП ИС с оксидной изоляцией и толстым защитным слоем оксида кремния) с использованием слоя нитрида кремния, выборочно нанесенного на подложку во избежание ее окисления, выборочно наносят слой оксида кремния толщиной 500 нм, образующий полевой изолятор 60.

Как показано на фиг.14, затем на поверхность подложки 10 при 1000oС наносят слой оксида кремния толщиной 10 нм. Этот слой оксида кремния используют как первый подзатворный изолятор 41. На первый подзатворный изолятор 41 выборочно наносят слой поликристаллического кремния, который легирован примесью с проводимостью n+-типа и который используется как узел 30 ЗУ. Затем, как показано на фиг.11, на узел 30 ЗУ химическим осаждением из паровой фазы наносят слой первого промежуточного изолятора 61 толщиной 500 нм. После этого часть первого промежуточного изолятора 61, расположенную в определенном месте узла 30 ЗУ, удаляют и в этом месте на узел 30 наносят слой оксида кремния толщиной 10 нм. Этот слой оксида кремния образует второй подзатворный изолятор 42. На второй подзатворный изолятор 42 выборочно наносят слой проводящего поликристаллического кремния, который используется в качестве второй словарной шины 52.

Как показано на фиг.15, на узел 30 ЗУ нанесена запирающая подложка 11 толщиной 500 нм из поликристаллического или аморфного кремния, на которую после термической обработки при 1000oС в атмосфере кислорода, содержащего аммиак или азот, наносят слой оксида/нитрида кремния толщиной 5 нм, который используется в качестве запирающего слоя 70. На фиг.12 показаны три таких подложки и два запирающих слоя. Минимальное количество подложек равно двум, а минимальное количество запирающих слоев 70 равно одному.

Затем, как показано на фиг.12, на подложке в процессе обычного теплового окисления при 1000oС формируют второй подзатворный изолятор 42 толщиной 10 нм, а на втором подзатворном изоляторе 42 также формируют первую словарную шину 51, выполненную в виде слоя поликристаллического кремния, легированного примесью вольфрама или молибдена, или слоя силицида.

Как показано на фиг.16, ЗУ имеет слой оксида/нитрида кремния толщиной 5 нм, который образован в процессе термической обработки при 1000oС в атмосфере кислорода, содержащего аммиак или азот, и используется как третий подзатворный изолятор 43. После этого всю поверхность полученной детали покрывают слоем проводящего поликристаллического кремния и подвергают анизотропному сухому травлению, в процессе которого на той ее части, в которой должна быть сформирована вторая словарная шина 52, оставляют слой фоторезиста, образующий в необходимом месте ЗУ вторую словарную шину 52. При этом на боковой стенке выступающей многослойной подложки 12, включающей запирающие подложки 11 и запирающие слои 70, даже если боковая стенка подложки 12 не покрыта фоторезистом, остается свободное место для второй словарной шины 52. Объясняется это тем, что при явно выраженном анизотропном сухом травлении в горизонтальном направлении травление не происходит. Поэтому образование имеющей равномерную толщину второй словарной шины 52 происходит автоматически с самоцентрированием вокруг содержащей запирающие слои многослойной подложки 12.

Затем легированием мышьяком или фосфором формируют показанную на фиг.11 и 12 область 24 стока и аналогичный первому промежуточному изолятору 61 второй промежуточный изолятор 62. Затем во втором промежуточном изоляторе 62 выполняют отверстие, которое заполняют алюминием или другим аналогичным материалом, образующим шину 23 передачи данных. Описанным выше способом можно изготовить предлагаемую в изобретении ячейку памяти, схема которой показана на фиг. 2. По сравнению с первым вариантом ячейки эта ячейка, в которой первая словарная шина 51 расположена рядом со второй словарной шиной 52, имеет большую площадь. Иначе говоря, у этой ячейки памяти при технологических размерах всех элементов, равных F, и точности совмещения элементов, равной 2/F, теоретическая площадь составляет величину, равную 13,5(= 3,0•4,5)F2.

На фиг. 17 показан еще один вариант возможного выполнения настоящего изобретения, в соответствии с которым ячейки памяти компонуются в матрицу, образуя матрицу памяти. В этом варианте для уменьшения общей площади ЗУ соседние шины считывания и управления смещены относительно одна другой.

На фиг. 18 показана временная диаграмма работы матрицы памяти, изображенной на фиг.17. Как показано на фиг.18, операция записи происходит при подаче импульсов на вторую словарную шину (WW1) и подаче необходимых характеризующих информацию напряжений на соответствующие шины передачи данных (D1, D2,...) множества элементарных ячеек памяти (МС11, МС12, МС13,...), которые соединены со второй словарной шиной. При этом все множество элементарных ячеек памяти одновременно записывают соответствующую информацию. Операция считывания выполняется с учетом того, что шины считывания (S1, S2, S3, S4,...) разделены смежными ячейками в направлении словарной шины, выборочным возбуждением чередующихся шин управления (C1, C2,...) сигналами адресации, что позволяет устранить взаимное влияние между ячейками. Например, в показанном на фиг.18 примере возбуждаются только нечетные шины управления. Часть информации, которая считывается из элементарных ячеек памяти М11, М12, М15, М16, поступает в шины считывания S1, S2, S3 и S4, при этом из ячеек МС13 и МС14 информация не считывается. Хотя на узел ЗУ каждой из элементарных ячеек памяти MC13 и МС14 и подается напряжение 1,8 В или 0,8 В, тем не менее считывающий транзистор каждой из ячеек находится в запертом состоянии, поскольку напряжение на шине управления С2 при этом равняется 2 В, напряжение на каждой шине S2 и S3 считывания равняется 2В-δ (около 200 мВ), а пороговое напряжение считывающего транзистора равняется 1,2 В.

Шины считывания можно также подводить и к смежным ячейкам памяти. В этом случае, хотя площадь ячейки памяти и увеличивается, появляется возможность упростить всю схему за счет того, что при этом отпадает необходимость для выборочного возбуждения декодировать шины управления сигналами адресации.

На фиг. 19, аналогичной фиг.10, на которой показано ЗУ, выполненное по второму варианту изобретения, в виде сверху показано ЗУ, выполненное по первому варианту изобретения. При таком выполнении ЗУ теоретическая площадь ячейки памяти становится равной 9,0(=3,0•3,0)F2, что намного меньше площади показанной на фиг.10 ячейки, выполненной по второму варианту изобретения.

На фиг. 20-23 показана последовательность операций по изготовлению ЗУ, выполненного по первому варианту изобретения. Сначала, как показано на фиг. 20, в кремниевой подложке с дырочной проводимостью, которая имеет удельное сопротивление приблизительно 10 Ом•см, обычным фототравлением и ионным легированием формируют обладающие электронной проводимостью области 21 и 22. Затем по технологии LOCOS с использованием слоя нитрида кремния, выборочно нанесенного на подложку во избежание ее окисления, выборочно наносят слой оксида кремния толщиной 500 нм, образующий область изолятора 60.

Как показано на фиг.21, затем на поверхность подложки 10 при 1000oС наносят слой оксида кремния толщиной 10 нм. Этот слой оксида кремния используется как первый подзатворный изолятор 41. На первый подзатворный изолятор 41 выборочно наносят слой поликристаллического кремния, который легирован обладающей электронной проводимостью примесью и который используется как узел 30 ЗУ. После этого ионным легированием формируют самосовмещенные с узлом 30 ЗУ выступающие участки обладающих электронной проводимостью областей 21 и 22, образующие так называемую СЛС-структуру (слаболегированный сток).

Как показано на фиг. 22, на поверхность узла 30 ЗУ при 1000oС наносят слой оксида кремния толщиной 10 нм, который используется как второй подзатворный изолятор 42. После этого всю поверхность полученной детали покрывают слоем проводящего поликристаллического кремния и подвергают анизотропному сухому травлению, в процессе которого на той ее части, в которой должна быть сформирована первая словарная шина 51, оставляют слой фоторезиста, позволяющий образовать в необходимом месте ЗУ первую словарную шину 51. При этом на боковой стенке узла 30 ЗУ, даже если она и не покрыта фоторезистом, остается свободное место для второй словарной шины 52. Объясняется это тем, что при явно выраженном анизотропном сухом травлении в горизонтальном направлении травление не происходит. Поэтому образование первой словарной шины 51 происходит автоматически с самосовмещением вокруг узла 30 ЗУ. Затем химическим осаждением из паровой фазы на полученную деталь наносят слой первого промежуточного изолятора 61 толщиной 500 нм, который полностью полируют методом ХМП (химико-механическая полировка) до полного удаления покрытия со всей верхней поверхности узла 30 ЗУ.

Затем, как показано на фиг.23, на узел 30 ЗУ наносят запирающую подложку 11 толщиной 500 нм из поликристаллического или аморфного кремния, на которую после термической обработки при 1000oС в атмосфере кислорода, содержащего аммиак или азот, наносят слой оксида/нитрида кремния толщиной 5 нм, который используется в качестве запирающего слоя 70. Затем в процессе термической обработки при 1000oС в атмосфере кислорода, содержащего аммиак или азот, формируют слой оксида/нитрида кремния толщиной 5 нм, который используется как третий подзатворный изолятор 43. После этого всю поверхность полученной детали покрывают слоем проводящего поликристаллического кремния и подвергают анизотропному сухому травлению, в процессе которого на той ее части, в которой должна быть сформирована вторая словарная шина 52, оставляют слой фоторезиста, позволяющий образовать в необходимом месте ЗУ вторую словарную шину 52. При этом на боковой стенке выступающей многослойной подложки 12, включающей подложки 11 и запирающие слои 70, даже если боковая стенка подложки 12 не покрыта фоторезистом, остается свободное место для второй словарной шины 52. Объясняется это тем, что в горизонтальном направлении при явно выраженном анизотропном сухом травлении травление не происходит. Поэтому образование имеющей равномерную толщину второй словарной шины 52 происходит автоматически с самосовмещением вокруг содержащей запирающие слои многослойной подложки 12.

Затем формируют показанные на фиг.1 область 24 стока, которая легирована мышьяком или фосфором, и аналогичный первому промежуточному изолятору 61 второй промежуточный изолятор 62. Затем во втором промежуточном изоляторе 62 выполняют отверстие, которое заполняют алюминием или другим аналогичным материалом, образующим шину 23 передачи данных. Изготовленная таким способом ячейка памяти показана на фиг.2. На фиг.1 показано сечение плоскостью А-А' по фиг. 19, а на фиг.24 показано сечение плоскостью В-В' по фиг.19. Теоретическая площадь ячейки памяти, выполненной по этому варианту изобретения, равна 9F2. Другими словами, в соответствии с этим вариантом изобретения можно изготовить самую маленькую из всех предлагаемых в изобретении ячеек памяти.

На фиг. 25 показано выполненное по третьему варианту изобретения ЗУ, в котором узел 30 ЗУ и подложка 12, содержащая подложки 11 и запирающие слои 70, выполнены одновременно по одной и той же технологии. В этом варианте изобретения ЗУ можно выполнить с меньшими по сравнению с другими вариантами размерами, поскольку при таком способе изготовления в отличие от первого варианта предлагаемого ЗУ отпадает необходимость выравнивания маски для совмещения узла 30 ЗУ с подложкой 12 при операции фототравления.

На фиг. 26-28 показаны некоторые из операций по изготовлению ЗУ, выполненного по третьему варианту изобретения. Как показано на фиг.26, после одновременного изготовления узла 30 ЗУ и подложки 12 с запирающими слоями на них в процессе термической обработки при 1000oС в атмосфере кислорода, содержащей аммиак и азот, наносят слой оксида/нитрида кремния толщиной 5 нм, который используется как второй подзатворный изолятор 42. Затем на всю поверхность полученной детали химическим осаждением из паровой фазы или другим аналогичным способом наносят слой проводящего поликристаллического кремния. После этого таким же способом наносят подлежащий травлению защитный слой из фоторезиста или полиамида, который после травления доводят до определенной толщины, получая необходимый подлежащий травлению защитный слой 63.

Используя защитный слой 63 как маску, осуществляют травление проводящего слоя поликристаллического кремния, формируя, как показано на фиг.23, первую словарную шину 51. После этого, выполняя операции, показанные на фиг.23, 24 и 1, получают структуру, показанную на фиг.21.

На фиг. 29 показана электрическая схема ЗУ, выполненного по четвертому варианту изобретения. В этом ЗУ, в отличие от ЗУ, схема которого показана на фиг.2 и в котором первая словарная шина 51 и вторая словарная шина 52 управляются независимо, первая словарная шина 51 и вторая словарная шина 52 объединены в одну первую словарную шину 51. Такое объединение первой и второй словарных шин 51 и 52 становится возможным за счет соответствующего выбора пороговых напряжений записывающего транзистора 1 и считывающего транзистора 2 и напряжения, приложенного к первой словарной шине 51.

На фиг.30 показана ячейка памяти, выполненная по четвертому варианту изобретения. Эта ячейка памяти имеет по сравнению с рассмотренными выше ячейками первого, второго и третьего вариантов более простую конструкцию, меньшие размеры и более проста в изготовлении.

На фиг.31 показана электрическая схема ЗУ, выполненного по пятому варианту изобретения.

На фиг. 32 показана электрическая схема матрицы памяти, выполненной по пятому варианту изобретения.

На фиг.33 показаны временные диаграммы работы ЗУ, выполненного по пятому варианту изобретения. ЗУ, выполненное по пятому варианту изобретения, отличается простотой изготовления из-за отсутствия в нем конденсатора и используемой для его запуска словарной шины. В этом ЗУ шина управления, используемая в предыдущих вариантах ЗУ, расположена параллельно словарной шине и используется как первая словарная шина. Рассмотрена работа этого ЗУ при изменении порогового напряжения считывающего транзистора до 0,5 В. При записи информация записывается как "1 В" или "0 В" в узле ЗУ. Операция считывания для каждой из ячеек памяти МС11 и МС12 выполняется при нулевом напряжении на первой словарной шине (RW1). При напряжении на узле ЗУ, равном 1 В, считывающий транзистор открывается, а при нулевом напряжении закрывается, что, как и в рассмотренных выше ЗУ, позволяет отличить информацию "1" от информации "0". Следует отметить, что считывающие транзисторы ячеек памяти МС21 и МС22, которые находятся в запертом состоянии, не оказывают отрицательного воздействия на операции считывания информации из ячеек памяти МС11 и MC12.

На фиг. 34 в виде сверху показана ячейка памяти, выполненная по пятому варианту изобретения, а на фиг.35 показано сечение плоскостью А-А' ячейки по фиг.34.

Описанные выше варианты изобретения относятся к ячейке памяти и матрице памяти, состоящей из таких ячеек. Однако реальное ЗУ содержит также ряд прямых периферийных схем, непосредственно соединенных с матрицей, таких как усилитель считываемого сигнала и декодер, и ряд косвенных периферийных схем, обеспечивающих функционирование устройств как запоминающего устройства, таких как логическая схема и схема ввода-вывода информации. Для того чтобы подавлять ток, имеющий величину ниже пороговой, длина затвора в матрице памяти обычно должна быть больше длины областей затвора в периферийной схеме, непосредственно соединенной с матрицей.

Говоря о прямых и косвенных периферийных схемах, используемых вместе с предлагаемыми в изобретении ЗУ, следует отметить, что при непосредственном использовании истока/стока транзистора, как показано, например, на фиг.14, для выполнения соединений диффузионным слоем требуется обязательное выравнивание маски, поскольку неточность при последующем формировании являющегося затвором транзистора узла 30 может привести к заметному ухудшению характеристик ЗУ. Поэтому, как показано на фиг.21, в предлагаемых ЗУ целесообразно использовать исток/сток (образованный на фиг.21 шиной управления 21 и шиной 22 считывания), выполненный самосовмещенным относительно узла 30 ЗУ.

Однако обычно эти шины выполняют отдельно от матрицы памяти, что расширяет возможности выбора различных вариантов для оптимального конструирования всей системы. Способ формирования этих шин основан на создании обычной самосовмещенной структуры с затвором из кремния или СЛС-структуры (слаболегированный сток) с пониженной концентрацией примеси около истока/стока. Следует подчеркнуть, что настоящее изобретение не ограничено ни одним из конкретных способов изготовления транзистора.

Как сказано выше, настоящее изобретение позволяет создать ЗУ, которое имеет характеристику обычного ЗУПВ и обладает свойствами энергонезависимого ЗУ. Иначе говоря, изобретение позволяет создать ЗУ, обеспечивающее выполнение операции хранения информации, аналогично обычному энергонезависимому ЗУ, в сочетании с усилением сигнала в ячейке памяти, аналогичным усилению, осуществляемому в обычном СЗУПВ. Другими словами, настоящее изобретение позволяет создать так называемое "энергонезависимое ЗУПВ", обладающее хорошей долговременной памятью в сочетании с устойчивой работой и быстродействием, характерными для ЗУПВ.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1999 |

|

RU2249262C2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, МНОЖЕСТВО ЗАПОМИНАЮЩИХ УСТРОЙСТВ И СПОСОБ ИЗГОТОВЛЕНИЯ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1997 |

|

RU2216821C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| Ячейка оперативной памяти | 2024 |

|

RU2826859C1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ С УПРАВЛЯЕМЫМ ПОТЕНЦИАЛОМ ПОДЗАТВОРНОЙ ОБЛАСТИ | 2011 |

|

RU2465659C1 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОНДЕНСАТОРАМИ, ОБРАЗОВАННЫМИ НАД И ПОД ТРАНЗИСТОРОМ ЯЧЕЙКИ ПАМЯТИ (ВАРИАНТЫ), И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 1995 |

|

RU2194338C2 |

| ЯЧЕЙКА ЭНЕРГОНЕЗАВИСИМОЙ ПАМЯТИ И СПОСОБ ЕЕ ПРОГРАММИРОВАНИЯ | 1996 |

|

RU2111556C1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ И СПОСОБ ЕЕ ПРОГРАММИРОВАНИЯ | 2009 |

|

RU2481653C2 |

| УСТРОЙСТВО ПАМЯТИ И СПОСОБ ИЗГОТОВЛЕНИЯ | 2001 |

|

RU2247441C2 |

| ЭЛЕМЕНТ ПАМЯТИ | 1992 |

|

RU2018994C1 |

Использование: в устройствах записи и хранения информации. Сущность изобретения: полупроводниковое запоминающее устройство (ЗУ) содержит узел ЗУ, образованный затвором транзистора, сформированного на полупроводниковой подложке, и многослойную структуру, которая состоит из полупроводниковых слоев и запирающих слоев в качестве изоляторов и которая сформирована на узле ЗУ, при этом запись информации в узел ЗУ или ее стирание из узла ЗУ осуществляются за счет инжекции зарядов в узел ЗУ через многослойную структуру, соответственно за счет удаления зарядов из узла ЗУ через многослойную структуру. Техническим результатом изобретения является создание полупроводникового ЗУ, обладающего хорошей долговременной памятью и одновременно работающего устойчиво и с высокой скоростью. 2 с. и 7 з.п. ф-лы, 35 ил.

| US 4669062 А, 26.05.1987 | |||

| Экономайзер | 0 |

|

SU94A1 |

| US 4630089 А, 16.12.1989 | |||

| US 5604357 A, 18.02.1997 | |||

| US 5194749 А, 16.03.1993 | |||

| Пюпитр для работы на пишущих машинах | 1922 |

|

SU86A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2018979C1 |

Авторы

Даты

2003-11-20—Публикация

1998-10-06—Подача