Изобретение относится к энергонезависимой памяти и к способу программирования энергозависимой памяти.

Самый труднопреодолимый недостаток энергонезависимых полупроводниковых запоминающих устройств (ЗУ) для среды хранения информации сверхбольшой емкости, таких как электрически стираемое программируемое постоянное запоминающее устройство (ЭСППЗУ) и флэш-ЭСППЗУ, заключается в высокой стоимости ЗУ из расчета на один бит. Для реакции этой проблемы в последнее время были проведены исследования ячейки памяти емкостью в несколько битов.

Плотность записи обычной энергозависимой памяти соотносится в отношении один к одному с числом ячеек памяти. Ячейка памяти в несколько битов хранит свыше двух битов в одной ячейке памяти, таким образом увеличивая плотность данных в одной и той же области кристалла, не уменьшая при этом размера ячейки памяти.

Для ячейки памяти емкостью в несколько битов в соответствующих ячейках должно программироваться более трех пороговых уровней напряжения. Например, чтобы каждая ячейка хранила двухбитовые данные, соответствующие ячейки должны программироваться на 22 , т.е. на четырех пороговых уровнях. Здесь четыре пороговых уровня соответствуют логическим состояниям 00, 01, 10 и 11 соответственно.

В многоуровневой программе самая главная проблема в том, что соответствующие уровни порогового напряжения имеют статистическое распределение. Величина распределения около 0,5 V.

Поскольку распределение уменьшается за счет точного регулирования соответствующих пороговых уровней, можно программировать большее число уровней, что в свою очередь увеличивает число битов для каждой ячейки. Уменьшение распределения напряжения может быть осуществлено известным способом программирования, в котором используются повторяющиеся программирование и контроль.

Согласно этому способу последовательность импульсов напряжения прикладывается к ячейкам, чтобы запрограммировать ячейку энергозависимой памяти на соответствующих пороговых уровнях. Для контроля достижения ячейкой определенного порогового уровня выполняется считывание между соответствующими программируемыми импульсами напряжения.

Во время контроля, когда проверяемый пороговый уровень достигает намеченного порогового уровня, программирование останавливается. Этим способом повторяющегося программирования и контроля трудно уменьшить распределение погрешностей пороговых уровней, ввиду ограниченной длительности импульса напряжения программирования. Кроме этого, алгоритм повторяющегося программирования и контроля осуществляется при помощи дополнительной схемы, которая увеличивает область периферийных схем кристалла. Более того, повторяющийся метод удлиняет время программирования. Для устранения этого недостатка компанией "СанДиск Ко., Лтд" (автор Р. Сернеа) был предложен способ одновременного программирования и контроля.

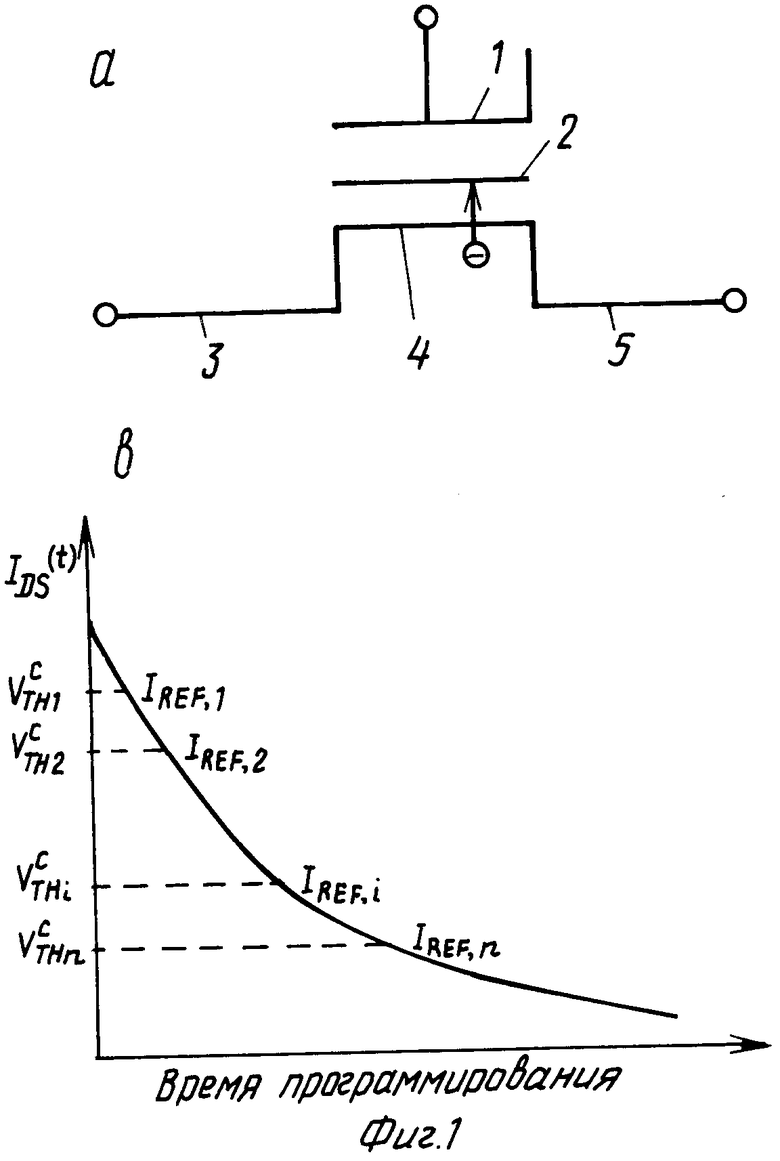

На фиг.1,a изображена условная схема энергонезависимой памяти, предложенной Р. Сернеа. Как показано на фиг.1,a ячейка энергонезависимой памяти состоит из управляющего затвора 1, плавающего затвора 2, истока 3, канальной области 4 и стока 5.

При приложении к управляющему затвору 1 и стоку 5 напряжения, достаточного для инициирования программирования, ток протекает между стоком 5 и истоком 3. Этот ток сравнивается с эталонным током и, когда достигает величины, равной или меньшей эталонного тока, генерируется сигнал завершения программирования.

Изложенный выше способ иллюстрируется с помощью фиг.1,b. Согласно этому известному способу контроль автоматически выполняется одновременно с программированием и это компенсирует недостатки способа с повторением, в котором программирование и контроль повторяются поочередно.

Однако в способе Сернеа не используется отдельная логическая схема программирования для осуществления программирования. Кроме того, в этом способе не используются средства, обеспечивающие разделение пути тока программирования и пути тока контроля. По этой причине в способе Сернеа трудно оптимизировать в отдельности программирование и контроль. Ток программирования и ток контроля не разделены и поэтому пороговые напряжения ячейки трудно непосредственно контролировать и регулировать. Обычно многоуровневое программирование выполняется таким образом, что напряжения, прикладываемые к соответствующим частям ячейки памяти, являются фиксированными, а величины эталонного тока, относящиеся к соответствующим уровням, изменяются. В этом способе, как показано на фиг.1,b, эталонные токи детектирования не имеют явной взаимосвязи с пороговыми напряжениями ячейки и не являются линейными по отношению к ним.

Структуру ячейки ЭСППЗУ или флэш-ЭСППЗУ можно разделить примерно на две части, в зависимости от места расположения плавающего затвора в канальной области. Первая структура является структурой простого многоуровневого затвора, в которой плавающий затвор полностью перекрывает канальную область ячейки. Вторая структура является структурой с расщепленным каналом, в которой плавающий затвор перекрывает только часть канальной области между истоком и стоком.

В канальной области та часть, в которой плавающий затвор не присутствует, называется передающим транзистором, который введен для исключения проблемы избыточного стирания. По своим размерам ячейка с расщепленным каналом более крупная, чем структура с простым многоуровневым затвором, что является нежелательным.

Еще один классификационный тип флэш-ЭСППЗУ определяется типом используемого затвора: двойного поликремниевого или тройного поликремниевого. Двойной поликремниевый затвор обычно используется в простой многоуровневой структуре. Тройной поликремниевый затвор используется в ячейке с расщепленным каналом. Ячейки ЭСППЗУ или флэш-ЭСППЗУ подробно раскрыты в патенте США N 5268318. Обычно третий затвор в тройном поликремниевом затворе является стирающим и используется только для стирания данных. В флэш-ЭСППЗУ стирание выполняется в группах блоков, составленных из множества ячеек.

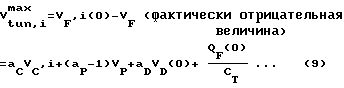

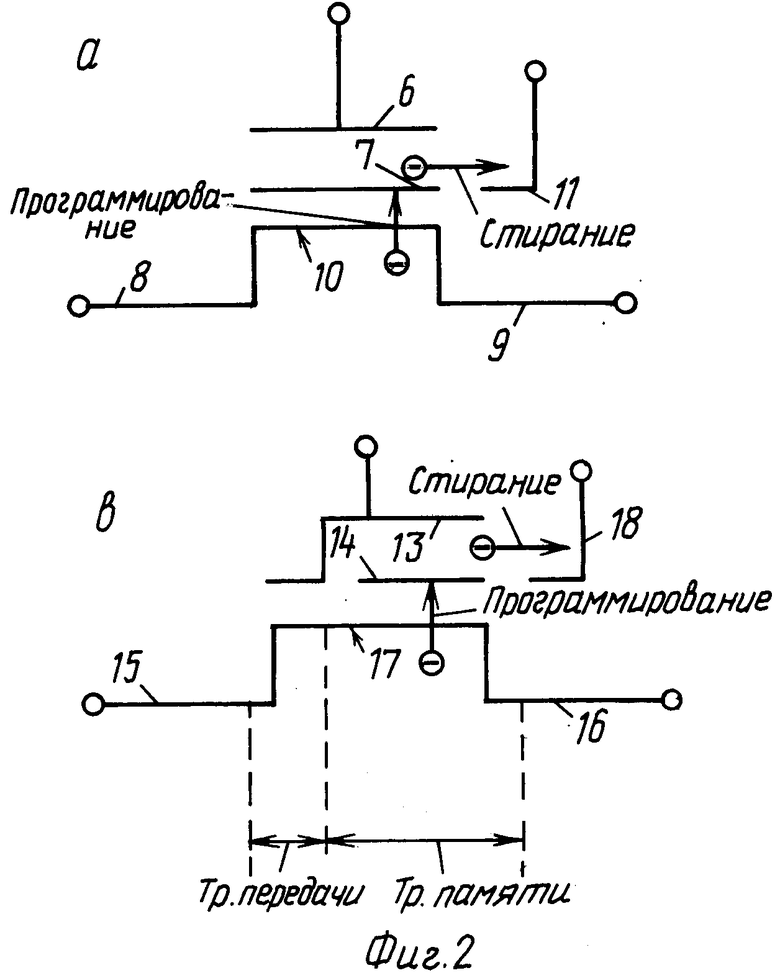

На фиг. 2, a представлена схема обычной ячейки энергозависимой памяти с простым многоуровневым затвором; на фиг.2,b - схема обычной ячейки энергозависимой памяти, имеющей структуру с расщепленным каналом. Фиг.2a и b иллюстрируют процедуры программирования и стирания и также структуру обычных ячеек энергозависимой памяти.

Как показано на фиг.2,a, обычно ячейка памяти с многоуровневым затвором включает управляющий затвор 6, плавающий затвор 7, исток 8, сток 9, канальную область 10 и стирающий затвор 11. Как показано на фиг.2,b, обычная ячейка с расщепленным каналом включает управляющий затвор 13, плавающий затвор 14, исток 15, сток 16, канальную область 17 и стирающий затвор 18.

На фиг.2, a и b стирающие затворы 11 и 18 для программирования не нужны. Поэтому при программировании обычные ячейки фиг.2, a и b имеют по сути ту же структуру, что и двойной поликремниевый затвор.

В известном уровне техники программирование выполняется только посредством управляющего затвора, электродов истока и/или стока, поэтому трудно разделить путь тока программирования от пути тока контроля в ячейке памяти для одновременного программирования и контроля. Соответственно, трудно непосредственно и эффективно контролировать несколько уровней.

Изобретение создано с учетом изложенных выше обстоятельств и имеет своей целью создание энергонезависимой памяти и способа программирования энергонезависимой памяти, при котором контроль осуществляется одновременно с многоуровневым программированием, причем области программирования и контроля полностью разделены.

Другой целью изобретения является создание энергонезависимой памяти и способа программирования энергонезависимой памяти, при котором при многоуровневом программировании соответствующие пороговые уровни контролируются напряжением, прилагаемым к управляющему затвору, причем соответствующие пороговые уровни и напряжения, соответственно прикладываемые к управляющему затвору, линейны относительно друг друга.

Еще одной целью изобретения является создание энергонезависимой памяти и способа программирования энергонезависимой памяти, в котором проблема излишнего стирания устранена простой многоуровневой структурой, в которой нет передающего транзистора и область ячейки уменьшена в целях компактности.

Дополнительные цели и преимущества изобретения будут изложены частично в нижеследующем описании и частично будут очевидны из описания, либо могут быть выявлены в практическом применении изобретения. Цели и преимущества изобретения могут быть реализованы и достигнуты средствами и комбинациями, конкретно перечисленными в прилагаемой формуле изобретения.

Для достижения целей изобретения и в соответствии с данным изобретением ячейка энергонезависимой памяти в данном изобретении состоит из плавающего затвора; области программирования, имеющей первый путь тока к плавающему затвору, для программирования посредством подачи носителей заряда в плавающий затвор через первый путь тока или путем извлечения носителей заряда, накопленных в плавающем затворе; и области контроля, имеющей второй путь тока, отделенный от первого пути тока, для контролирования количества зарядов плавающего затвора при помощи второго пути тока при программировании.

Кроме того, для достижения целей данного изобретения предусматривается ячейка энергонезависимой памяти, состоящая из плавающего затвора; затвора программирования для подачи носителей заряда в плавающий затвор в целях программирования; управляющего затвора для контролирования количества носителей, подаваемых в плавающий затвор для программирования; полевого транзистора, включающего плавающий затвор, исток, сток и канальную область между истоком и стоком и контролирующего носители заряда, подаваемые в плавающий затвор во время программирования.

Помимо этого, для достижения целей изобретения для ячейки энергонезависимой памяти, состоящей из управляющего затвора, плавающего затвора, затвора программирования и транзистора, имеющего пороговое напряжение и включающего плавающий затвор, исток, сток и канальную область между стоком и истоком, предлагается способ программирования ячейки энергонезависимой памяти, который состоит из следующих этапов: подача первого напряжения на управляющий затвор и второго напряжения на затвор программирования, чтобы носители заряда для программирования подавались в плавающий затвор с затвора программирования и инверсионный слой формировался в канальной области; контролирование удельной электропроводности инверсионного слоя при программировании и остановка подачи по меньшей мере одного из напряжений - первого и второго - на управляющий затвор и на затвор программирования, когда контролируемая удельная электропроводность достигает эталонной величины.

Также для достижения целей изобретения предусматривается ячейка энергонезависимой памяти, состоящая из плавающего затвора, разделенного на первую и вторую области; программирующего полевого транзистора, включающего первую область, относящуюся к части плавающего затвора, первый сток и общий исток, канальную область между первым стоком и общим истоком, и имеющего первое пороговое напряжение для подачи носителей заряда в плавающий затвор в целях программирования; управляющего затвора для контролирования количества носителей заряда, подаваемых в плавающий затвор для программирования; и контролирующего полевого транзистора, включающего вторую область плавающего затвора, исключая первую область, второй сток и общий исток, канальную область между вторым стоком и общим истоком, и имеющего второе пороговое напряжение для контроля количества носителей заряда, подаваемых в плавающий затвор при программировании.

Кроме того, для достижения целей изобретения для ячейки энергонезависимой памяти, состоящей из управляющего затвора, плавающего затвора, разделенного на первую и вторую область, предусматривается программирующий полевой транзистор, включающий первую область плавающего затвора, первый сток, общий исток и первую канальную область между первым стоком и общим стоком, и имеющий первое пороговое напряжение; и контролирующий полевой транзистор, включающий вторую область плавающего затвора, второй сток и общий исток, вторую канальную область между вторым стоком и общим стоком, и имеющий второе пороговое напряжение; предлагается способ программирования ячейки энергонезависимой памяти, состоящей из следующих этапов: подача первого напряжения в управляющий затвор и второго напряжения на первый сток, чтобы носители заряда для программирования поступали в плавающий затвор через первую канальную область для программирования и формирования инверсионного слоя во второй канальной области; и контролирование удельной электропроводности инверсионного слоя при программировании и остановка подачи по меньшей мере одного из напряжений - первого и второго - на управляющий затвор и первый сток, когда контролируемая удельная электропроводность достигает эталонной величины.

Прилагаемые чертежи иллюстрируют осуществление изобретения и вместе с описанием служат для объяснения целей, преимуществ и принципов изобретения.

На фиг. 1, a показана принципиальная схема обычной ячейки энергонезависимой памяти;

на фиг. 1, b - график, объясняющий принцип автоматического контроля/программирования обычной энергонезависимой памяти фиг. 1, a;

на фиг. 2, a - принципиальная схема обычной энергонезависимой памяти с простым многоуровневым затвором;

на фиг. 2,b - принципиальная схема обычной энергонезависимой памяти со структурой с расщепленным каналом;

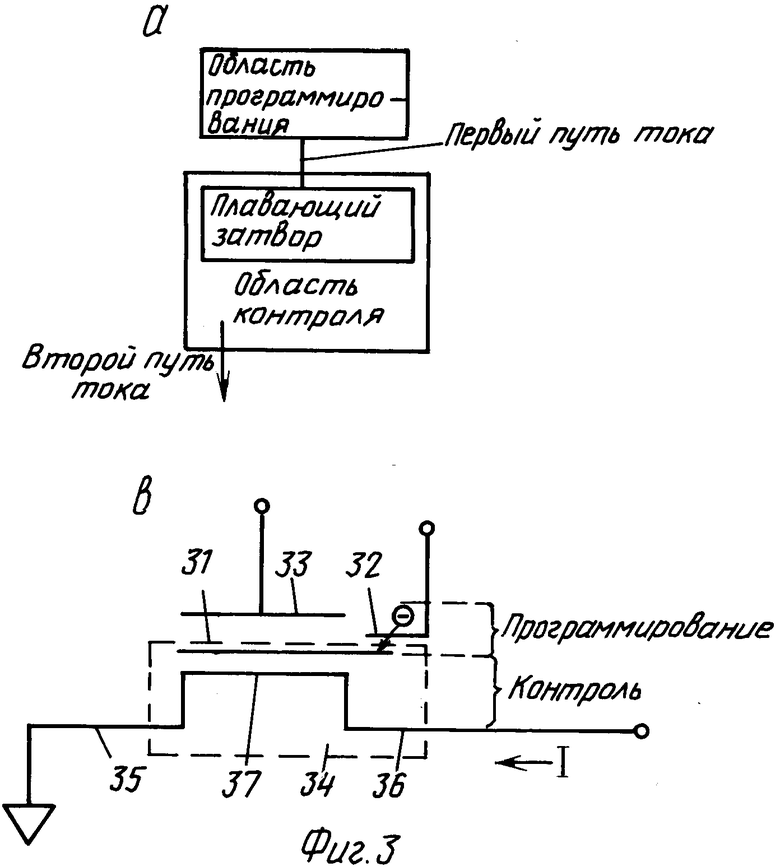

на фиг. 3,a - блок-схема ячейки энергонезависимой памяти согласно данному изобретению;

на фиг. 3,b - принципиальная схема первого осуществления энергонезависимой памяти согласно данному изобретению;

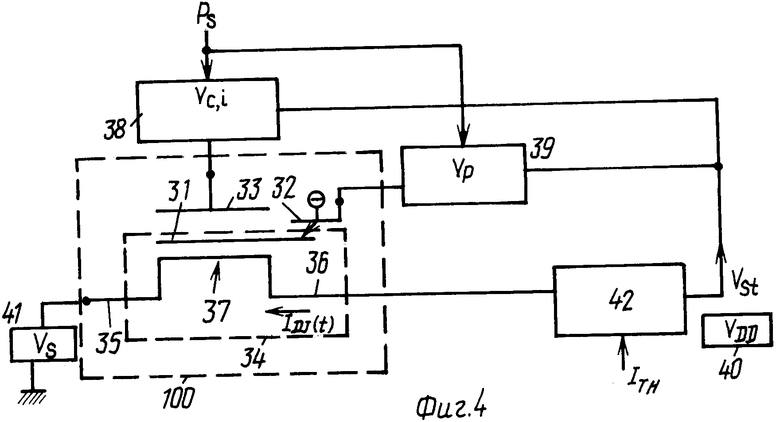

на фиг. 4 - схема, поясняющая способ программирования, использующий обнаружение тока в соответствии с первым вариантом осуществления изобретения;

на фиг. 5,a-i - временные диаграммы сигналов, присутствующих в соответствующих точках схемы по фиг. 4;

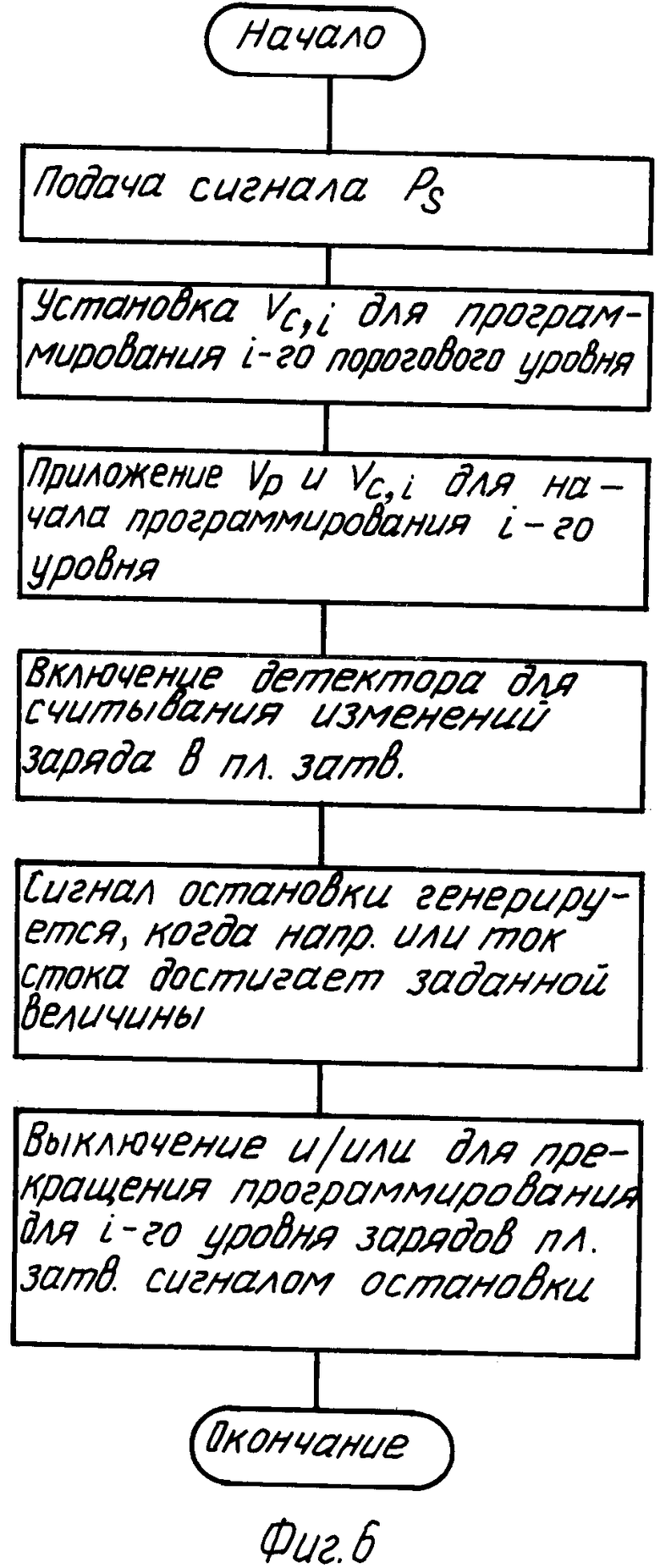

на фиг. 6 - блок-схема многоуровневого программирования в соответствии с первым вариантом осуществления изобретения;

на фиг. 7,a - эквивалентная принципиальная схема емкостей энергонезависимой памяти фиг. 3, b;

на фиг. 7, b - график, изображающий взаимосвязь между программируемыми пороговыми уровнями и соответственно приложенными к управляющему затвору напряжения;

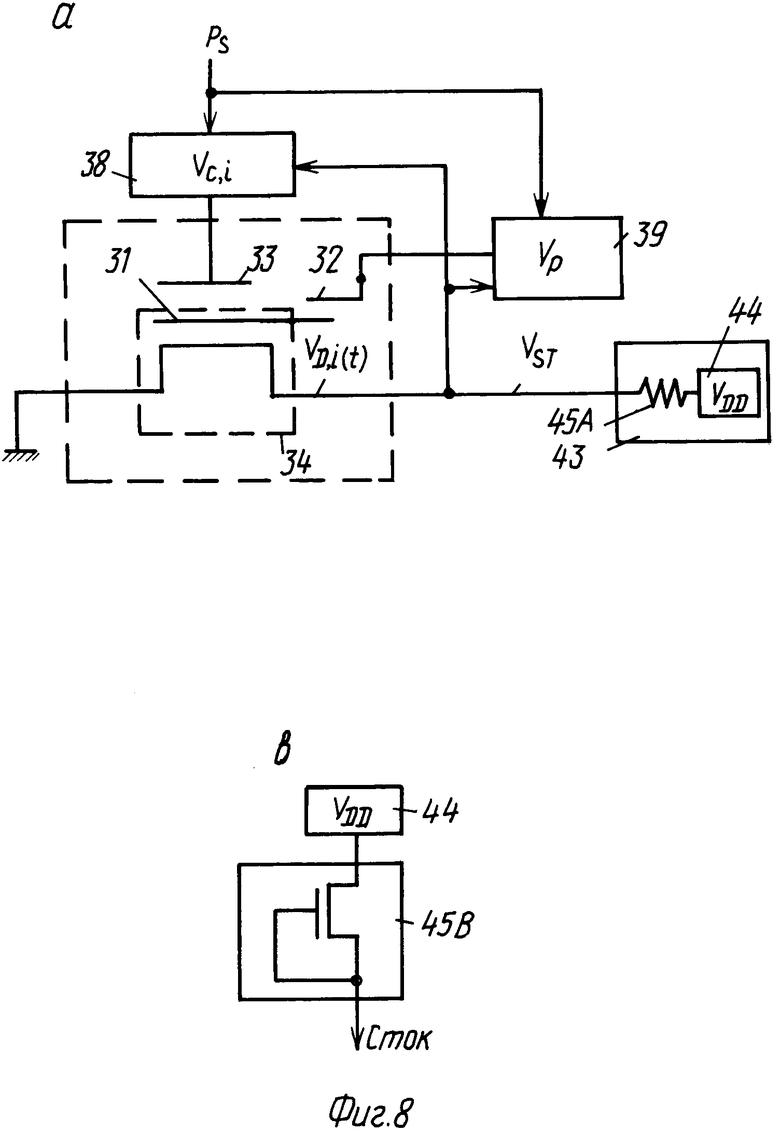

на фиг. 8,a - схема, поясняющая порядок программирования в соответствии с данным изобретением с использованием детектирования напряжения согласно первому варианту осуществления данного изобретения;

на фиг. 8,b - принципиальная схема другого варианта осуществления части схемы детектирования напряжения по фиг. 8,a;

на фиг. 9,a - первая структура энергонезависимой памяти в соответствии с первым вариантом осуществления изобретения;

на фиг. 9, b - поперечное сечение первой структуры энергонезависимой памяти по линии A-A на фиг. 9,a;

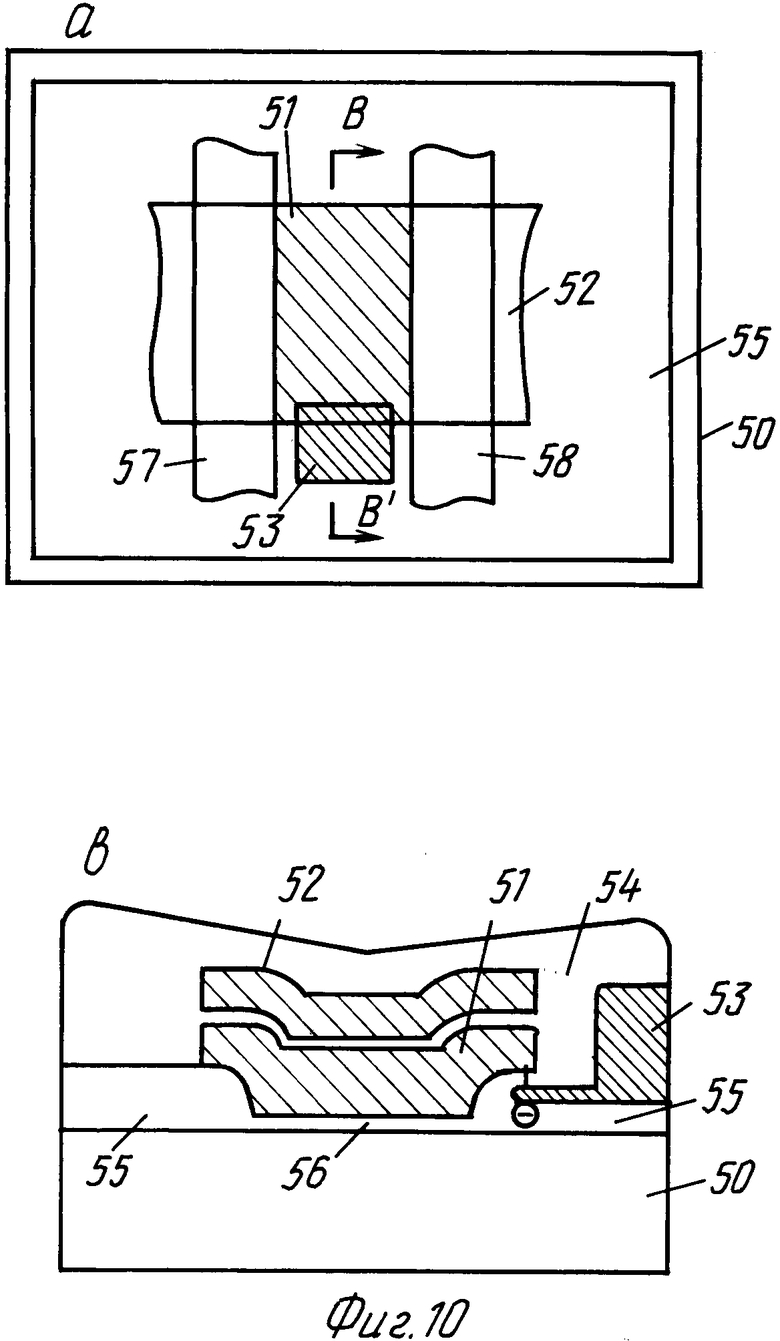

на фиг. 10,a - вторая структура энергонезависимой памяти в соответствии с первым вариантом осуществления изобретения;

на фиг. 10, b - поперечное сечение второй структуры энергонезависимой памяти по линии B-B на фиг. 10,a;

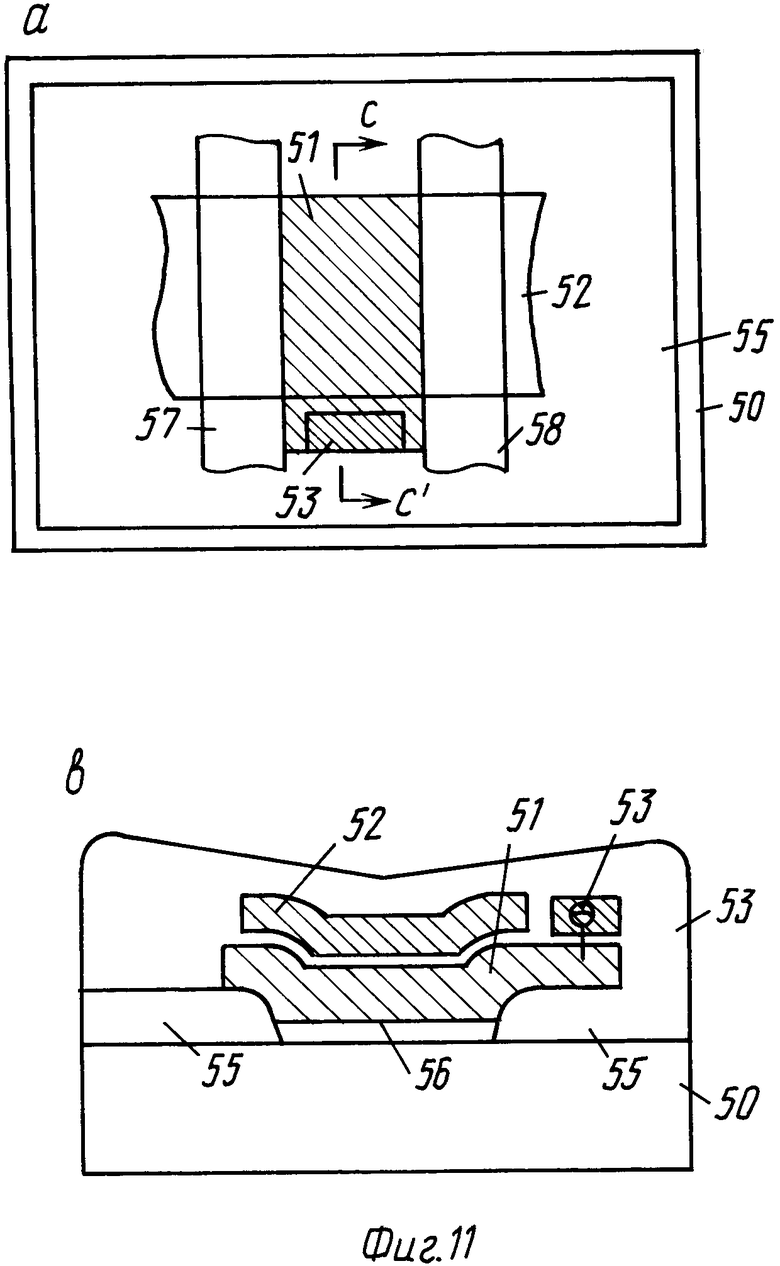

на фиг. 11,a - третья структура энергонезависимой памяти в соответствии с первым вариантом осуществления изобретения;

на фиг. 11, b - поперечное сечение третьей структуры энергонезависимой памяти по линии C-C' на фиг. 11,a;

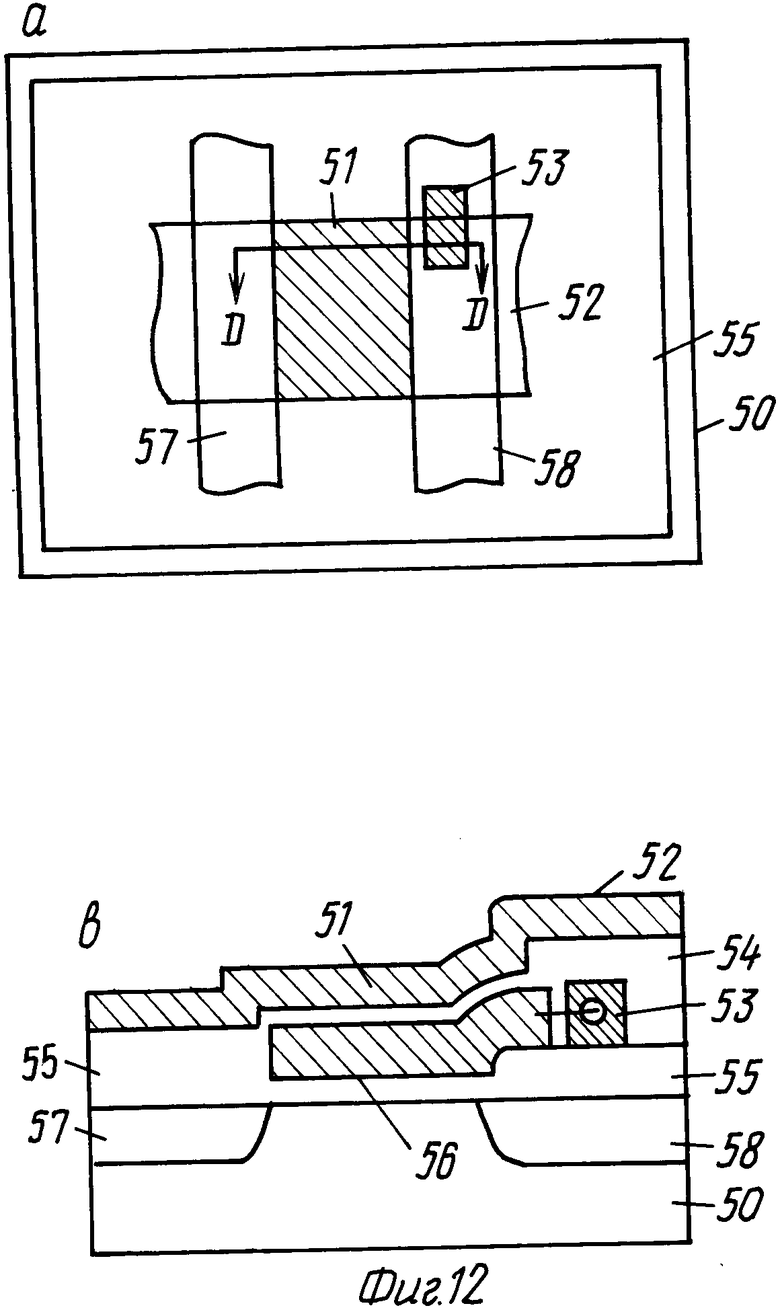

на фиг. 12,a - четвертая структура энергонезависимой памяти в соответствии с первым вариантом осуществления изобретения;

на фиг. 12,b - поперечное сечение четвертой структуры энергонезависимой памяти по линии D-D' на фиг. 12,a;

на фиг. 13, a - принципиальная схема энергонезависимого запоминающего устройства, использующего ячейку энергонезависимой памяти по фиг. 3,b;

на фиг. 13,b - таблица напряжений, подаваемых в соответствующие шины по фиг. 13,a во время работы;

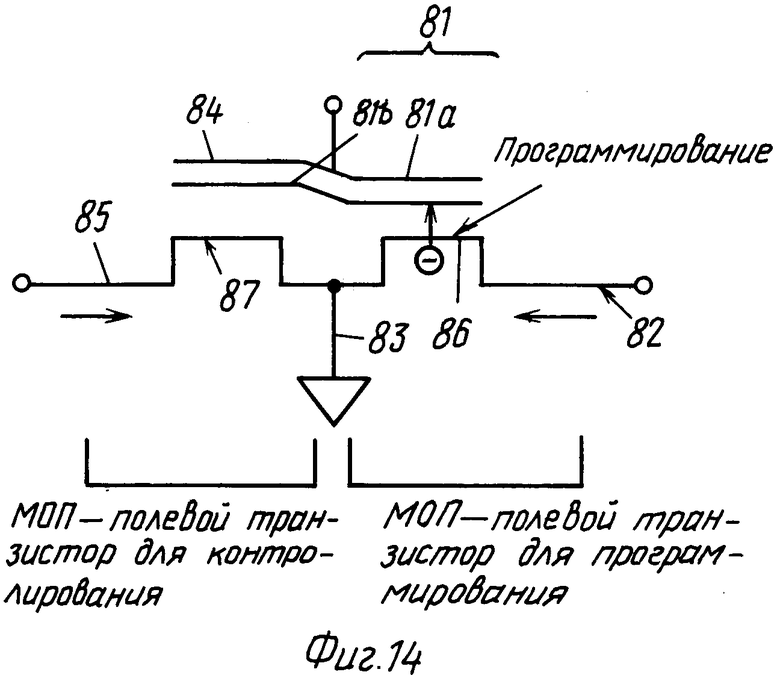

на фиг. 14 - принципиальная схема второго варианта осуществления энергонезависимой памяти согласно изобретению;

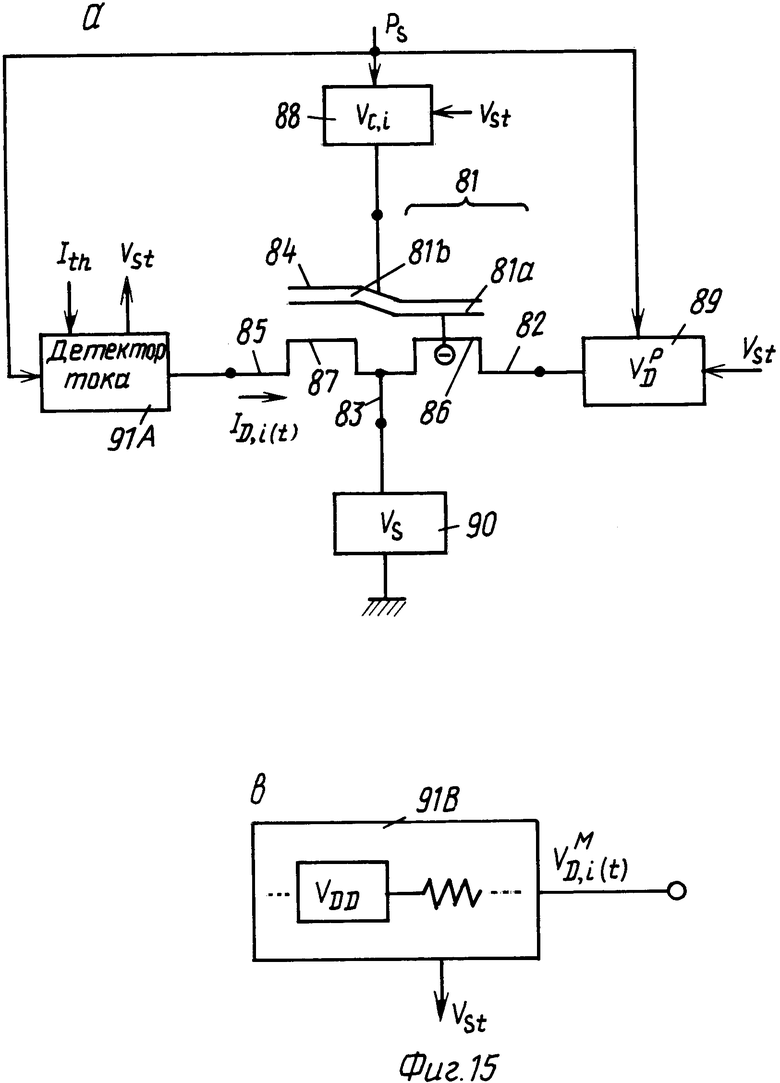

на фиг. 15,a - схема, объясняющая способ программирования в соответствии с вторым вариантом осуществления изобретения;

на фиг. 15,b - схема детектора напряжения, используемого вместо детектора тока фиг. 15,a;

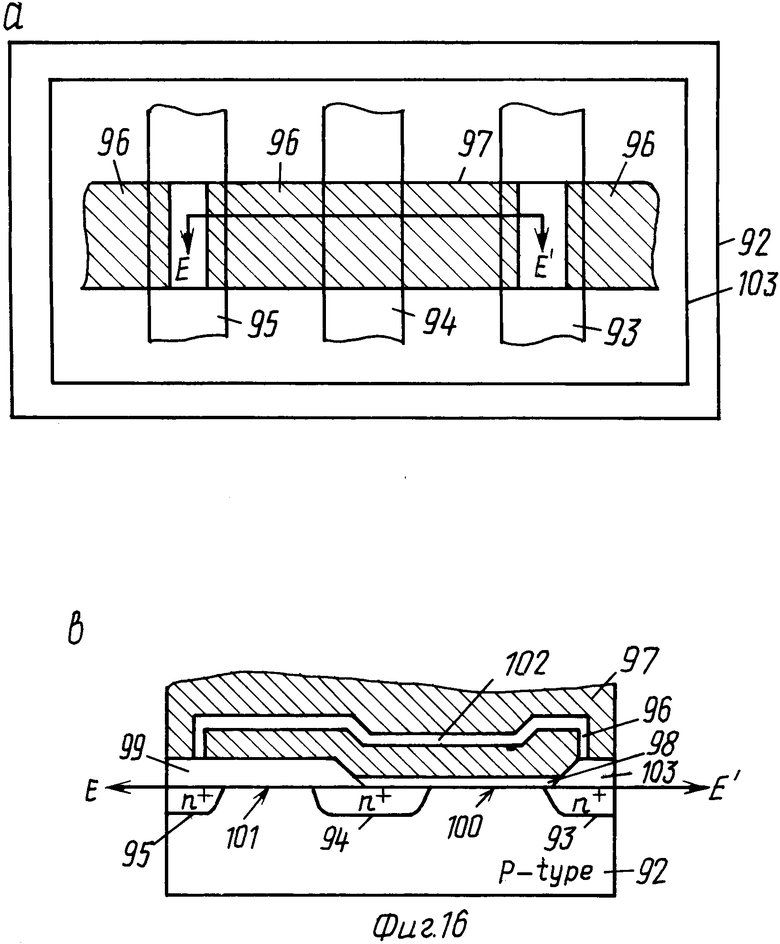

на фиг. 16, a - структура энергонезависимой памяти в соответствии с вторым вариантом осуществления изобретения;

на фиг. 16,b - поперечное сечение структуры энергонезависимой памяти по линии E-E фиг. 16;

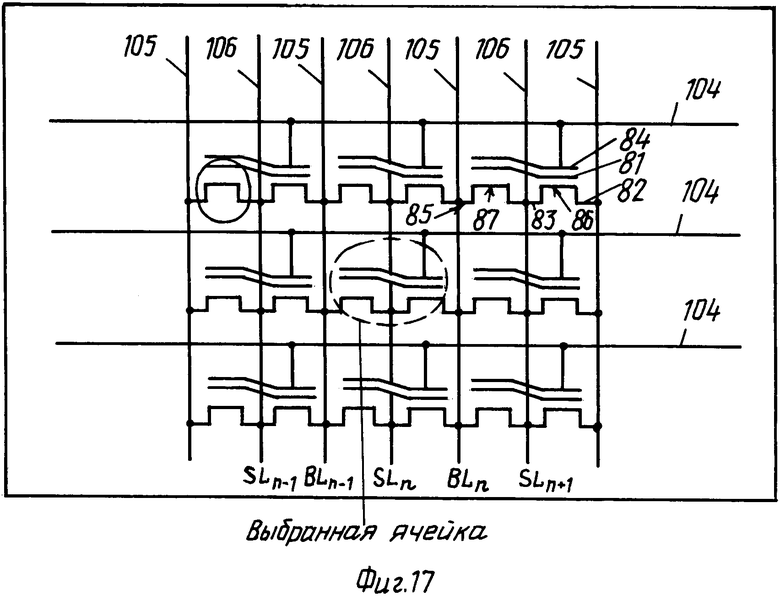

на фиг. 17 - принципиальная схема энергонезависимого запоминающего устройства, использующего ячейку энергонезависимой памяти по фиг. 14;

на фиг. 18 - таблица напряжений, подаваемых в соответствующие линии по фиг. 17 во время работы.

Первый вариант

Как показано на фиг. 3,a, ячейка энергонезависимой памяти состоит из плавающего затвора, области программирования, имеющей первый путь тока к плавающему затвору, для программирования подачей носителей заряда в плавающий затвор через первый путь тока, либо извлечением носителей зарядов, накопленных в плавающем затворе, и области контроля, имеющей второй путь тока, отделенный от первого пути тока для контроля величины заряда плавающего затвора при помощи второго пути тока при программировании.

Как показано на фиг. 3,b, ячейка энергонезависимой памяти состоит из плавающего затвора 31, затвора программирования 32 для подачи отрицательных зарядов (электронов) или положительных зарядов (дырок) в плавающий затвор 31 для многоуровневого программирования, управляющего затвора 33 для подачи напряжения в плавающий затвор 31 емкостной связью между управляющим затвором и плавающим затвором и для контролирования количества зарядов, поступающих в плавающий затвор 31 от затвора программирования 32 для программирования, и транзистора 34 для контроля (или опознания) зарядов, поступающих в плавающий затвор 31 во время многоуровневого программирования. На фиг. 3,b, транзистор 34 включает плавающий затвор 31, исток 35, сток 36 и канальную область 37 между истоком 35 и стоком 36.

Как показано на фиг. 3,b, энергонезависимая память в соответствии с данным изобретением сконструирована для осуществления многоуровневого программирования с использованием третьего затвора программирования 32 и для контроля завершения программирования путем проверки количества зарядов, подаваемых в плавающий затвор 31 при многоуровневом программировании.

Управляющий затвор 33, плавающий затвор 31, затвор программирования 32 могут выполнять только многоуровневое программирование. Наоборот, транзистор 34 может выполнять только контролирование количества зарядов плавающего затвора 31 для контроля завершения или продолжения программирования. Область программирования отделена полностью от области контроля. Эти две области соединены через плавающий затвор 31. Плавающий затвор 31 и затвор программирования 32, относящиеся к области программирования, могут рассматриваться как компоненты, образующие туннельный диод. Программирование осуществляется в соответствии с механизмом туннелирования посредством туннельного диода.

Как указано выше, в известном уровне техники не известно использование затвора программирования 32 и как программирование, так и контроль выполняются при помощи стока 36 и канальной области 37 транзистора 34. В этом отношении данное изобретение отличается от существующего уровня техники.

Далее описывается способ многоуровневого программирования с использованием энергонезависимой памяти фиг. 3, a и b. Способ программирования в данном изобретении включает детектирование напряжения и детектирование тока.

Сначала будет объяснено детектирование тока. На фиг. 4 показаны первый источник напряжения 38, второй источник напряжения 39, третий источник напряжения 40, четвертый источник напряжения 41, детектор тока 42 и энергонезависимую память 100, аналогичную изображенной на фиг. 3. Символ PS относится к сигналу начала программирования, поступающему от внешних устройств. Символ VST обозначает сигнал остановки программирования.

Первый источник напряжения 38 подает напряжение VC,i (i=0, 1, 2,...,n-1) в управляющий затвор 33 энергонезависимой памяти 100 в целях программирования i-го порогового уровня при многоуровневом программировании. Напряжение VC,i имеет величины, которые изменяются вместе с соответствующими уровнями программирования.

Второй источник напряжения 39 подает напряжение VP на затвор программирования 32 для многоуровневого программирования. Напряжение VP всегда имеет фиксированную отрицательную величину.

Третий источник напряжения 40 наводит напряжение VD на сток 36 для контролирования состояния программирования, т.е. ток стока ID,i(t), при многоуровневом программировании. Четвертый источник напряжения 41 подает напряжение VS в исток 35. Например, напряжение VS может быть напряжением земли. ID,i(t) обозначает ток, протекающий по стоку 36 в момент (t).

Детектор тока 42 имеет величину порогового тока Ith и генерирует сигнал VST остановки программирования, когда ток ID,i(t), протекающий через сток 36, достигает порогового тока Ith при программировании i-го порогового уровня. Другими словами, сигнал VST остановки программирования генерируется, когда ID,t(t)≤Ith (при t=tP,i). Время tP,i относится ко времени, когда программирование i-го порога завершено. Здесь i-й пороговый ток детектора тока 42 может быть определен величиной, близкой пороговой области транзистора, которая может быть больше нуля или равна нулю.

Произвольный эталонный ток IRBF, превышающий пороговый ток, может также использоваться для данного изобретения, причем результат будет тот же. Однако, если эталонный ток IREF имеет большую величину, то большую величину должно иметь также и первоначальное напряжение на плавающем затворе 31 VF,i(O), чтобы удовлетворять неравенству ID,i(O) > IREF на первоначальном этапе многоуровневого программирования. Кроме этого, для повышения первоначального напряжения VF,i(O) должно быть также увеличено напряжение VC,i.

Ток ID,i(t) указывает величину тока стока 36, обусловленного напряжением VF,i(t) на плавающем затворе 31 при программировании i-го уровня. Величина тока наибольшая на начальной стадии программирования и уменьшается в ходе программирования. Когда уменьшенная величина достигает величины i-го порогового тока детектора тока 42, детектор тока генерирует сигнал VST остановки программирования.

В соответствии с изложенным выше условием многоуровневое программирование с использованием обнаружения тока стока будет описываться со ссылкой на фиг. 4, 5, a-i и 6. Фиг.5, a-i изображает временные диаграммы сигналов в соответствующих точках фиг. 4. На фиг. 6 представлена блок-схема алгоритма, иллюстрирующая двухуровневое или многоуровневое программирование, согласно данному изобретению.

Предположим, что соответствующая ячейка находится в состоянии стирания. Здесь состояние стирания означает нулевой уровень, т.е. низший. Данный вариант осуществления излагается исходя из того предположения, что полевой транзистор плавающего затвора имеет канал n-типа, образованный на подложке p-типа. Разумеется, может применяться полевой транзистор плавающего затвора, в котором используется канал p-типа на подложке n-типа. В данном случае, если прилагаемые напряжения установлены с противоположными полярностями и знаки соответствующих напряжений и пороговых напряжений поменялись на обратные значения, то могут выполняться те же действия, что в предыдущем случае.

Во-первых, когда внешний сигнал PS начала программирования, как показано на фиг. 5, a, подается для начала осуществления многоуровневого программирования, положительное напряжение VC,i устанавливается для программирования i-го уровня.

Когда подается сигнал PS начала программирования, фиг. 5, a, положительное напряжение VC,i фиг. 5, b и отрицательное напряжение Vp фиг. 5, c подаются на управляющий затвор 33 и затвор программирования 32 соответственно от первого и второго источников напряжения 38 и 39. Затем туннелирующее напряжение Vtun,i (t) фиг. 5, g подается между затвором программирования 32 и плавающим затвором 31, в результате чего заряды для программирования i-го порогового уровня подаются в плавающий затвор 31 от затвора программирования 32. После приложения VC,i и Vp детектор тока 42 включается для контроля изменения заряда в плавающем затворе 31.

Как показано на фиг. 5, d, напряжение VF,i(t) для программирования i-го порогового уровня прилагается к плавающему затвору 31, и в канальной области 37 полевого транзистора 34 формируется инверсионный слой. Поскольку исток 35, сток 36 и канальная область 37 расположены в полупроводниковой подложке, то при формировании инверсионного слоя токи перетекают от стока 36 в исток 35 через канальную область 37. Напряжения подаются от третьего и четвертого источника напряжения 40 и 41, в результате чего напряжение стока VD и напряжение истока VS индуцируются в сток 36 и исток 35 соответственно. Здесь ток ID,i(t) протекает через сток 36. Как показано на фиг. 5, e, ток ID,i(t) на начальной стадии имеет наибольшую величину и снижается в процессе программирования, потому что электроны инжектируются в плавающий затвор, чтобы понизить напряжение плавающего затвора.

Во время программирования i-го порогового уровня детектор тока 42 контролирует ток стока ID,i(t). Когда эта величина достигает величины i-го порогового тока, как изображено на фиг. 5,e, программирование i-го порогового уровня завершается и выдается сигнал VST остановки программирования (фиг. 5, f). Выше объяснялось, что детектор тока 42 контролирует ток ID,i(t) на стоке 36. Однако можно также сказать, что детектор тока 42 контролирует изменение величины напряжения и заряда на плавающем затворе 31 во время программирования (фиг. 5,d). Контролирование тока ID,i(t) может рассматриваться как контролирование удельной электропроводности инверсионного слоя, образованного в канальной области 37.

На фиг. 4 сигнал VST остановки программирования прикладывается к первому и второму источникам напряжения 38 и 39. Первый и/или второй источники напряжения 38 и 39 останавливают подачу положительного напряжения VST и отрицательного напряжения VP на управляющий затвор 33 и затвор программирования 32 в ответ на сигнал VST остановки программирования, как показано на фиг. 5,b и c. Когда обнаруживается, что ток ID,i(t) стал ниже порогового тока Ith в тот момент, когда t = tP,i, программирование i-го порогового уровня завершается. Время tP,i показывает, когда программируется i-й пороговый уровень. I-й пороговый ток заранее устанавливается как величина, в основном соответствующая пороговому напряжению V

Другими словами, на фиг. 3 по той причине, что полевой транзистор 34 формируется с плавающим затвором 31, истоком 35 и стоком 36, пороговое напряжение V

Фиг. 5, i - график, изображающий величину изменения заряда в плавающем затворе 31 с начальной величины заряда QF,0(0) до величины QF,1(tp,1), когда завершено программирование первого порогового уровня, и до величины QF,2(tp,2), когда завершено программирование второго порогового уровня, в том случае, когда i-е пороговые уровни соответствуют первому и второму уровням. На фиг.5, i следует отметить, что, когда напряжения VF,1 (t) и VF,2(t) на плавающем затворе 31 достигают порогового напряжения V

Со ссылками на фиг. 7,a поясняется взаимосвязь между напряжением Vc,i, прилагаемым к управляющему затвору 32 от первого источника напряжения 38, и пороговым напряжением на соответствующем уровне, которая является значительным результатом данного изобретения. На фиг. 7,a обозначение Cc представляет емкость между управляющим затвором 33 и плавающим затвором 31; Cp представляет емкость между затвором программирования 32 и плавающим затвором 31, CD представляет емкость между стоком 36 и плавающим затвором 31, а Cs представляет емкость между истоком 35 (включая подложку) и плавающим затвором 31.

Сумма CT этих емкостей может быть выражена следующим уравнением (1):

CT = Cc + CP + CD + Cs.... (1)

Коэффициенты связи соответствующих емкостей определяют следующими уравнениями (2):

aC = Cc/CT, aP = CP/CT, и aD = CD/CT... (2)

На фиг. 7, a напряжение на плавающем затворе 31 при программировании может быть выражено следующим уравнением (3):

где

QF(t) обозначает величину заряда в плавающем затворе 31. В уравнении (3) предполагается, что исток и подложка заземлены.

При программировании пороговое напряжение V

Другими словами, уравнение (4) V

Пороговое напряжение V

Пороговое напряжение V

Как указано выше, программирование на соответствующих уровнях останавливается, когда напряжение VF(t) на плавающем затворе 31 понижается до тех пор, пока не будет достигнута величина порогового напряжения V

VF(tP)=V

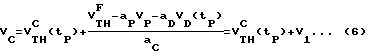

Преобразование уравнения (5) относительно напряжения VC, прикладываемого к управляющему затвору 33 от первого источника напряжения 38, дает следующее уравнение (6):

где

V1 определяется по следующей формуле:

Здесь важно, что величина V1 при моменте t = tP обнаружения является постоянной относительно напряжения VC,i управляющего затвора на соответствующих уровнях.

Величина V1 определяется напряжением стока VD(tp), когда t = tp, напряжением Vp, прилагаемым к затвору программирования 32, и такими параметрами как V

С использованием уравнения (6) напряжение VC,i управляющего затвора 33, требуемое для программирования i-го порогового уровня, может быть выражено следующим уравнением (7):

VC,i=V

где

i=0, 1, 2, 3, ... , n-1.

Из этого уравнения видно, что программируемые пороговые уровни и соответствующие приложенные напряжения управляющего затвора имеют линейную зависимость крутизной, равной 1. На фиг. 7,b показан этот результат. Подобным же образом, согласно уравнению (4), величина заряда плавающего затвора линейна относительно напряжений управляющего затвора.

Поскольку величина V1, как указано выше, постоянная, i-й сдвиг ΔVC,i напряжения, прикладываемого к управляющему затвору 33 при многоуровневом программировании, может быть выражено следующим уравнением (8):

ΔVC,i=ΔV

Согласно уравнениям (7) и (8), когда при многоуровневом программировании определяется сдвиг ΔV

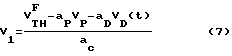

Как показано на фиг. 5, g при программировании соответствующего уровня напряжение туннелирования Vtun,i, прилагаемое между плавающим затвором 31 и затвором программирования 32 для туннелирования, имеет наибольшую величину в начале и наименьшую в тот момент, когда напряжение VF,i(t) достигает данного порогового напряжения V

Максимум V

В уравнении (9), если величина первоначального заряда QF(0) плавающего затвора 31 равна нулю, то уравнение (9) может быть переписано в виде следующего уравнения (10)

V

До сих пор излагалось описание многоуровневого программирования. Процесс стирания с помощью энергонезависимой памяти по фиг. 3 будет ниже.

Стирание выполняется путем приложения напряжений к соответствующим компонентам для создания между плавающим затвором и истоком, стоком или канальной областью, электрических полей достаточной силы, чтобы стереть носители заряда, накопленные в плавающем затворе. Тем самым носители заряда стираются на исток, сток или канальную область туннелированием. В данном изобретении стертое состояние означает низший пороговый уровень, то есть V

Во-первых, пороговые уровни всех ячеек выбранного блока стираются, чтобы они стали "ниже нуля", то есть V

Для того чтобы контролировать изменение заряда в плавающем затворе при программировании, напряжение VC,i должно быть приложено так, чтобы на начальном этапе программирования канал транзистора, показанного на фиг. 4, был инвертированным, чтобы уменьшить протекание тока стока и проводимость инверсионного слоя (при программировании). Для этой цели должно удовлетворяться следующее уравнение (11):

VF,i(0) > V

Значения VC,i и VP должны определяться так, чтобы туннельное электрическое поле, образованное между затвором программирования 32 и плавающим затвором 31 для создания туннелирования между ними, было достаточно сильным для осуществления программирования.

Значение VP является фиксированным отрицательным значением, так что напряженность туннельного электрического поля увеличивается, когда значение VC,i становится высоким. Скорость программирования также увеличивается по мере увеличения сдвига ΔV

Итак выше был изложен способ программирования на основе детектирования тока.

Далее со ссылкой на фиг. 8 будет объяснен способ программирования на основе детектирования напряжения. Способ программирования на основе детектирования напряжения в основном тот же, что и в программировании на основе детектирования тока.

Схема по фиг. 8 поясняет программирование в данном изобретении с использованием детектирования напряжения. Фиг. 8 в основном идентична фиг. 4, за исключением детектора напряжения 43, который применяется вместо детектора тока 42 на фиг. 4.

Детектор напряжения 43 может быть образован источником эталонного напряжения 44 и резистором 45, подключенным между источником эталонного напряжения 44 и стоком 36. Резистор 45 можно заменить диодом и тем самым образовать детектор напряжения 43. Это - самая простая конфигурация. Детектор напряжения 43 контролирует напряжение стока 36 при программировании. Во время контролирования, когда напряжение VF,i плавающего затвора 31 достигает порогового напряжения V

Как и в способе детектирования тока, программирование завершается, когда в ответ на сигнал VST остановки программирования первый и/или второй источники напряжения 38 и 39 отсекают напряжение VC,i управляющего затвора и напряжение VP затвора программирования.

Другие компоненты по сути те же, что и в способе с детектированием тока, и они описываться не будут.

Как показано на фиг. 9,a и b, первый вариант осуществления структуры энергонезависимой памяти соответственно изобретению содержит полупроводниковую подложку 50 первого электропроводного типа, имеющую на своей поверхности канальную область, образованный на канальной области плавающий затвор 51, образованный над плавающим затвором 51 управляющий затвор 52, образованный в прилегании к плавающему затвору 51 затвор программирования 53 и образованный между затвором программирования 53, плавающим затвором 51 и управляющим затвором 52 изолирующий слой 54. Изолирующий слой 54 между плавающим затвором 51 и затвором программирования 53 достаточно тонкий для осуществления туннелирования между ними.

Ссылаясь на фиг. 9, a и b, можно заметить, что изоляция защитным слоем оксида 55 образована на поверхности подложки 50, окружающей канальную область. Часть плавающего затвора 51 выходит к поверхности изолирующего защитного оксидного слоя 55. На фиг. 9, b затвор программирования 53 размещен рядом с одной стороной управляющего затвора 52. Изолирующий слой затвора 56 сформирован достаточно тонким для осуществления туннелирования между канальной областью и плавающим затвором 51.

Как показано на фиг. 10, a и b, второй вариант осуществления структуры, соответствующий изобретению, аналогичен первому. В этом варианте часть затвора программирования 53 размещена рядом с нижней поверхностью плавающего затвора 51. Ссылаясь на фиг. 11, a и b, третий вариант осуществления структуры, соответствующий изобретению, показанный на фиг. 11, a и b, аналогичен первому. В этом третьем варианте осуществления затвор программирования 53 размещен сверху от плавающего затвора 51.

На фиг. 12, a и b представлен четвертый вариант структуры энергонезависимой памяти, соответствующий данному изобретению, содержащий полупроводниковую подложку 50 первого электропроводного типа, имеющую канальную область на своей поверхности, образованный на канальной области плавающий затвор 51, две области 57 и 58 легирующей примеси второго электропроводного типа, на каждой стороне канальной области в поверхности полупроводниковой подложки; образованный над плавающим затвором 51 управляющий затвор 52; размещенный рядом с плавающим затвором 51 затвор программирования 53 и изолирующий слой 54, образованный между плавающим затвором 51 и плавающим затвором 52. Изолирующий слой 54 между плавающим затвором 51 и затвором программирования 53 достаточно тонкий, чтобы можно было осуществить между ними туннелирование. Изолирующий защитный оксидный слой 55 окружает канальную область. Изолирующая затвор пленка 56 сформирована достаточно тонкой, чтобы осуществлять туннелирование между канальной областью и плавающим затвором 51.

Как показано на фиг. 13, a, запоминающее энергонезависимое устройство согласно данному изобретению состоит из полупроводниковой подложки 60, множества кодовых шин 61, расположенных с разнесением на заданные расстояния на подложке 60; множества разрядных шин 62, перпендикулярных кодовым шинам и образующих множество квадратов или прямоугольников, расположенных на интервалах с заданным расстоянием; множества программирующих шин 63, расположенных в том же направлении, что и соответствующие разрядные шины; и множества ячеек энергонезависимой памяти 64, расположенных в каждом соответствующем квадрате или прямоугольнике.

Согласно фиг. 13, a, как показано на фиг. 3, каждая из ячеек энергонезависимой памяти 64 состоит из плавающего затвора 65, затвора программирования 66 для подачи в целях программирования, зарядов в плавающий затвор 65, управляющего затвора 67 для контролирования количества зарядов, подаваемых для программирования в плавающий затвор 65, и полевого транзистора 68 для считывания (или контроля) количеств носителей заряда, подаваемых во время программирования в плавающий затвор 65. Полевой транзистор 68 составлен из плавающего затвора 65, истока 69, стока 70, канальной области 71 между истоком 69 и стоком 70.

Управляющий затвор 67 соответствующих ячеек памяти соединен с близлежащей кодовой шиной 61, а затвор программирования 66 соединен с близлежащей программирующей шиной 63. Исток 69 ячейки энергонезависимой памяти 64 обычно соединяется с близлежащей разрядной шиной 62 вместе со стоком 70 ячейки энергонезависимой памяти 64, размещенной в близлежащем или прилегающем квадрате.

Как показано на фиг. 13,b, когда устройство энергонезависимой памяти работает в режиме программирования, напряжение ≈8-≈15 B подается в выбранную программирующую шину 63, 0 B - в невыбранные программирующие шины 63, 3-12 B - в выбранную кодовую шину 61, 0 - ≈10 B - в невыбранные кодовые шины 61, 0,5-2 B - в выбранную разрядную шину 62, 0 B - в невыбранные разрядные шины 62, расположенные слева, например, от выбранной ячейки, 0,5-2 B - в более чем одну разрядную шину, расположенную, например, справа от выбранной ячейки, и 0 B - на подложку 60.

Когда запоминающее энергонезависимое устройство работает в режиме стирания, напряжения прикладываются двумя способами.

Во-первых, для стирания разрядных шин 62 напряжение 0-≈12 B подается на все программирующие шины 63 выбранного блока стирания, ≈7- ≈12 B- на все кодовые шины 61 выбранного блока стирания, 0-6 B - на все разрядные шины 61 выбранного блока стирания и 0 B - на подложку 60.

Для стирания посредством подложки 60 напряжение 0 - ≈12 B подается на все программирующие шины 63 выбранного блока стирания, ≈7 - ≈12 B - на все кодовые шины 61 выбранного блока стирания. Выходы разрядных шин 62 выбранного блока переводятся в третье состояние. Напряжение 0-6 B подается на подложку 60.

Когда запоминающее энергонезависимое устройство работает в режиме считывания, напряжение 0 B подается на программирующие шины 63, напряжение питания VCC - на выбранную кодовую шину 61, 0 B - на невыбранные кодовые шины 61, 0,5-2 B - на выбранную разрядную шину 62, 0 B - на невыбранные разрядные шины 62, размещенные, например, слева; 0,5-2 B - на разрядные шины 62, размещенные, например, справа от выбранной ячейки, и 0 B - на подложку 60.

Напряжения фиг. 13, b могут изменяться структурными характеристиками электрических параметров ячеек памяти, например коэффициентом связи или толщиной изолятора туннеля.

Второй вариант осуществления

Далее следует описание второго варианта осуществления ячейки и устройства энергонезависимой памяти, выполненных согласно данному изобретению, и способа программирования со ссылками на фиг. 14, 15, a, b, 16, a, b, 17 и 18.

Как показано на фиг. 14, энергонезависимая память состоит из плавающего затвора 81, разделенного на первую область 81a и вторую область 81b; программирующего полевого транзистора, включающего первую область 81a плавающего затвора 81, первый сток 82 и общий исток 83, канальную область между первым стоком 82 и общим истоком 83, и имеющего первое пороговое напряжение V

Как показано на фиг. 14, в противоположность первому варианту осуществления второй вариант осуществления ячейки энергонезависимой памяти согласно данному изобретению не имеет затвора программирования и вместо имеется три области легирующей примеси (сток контролирующего транзистора, общий исток и сток программирующего транзистора) на поверхности подложки.

Помимо компонентов по фиг. 14, память на фиг. 15,а содержит первый источник напряжения 88 для подачи напряжения на управляющий затвор 84, второй источник напряжения 89 для подачи напряжения V

На фиг. 15, а напряжение VC,i, подаваемое в управляющий затвор 84 от первого источника напряжения 88, является положительным и изменяется согласно программированию соответствующего порогового уровня при иерархическом программировании. Напряжение V

Как следует из фиг. 15,а, помимо компонентов по фиг. 14, ячейка энергонезависимой памяти кроме вышеперечисленного включает первый источник напряжения 88 для подачи напряжения VC,i в управляющий затвор 84, второй источник напряжения 89 для подачи напряжения V

Даже, когда детектор напряжения 91B на фиг. 15,b используется вместо детектора тока 91A на фиг. 15,а, напряжение VC,i, подаваемое в управляющий затвор 84 от первого источника напряжения 88, является положительным и изменяется согласно программированию соответствующего порогового уровня в многоуровневом программировании. Напряжение V

Напряжение VP устанавливается на величину, меньшую или равную нулю (≤0), и подается на затвор программирования первого варианта осуществления, изображенного на фиг. 15, a и b, использует программирующий полевой транзистор вместо затвора программирования.

В ячейке энергонезависимой памяти, состоящей из управляющего затвора 84; плавающего затвора, разделенного на первую и вторую области 81a и 81b; программирующего полевого транзистора, имеющего первое пороговое напряжение V

На фиг. 14, 15,a и b подача носителей заряда в плавающий затвор 81 из первой канальной области 86 для программирования может осуществляться горячей инжекцией носителей или туннелированием Фаулера-Норхайма (ФНХ). В случае программирования с помощью механизма туннелирования напряжение, прилагаемое к первому стоку, меньше или равно нулю, а напряжение, прилагаемое к общему истоку, равно напряжению первого стока.

Как показано на фиг. 16,a и b, ячейка энергонезависимой памяти состоит из полупроводниковой подложки 92 первого электропроводного типа (P-тип), первой области легирующей примеси 93 второго электропроводного типа (n+), второй области легирующей примеси 94, третьей области легирующей примеси 95, последовательно образованных на поверхности подложки 92, разнесенных на заданные расстояния, первого изоляционного слоя 98 затвора на первой и второй областях 93 и 94 легирующей примеси на подложке 92, второго изоляционного слоя 99 затвора на второй области 94 легирующей примеси и третьей области 95 легирующей примеси, толщина которого отличается от толщины первого изоляционного слоя 98 затвора; первой канальной области 100, определяемой участком между первой и второй областями 93 и 94 легирующей примеси на поверхности подложки 92, второй канальной области 101, определяемой участком между второй и третьей областями 94 и 95 легирующей примеси на поверхности подложки 92; плавающего затвора 96, образованного над первой и третьей областями 93 и 95 легирующей примеси на первом и втором изоляционных слоях 98 и 99 затвора; управляющего затвора 97, образованного над плавающим затвором 96; и слоя 102 изоляции, и изоляционного слоя 102, образованного для изолирования плавающего затвора 96 от управляющего затвора 97.

Здесь, как показано на фиг. 16,b, второй изолирующий слой 99 затвора толще первого изолирующего слоя 98 затвора. Первый изолирующий слой 98 затвора определен достаточно тонким, чтобы носители заряда могли стираться в первую канальную область 100 от плавающего затвора 96 посредством туннелирования.

Хотя на фиг. 16,a и b это подробно не показано, изолирующий поле слой 103 формируется на поверхности подложки 92, исключая первый изолирующий слой 98 затвора и второй изолирующий слой 99 затвора. На фиг. 16,a и b плавающий затвор 96 сформирован на первой и второй канальных областях 100 и 101. Часть плавающего затвора 96 выходит на поверхность изолирующего слоя 103.

Как показано на фиг. 17, запоминающее энергонезависимое устройство, согласно данному изобретению, состоит из множества кодовых шин 104, расположенных с разнесением на заданные расстояния; множества разрядных шин 105 второго электропроводного типа, расположенных перпендикулярно кодовым шинам 104 и тем самым образующих множество квадратов или прямоугольников, разнесенных на заданные расстояния; шин 106 общего истока, делящих соответствующие квадраты и прямоугольники в том же направлении, что и разрядные шины 105, на левую и правую области между разрядными шинами 105; и множества ячеек энергонезависимой памяти, имеющих управляющий затвор 84, плавающий затвор 81, разделенный на первую и вторую области 81a и 81b, программирующий полевой транзистор, находящийся, например, справа от квадратов и подающий носители зарядов в плавающий затвор 81 для программирования, и контролирующий полевой транзистор, находящийся, например, слева от квадратов и контролирующий количество носителей зарядов плавающего затвора 81 при программировании. Программирующий полевой транзистор включает первую область 81a плавающего затвора 81, первый сток 82, общий сток 83 и первую канальную область 86 между первым стоком 82 и общим истоком 83. Контролирующий полевой транзистор включает вторую область 81b плавающего затвора 81, второй сток 85, общий сток 83, вторую канальную область 87 между вторым стоком 85 и общим истоком 83. Управляющий затвор 84 соединен с близлежащей кодовой шиной 104, общий исток 83 соединен с шиной 106 общего истока. Первый сток 82 соединен с близлежащей разрядной шиной 105 вместе с вторым стоком 85 энергонезависимой памяти, находящейся в квадрате, например, справа от первого стока, а второй сток 85 соединен с первым стоком 82 энергонезависимой памяти, находящейся в квадрате, например, слева от второго стока 85.

Устройство энергонезависимая память по фиг. 17 действует в режиме программирования с использованием механизма горячей инжекции носителей. Как показано на фиг. 18, напряжение 6 - 13 B можно прилагать к выбранной кодовой шине, 0 B - к невыбранной кодовой шине, 5 - 9 B - к выбранной n-й разрядной шине, 0,5 - 2 B - к выбранным (n - 1)-м разрядным шинам, 0 B - к другим разрядным шинам, 0 B - к выбранной n-й шине истока; причем выводы невыбранной (n + 1)-й шины истока переводятся в третье состояние, невыбранная (n-1)-я шина истока равна выбранной (n-1)-й разрядной шине; и O B - к подложке. Когда запоминающее энергонезависимое устройство действует в режиме программирования с помощью механизма туннелирования, напряжение 10 - 20 B прилагается к выбранной кодовой шине, O B - к невыбранной шине, O B - к выбранной n-й разрядной шине, 5 - 10 B - к другим разрядным шинам, O B - к выбранной n-й шине истока, 5 - 10 B - к другим шинам истока и O B - к подложке.

Когда запоминающее энергонезависимое устройство по фиг. 17 действует в режиме стирания, напряжение от -7 до -12 B может прилагаться к выбранной кодовой шине и невыбранной кодовой шине, выводы всех разрядных шин переводятся в третье состояние, VCC прилагается ко всем шинам истока и O B - к подложке.

Когда запоминающее энергонезависимое устройство по фиг. 17 действует в режиме считывания, VCC может прилагаться к выбранной кодовой шине, напряжение O B - к невыбранной кодовой шине, напряжение от 0,5 B до 2 B - к выбранной n-й разрядной шине, O B - к другим разрядным шинам, O B - ко всем шинам истока и O B - к подложке.

Напряжение по фиг. 18 можно изменять структурными характеристиками или электрическими параметрами ячеек памяти, например коэффициентом связи или толщиной туннельного изолятора.

Как указано выше, данное изобретение обладает преимуществами в следующих отношениях.

Во-первых, программирование соответствующего порогового уровня выполняется лишь изменением напряжения управляющего затвора, в результате чего облегчается многоуровневое программирование.

Во-вторых, соответствующие уровни порогового напряжения и соответствующие напряжения управляющего затвора линейны, и сдвиг порогового напряжения совпадает со сдвигом напряжения управляющего затвора, точно регулируя сдвиг соответствующих напряжений порогового уровня.

В-третьих, состояние стирания контролируется программированием низшего уровня при произвольном напряжении управляющего затвора, в результате чего проблема излишнего стирания устраняется.

В-четвертых, программирование и контроль выполняются одновременно в самой ячейке энергонезависимой памяти, не требуя отдельной схемы для контроля программированного содержания и ускоряя скорость программирования.

В-пятых, перед стиранием предварительное программирование не нужно.

В-шестых, для работы требуется невысокое напряжение - ниже ±12B.

В-седьмых, для контроля требуется только слабый ток - меньше нескольких долей или десятых 1мА.

В-восьмых, ячейка энергонезависимой памяти сконструирована как простой многоуровневый затвор, а не расщепленный канал, что делает ее более компактной.

В-девятых, точность многоуровневого программирования, то есть распределение погрешностей программирования пороговых напряжений, точно определяется только параметрами, зафиксированными во время изготовления энергонезависимой памяти, и приложенными напряжениями смещения. По этой причине распределение погрешностей соответствующих уровней энергонезависимой памяти данного изобретения не зависит от большого числа циклов программирования/стирания. Даже во время программирования память не зависит от захвата зарядов в оксидном слое, подвижности каналов, сопротивления разрядной шины и неустойчивых или непредсказуемых электрических компонентов.

В-десятых, в способе программирования энергонезависимой памяти согласно данному изобретению управление осуществляется напряжением, благодаря чему этот способ выполняет многоуровневое программирование легче и точнее, чем способ с управлением тока.

В-одиннадцатых, запоминающее энергонезависимое устройство согласно данному изобретению реализует матрицу с бесконтактной виртуальной "землей" при помощи структуры простого многоуровневого затвора, а не асимметричной ячейки, подобной структуре расщепленного канала, благодаря чему значительно уменьшается размер кристалла.

В двенадцатых, исток и сток энергонезависимой памяти согласно данному изобретению используется только в считывании, с приложением низкого напряжения, требуемого только для считывания на исток и сток. Тем самым оптимизируется диффузионная область истока и стока.

Изложенное выше описание предпочтительных вариантов осуществления изобретения дано в целях иллюстрирования и описания. Его цель не заключается в исчерпывающем описании или в точном ограничении изобретения раскрытой здесь формой; модификации и изменения возможны в свете вышеизложенных объяснений, либо могут осуществляться при практическом использовании данного изобретения. Изложенные выше варианты осуществления были выбраны и описаны для объяснения принципов изобретения и его практической реализации, чтобы специалист в данной области смог использовать изобретение в различных осуществлениях и с разными модификациями применительно к конкретным случаям его использования. Следует иметь в виду, что объем изобретения определяется формулой изобретения и ее эквивалентами.

Изобретение относится к энергонезависимой памяти и способам ее программирования. Целью изобретения является создание энергонезависимой памяти и способа ее программирования, при котором контроль осуществляют одновременно с многоуровневым программированием. При этом области программирования и контроля полностью разделены. Ячейка энергонезависимой памяти включает плавающий затвор, область программирования, имеющую первый путь тока к плавающему затвору. С помощью изобретения можно осуществлять программирование подачи носителей заряда в плавающий затвор по первому пути тока, либо извлечение носителей заряда, накопленных в плавающем затворе. Область контроля имеет второй путь тока, отделенный от первого пути тока. Контроль количества заряда плавающего затвора осуществляется посредством второго пути тока при программировании. 9 с. и 45 з.п. ф-лы, 18 ил.

| US, патент, 5268318, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| US, патент, 5187683, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| EP, заявка, 0647947, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1998-05-20—Публикация

1996-01-24—Подача