Область техники, к которой относится изобретение

Настоящее изобретение касается запоминающего устройства, способного к интеграции очень высокой степени для обеспечения матрицы ячеек памяти.

Предпосылки создания изобретения

В традиционных полупроводниковых запоминающих устройствах один бит информации представляется электронами, хранящимися в статическом конденсаторе в каждой ячейке памяти. Двоичное число "1" представляется дефицитом N электронов, а "0" представляется состоянием нейтрального заряда. В обычном 16-мегабитовом динамическом запоминающем устройстве с произвольной выборкой (ДЗУПВ) количество электронов N составляет порядка 800000. Для увеличения объема памяти отдельные ячейки памяти необходимо делать меньше, но этого нельзя достичь просто с помощью уменьшения обычной ячейки памяти, поскольку существует нижний предел для величины N. Количество электронов N ограничивается необходимостью согласовывать ток утечки из ячейки, внутренний шум и влияние падающих альфа-частиц, и эти факторы не снижаются соразмерно с уменьшением площади ячейки памяти. Можно оценить, что N должно быть свыше 130000 в 16-гигабитном ДЗУПВ, то есть коэффициент приблизительно в 6 раз меньше, чем для 16-мегабитного ДЗУПВ. Однако размер ячейки, требуемой для 16-гигабитного ДЗУПВ, необходимо снизить на три порядка по величине по сравнению с 16-мегабитным ДЗУПВ и, следовательно, уменьшенный размер ячейки не может вместить количество электронов, требуемое для удовлетворительной работы. Пытаясь сохранить величину N достаточно большой, исследовали трехмерные конденсаторы с имеющими вырезы или многоуровневыми структурами вместе с пленками конденсаторов, имеющими высокую диэлектрическую проницаемость, но полученные в результате предлагаемые структуры и процессы изготовления оказались крайне сложными. Кроме того, существенно возросло потребление энергии, поскольку во время хранения данных необходимо обновлять сравнительно большое количество N электронов в ячейках, и это время имеет тенденцию сокращаться, так как масштаб устройства минимизируется.

Другой тип запоминающего устройства, который демонстрирует энергонезависимые характеристики, известен как флэш-память. В таком устройстве приблизительно 105 электронов инжектируются в плавающий затвор через туннельный переход, обычно образованный из SiO2 с толщиной порядка 10 нм. Хранящийся заряд образует поле, которое влияет на электрический ток на участке между стоком и истоком. Заряд либо записывается на плавающий затвор, либо стирается с него, применяя электрическое поле через затвор. Во время циклов стирания и записи применяется очень высокое электрическое поле, и в результате пленка SiO2 разрушается, ограничивая срок службы запоминающего устройства заранее определенным количеством циклом стирания-записи, обычно равным порядка 105 циклов. Более того, время стирания-записи обычно составляет несколько миллисекунд, на четыре порядка по величине ниже, чем у обычного ДЗУПВ. Такая плохая характеристика ограничивает применение устройств флэш-памяти.

До настоящего времени предлагались альтернативные способы с целью обеспечения запоминающих устройств, которые работают с небольшими, точными количествами электронов, известных как одноэлектронные запоминающие устройства. Одноэлектронное запоминающее устройство описано в заявке этого же заявителя на патент РСТ/GВ93/02581 WO-A-94/15340). Точное количество электронов поступает в узел памяти или покидает его через многотуннельный переход под управлением прикладываемых напряжений затвора, а электронное состояние в узле памяти определяется с помощью электрометра. Однако недостаток устройства заключается в том, что для каждого узла памяти требуется значительное количество схем, и устройство в настоящее время работает только при низкой температуре, ниже температуры жидкого гелия 4,2 К. К. Яно, Т. Ишии, Т. Хашимото, Т. Кобаяси, Ф. Мурай и К. Секи в работе "Транзакции по электронным устройствам", Институт инженеров по электротехнике и радиоэлектронике (IEEE), сентябрь 1994 г. , т.41, 9, стр.1628-1638, и К. Яно, Т. Ишии, Т. Сано, Т. Майн, Ф. Мурай и К. Секи в 1996 г. в работе "Международная конференция по вопросам твердотельных схем". Институт инженеров по электротехнике и радиоэлектронике (IEEE), 1996 г., FR 16.4, стр.266, предложили и продемонстрировали другое одноэлектронное запоминающее устройство. В устройстве используется поликристаллическая пленка, проходящая между истоком и стоком, к которой прикладывается напряжение затвора. Небольшое количество электронов хранится в зернистой структуре поликристаллической кремниевой пленки. Размер памяти является относительно небольшим по сравнению со структурой в упомянутой выше заявке на патент РСТ/GВ93/02581, и она способна работать при комнатной температуре. Кроме того, память демонстрирует несколько преимуществ по сравнению с обычной флэш-памятью, при меньшем времени стирания-записи из-за небольшого количества хранящихся электронов, и оперативный срок службы улучшен благодаря тому, что используется низковольтная туннельная инжекция, а не инжекция электронов высоким полем. Однако время считывания хранящейся информации относительно длительное, порядка нескольких микросекунд, поскольку необходимо иметь достаточно высокое сопротивление между истоком и стоком для гарантии длительного времени хранения электронов в гранулах.

Другая конструкция описана С. Тивари, Ф. Рэнэ, Х. Хэнэфи, А. Харстейном, Е. Ф. Краббом и К. Ченом в "Журнале прикладной физики", 4 марта 1996 г., том 68, 10, стр. 1377-1379, С. Тивари, Ф. Рэнэ, К. Ченом, Л. Ши и Х. Хэнэфи в "Журнале прикладной физики", 26 августа 1996 г., том 69, 9, стр.1232-1234, и Х.Ай. Хэнэфи, С. Тивари и Ай. Кэном в работе "Транзакции по электронным устройствам". Институт инженеров по электротехнике и радиоэлектронике (IEEE), 9 сентября 1996 г. , т.43, 9, стр.1553-1558. В этом запоминающем устройстве используются кремниевые кристаллы, которые лежат под затвором транзисторного устройства. Электроны инжектируются в кремниевые нанокристаллы, которые имеют размер 5 нм, из кремниевой подложки через тонкий туннельный оксидный слой толщиной порядка 1,1-1,8 нм. Хранящиеся электроны смещают пороговое напряжение транзистора. Время считывания хранящейся информации является сравнительно коротким, порядка нескольких десятков наносекунд, поскольку канал транзистора имеет высокую подвижность электронов. Цикл долговечности для записи и считывания информации существенно улучшен по сравнению с обычным устройством флэш-памяти. Однако время считывания неудовлетворительно большое, порядка нескольких миллисекунд, так как выравнивание зоны проводимости неблагоприятно для туннелирования электронов из нанокристаллов в объемный кремний.

Другое запоминающее устройство, которое функционирует в соответствии с принципами флэш-памяти, раскрыто в работе "Электрически перепрограммируемая память, использующая структуру двойного инжектора электронов" Д.Дж. Ди-Мария, К.М. Де-Мейера и Д.У. Донга, "Журнал по электронным устройствам". Институт инженеров по электротехнике и радиоэлектронике (IEEE), том EDL-1, 9, сентябрь 1980 г., стр.179-181. В этом устройстве проводимость участка между стоком и истоком управляется зарядом, записываемым или стираемым с плавающего затвора через туннельный переход с электрода затвора. Однако недостатки данного устройства заключаются в том, что оно имеет медленное время считывания-записи, порядка миллисекунд, и что срок службы туннельного перехода ограничен, поскольку, как и в обычной флэш-памяти, используется инжекция высокого поля Фоулера-Нордхейма. Аналогичное устройство описано в патенте США 3878549, выданном С. Ямазаки.

Краткое изложение сущности изобретения

С целью преодоления этих проблем и недостатков изобретение обеспечивает запоминающее устройство, содержащее канал для носителей заряда, узел для хранения заряда с целью образования поля, которое изменяет проводимость канала, и конфигурацию туннельного перехода, через который носители заряда туннелируют в ответ на данное напряжение, чтобы запоминаться в узле, где конфигурация туннельного перехода проявляет профиль энергетической зоны, который содержит относительно широкий с точки зрения размера элемент барьера со сравнительно низкой высотой барьера и по меньшей мере один относительно узкий с точки зрения размера элемент барьера со сравнительно большой высотой барьера.

Изобретение позволяет оптимизировать для запоминающего устройства время записи, считывания и стирания.

Относительно широкий элемент барьера профиля энергетической зоны действует как барьер для долгосрочного хранения заряда в узле. Широкий элемент барьера можно повысить и понизить по выбору так, что заряд после этого может туннелировать через относительно узкий элемент барьера, чтобы быть записанным или стертым из узла.

Элемент профиля энергетической зоны, который имеет относительно большую высоту барьера, может быть обеспечен с помощью элемента с шириной 3 нм или меньше. Можно включить множество элементов относительно высокого барьера и можно подходящим образом обеспечить конфигурацию многотуннельного перехода.

Конфигурацию барьера можно делать с помощью ряда различных способов. Она может включать чередующиеся слои относительно электропроводного и электроизоляционного материала, где слои совместно обеспечивают относительно широкий элемент барьера небольшой высоты профиля энергетической зоны, а отдельные электроизоляционные слои обеспечивают элементы относительно высокого барьера. Чередующиеся слои могут содержать поликристаллический кремний и нитрид кремния, соответственно, хотя можно использовать и другие материалы.

В качестве альтернативы, конфигурация барьера может содержать конфигурацию барьера Шотки с чередующимися слоями электропроводного материала и полупроводникового материала.

Узел хранения заряда может содержать слой электропроводного материала между барьерной конфигурацией и каналом. Узел может содержать множество электропроводных островков. В альтернативном устройстве островки распределены в барьерной конфигурации и могут давать повышение элементам относительно низкого барьера профиля энергетической зоны благодаря их энергии заряда. Островки могут иметь диаметр 5 нм или меньше. Их можно размещать в слоях, разделенных электроизоляционным материалом.

Островки можно образовывать с помощью ряда способов. Они могут содержать нанокристаллы полупроводникового материала. В качестве альтернативы, их можно образовывать из металла, например, с помощью напыления, так, чтобы распределить их в электроизоляционном металлическом окисле. В качестве альтернативы, островки могут содержать частицы, осажденные из жидкой суспензии металлических или полупроводниковых частиц.

Конфигурацию туннельного перехода можно располагать между каналом и управляющим электродом так, чтобы с помощью изменения напряжения на управляющем электроде можно было управлять величиной заряда, который туннелирует в узел хранения заряда. В другой соответствующей изобретению конфигурации предусмотрен электрод затвора для приложения дополнительного поля к конфигурации барьера заряда для управления туннелированием заряда в узел.

Величина заряда, который может храниться в узле, может ограничиваться посредством эффекта блокировки Кулона, дискретным числом электронов.

При использовании конфигурация туннельного перехода демонстрирует диапазон запирающих напряжений, в котором носитель заряда, туннелирующий в узел, блокируется, и может быть обеспечено средство управления для увеличения и уменьшения диапазона запирающих напряжений с целью управления величиной заряда, хранящегося в узле. Величина заряда, которая может храниться в узле, может быть ограничена множеством дискретных электронных состояний. Средство управления может действовать с целью повышения и понижения диапазона запирающих напряжений таким образом, чтобы обеспечить возможность проявлять только выбранное одно из состояний в узле.

В качестве альтернативы, средство управления может функционировать для изменения ширины диапазона запирающих напряжений.

Соответствующее изобретению запоминающее устройство пригодно для изготовления в виде множества ячеек памяти в матрице из рядов и столбцов на общей подложке.

Данные можно избирательно считывать из каждой ячейки отдельно, а новые данные можно записывать в ячейку или можно обновлять записанные данные. Матрица ячеек памяти может включать линии считывания для обнаружения тока, протекающего по каналам соответствующих столбцов ячеек памяти, линии слов, линии данных для управления барьерными конфигурациями ячеек памяти их соответствующих столбцов, схему предварительной зарядки, предназначенную для предварительной зарядки линии считывания, линии считывания, снимающие уровень заряда в зависимости от хранящегося заряда в узле хранения заряда конкретной одной из ячеек в ее столбце, считываемом под действием напряжения считывания, прикладываемого к соответственной линии слов, схему считывания-записи для передачи уровня напряжения линии считывания в соответствующую линию слов для столбца, выдачу данных в ответ на уровень напряжения в линии данных для обеспечения выходных данных, соответствующих хранящимся данным в ячейке считывания, и средство обновления данных для приложения напряжения записи к линии слов считываемой ячейки так, что данные, соответствующие уровню напряжения в линии данных, записываются обратно в считанную прежде ячейку. Эта матрица также может включать средство для изменения уровня напряжения на линии данных после действия схемы считывания-записи под действием входных данных, подлежащих записи в ячейку, таким образом, что входные данные записываются в ячейку.

Предпочтительные схемы для матрицы можно образовывать на общей подложке с ячейками памяти, а исток и стоки транзисторов в периферийных схемах можно делать с помощью тех же самых этапов процесса, которые используются для образования областей стоков и истоков в ячейках матрицы.

Изобретение также включает способ изготовления запоминающего устройства, которое содержит канал для носителей заряда, узел для хранения заряда, который меняет проводимость канала, и конфигурацию туннельного перехода, через которую носители заряда туннелируют в ответ на данное напряжение, так, чтобы запоминаться в узле, причем способ включает образование конфигурации туннельного перехода таким образом, что она демонстрирует профиль энергетической зоны, который содержит относительно широкий по размеру барьерный компонент с относительно низкой высотой барьера и по меньшей мере один относительно узкий по размеру барьерный компонент с относительно большой высотой барьера.

Краткое описание чертежей

Для того чтобы изобретение стало более понятным, теперь в качестве примера будут описаны его варианты осуществления со ссылкой на прилагаемые чертежи, на которых;

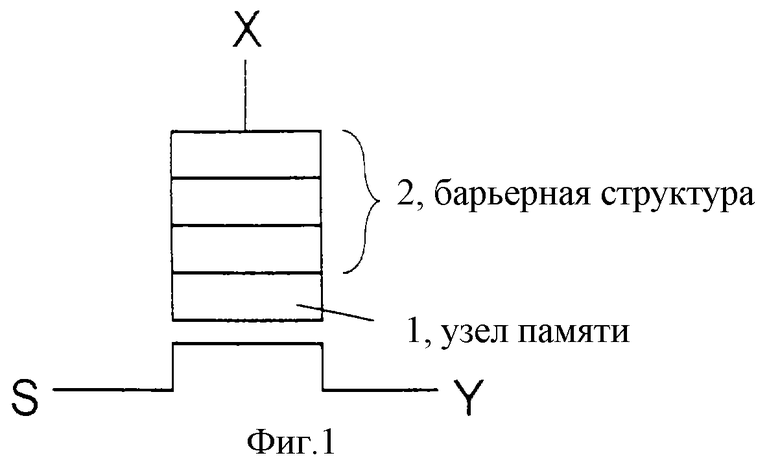

Фиг. 1 представляет схематическое изображение первого типа соответствующего изобретению запоминающего устройства.

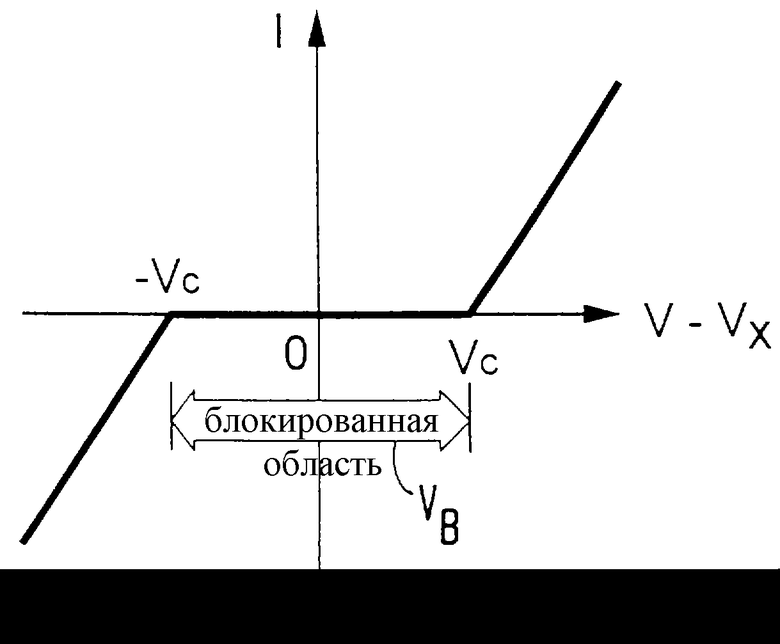

Фиг. 2 представляет график вольт-амперных характеристик показанной на фиг.1 барьерной структуры 2.

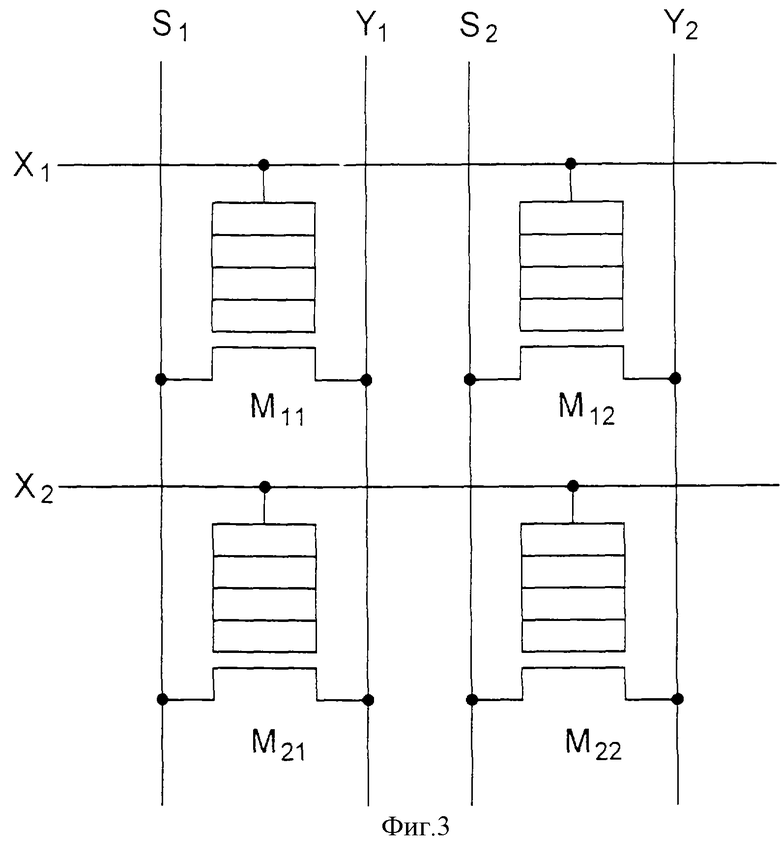

Фиг. 3 представляет схематическое изображение принципиальной электрической схемы матрицы из показанных на фиг.1 запоминающих устройств.

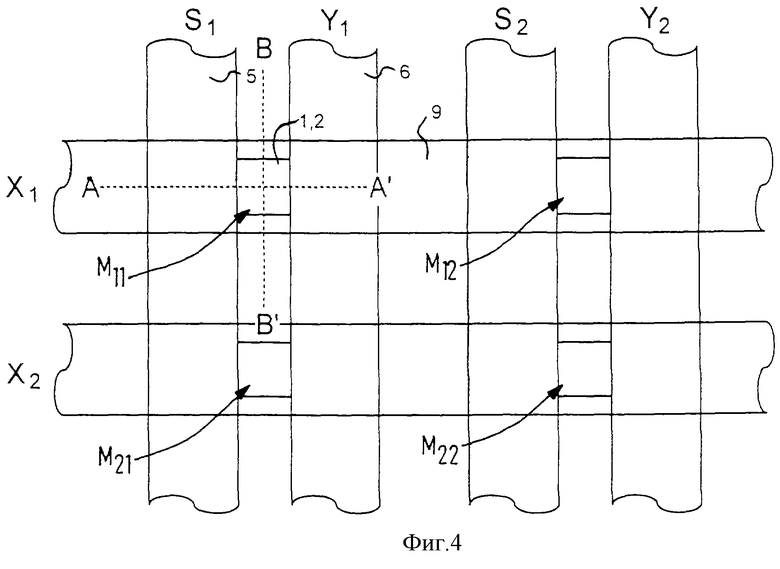

Фиг.4 представляет схематический вид сверху структурной конфигурации показанной на фиг.3 схемы матрицы памяти.

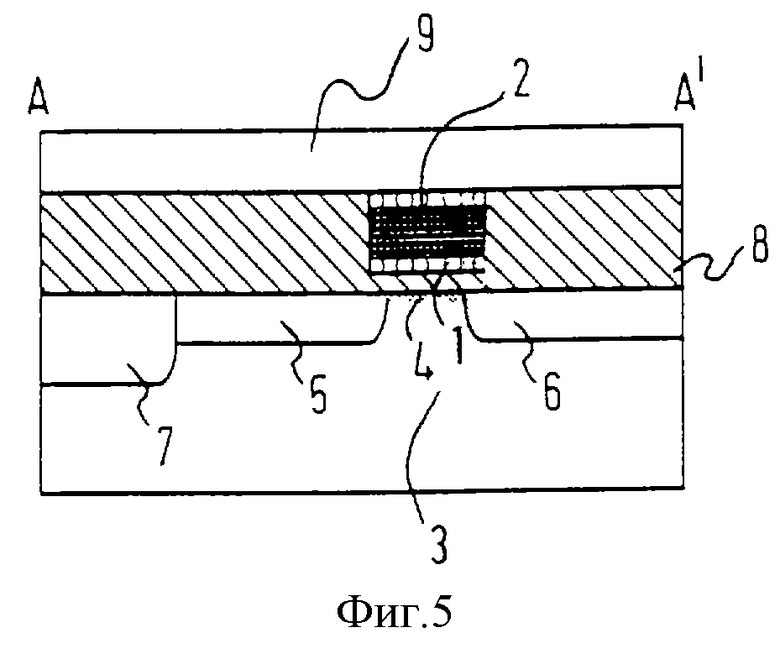

Фиг. 5 представляет вид в разрезе, взятый по линии А-А' фиг.4 через ячейку памяти M11.

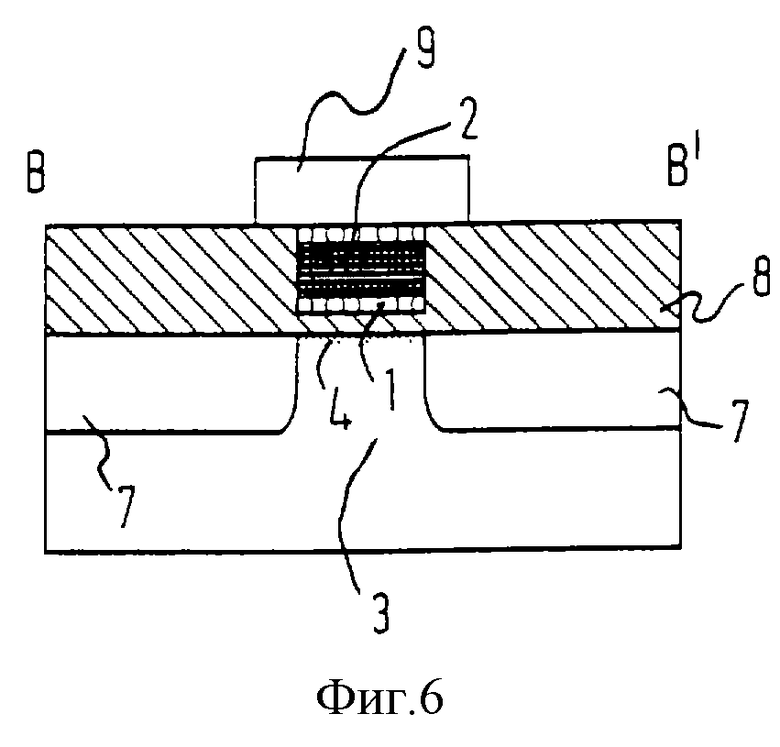

Фиг.6 представляет сечение ячейки М11 фиг.4, взятое по линии В-В'.

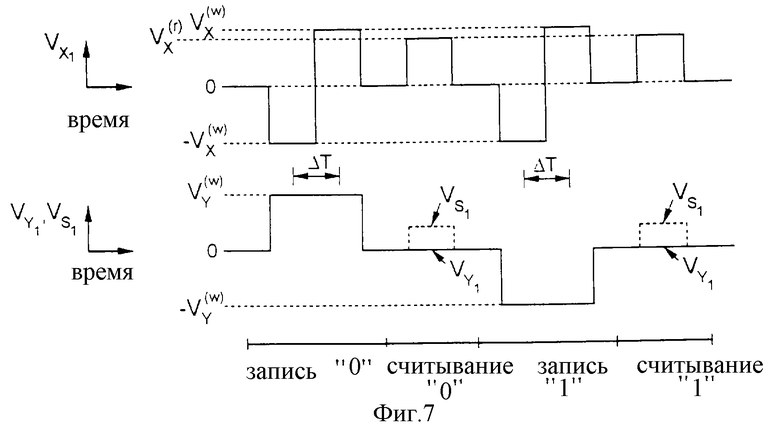

Фиг. 7 иллюстрирует способ считывания и записи данных в отдельную ячейку матрицы памяти.

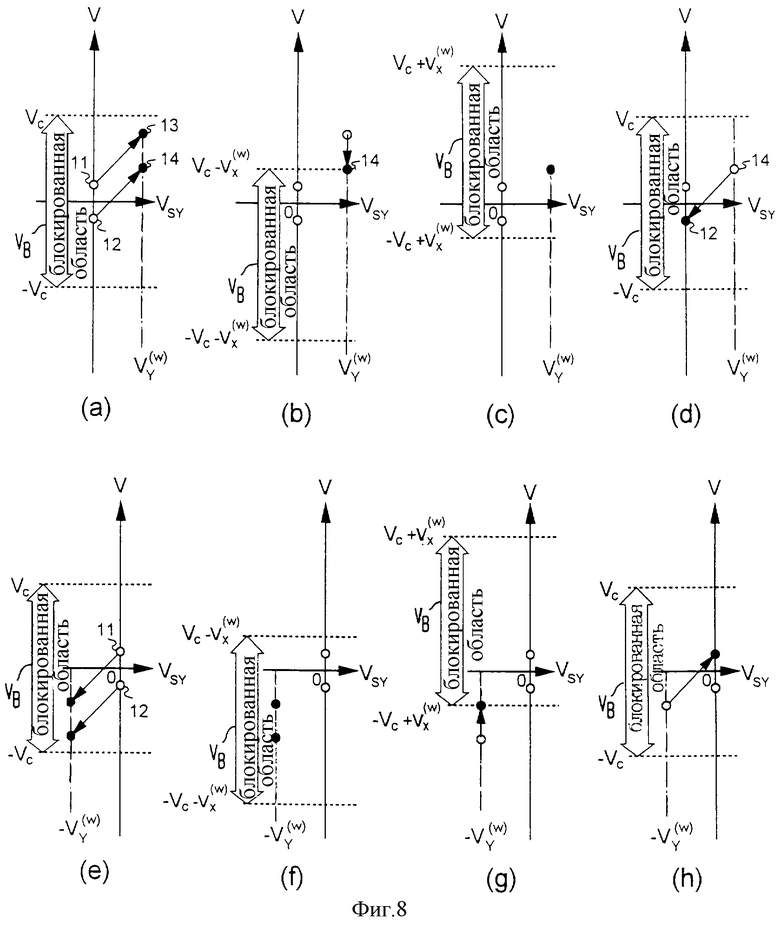

Фиг. 8 представляет график напряжения V узла памяти 1 запоминающего устройства, построенный относительно напряжения VSY, на истоке и стоке устройства во время записи двоичного "0" (фиг.8а-8d) и записи двоичной "1" (фиг.8е-8h).

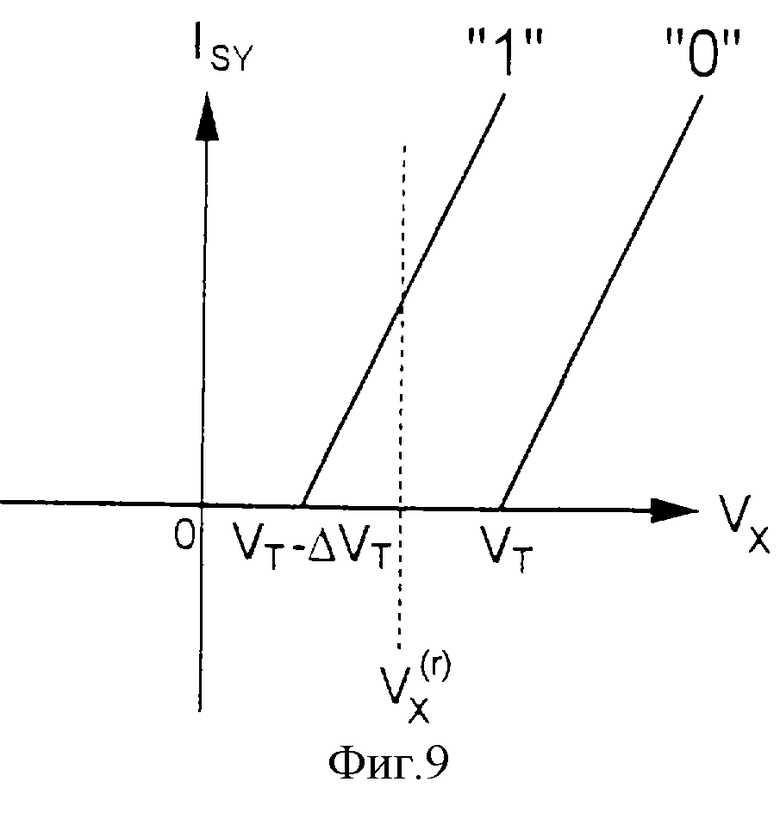

Фиг. 9 представляет график зависимости тока стока-истока ISY от управляющего напряжения затвора VX для двоичной "1" и "0", хранящихся в узле памяти 1.

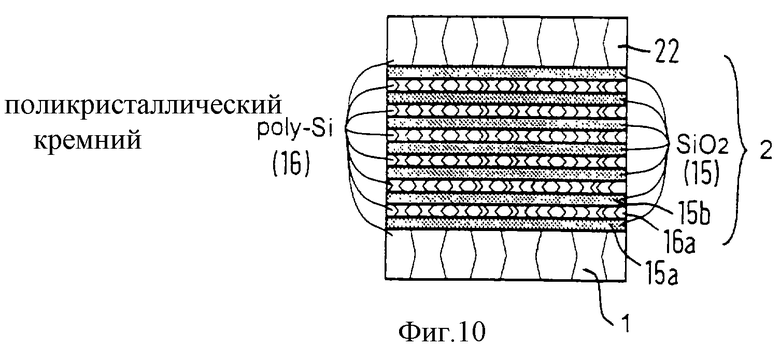

Фиг. 10 представляет более подробный вид в разрезе барьерной структуры 2 запоминающего устройства.

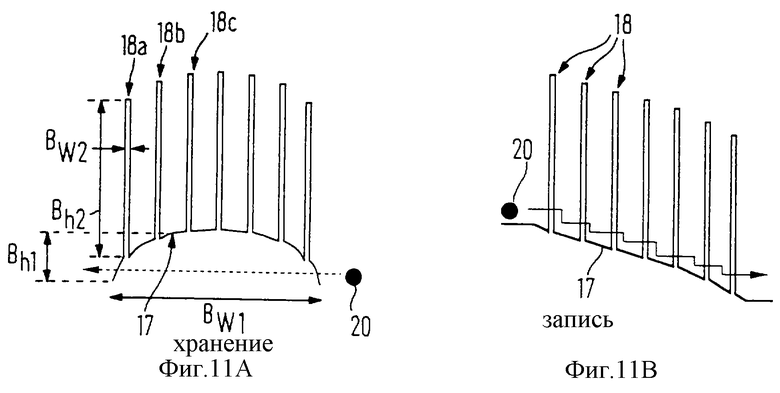

Фиг. 11а иллюстрирует диаграмму энергетической зоны проводимости для барьерной структуры 2, при запоминании носителей заряда в узле памяти 1.

Фиг. 11b иллюстрирует соответствующую диаграмму энергетической зоны, когда носители заряда записываются в узел 1 путем туннелирования из управляющего электрода X.

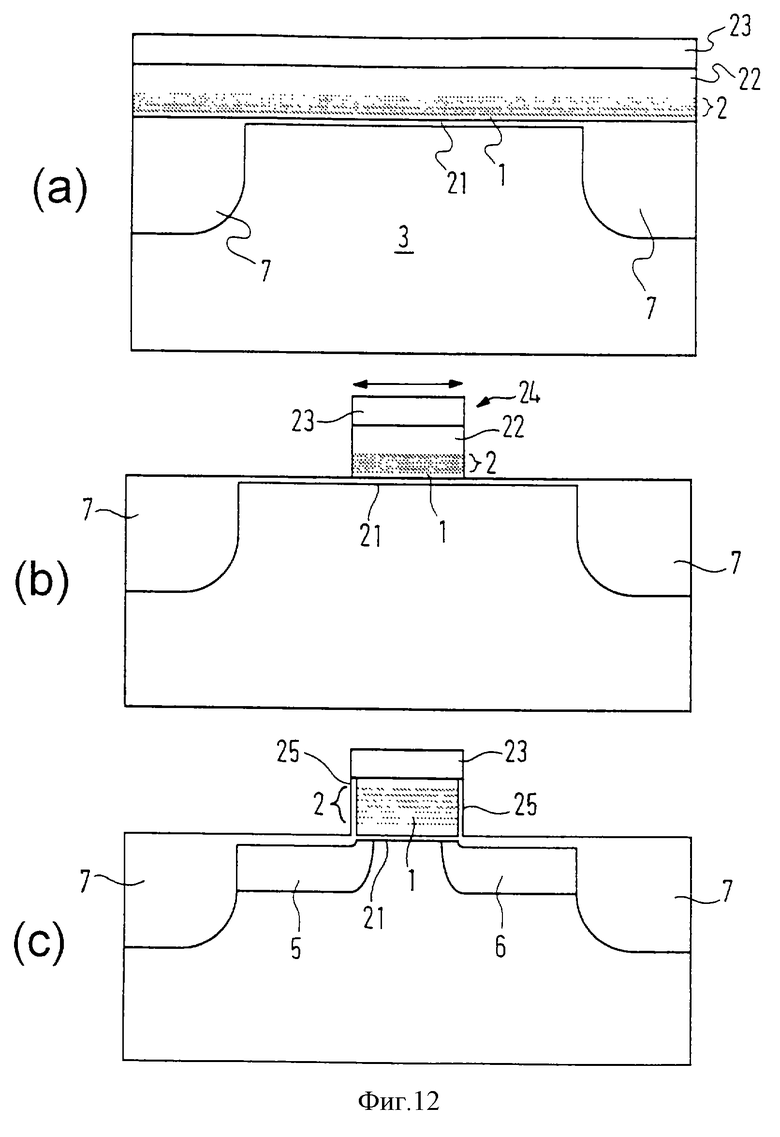

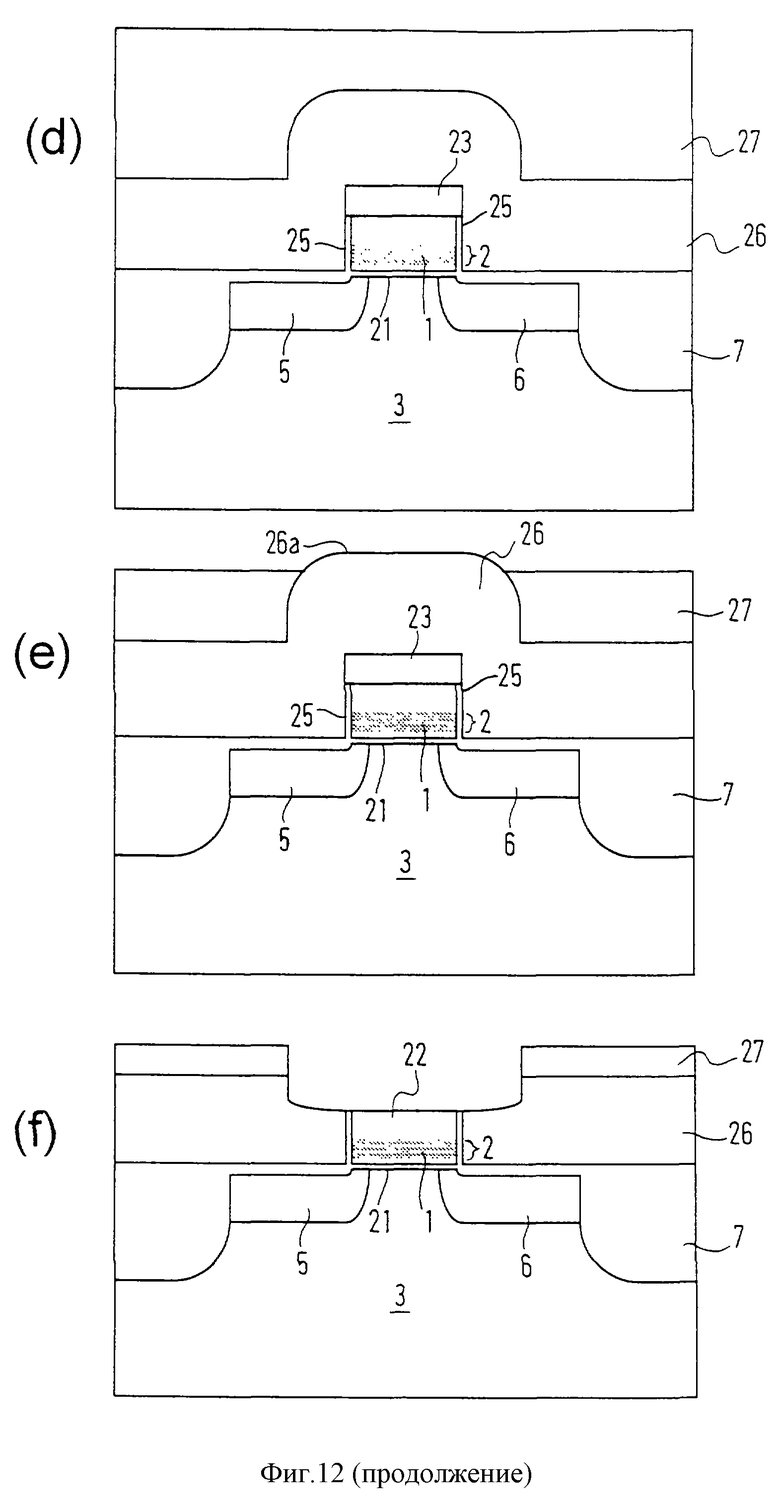

Фиг. 12а-12f представляют виды в поперечном разрезе, соответствующем линии А-А' на фиг. 4, иллюстрирующие различные производственные этапы изготовления запоминающего устройства.

Фиг. 13 представляет схематический поперечный разрез структуры барьера Шотки, который в качестве альтернативы можно использовать в запоминающем устройстве.

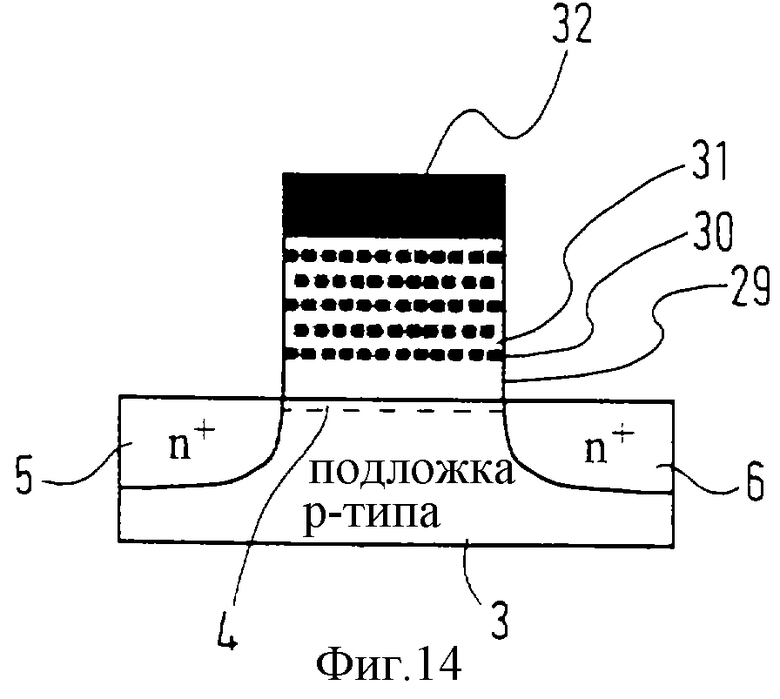

Фиг.14 представляет схематический поперечный разрез альтернативной барьерной структуры, которая включает проводящие островки нанометрического масштаба, для третьего варианта осуществления запоминающего устройства в соответствии с изобретением.

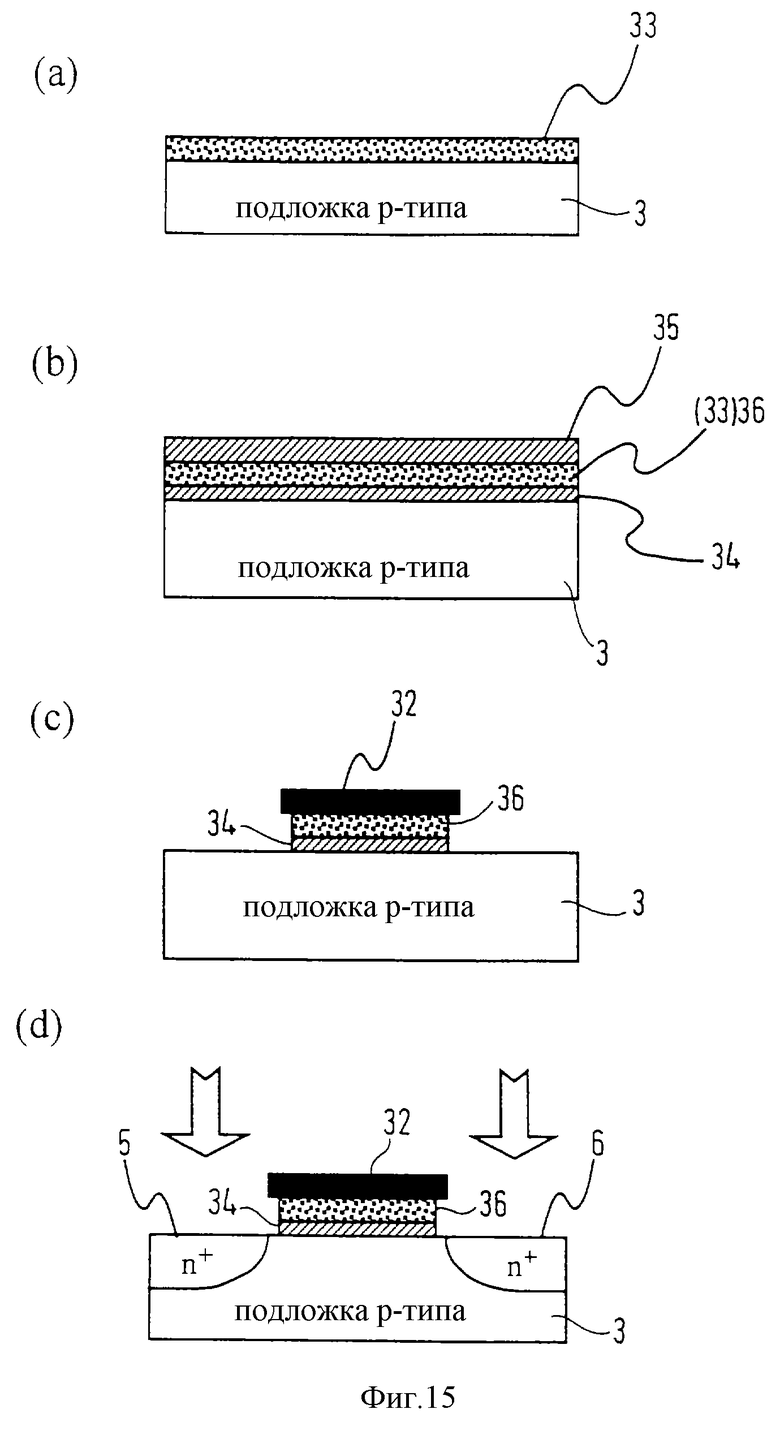

Фиг. 15 иллюстрирует ряд производственных этапов для изготовления соответствующего изобретению запоминающего устройства, в котором кремниевые кристаллы нанометрического масштаба распределены по всему SiO2.

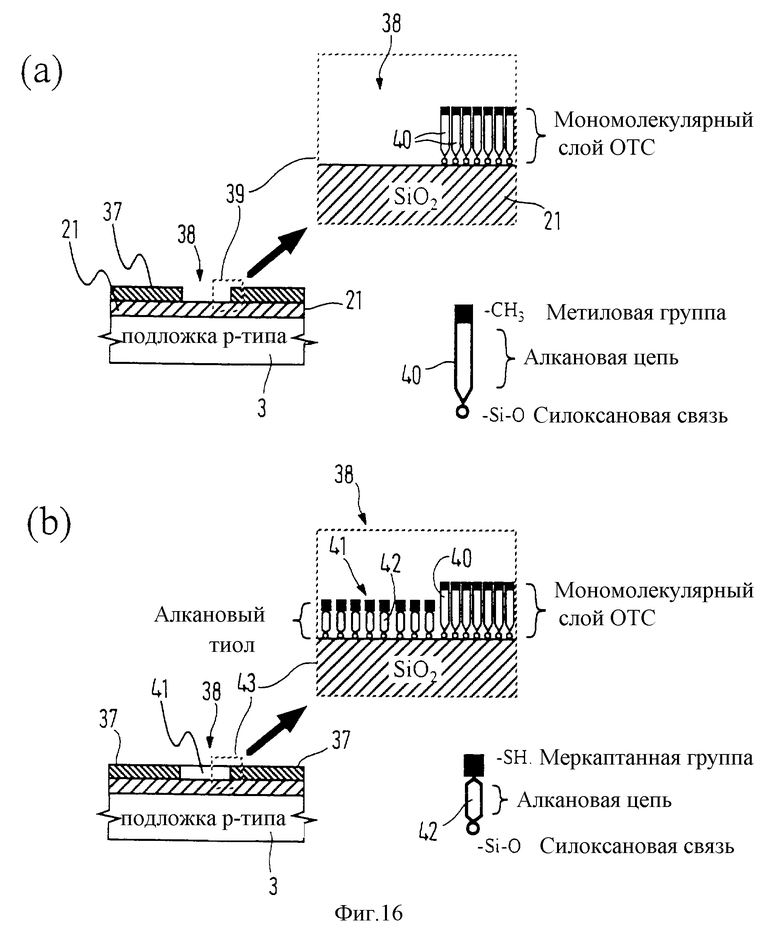

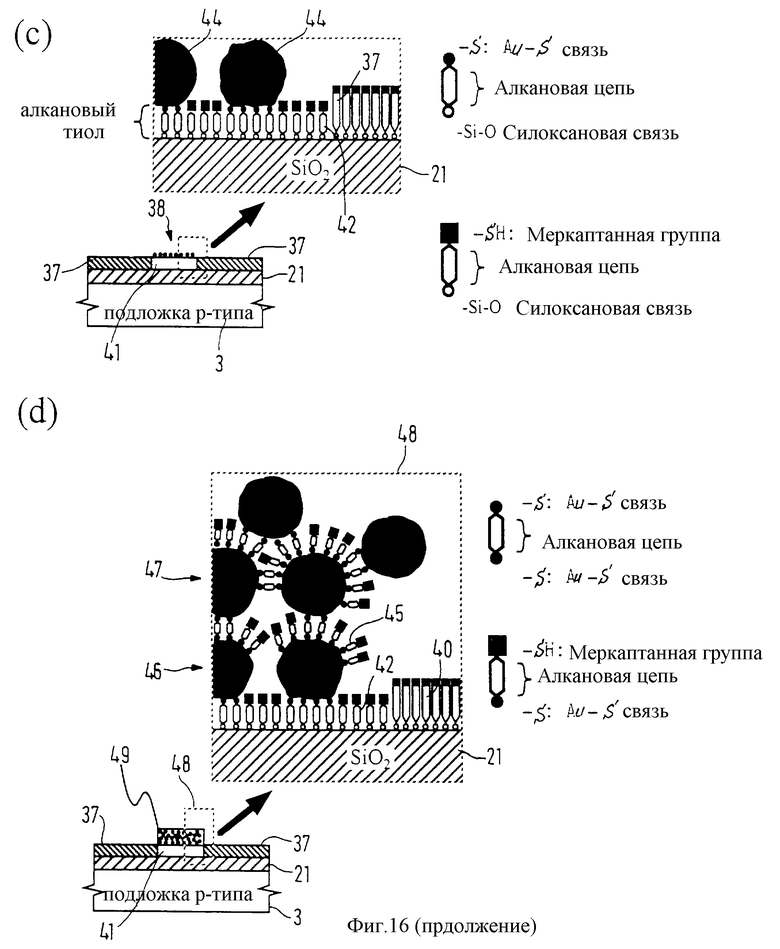

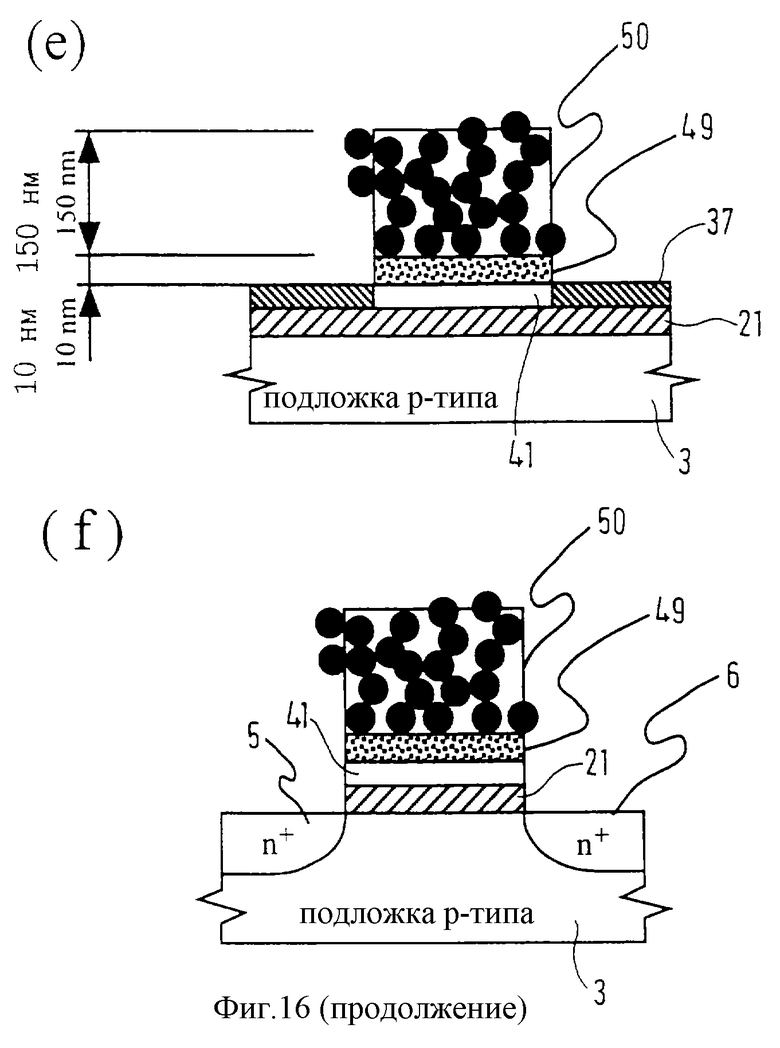

Фиг. 16а-16f иллюстрируют этапы процесса для образования альтернативного варианта осуществления, в котором барьерная структура включает золотые частицы нанометрического масштаба, осаждаемые из коллоидного раствора.

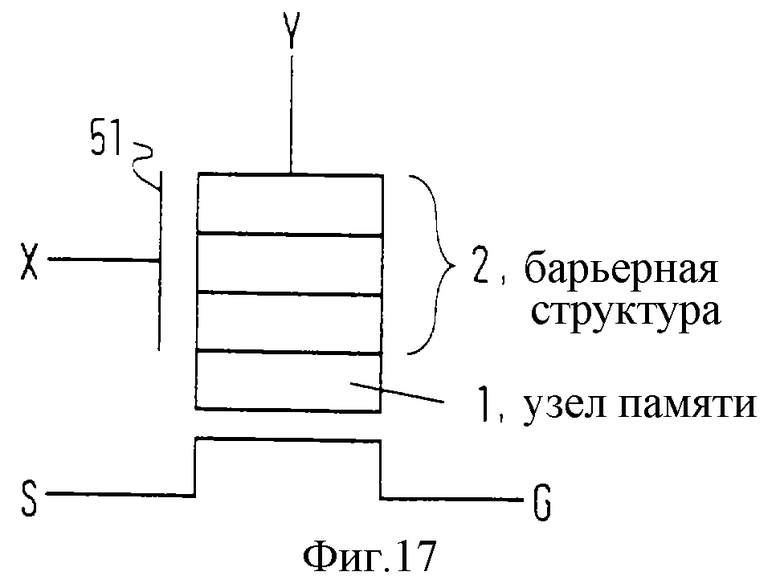

Фиг. 17 представляет схематическое изображение второго типа соответствующего изобретению запоминающего устройства.

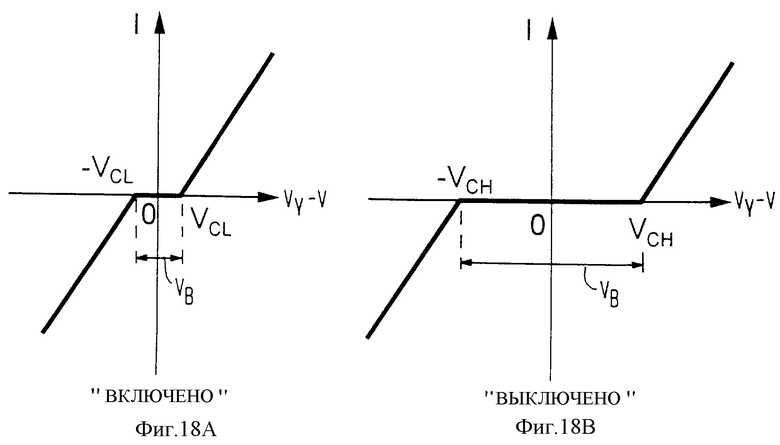

Фиг. 18а и 18b представляют графики тока I, протекающего через барьерную структуру 2 фиг. 17, в функции напряжения VY, прикладываемого к контакту Y при наличии (режим "включено") напряжения, приложенного к контакту X, и при отсутствии такого напряжения (режим "выключено").

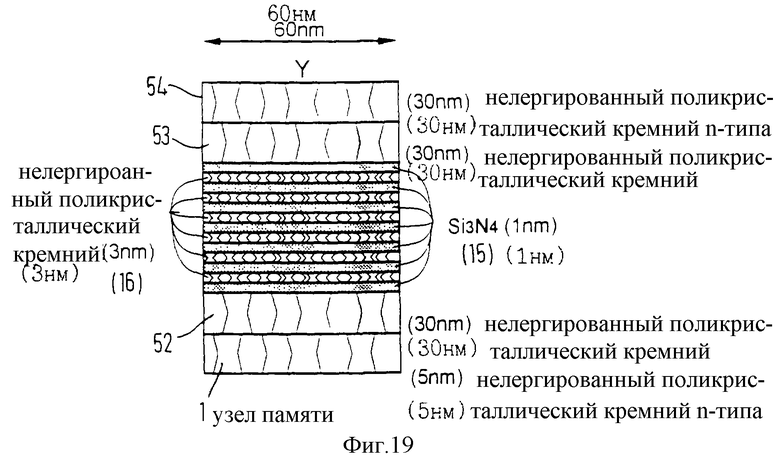

Фиг. 19 представляет увеличенное схематическое поперечное сечение показанной на фиг.17 барьерной структуры.

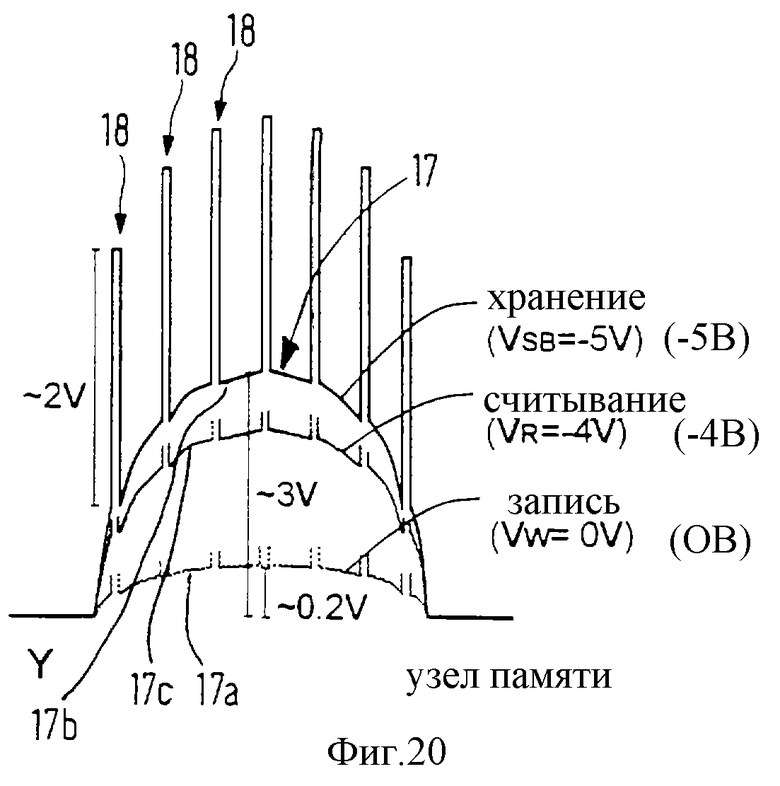

Фиг.20 представляет диаграмму энергий в зоне проводимости для показанной на фиг.19 барьерной структуры.

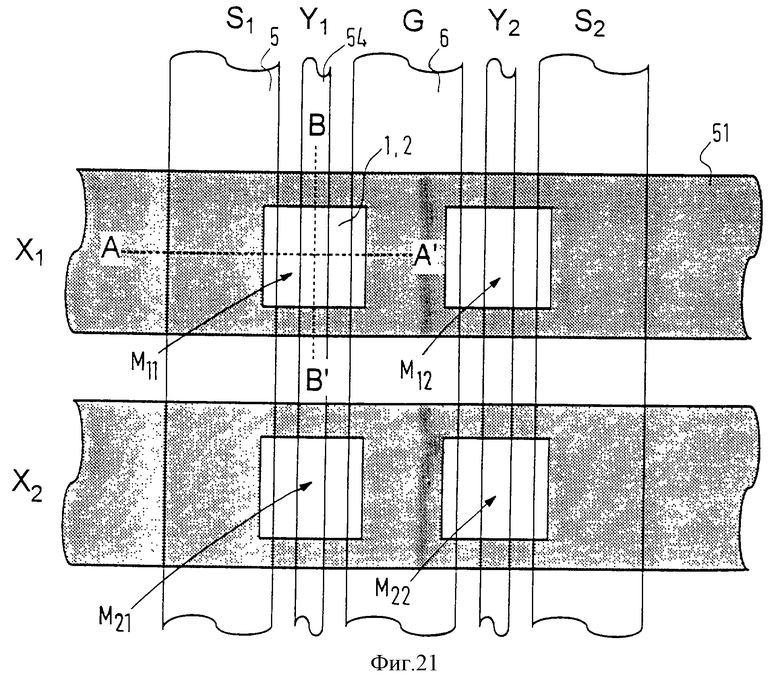

Фиг.21 представляет схематический вид сверху матрицы ячеек памяти, включающей запоминающие устройства показанного на фиг.17 второго типа.

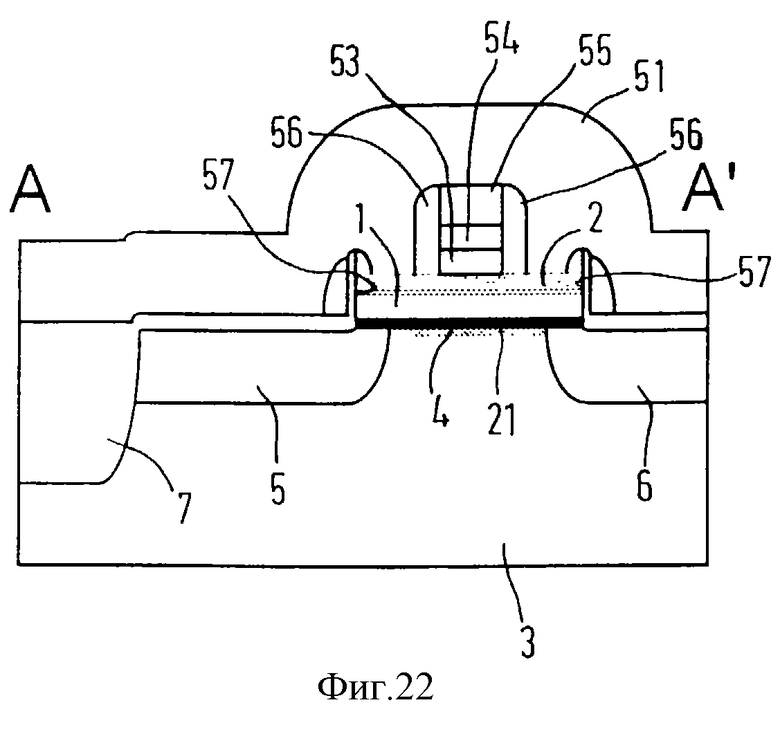

Фиг. 22 представляет вид в поперечном разрезе, взятый по линии А-А' фиг. 21.

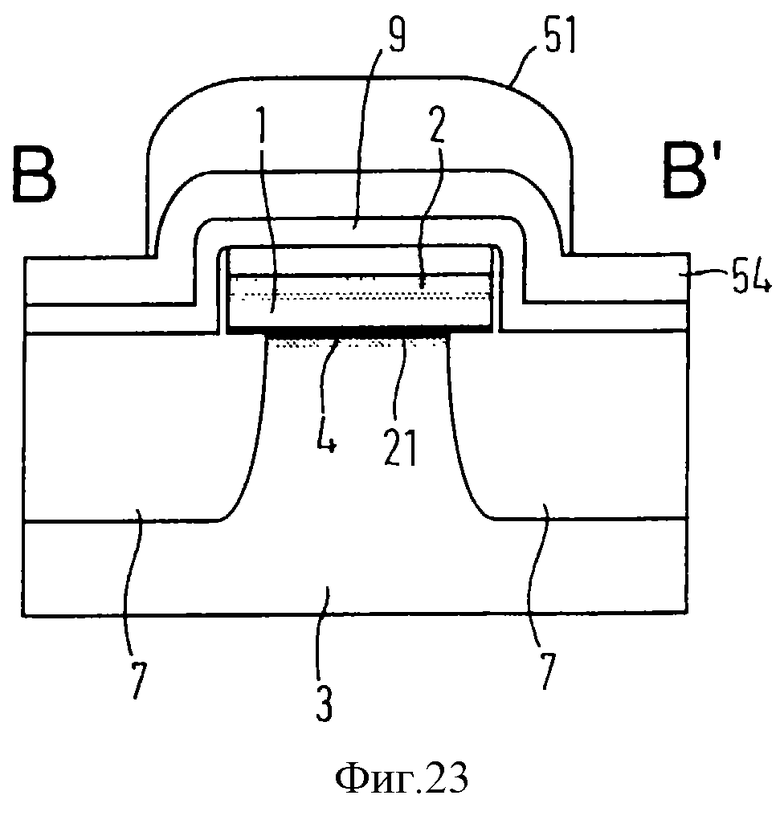

Фиг. 23 представляет вид в поперечном разрезе, взятый по линии В-В' фиг. 21.

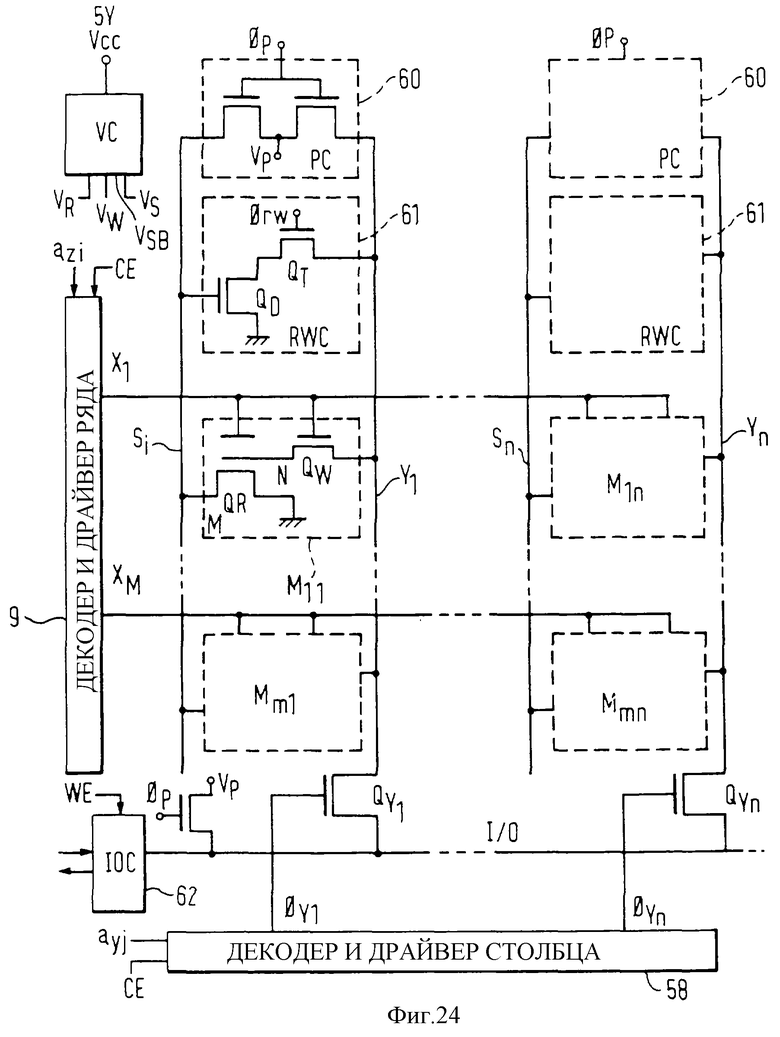

Фиг. 24 представляет электрическую принципиальную схему показанной на фиг. 21, 22 и 23 конфигурации ячейки памяти совместно со встроенными драйверами и другими периферийными устройствами.

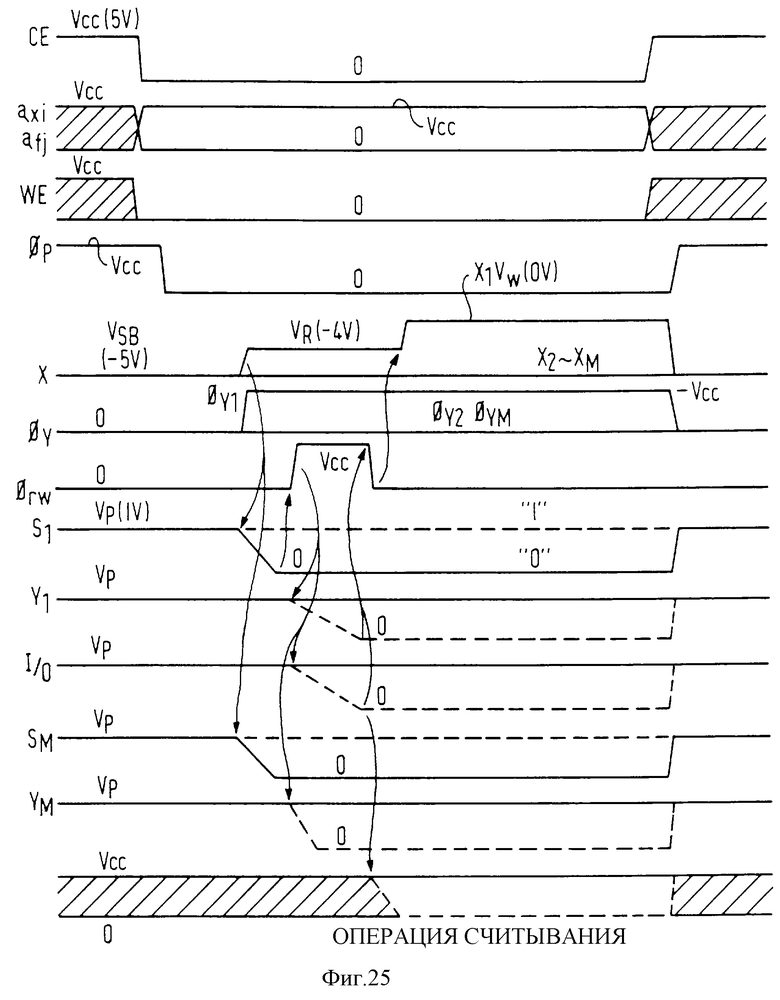

Фиг. 25 представляет диаграмму формы сигнала, иллюстрирующую процесс считывания информации из ячейки памяти M11.

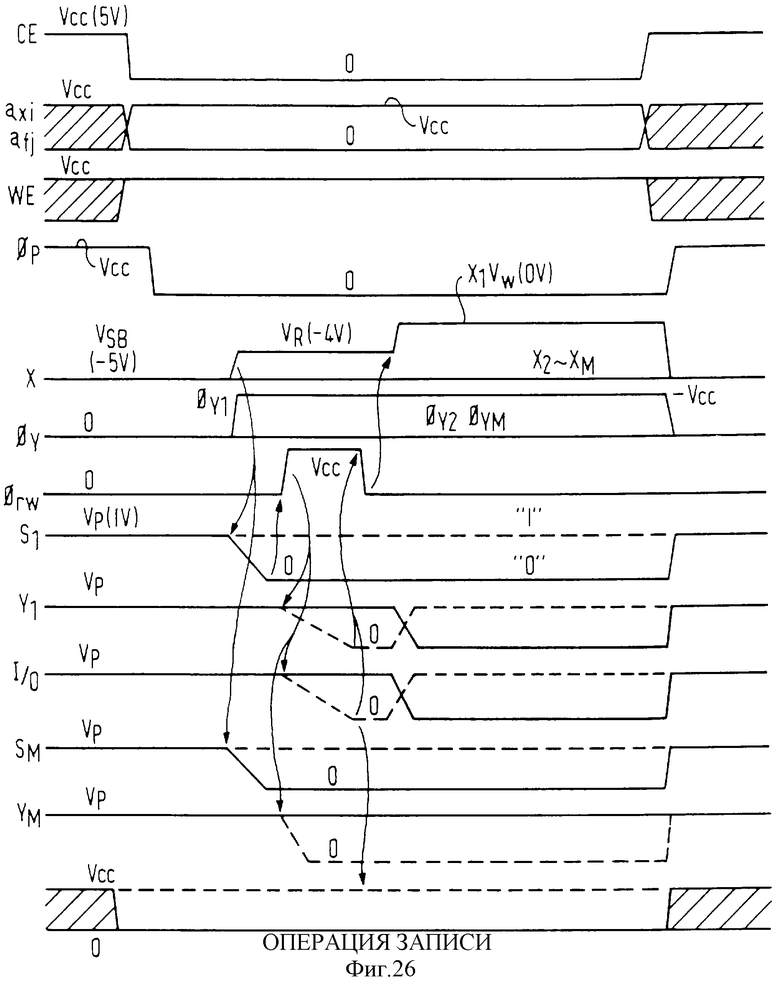

Фиг. 26 представляет диаграмму формы сигнала, иллюстрирующую процесс записи данных в ячейку памяти М11.

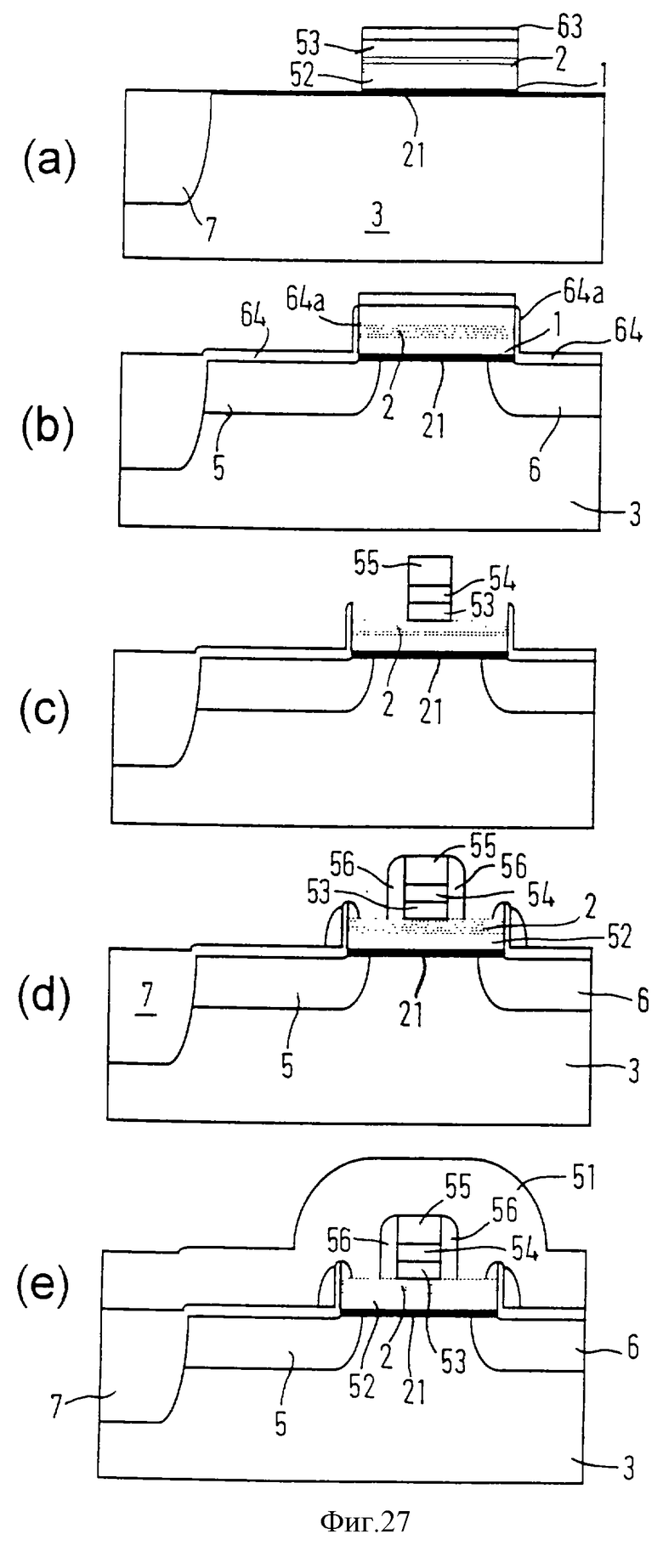

Фиг.27а-27е иллюстрируют этапы обработки для изготовления показанного на фиг.21-23 запоминающего устройства.

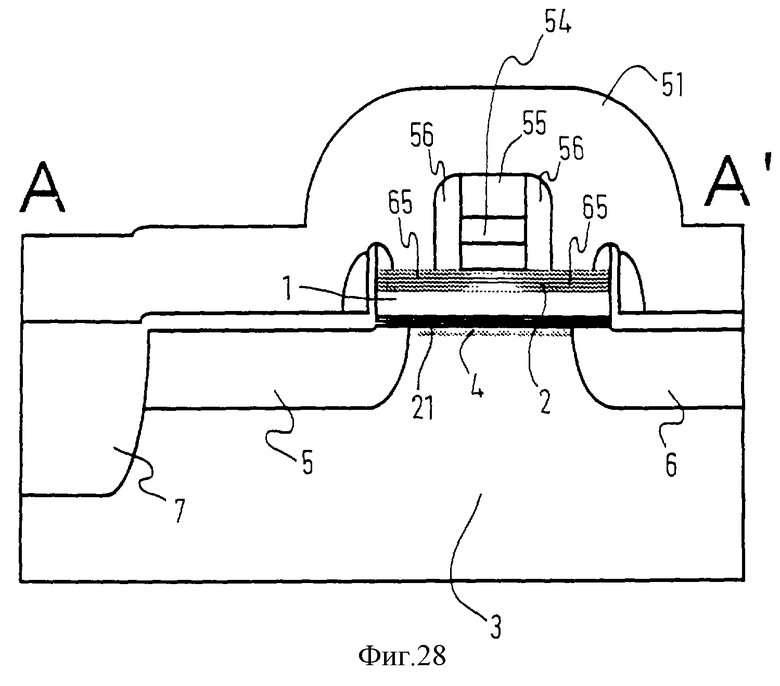

Фиг. 28 представляет схематический поперечный разрез модификации запоминающего устройства.

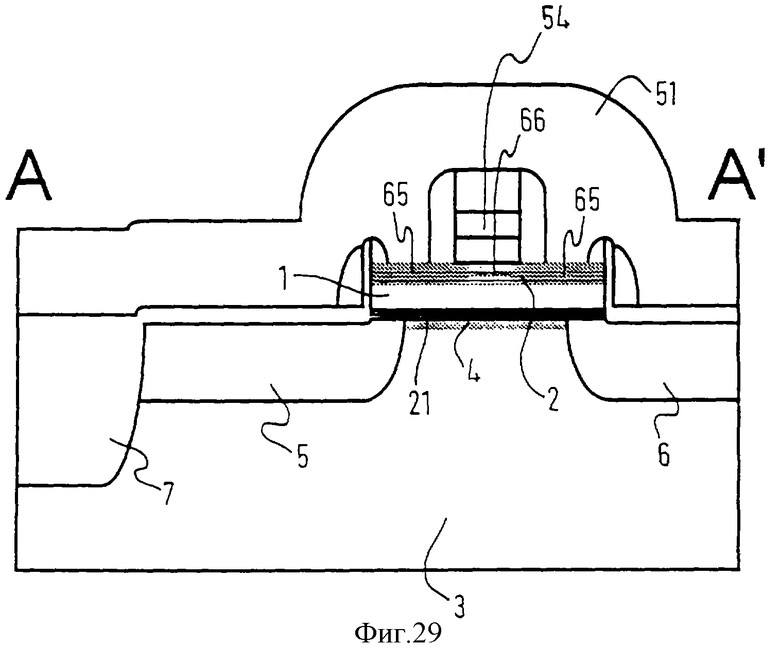

Фиг.29 представляет схематический поперечный разрез следующей модификации устройства.

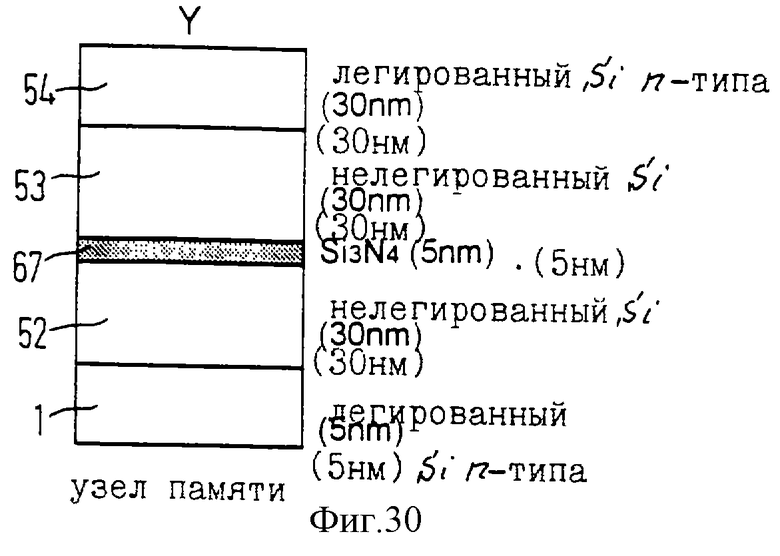

Фиг.30 представляет схематический поперечный разрез альтернативной барьерной структуры, предназначенной для использования во втором типе соответствующего изобретению запоминающего устройства.

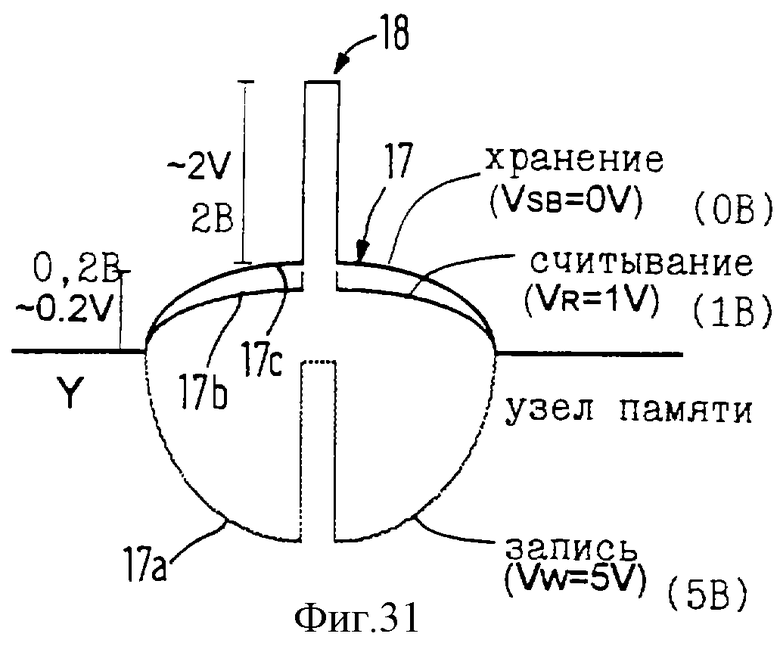

Фиг. 31 представляет диаграмму энергетической зоны проводимости, соответствующей показанной на фиг.30 барьерной структуре.

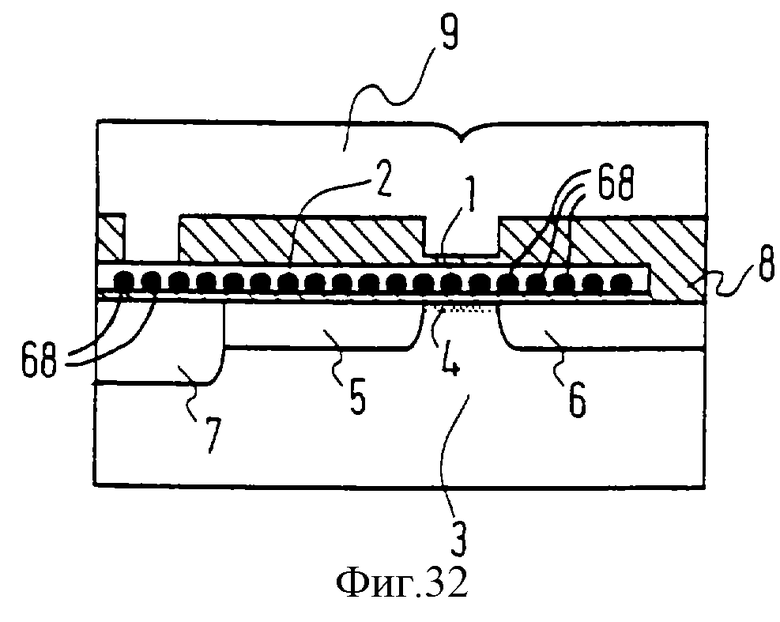

Фиг. 32 представляет схематический поперечный разрез третьего типа соответствующего изобретению запоминающего устройства.

Подробное описание изобретения

В последующем описании соответствующие изобретению варианты осуществления запоминающего устройства можно классифицировать по трем различным типам.

Тип 1

На фиг.1 показана общая конфигурация первого типа соответствующего изобретению запоминающего устройства. Узел памяти 1 и барьерная структура 2 объединены внутри управляющего электрода полевого транзистора, имеющего выводы истока и стока S, Y и вывод управляющего электрода X. Когда информация запоминается, носители заряда туннелируют через барьерную структуру 2 в узел памяти 1, и устройство действует как запоминающий конденсатор, так что заряд удерживается в узле 1. Для считывания информации проводимость канала исток-сток S, Y контролируется и изменяется между относительно высоким и относительно низким состояними проводимости в зависимости от уровня заряда, хранящегося в узле памяти 1.

На фиг. 2 показана вольт-амперная характеристика барьерной структуры 2, где V - напряжение узла памяти. Поток электронов I через барьерную структуру от вывода Х сильно подавляется в области блокирования VP, которая проходит между верхним и нижним пороговыми напряжениями ±VC. Однако вне этой области запирающего напряжения носители заряда могут туннелировать в узел памяти 1 или из него через барьерную структуру, в зависимости от полярности смещающего напряжения VX, прикладываемого к выводу X. Барьерную структуру можно рассматривать как многотуннельный переход, в котором два или больше туннельных перехода соединены последовательно.

Показанное на фиг.1 запоминающее устройство можно использовать в качестве ячейки памяти в матрице из таких устройств, расположенных в рядах и столбцах, как показано на фиг.3, со связанными с ними линиями слов X1, Х2 и т. д. и линиями двоичных разрядов S1, Y1, S2, Y2 и т.д. Таким образом, матрица включает в себя ячейки памяти Мmn, где m и n представляют номера рядов и столбцов, соответственно.

Первый вариант осуществления изобретения

Теперь рассмотрим структуру первого варианта осуществления ячейки памяти Мmn со ссылкой на фиг.4, 5 и 6, где фиг.4 представляет вид сверху матрицы ячеек, а фиг.5 и 6 являются поперечными разрезами, взятыми по линии А-А' и В-В' фиг.4, соответственно, ячейки М11.

Рассмотрим фиг.5, где устройство образовано в подложке 3, которая в данном примере содержит полупроводниковую подложку р-типа, в которой проводящий канал 4 проходит между истоком n+ и областями стока 5, 6. Электроизоляционная область SiO2 7 изолирует ячейку от следующей ячейки в матрице. Подложку закрывает электроизоляционный слой SiO2 8. Узел памяти 1 и закрывающая его конфигурация 2 туннельного перехода образованы в области, окруженной слоем 8. Проводящий управляющий электрод 9 накрывает конфигурацию 2 туннельного перехода. Управляющий электрод 9 образует линию слов Х1, которая проходит по ряду матрицы. Области истока и стока 5, 6 образуют линии двоичных разрядов S1, Y1, которые проходят по столбцу матрицы, показанной на фиг.4. Должно быть понятно, что другие ячейки в матрице имеют соответственные линии слов и двоичных разрядов.

Узел памяти 1 состоит из точечных элементов или гранул нанометрического масштаба, ограничивающих количество электронов, которые могут запоминаться путем зарядки через барьерную конфигурацию 2 так, чтобы обеспечить однородное поле в боковом направлении по узлу.

Теперь будет описан процесс избирательных записи и считывания данных для ячейки памяти М11 со ссылкой на фиг.7 и 8. В этом процессе линия слов X1 и линии двоичных разрядов S1, Y1, связанные с ячейкой памяти M11, активируются, а другие линии слов и двоичных разрядов заземляются. Когда информация записывается в М11, к линии слов Х1 подводится импульсная форма волны напряжения с положительным пиковым значением VX (W) и отрицательным значением - VX(W). Когда записывается "0", к линиям двоичных разрядов Y1 и S1 подводится положительный импульс напряжения с высотой VY W. С другой стороны, когда записывается "1", импульс напряжения с пиковым значением -VY (W) прикладывается к линиям двоичных разрядов Y1 и S1. Требование к этим импульсам таковы, что они должны перекрываться в течение времени Т. В этом примере VX (W)=1,2 В, VY (W)=1,8 В, а Т=10 нс.

Рассмотрим фиг.8, где количество электронов, которые могут находиться в узле памяти 1, ограничивается протяженностью области блокирования и напряжения конфигурации туннельного перехода 2. Таким образом, напряжение в узле не может превышать ±VC. На фиг.8(а) бит "1" двоичных данных отображается положительно заряженным состоянием 11 (недостаток электронов) в узле памяти 1, тогда как "0" отображается отрицательно заряженным состоянием 12 (избыток электронов) в узле памяти 1. В этом примере напряжения узла памяти в состояниях "1" и "0" составляет +0,4 В и -0,4 В, соответственно. Теперь будет описан процесс записи "0" в узле 1 со ссылкой на фиг.8(е)-8(d), где VSY=VS= VY, a черные точки отображают окончательное электронное состояние, которое возникает на каждом этапе. Как показано на фиг.8(а), положительное напряжение VY (W) (1,8 В) прикладывается к линиям двоичных разрядов S1 и Y1, два состояния 11 и 12 перемещаются в точку 13 (1,6 В) и точку 14 (0,8 В), соответственно, по линии постоянного количества электронов в узле памяти, то есть

V = (Cg/CΣ)VSY+VO, (1)

где CΣ представляет общую емкость узла памяти, Сg представляет емкость между узлом памяти и клеммам Y1 и S1, а VO - напряжение узла памяти, когда VSY = O(-CΣVO/q представляет количество избыточных электронов в узле памяти, где q - элементарный заряд). В настоящем варианте осуществления CΣ/Cg = 1,5.

Когда отрицательное напряжение - VX (W)(-1,2 В) прикладывается к линии слов Х1, как показано на фиг.12b, область блокирования VB смещается, как показано, состояние 13 переходит в состояние 14, поскольку состояние 13 находится вне области блокирования и не может здесь существовать.

Когда положительное напряжение VX (W) (1,2 В) прикладывается к линии слов X1, как показано на фиг.12с, это состояние сохраняется. Затем линия слов и линии двоичных разрядов заземляются, как показано на фиг.12d, а состояние 14 переходит в "0" состояние 12 по линии постоянного количества электронов в узле памяти 1.

Следует отметить, что любое состояние электронов между состояниями "0" и "1" 11, 12 обновляется с помощью процесса для установления состояния "0". Соответственный процесс для записи состояния "1" 11 показан на фиг.8е-8h. В этой последовательности любое состояние между состояниями "0" и "1" изменяется на обновление состояния "1".

Можно заметить, что процесс записи требует одновременной подачи форм сигналов записи на линии двоичных разрядов и линию слов, связанные с конкретной ячейкой памяти. Таким образом, можно индивидуально адресовать ячейки памяти. Во время процесса записи область блокирования смещается последовательно вверх и вниз таким образом, чтобы принудить состояния электронов в узле селективно принимать значение либо "1", либо "0". Однако, если сигнал записи прикладывается к линии слов X1, но не к линиям двоичных разрядов Y1 и S1, или сигналы записи прикладываются к линиям двоичных разрядов, но не к линии слов, запись произведена не будет, и в узле 1 сохранится существующее состояние.

Для считывания хранящейся информации положительное напряжение затвора VX (r) прикладывается к линии слов Х1 и определяется ток ISY между S1 и Y1. Как показано на фиг.9, пороговое напряжение транзистора задается напряжением VT, когда узел памяти 1 заряжен отрицательно ("0"), и величиной Vt-ΔVT, тогда узел памяти заряжен положительно ("1"). Эти пороговые напряжения VT и VT-ΔVT положительные, так что в невыбранных ячейках памяти электрический ток между S и Y не течет (VX=0). Напряжение затвора VX (r) нa выбранной линии слов выбирается между VT-ΔVT и ΔVT. Таким образом, ISY>0 для "1" и ISY=0 для "0". Таким образом, можно использовать детектор тока (не показанный) для обнаружения тока, текущего между линиями двоичных разрядов Y1 и S1 (и другими соответственными частями линий двоичных разрядов в матрице), когда напряжение затвора VX (r) прикладывается к линии слов Х1. Для того чтобы считывать данные из всей матрицы памяти, процесс последовательно повторяется для других линий слой Х матрицы. В настоящем варианте осуществления изобретения, V(r)X=0,8 В, VT-ΔVT=0,4 В и VT=1,2 В. В соответствии с изобретением, конфигурация туннельного перехода 2 увеличивает время хранения и улучшает характеристику считывания-записи. Время хранения узла 1 определяется способностью конфигурации туннельного перехода 2 подавлять течение электронов в блокированной области VB показанной на фиг.2 вольт-амперной характеристики. Время хранения tS приблизительно задается с помощью выражения

tS=tWexp(-qVC/kT), (2)

где k - постоянная Больцмана, Т - абсолютная температура, q - элементарный заряд, a tW - время записи. Желательно, чтобы обеспечить, например, время хранения tS, равное десяти лет, и tW, равное 10 нс, напряжение VC должно быть больше 1 В для работы при комнатных температурах. Если бы необходимо было использовать эффект от заряда одного электрона, то потребовало бы образования барьерной структуры 2 из металлических частиц размером менее 1 нм, чего нельзя легко добиться с помощью существующих в настоящее время технологий изготовления.

В способе, с помощью которого можно достичь повышенного запирающего напряжения VC, используется эффект искривления энергетической зоны для барьерной конфигурации 2 заряда, который описан непосредственно в связи с многотуннельным переходом в работе К. Наказато и Х. Ахмеда, "Журнал прикладной физики", 5 июня 1995 г., том 66, 23, стр.3170-3172. Характеристики, необходимые для туннельного перехода для циклов хранения и записи, можно рассматривать отдельно. Для цикла хранения высоту и ширину туннельного перехода можно обозначить символами фS и dS, соответственно, а для цикла записи фW и dW. Для сохранения запомненной информации в течение более 20 лет высота барьера фS должна быть больше 1,8 эВ для подавления термически активируемого тока эмиссии Пула-Френкеля, а толщина туннельного перехода dS должна быть толще 8 нм•{фS(эВ)}-1/2 для управления туннельным током утечки. Однако для получения небольшого времени записи, примерно 10 нс, ширина dW туннельного перехода должна быть меньше, чем 2 нм • {фW(эВ)}-1/2, где фw является высотой барьера для цикла записи.

Барьерная конфигурация 2, которая может удовлетворить этим критериям, показана на фиг. 10 и содержит многотуннельный переход, состоящий из слоев 15, 16 электроизоляционного и неэлектроизоляционного материала, соответственно. В этом примере электроизоляционные слои 15 содержат 1-3 нм толщины Si3N4, а неэлектроизоляционные слои 16 содержат поликристаллический кремний толщиной 3-10 нм.

Полученная в результате диаграмма энергетической зоны проводимости для показанной на фиг.10 барьерной конфигурации 2 иллюстрируется на фиг.11 и содержит первый относительно широкий барьерный компонент 17, с шириной BW1, соответствующей объединенной ширине всех слоев 15, 16, которые составляют барьерную конфигурацию 2. Кроме того, каждый из электроизоляционных слоев 15 дает повышение сравнительно узкой барьерной компоненты 18а, 18b и т.д., каждый из которых имеет ширину ВW2, разнесенных друг от друга посредством запирающих областей, которые в данном случае образованы из слоев 16 из поликристаллического кремния. Относительно широкий барьерный компонент 17 имеет относительно низкую барьерную высоту Bh1, в то время как барьерные компоненты 18а, 18b и т.д. обеспечивают значительно более высокие барьеры Вh2а, Bh2b.

Два компонента 17, 18 барьера выполняют разные роли. Узкие и высокие барьерные компоненты 18 действуют как туннельные переходы, которые сдерживают эффект объединенного туннелирования, а именно, спонтанное туннелирование через два или более туннельных перехода за счет механического эффекта квантования, так что электроны перемещаются только через один барьер 18 одновременно и остаются в течение некоторого периода времени в области между ними. Во время нахождения в этой области электроны неупруго рассеиваются по направлению к локальному состоянию равновесия, регулируемому энергией широкого барьерного компонента 17. Таким образом, на перенос электронов оказывает сильное воздействие широкий барьерный компонент 17. Ширину и высоту высоких, узких барьерных компонентов 18 нельзя изменять с помощью внешних смещений, поскольку они определяются материалами, образующими барьерную конфигурацию 2. Однако компонент широкого, низкого барьера 17 можно модулировать с помощью внешних смещений.

На фиг.11а показана диаграмма зоны при отсутствии прикладываемого напряжения VX. Можно заметить, что когда к управляющему электроду 9 не прикладывается напряжение, электрон 20 в узле 1 хранения заряда вынужден туннелировать через всю ширину относительно широкого барьерного компонента 17, если имеется утечка из узла 1, в результате чего утечка заряда сильно подавляется. Однако, когда к электроду 9 прикладывается напряжение, диаграмма энергетической зоны проводимости для барьера 2 изменяется до конфигурации, показанной на фиг.11b, из которой можно заметить, что приложенное напряжение заставляет относительно широкий барьерный компонент 17 образовывать идущий вниз уклон по направлению к узлу 1 хранения заряда, в результате чего электрон 20 вынужден туннелировать только через относительно узкие барьерные компоненты 18 для того, чтобы достичь узла хранения. Таким образом, барьерная конфигурация обеспечивает относительно широкий барьерный компонент 17 для долговременного хранения электронов в узле 1, не требуя приложения крайне высоких напряжений к электроду 9 для того, чтобы заставить электроны туннелировать в узел 1 во время процесса записи.

В слоях 16 гранулы поликристаллического кремния имеют диаметр, у которых почти такой же размер, как толщина. Размер гранул в узле памяти 1 может быть больше, чем размер слоев 16, в результате чего электроны могут устойчиво храниться в узле памяти 1 с целью обеспечения надежного функционирования. В устройстве на фиг.10 узел памяти 1 имеет толщину 5-30 нм и образован из поликристаллического кремния. В модификации узел 1 можно легировать для улучшения стабильности состояний электронов в узле. Из вышеизложенного видно, что при запоминании информации слои 17 поликристаллического кремния образуют области перехода и таким образом увеличивают dS, тогда как в процессе записи слои 16 не действуют в качестве барьера, а вместо этого устройство обеспечивает градиент потенциала, который ускоряет электроны от электрода 9 по направлению к узлу 1, что способствует быстрой записи электронов в узел.

Теперь будет описан более подробно пример изготовления устройства со ссылкой на фиг.12. Для подложки 3 используется пластинка из кремния р-типа с удельным сопротивлением 10 Ом-см. Сначала образуют электроизоляционный слой 7 из непроводящего SiO2 толщиной 500 нм. После образования электроизоляционного слоя 7, с помощью термического окисления на верхнюю часть кремниевой подложки 3 р-типа наращивают оксидную пленку затвора 21 толщиной 10 нм. Затем наносят слой, который предназначен для образования узла памяти 1. Слой 1 содержит Si n-типа, нанесенный толщиной 10 нм, имеющий поверхность, преобразованную в нитрид кремния в атмосфере NH3 при температуре 900oС. Толщина получающегося в результате нитрида кремния самоограничивается 2 нм. Это соответствует показанному на фиг.10 слою нитрида 15а. После этого наносят слой нелегированного кремния толщиной 5 нм так, чтобы образовать покрывающий слой 16а (фиг. 10), который затем подвергают азотированию для образования следующего слоя 15b нитрида кремния 2 нм толщины. Для построения барьерной структуры 2 процесс повторяют несколько раз.

Затем на слой барьерной структуры 2 наносят пленку 22 легированного кремния n-типа толщиной 20 нм. На пленку 22 наносят пленку 23 из SiQ2 толщиной 20 нм методом химического осаждения в паровой фазе (ХОПФ).

Различные слои кремниевой пленки наносят в аморфном состоянии, но они преобразуются в поликристаллический кремний во время азотирования и процесса загустения при ХОПФ осаждаемого слоя 23 SiO2, затем верхнюю часть пленки 23 SiO2 структурируют с помощью обычных методов литографии и реактивного ионного травления в атмосфере CHF3 и газообразного аргона.

Затем, используя структурированный слой 23 SiO2 в качестве маски, слои 22, 2 и 1 поликристаллического кремния и нитрида кремния протравливают с помощью реактивного ионного травления, используя CF4 для образования конфигурации затвора 24, как показано на фиг.12b. Конфигурация затвора 24 обычно имеет длину 1, равную 0,15 мкм.

После этого пластинку оксидируют для образования наружного слоя 25 толщиной 30 нм термического SiO2, как показано на фиг.12с. Затем с помощью ионной имплантации ионами мышьяка формируются области истока и стока 5, 6.

Затем, как показано на фиг.12d, наносят 100 нм на пленку 26 SiO2, которую закрывают слоем оптического фоторезиста 27, наносимого достаточной толщиной для получения плоской верхней поверхности, в данном примере толщиной 1500 нм. Затем фоторезист 27 опять вытравливают до тех пор, пока верхняя часть слоя 26 SiO2 не выступит сквозь поверхность. Травление выполняют методом распыления в атмосфере O2. Полученная в результате конфигурация показана на фиг.12е.

Верхнюю часть 26а пленки 26 SiO2 удаляют с помощью реактивного ионного травления в атмосфере газа WF6 до тех пор, пока не покажется верхняя часть пленки 22 поликристаллического кремния, как показано на фиг.12f.

После удаления оптического фоторезиста 27 на полученную в результате поверхность наносят металл и структурируют с помощью обычных литографических приемов для обеспечения управляющего электрода 9, который образует описанные выше линии слов X1.

Должно быть ясно, что запоминающее устройство можно модифицировать различными способами. Например, толщина электропроводных слоев 15 может отличаться от описанного значения 5 нм и, в общем, может быть удовлетворительной толщина в 10 нм или меньше. Толщину электроизоляционных слоев 16 можно изменять от описанного выше значения в 2 нм так, чтобы находиться в диапазоне 3 нм или меньше, чтобы образовывать удовлетворительные узкие высокие барьерные компоненты 18, хотя описанный процесс изготовления дает в результате правильное управление толщиной каждого слоя 16 так, что она становится порядка 2 нм. Кроме того, количество наборов слоев 15, 16 может отличаться от описанного в примере семь до достаточных количеств для образования удовлетворительно широкого, узкого барьерного компонента 17 поперек барьерной конфигурации 2.

Второй вариант осуществления изобретения

В модификации, показанной на фиг.10, барьерную конфигурацию 2 можно заменить конфигурацией барьера Шотки, как показано на фиг.13. В этом случае вместо использования электроизоляционных слоев 15 нитрида кремния используют металлические слои 28 таким образом, чтобы обеспечить множественную конфигурацию диодов Шотки, перекрывающих друг друга. Металлические слои 28 можно делать из W, или они могут содержать пленки из силицида, типа CoSi2, образованные между пленками 16 из нелегированного поликристаллического кремния.

Теперь будут описаны следующие соответствующие изобретению варианты осуществления запоминающего устройства, в котором конфигурация 2 туннельного перехода состоит из островков нанометрического масштаба, распределенных в кристаллической решетке из электроизоляционного материала. В последующих примерах островки нано-масштаба имеют диаметр 5 нм или меньше и разделены электроизоляционным материалом с толщиной нанометрического масштаба в кристаллической решетке, например, размером 3 нм или меньше, что дает повышение узким, высоким барьерным компонентам конфигурации туннельного перехода. Узел хранения заряда можно образовывать с помощью проводящих островков так, чтобы они были распределены по барьерной конфигурации, а не образовали отдельный слой 1, как описывалось прежде. Для обеспечения получающейся в результате конфигурации многотуннельного перехода можно использовать несколько различных процессов изготовления, как теперь будет описано.

Третий вариант осуществления изобретения

Фиг. 14 иллюстрирует схематическое поперечное сечение другого соответствующего изобретению варианта осуществления запоминающего устройства. В этом варианте осуществления узел памяти 1 и барьерная структура 2 реализованы путем объединения кристаллов нанометрического масштаба, которые распределены в окружающей их кристаллической решетке SiO2. Рассмотрим фиг.14, на которой подложка 3 обеспечена областями истока и стока 5, 6 с каналом 4 между ними. Оксидный слой затвора 29 покрывает канал 4 и имеет толщину 5 нм, образован с помощью процесса термического оксидирования на подложке. После этого наносят слой кремния толщиной 6 нм с помощью электронно-лучевого парообразования или ХОПФ, который затем подвергают быстрому термическому оксидированию и кристаллизации. Этот процесс описан в работе Е.Х. Николиана и Р. Цу, "Журнал прикладной физики", том 74, 1993 г., стр. 4020-4025, и М. Фукуда, К. Накагава, С. Миязаки и М. Хироуза, "Обширные рефераты" (Extended abstrakts) Международной конференции по твердотельным устройствам и материалам, 1996 г., Иокогама, 1996 г. , стр. 175-178. Это образует островки в форме нанокристаллов Si со средним диаметром 3 нм, расположенные в слое 30 с оксидным слоем туннелирования 31 толщиной 2 нм, покрывающим слой 30. Собственная емкость 3 нм кристаллов Si дает энергию зарядки порядка 100 мэВ, которая достаточна для ограничения с помощью блокады Кулона количества электронов внутри каждого нанокристалла, при комнатной температуре. Нанесение слоя 29 с последующим быстрым термическим оксидированием и процессом кристаллизации повторяют несколько раз для построения составного слоя достаточной толщины. В данном варианте осуществления процесс повторялся пять раз для обеспечения толщины объединенного слоя 20 нм, содержащего пять слоев нанокристалла 30 внутри этой толщины. После этого на верхней поверхности образуется контактный слой кремния n-типа 32. Должно быть ясно, что полученную в результате структуру затвора можно включать в описанный выше процесс изготовления запоминающего устройства со ссылкой на фиг.12. Однако должно быть понятно, что узел памяти 1 больше не обеспечивается в качестве отдельного слоя, а вместо этого образуемые в каждом слое 30 нанокристаллы обеспечивают местоположения для хранения электронов, распределенные в электроизоляционных оксидных слоях 29, 31.

Четвертый вариант осуществления изобретения

Фиг. 15 иллюстрирует этапы процесса для образования другого варианта осуществления запоминающего устройства. В этом варианте осуществления объединение кремниевых нанокристаллов и окружающих слоев SiO2 образовано посредством использования пористых пленок Si. Рассмотрим фиг.15а, где пористая пленка Si 33 толщиной 20 нм образована с помощью анодирования Si р-типа. Анодирование выполняется в 25% водном растворе фтористоводородной кислоты, разведенной этанолом с постоянным анодным током 10 мА/см2 в течение 5 с. В результате образуется составная пленка, содержащая 4~5 нм нанокристаллического Si, внедренного в кристаллическую решетку SiO2. Этот способ известен сам по себе и описывается более подробно в работе Я. Канемицу и др. "Физический обзор" (Phys. Rev.), том В48, 1993 г., стр.2827.

Затем пористая кремниевая пленка 33 термически оксидируется для образования оксидной пленки затвора 34 толщиной 5 нм вместе с верхним оксидным слоем 35 толщиной порядка 7 нм, как показано на фиг.15b. Этот процесс, кроме того, приводит к отжигу, который сокращает диаметр каждого

нанокристалла в пористой Si пленке, а также толщину самого пористого слоя 33. После процесса отжига пористый слой Si 33 имеет толщину 14~16 нм, а средний диаметр частиц уменьшается примерно до 3 нм. Соответствующая энергия заряда для частиц нанокристаллического кремния равна порядка 100 мэВ, которая, как объяснялось выше, приводит к ограничению количества электронов, которые могут проникнуть в узел, из-за блокады Кулона. Полученная в результате пленка обозначена позицией 36 на фиг.15b и содержит приблизительно 3-4 нанокристаллические частицы по своей толщине, благодаря чему обеспечивает многотуннельный переход (МТП) при рассмотрении перемещения электронов вертикально через слой.

После этого верхний оксидный слой 35 удаляют и наносят затвор 32 из материала поликристаллического кремния, как описывалось выше. Используя затвор 32 из поликристаллического кремния в качестве маски, составную пленку 36 и лежащий под ней оксид затвора 34 удаляют с помощью обычных технических приемов травления и затем имплантируют области истока и стока 5, 6 описанным выше со ссылкой на фиг.12 способом. Этот способ изготовления имеет преимущество по сравнению с описанным со ссылкой на фиг.14 способом, заключающееся в том, что многотуннельный переход образуют с помощью одного процесса анодирования, снижая количество нанесения Si и необходимые этапы оксидирования.

Пятый вариант осуществления изобретения

Составные материалы нанокристаллов и окружающей кристаллической решетки можно делать другими способами, используя различные материалы. Один пример описан в работе Е. Бар-Садехом и др. "Физический обзор", том В50, 12, 1994 г. , стр.8961-8964. В этом способе слой частиц Аu в кристаллической решетке Аl2О3 можно использовать для замены показанного на фиг.15 пористого кремниевого слоя. Составную пленку 30 нм толщины из Аu и Al2O3 можно делать с помощью совместного напыления золота и алюминия на слой окиси кремния толщиной 5 нм, который образован с помощью термического оксидирования подложки 3. Последующее изготовление устройства такое же, как в четвертом варианте осуществления изобретения. Условия напыления для изготовления составной пленки выбирают так, чтобы реализовать объемное содержание золота, равное 0,4. В этих условиях образуются изолированные частицы Аu в составной пленке, имеющие диаметр порядка 3~5 нм. Следовательно, 30 нм пленка содержит 5~10 частиц Аu по ее толщине, образующих вертикальный МТП. Должно быть ясно, что это можно использовать в качестве подложки для пористого кремниевого слоя, описанного со ссылкой на фиг.15.

С помощью этого способа совместного напыления можно образовывать составные пленки из других благородных металлов, типа Ag, Pt, с какой-нибудь другой кристаллической решеткой из окиси металла, типа SiO2 или Сr2О3.

Составную пленку оксидной кристаллической решетки с металлическими островками также можно образовывать путем термического разложения исходных металлических окислов. Например, окись золота, являющаяся исходным металлическим окислом, может быть образована с помощью реактивного распыления мишени из сплава Au - Si в кислородной плазме, как описано в работе Л. Майя и др. в "J. Vac. Sci. Tectnol." (Журнал вакуумной научной технологии), том В14, 1996 г., стр.15-21.

Шестой вариант осуществления изобретения

На фиг.16 показан способ образования составных нанокристаллов и изоляционных туннельных переходов с помощью способа химического осаждения из коллоидного раствора. Рассмотрим фиг.16а, где оксидный слой 21 толщиной 5 нм образован с помощью процесса термического оксидирования на подложке 3 из Si р-типа. Затем на поверхности слоя 21 из SiO2 производится мономолекулярный слой 37 из октадецил-трихлоросилана (ОТС). Как описывается более подробно в работе М.Дж. Лерсела и др., "J. Vac. Sci. Technol." (Журнал вакуумной научной технологии), том В11, 1993 г., стр.2823-2828. Более подробно, подложку 3 со слоем 21 из SiО2 погружали в раствор 1 миллиграмм-молекулы гексадекана ОТС более чем на 12 часов. В результате получили спонтанное образование мономолекулярного слоя ОТС 37. Молекулы ОТС можно удалить с поверхности SiO2 21 с помощью облучения электронным лучом мощностью 60 кВ. Таким образом, изображения окон в ОТС образуются на мономолекулярном слое 37 с помощью обычной электронно-лучевой литографии. После образования окна в ОТС, подложку погружали в 1% водный раствор фтористоводородной кислоты на 30 с, вымывая остатки облученного электронным лучом ОТС, оставляя окно 38. Краевая область окна показана в увеличенном виде внутри пунктирного контура 39. Показан пример молекулы ОТС 40. Она состоит из цепи алканов, имеющей силоксанную связь на одном конце и метиловую группу на другом. Как показано на увеличенной площадке 39, молекулы 40 образуют силоксановую связь со слоем SiO2 21 и образуют плотно упакованную ковалентно связанную сетку. Метиловая группа на верхнем конце является по существу инертной и, следовательно, очень устойчивой к химическому агрессивному воздействию во время обработки подложки.

Затем подложку со структурированным мономолекулярным слоем ОТС 37 поместили в разбавленный (0,05%) безводный раствор толуола (3-Меркаптопропил) триметоксисилана в условиях фракционирования с дефлегмацией (то есть нагревания приблизительно до 100oС) в течение десяти минут. Потом подложку поместили в печь при температуре 105oС на 30 минут для отверждения силоксанных связей. Результат показан на фиг.16b. Эта процедура создает мономолекулярный слой тиола алканов 41 на слое SiO2 21 в области окна 38. Структура отдельных молекул 42, которые образуют мономолекулярный слой тиола алканов, состоит из силоксанной связи на одном конце алкановой цепи с меркаптанной группой на другом. Этот процесс описан более подробно в работе А. Дорона и др., "Langmuir", том 11, 1995 г., стр.1313-1317. Молекулы ОТС вне области окна 38 остаются не затронутыми. Расположение на одной прямой молекул 37, 42 можно видеть более ясно на увеличенном виде края окна, изображенного внутри пунктирной линии 43. В принципе, эту модификацию поверхности можно выполнить с другими алкановыми тиолами, оканчивающимися на одном конце алкоксисиланом ((СН3О)3Si- или (С2H5О)3-Si-).

Затем подложку погружают в коллоидный раствор золота по меньшей мере на пять часов при комнатной температуре, в результате чего в области окна 38 оказывается прикрепленным мономолекулярный слой коллоидальных золотых частиц 44. Это происходит только в области окна, где поверхность оканчивается меркаптанными группами (-SH), из-за сильного сродства серы с золотом. Средний размер золотых коллоидных частиц составляет 2 нм.

Известно, что коллоидальные частицы золота могут быть приготовлены химическим путем и иметь средние диаметры в диапазоне 2~5 нм с хорошо определенным распределением по размеру, обычно со стандартным отклонением 10%. Такие наночастицы оседают на поверхности, оканчиваемой меркаптанными группами, образуя ковалентные связи между атомом серы в подложке и атомом золота в поверхности золотых коллоидных частиц. Осаждение частиц автоматически прекращается, когда слой приближается к мономолекулярному слою, поскольку электростатические силы, обусловленные поверхностным зарядом золотых частиц, которые обеспечены ионизацией адсорбируемых веществ на золотых коллоидных частицах, предотвращают осаждение других коллоидных частиц на верхней части поверхности подложки или очень близко к уже осажденным там частицам. В отношении более подробного описания мы ссылаемся на наш патент ЕР 96300779.4, зарегистрированный 6 февраля 1996 г. Коллоидальные суспензии таких частиц с заранее определенными средними размерами частиц и распределениями диапазонов диаметров можно приобрести на рынке, у фирмы Нанопробс Инк. (Nanoprobes Inc. ), 25E Луп Роад Сти 124, Стоуни Брук (Stony Brook), Нью-Йорк 11790-3350, США. Частицы подаются в водной суспензии. Адсорбированные ионы цитрата сообщают отрицательный заряд частицам Аu.

Затем подложку погружают в 5 миллиграмм-молекулярный этаноловый раствор дитиола (а именно, 1,6-гександитиол) после описанного выше осаждения золотых частиц из коллоидного раствора. Один из двух атомов серы в дитиоле образует связи Au- S с золотой коллоидной поверхностью, замещая поверхностные адсорбируемые вещества золотых частиц дитиолами, тогда как другой конец атома серы в дитиоле ориентирован от золотой поверхности в форме свободной меркаптанной группы. Это расположение показано на фиг.16d с молекулами дитиола, обозначенными ссылочной позицией 45. Следовательно, поверхность золотых частиц преобразовывается в поверхность, покрытую меркаптанной группой, которая может принимать дополнительный слой золотых частиц.

Далее, обработанную дитиолом поверхность снова погружают в золотой коллоидный раствор для осаждения дополнительного слоя. Этот процесс повторяют пять раз для образования пяти слоев 2 нм золотых частиц, которые соединяются с помощью алкановых цепей дитиола. Два из золотых уровней 46, 47 показаны на увеличенном разрезе 48 на фиг.16b. Полученная в результате структура из пяти слоев золота, имеющая толщину порядка 10 нм, обозначена на фиг. 16d ссылочной позицией 49.

После этого, как показано на фиг.16е, процесс осаждения золота повторяется еще пять раз с золотым коллоидным раствором, который содержит золотые частицы большего размера, например, 40 нм. С помощью этого процесса образуется составной слой 50 из 40 нм золотых частиц толщиной 150 нм на верхней части слоя 49. Поскольку частицы, которые образуют слой 50, имеют значительно больший диаметр, они проявляют пренебрежимо маленькую энергию заряда порядка 1 мэВ и, следовательно, электронная электропроводность через составной слой 50 проявляет омический характер, в отличие от меньших частиц, которые образуют слой 49, демонстрирующих характеристики проводимости, над которыми доминирует эффект блокады Кулона. Поэтому структура 50 из больших золотых частиц функционирует как обычный металлический слой и, следовательно, выполняет функцию затвора таким же образом, как, например, затвор 22 из поликристаллического кремния, описанный в предыдущих вариантах осуществления изобретения.

После этого золотой составной слой 50 используют как массу для сухого травления слоя ОТС 37 и оксидного слоя затвора 21 так, чтобы обеспечить возможность имплантировать области истока и стока 5, 6 в поверхность 3 с помощью обычных ионно-лучевых технических приемов.

Тип 2

На фиг.17 показана общая конфигурация другого типа соответствующего изобретению запоминающего устройства. Устройство аналогично показанному на фиг. 1 и подобные части обозначены теми же самыми ссылочными позициями. Устройство фиг. 17 дополнительно включает управляющий затвор 51, который позволяет селективно прикладывать поле к барьерной конфигурации 2 таким образом, чтобы изменять ее характеристики туннельного перехода. Таким образом, когда к выводу Y прикладывается напряжение, то благодаря изменению напряжения на выводе Х поле на затворе 51 может изменяться, и, в результате этого, поле изменяет характеристики туннельного перехода в переходе 2. Влияние поля, прикладываемого с помощью затвора 51, можно видеть на графиках фиг.18. Напряжение на затворе 51 можно использовать для переключения устройства между состояниями "включено" и "выключено", иллюстрируемыми на фиг.18а и 18b соответственно. Прикладываемое к затвору 51 напряжение меняет ширину запирающего напряжения VB. Как показано на фиг.18а, когда напряжение VX "включено" прикладывают к затвору 51, запирающее напряжение является относительно небольшим и в некоторых условиях отсутствует. На фиг.18а запирающее напряжение VB простирается от - VCL до + VCL, тогда как в случае другого напряжения "выключено" на затворе 51 блокирующая область приобретает более широкий диапазон, простирающийся от - VCH до +VCH. Таким образом, когда устройство переключается на состояние "включено", заряд может туннелировать в узел памяти 1 и храниться в течение состояния "выключено". Во время состояния "выключено" смещающее напряжение можно прикладывать к затвору 51 по существу для усиления VCH, как описано в работе К. Наказато и Х. Ахмеда. "Журнал прикладной физики", 5 июня 1995 г., том 66, 23, стр.3170-3172. Создаваемое напряжением VX поле, подаваемое на линию слов 51, прикладывают к конфигурации барьерного перехода 3 таким образом, чтобы сжать непроводящую область, как можно заметить при сравнении фиг.18а с 18b.

Теперь будет представлено более подробное описание со ссылкой на фиг.19 и 20 модуляции области запирающего напряжения для туннельного перехода 2 с помощью затвора 51. Фиг.19 иллюстрирует разрез узла памяти 1, конфигурации барьерного перехода 2 и вывода Y. Затвор 51 опущен на фиг.19, но будет описан ниже. Конфигурация туннельного перехода 2 состоит из чередующихся слоев 15, 16 нелегированного поликристаллического кремния толщиной 3-10 нм и нитрида кремния толщиной 1-3 нм, образованных описанным выше со ссылкой на фиг. 10 образом. Узел памяти 1 состоит из слоя легированного поликристаллического кремния n-типа толщиной 5-30 нм и закрывается слоем 52 нелегированного поликристаллического кремния толщиной 30 нм. Соответствующий нелегированный слой 53 расположен на другой стороне конфигурации перехода, под слоем 54 легированного поликристаллического кремния n-типа толщиной 30 нм.

Как можно видеть из диаграммы энергетической зоны на фиг.20, семь электроизоляционных слоев 15 нитрида кремния дают повышение соответственным относительно узким и относительно высоким барьерным компонентам 18 аналогичным описанному со ссылкой на фиг.11 образом, вместе с относительно широким, но низким барьерным компонентом 17. Эффект от прикладывания напряжения к затвору 51 заключается в повышении и понижении барьерного компонента 17 по выбору, вместе с барьерными компонентами 18, которые, соответственно, увлекаются вверх и вниз.

В процессе записи напряжение VX, прикладываемое к выводу Х (фиг.17), устанавливают на напряжение записи VW (OV) и в результате высота широкого барьерного компонента 17, которая фактически является внутренним электростатическим потенциалом в конфигурации перехода, в данном примере является относительно низкой величиной порядка 0,2 В. Таким образом, электроны могут туннелировать через узкие барьерные компоненты 18 и не задерживаются низким широким барьерным компонентом 17а, так что электроны туннелируют из вывода Y в узел памяти 1.

Хранящийся заряд в узле 1 может удерживаться, благодаря повышению VX до вспомогательного напряжения VSB, в данном примере равно -5 В. Это увеличивает общую высоту относительно широкого барьерного компонента 17 до уровня 17 b, который в данном примере составляет порядка 3 В. Полученное в результате увеличение высоты барьерного компонента 17 сдерживает туннелирование носителей заряда из узла памяти 1 так, что информация может сохраняться в узле длительные периоды времени ~10 лет.

Для считывания информации VX устанавливают на напряжение считывания VR, которое в данном примере составляет порядка -4 В. Как будет описано ниже, это удерживает заряд, хранящийся в узле памяти 1, но позволяет считывать информацию из канала исток-сток устройства в течение относительно короткого цикла считывания, равно ~100 нс. Барьерный компонент 17 принимает форму 17с, показанную на фиг.20.

Седьмой вариант осуществления изобретения

Теперь будет описана более подробно структура матрицы таких устройств со ссылкой на фиг.21, которая изображает прямоугольную матрицу из четырех ячеек на горизонтальной проекции, совместно с фиг.22 и 23, которые иллюстрируют разрезы по одной из ячеек, вдоль линий А-А' и В-В' фиг.21, соответственно. Рассмотрим фиг.22, где общая структура каждой ячейки памяти аналогична структуре первого типа, как показано на фиг.5, но с дополнением затвора 51, а те же самые каналы обозначены такими же ссылочными позициями. Рассмотрим фиг. 22, где подложка 3 р-типа включает в себя проводящий канал 4 между областями истока и стока 5, 6 вместе с электроизоляционной областью 7 для изоляции одной ячейки от другой. Устройство включает узел памяти 1 и лежащую поверх барьерную структуру 2, образованную, как показано на фиг.19, с покрывающим их слоем 53 нелегированного поликристаллического кремния и линией двоичных разрядов, образованной слоем 54 легированного поликристаллического кремния n-типа. Линия двоичных разрядов 54 закрывается электроизоляционными ХОПФ SiO2 55 и стенками SiO2 56, как будет описано более подробно ниже. Боковой затвор 51 для ячейки состоит из слоя поликристаллического кремния n-типа толщиной 100 нм, который проходит поперек линии двоичных разрядов и накрывает боковые кромки 57 барьерной структуры 2.

Рассмотрим вновь фиг.21, на которой видно, что стоки 6 для соседних ячеек памяти в конкретном ряду делают с использованием общей области стока 6, что снижает размер ячейки памяти.

Информацию можно записывать в конкретную ячейку, например, ячейку памяти М11, показанную на фиг.21, прикладывая напряжение записи VW к линии слов X1 (51) и подходящее напряжение к линии двоичных разрядов Y1 (54) в зависимости от двоичного кода "0" или "1". Это вызывает запись заряда в узле памяти 1 ячейки памяти М11, соответствующей двоичному "0" или "1", в зависимости от напряжения линии двоичных разрядов Y1. Данные не записываются в другие ячейки памяти в столбце, поскольку на линии слов Х2 и т.д. других ячеек поступает вспомогательное напряжение VSB. После этого к линии слов Х1 прикладывают вспомогательное напряжение VSB для сохранения данные в узле 1 ячейки М11. На линии двоичных разрядов не следует подавать напряжение. Когда требуется считывать хранящиеся данные из ячейки М11, напряжение считывания VR на линии слов X1 подается более низкое, чем вспомогательное напряжение VSB. Периферийные схемы (не показанные) воспринимают проводимость истока-стока ячейки M11, считывая ток, протекающий между линиями S1 и G (линии 5, 6). Другие ячейки памяти в столбце смещаются с помощью вспомогательного напряжения VSB, прикладываемого к их линиям слов Х2, и т.д., и таким образом эти ячейки не адресуются при считывании М11.

Кроме того, можно использовать другой способ работы схемы, аналогичный обычному способу, применяемому при обычных ДЗУПВ, в котором хранящаяся информация передается в периферийные схемы и затем заменяется на новую информацию, которая записывается в каждом узле памяти. Этот способ имеет преимущество, разрешая широкие допустимые отклонения в расчетной величине диапазона запирающего напряжения VB, посредством чего допуская появление существенных изменений значений VCL и VCH в различных ячейках. Двоичная "1" представляется напряжением узла памяти VH, а двоичный "0" представляется напряжением узла памяти VL. В отношении схемы существует только требование, чтобы VCH было больше, чем VH, и чтобы VСL было меньше, чем VL, то есть VCH>VH>VL>VCL, и фактически нет необходимости определять их величины. Этот широкий расчетный допуск делает возможным объединение большого количества ячеек памяти в микросхеме.

Теперь будет приведено подробное описание этого способа работы со ссылкой на фиг.24-26. Фиг.24 схематически иллюстрирует электрическую схему матрицы ячеек памяти, соответствующую фиг.21, и дополнительно показывает периферийные схемы, которые объединены на той же полупроводниковой подложке 3, что и матрица ячеек памяти. Каждая ячейка памяти М11-Мmn соответствует запоминающему устройству второго типа, как описывалось выше, хотя схема представлена эквивалентной схемой, состоящей из двух транзисторов QR и QR. Узел памяти 1 представлен индексом N. На фиг.24 показана конфигурация для ячейки памяти М11. Интегральная схема включает декодер и драйвер столбца 58, декодер и драйвер ряда 59, находящийся в микросхеме преобразователь напряжения VC, который создает ряд управляющих напряжений, описываемых более подробно ниже, от внешнего источника напряжения VСС, который в данном примере является источником напряжения 5 В. Каждый столбец матриц ячеек памяти имеет связанную с ним схему предварительной зарядки 60 (PC) и схему считывания-перезаписи 61 (RWC), PC 60 и RWC 61 подробно показаны для столбца n=1 матрицы ячеек памяти, а соответствующие схемы для столбца n показаны в пунктирном контуре.

Схема ввода-вывода данных 62 принимает данные из внешнего источника и передает данные из матрицы памяти способом, описанным более подробно ниже.

Система условных обозначений различных сигналов, линий и компонентов, используемых на фиг.24, 25 и 26, суммирована в таблице.

Теперь будет подробно описан процесс считывания данных со ссылкой на фиг. 25. Когда сигнал разблокирования микросхемы СЕ имеет уровень напряжения VCC, далее обозначаемый как "высокий", микросхема неактивна. В этих условиях сигнал предварительной зарядки фр является "высоким", a S1... Sn, Y1...Yn и I/O предварительно заряжаются до напряжения VP, потому что транзисторы в PC 60 находятся в "открытом" состоянии. Когда СЕ заряжается от "высокого" до нулевого напряжения (далее обозначаемого как "низкое"), микросхемы становятся активными. Затем фр становится "низким" для переключения транзисторов PC 60 в "запертое" состояние. После этого напряжения линий S1... Sn, Y1...Yn плавают, сохраняя величину напряжения VP. Линия слов выбирается с помощью подачи сигналов адреса ряда (аxi) на драйвер ряда 59. Когда напряжение считывания VR прикладывается к Х1, из первого ряда ячеек памяти М11...М1n считывается информация, а выходные сигналы появляются на соответствующих линиях считывания, S1. .. Sn. Рассматривая, в качестве примера, ячейку памяти М11, когда напряжение на узле памяти N равно VP, транзистор QR находится в "открытом" состоянии, а соответствующая считывающая линия S разряжается до 0 В. В качестве альтернативы, когда напряжение на узле памяти равно 0 В, S1 удерживается на значении VP, так как транзистор QR находится в "запертом" состоянии. После того как напряжение в S1 устанавливается на 0 В или VP, сигнал считывания-записи фrw становится "высоким", а информация S1 передается в Y1 через PWC 61. То есть, когда S1 имеет 0 В, Y1 удерживается на величине VP, поскольку QD находится в его "запертом" состоянии. Однако, когда S1 равен VP, Y1 разряжается до 0 В, так как оба транзистора QD и QT находятся в "открытом" состоянии. Тогда фy1 становится по выбору высоким в ответ на подаваемые сигналы адреса столбца (аyj), так что QY1 переходит в "открытое" состояние. Таким образом, изменение напряжения Y1 передается на вывод данных Dout через линию ввода-вывода I/O и IOC 62. После того как Y1 установится на 0 В или VP, напряжение на линии слов Х1 изменяется на напряжение записи VW, так что транзистор QW "открывается", а напряжение Y1 восстанавливается на узле памяти N. Таким образом, даже если происходят какие-либо нарушения в напряжении узла памяти во время операции считывания, информация обновляется для 0 В или VP. Таким же образом осуществляются операции считывания и перезаписи в других ячейках того же ряда, М12... М1n, но считанная информация не передается в линию I/O, как в случае ячейки М11. Когда операции считывания и перезаписи завершаются, СЕ становится высоким, Х1 устанавливается на вспомогательное напряжение VSB, и фр тогда становится высоким.

Теперь будет описана операция записи. В качестве примера, на фиг.26 показана операция записи для ячейки памяти M11. С помощью такой же операции, как описывалась в операции считывания, хранящаяся в М11 информация передается в S1 и Y1. Затем напряжение, соответствующее входным данным Din, подается на I/O, и считываемая информация в Y1 замещается этим напряжением. Затем она запоминается в узле памяти N с помощью приложения напряжения записи VW к линии слов X1. Во время той же операции могут восстанавливаться другие ячейки в том же ряду, M12...М1n. Должно быть понятно, что этот процесс повторяется последовательно, ряд за рядом, для записи данных во все ячейки матрицы памяти.

Теперь будет описан пример способа изготовления соответствующей показанному на фиг.21-23 варианту осуществления ячейки памяти со ссылкой на фиг. 27.

Рассмотрим фиг. 27а, где пластинку 3 кремниевой подложки р-типа с сопротивлением 10 Ом-см термически окисляют для образования слоя 21 из SiO2 толщиной 5 нм. Затем слой 21 наносят пленку 1 из легированного кремния n-типа толщиной 10 нм. Ее закрывают пленкой 52 из нелегированного кремния 30 нм толщины. Поверхность пленки 52 закрывают слоем из нитрида кремния толщиной 1 нм в окружении NH3 при температуре 700oС для образования первого слоя из слоев 15, показанных на фиг.19. Толщину слоя нитрида кремния можно контролировать с помощью управления температурой ее роста, от 2,5 нм при 1000oС до 1 нм при 700oС. Затем наносят слой 16 нелегированного кремния и азотируют для образования другого слоя 15 нитрида кремния толщиной 1 нм. Этот процесс повторяют шесть раз, последовательно образуя многотуннельный переход 2, содержащий семь наборов покрывающих слоев 15, 16, показанных более подробно на фиг. 19. После этого наносят пленку 53 из нелегированного кремния 30 нм толщины, которую, в свою очередь, покрывают 20 нм пленкой 63 из Si3N4, которую наносят с целью маскирования, и структурируют с помощью литографии и сухого травления в атмосфере СНF3 и газа аргона. Затем вытравливают слои нитрида кремния 53, 15, 16, 52 и 1, используя известный сам по себе способ сухого травления.

Рассмотрим фиг. 27b, где поверхность пластинки оксидируется для образования SiO2 64 толщиной 30 нм, с боковыми краями 64а на вертикальных боковых сторонах барьерной конфигурации 2, используя в качестве маски пленку 63 из Si3N4. Для образования областей истока и стока 5, 6 имплантируют ионы мышьяка.

Затем, как показано на фиг.27с, удаляют пленку 63 из Si3N4 и наносят пленку 54 из легированного кремния n-типа толщиной 30 нм, за которой следует пленка 55 из SiO2 толщиной 50 нм, наносимая с помощью обычного процесса ХОПФ. После этого слой 55 структурируется с помощью литографии и способов сухого травления. Ширину линии двоичных разрядов, то есть ширину показанной на фиг. 21 линии Y1 (54), выбирают равной 60 нм, что обеспечивает хорошую управляемость внутренним электростатическим потенциалом устройства. Толщину различных слоев в линии двоичных разрядов Y1 можно выбирать в зависимости от размера матрицы ячеек памяти. Для более широких линий двоичных разрядов слои следует делать толще. Используя защитный слой и пленку 55 из SiO2 в качестве маски, слои 54 и 55 селективно протравливают в атмосфере газа Сl2 до тех пор, пока не откроется первый слой нитрида кремния конфигурации туннельного перехода 2.

Как показано на фиг.27d, для обеспечения боковых стенок 56 наносят слой ХОПФ SiO2 толщиной 30 нм и подвергают сухому травлению в атмосфере СНF3 и газа аргона.

Затем, как показано на фиг. 27е, где с этого времени для определения линии слов наносят и структурируют с помощью обычных способов литографии и сухого травления слой 51 поликристаллического кремния.

МОП-транзисторы (металл - оксид - полупроводник) n-типа и р-типа, которые используются в показанных на фиг.24 периферийных схемах, можно выполнять на той же самой подложке 3 с помощью обычных способов. Области истока и стока для МОП-транзисторов n-типа можно образовывать в то же время, когда создаются исток и стоки 5, 6 ячеек памяти Мmn, как описывалось со ссылкой на фиг.27b.

В данном варианте осуществления для сохранения в отдельных узлах памяти 1 запомненной информации к линиям слов необходимо прикладывать вспомогательное напряжение VSB, равное -5 В. Этого можно добиться при выключенном устройстве с помощью использования внешней аккумуляторной батареи или конденсатора. Поскольку течет незначительный ток, за исключением пренебрежимо маленького тока утечки, можно получить действительно энергонезависимые характеристики. В описываемой ниже модификации использование внешней аккумуляторной батареи или конденсатора исключается, благодаря смещению всех напряжений вверх на +5 В. В этом случае вспомогательное напряжение становится равным 0 В и, таким образом, внешняя аккумуляторная батарея не требуется.

Восьмой вариант осуществления изобретения

На фиг.28 показан один способ смещения вспомогательного напряжения, где под контактными площадками линий слов образована легированная область р-типа 65. Эту конфигурацию можно рассматривать как модификацию показанной на фиг. 22 конфигурации. Легированная область р-типа 65 образована путем ионной имплантации ионов бора, используя в качестве маски слои SiO2 55-56 после этапа процесса, показанного на фиг.27(d). Напряжение в линии слов сдвигается примерно на 1 В при комнатной температуре. В этой структуре имеется другое преимущество, состоящие в том, что можно управлять более эффективно внутренним электростатическим потенциалом, а следовательно, краем энергетической зоны энергии проводимости. Вследствие эффектов поперечного распространения имплантированных ионов бора и получаемой в результате контактной разности потенциалов образованного имплантированного перехода типа р-i, эффективная ширина линии двоичных разрядов может быть значительно меньше, чем фактическая ширина линии двоичных разрядов, так что даже ширина линии двоичных разрядов равна 1 мкм, достаточна для реализации представленного запоминающего устройства, вместо ширины 0,06 мкм линии двоичных разрядов в седьмом варианте осуществления изобретения. В этой структуре VSB=-4 В; VR=-3 В и VW=1 B.

Девятый вариант осуществления изобретения

Кроме того, как показано на фиг.29, внутри барьерной структуры можно образовывать тонкий легированный слой 66 р-типа, получая в результате даже более высокую контактную разность потенциалов. Конфигурацию на фиг.29 можно рассматривать как модификацию показанной на фиг.28 конфигурации. Такой слой 66 р-типа можно легко образовать путем нанесения кремниевой пленки р-типа или имплантации ионов бора на промежуточной стадии образования барьерной структуры, так как ее образуют с помощью способа повторяемого нанесения. Для снижения диффузии бора тонкие туннельные переходы 15 на фиг.19 располагают в промежутках между легированными слоями 66 р-типа. В этом случае напряжение линии слов управляет непосредственно внутренним электростатическим потенциалом, а следовательно, краем энергетической зоны энергии проводимости. Это снижает разницу напряжений в линии слов между циклами резервирования и записи. В этой структуре, VSB=-2 В, VR=-1В и VW= 1 В.

Десятый вариант осуществления изобретения

В данном варианте осуществления изобретения используется более толстый туннельный переход, порядка 5 нм, как показано на фиг.30. Конфигурацию на фиг. 30 можно рассматривать как модификацию показанной на фиг.19 конфигурации, а барьерную структуру можно вводить в устройство, описанное со ссылкой на фиг. 21-23. Узел памяти 1 на фиг.30 перекрывают нелегированным слоем 52 поликристаллического кремния толщиной 30 нм, который сам закрывается одним барьерным слоем 67 толщиной 5 нм, образованным из материала Si3N4. Пленку Si3N4 можно образовать с помощью плазменного азотирования при температуре 550oС и при уровне мощности 300-500 Вт. Ее закрывают слоем 53 нелегированного Si толщиной 30 нм и слоем 54 легированного Si n-типа толщиной 30 нм, описанным выше со ссылкой на фиг.19. Полученная в результате диаграмма энергетической зоны проводимости для барьерной структуры показана на фиг.31 и состоит из относительно широкой барьерной компоненты 17 относительно низкой высоты барьера вместе с относительно узкой барьерной компонентой 18, образованной слоем 67, относительно большой высоты барьера. В данном примере, высота барьера составляет порядка 2 В, который образован слоем электроизоляционного Si3N4 толщиной 5 нм. Во время операции записи напряжение записи прикладывается к боковому затвору 51 (не показанному) на фиг.30. В данном примере напряжение записи VW=5 В снижает барьерную конфигурацию в переходном состоянии таким образом, что относительно широкая барьерная компонента принимает конфигурацию 17а, показанную на фиг.31. Для считывания данных на затвор 51 подают напряжение VR=1 В, так что барьер принимает конфигурацию 17b. В таком устройстве можно считывать данные из запоминающего устройства. Для хранения информации используется вспомогательное напряжение VSB=0 В таким образом, что конфигурация 17с положительно блокирует утечку заряда из узла памяти 1 с помощью напряжения 0 В, подводимого к линии слов X.

Тип 3

Одиннадцатый вариант осуществления изобретения

Другой тип соответствующего изобретению запоминающего устройства схематически показан на фиг.32. Устройство в общем подобно варианту осуществления, описанному со ссылкой на фиг.4 и 5, и аналогичные части обозначены теми же самыми ссылочными позициями. В соответствующем фиг.32 варианте осуществления барьерная структура состоит из матрицы горизонтальных точечных элементов 68. Точечные элементы можно производить с помощью ряда различных способов, типа способа ионно-лучевого осаждения, как описано в работе У. Чена, Х. Ахмеда и К. Наказато, "Журнал прикладной физики", 12 июня 1995 г., том 66, 24, стр. 3383-3384 или с помощью одноатомной литографии, как описано Х. Ахмедов в трудах "Третьего международного симпозиума по вопросам новых явлений в мезоскопических структурах", декабрь 1995 г. Кроме того, горизонтальные точечные элементы 68 можно заменять гранулами в пленке из поликристаллического кремния, например, как описано Яно и др. (см. выше) с помощью нанокристаллов, как описано посредством способа в настоящих третьем, четвертом и пятом вариантах осуществления изобретения, и с помощью коллоидальных частиц, как описано посредством способа в настоящем шестом варианте осуществления изобретения.

Много вариантов и модификаций находятся в пределах объема настоящего изобретения. Например, различные области материала n-типа и р-типа можно заменять друг другом для образования устройств с дополнительными характеристиками проводимости описанным выше устройствам. Кроме того, толщина различных слоев, которые составляют описанные примеры наслаиваемых туннельных переходов, может отличаться от конкретных примеров, приведенных выше. Точно так же можно использовать отличающиеся электроизоляционные материалы. Например, вместо нитрида кремния можно в качестве туннельного перехода использовать окись кремния. Более того, можно использовать другие системы изготовления полупроводников, с отличающейся основной подложкой, типа кремния на изоляторе, SiGe, Ge, GaAs и других, хорошо известных специалистам в данной области техники. Кроме того, различные другие варианты осуществления барьерной структуры и ее модификации, описанные для использования в первом типе соответствующего изобретению запоминающего устройства, можно использовать в вариантах осуществления второго типа с боковым затвором 51, и соответствующие второму типу варианты осуществления можно модифицировать для использования без бокового затвора, или с фиксированным напряжением, подводимым к боковому затвору, чтобы работать в соответствии с принципами первого типа.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1998 |

|

RU2216819C2 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1999 |

|

RU2249262C2 |

| ЭЛЕМЕНТ ПАМЯТИ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1981 |

|

SU1012704A1 |

| МАГНИТОЭЛЕКТРИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2573207C2 |

| ФЛЭШ ЭЛЕМЕНТ ПАМЯТИ ЭЛЕКТРИЧЕСКИ ПЕРЕПРОГРАММИРУЕМОГО ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2015 |

|

RU2584728C1 |

| ВСТРАИВАЕМАЯ С СБИС ТЕХНОЛОГИИ КМОП/КНИ ПАМЯТЬ "MRAM" И СПОСОБ ЕЕ ИЗГОТОВЛЕНИЯ (ВАРИАНТЫ) | 2012 |

|

RU2532589C2 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2015 |

|

RU2681344C1 |

| ЯЧЕЙКА МАГНИТНОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА С МАЛЫМ ЭНЕРГОПОТРЕБЛЕНИЕМ | 2012 |

|

RU2573757C2 |

| УСТРОЙСТВО ПАМЯТИ НА ТОНКОПЛЕНОЧНОЙ СТРУКТУРЕ КРЕМНИЯ НА СТЕКЛЕ | 2006 |

|

RU2402107C2 |

| Интегральное запоминающее устройство | 1976 |

|

SU731864A1 |

Изобретение относится к запоминающим устройствам высокой степени интеграции и способу их изготовления. Предложены запоминающее устройство и способ его изготовления, при этом устройство содержит узел памяти, в который записывается заряд через конфигурацию туннельного перехода, имеющую профиль энергетической зоны, который содержит относительно широкий по размеру барьерный компонент с относительно низкой высотой барьера и по меньшей мере один относительно узкий по размеру барьерный компонент с относительно большой высотой барьера. Также предложены множество запоминающих устройств и матрица из запоминающих устройств, сформированных в виде матрицы ячеек памяти на общей подложке. В результате появляется возможность увеличения объема памяти с уменьшением размеров устройства и повышением надежности. 7 с. и 57 з.п. ф-лы, 34 ил., 1 табл.

Авторы

Даты

2003-11-20—Публикация

1997-11-14—Подача