ПЕРЕКРЕСТНАЯ ССЫЛКА НА СВЯЗАННЫЕ ЗАЯВКИ

Настоящая заявка основана на и испрашивает приоритет предварительной патентной заявки США № 62/130,484, поданной 9 марта 2015, все содержание которой включено в настоящий документ посредством ссылки.

ОБЛАСТЬ ТЕХНИКИ

Варианты осуществления настоящего изобретения относятся к полупроводниковому запоминающему устройству.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

MRAM (магниторезистивная память с произвольным доступом) представляет собой устройство памяти, которое использует магнитные элементы с магниторезистивным эффектом в качестве ячеек памяти, которые хранят информацию, и привлекает внимание как устройство памяти следующего поколения, характеризуемое высоким быстродействием, большой емкостью и энергонезависимостью. Кроме того, были проведены исследования и разработки касательно возможности MRAM заменять энергозависимую память, такую как DRAM и SRAM. В этом случае, MRAM желательно работать в соответствии с теми же спецификациями, что и для DRAM и SRAM, чтобы поддерживать низкими затраты на разработку и обеспечить плавное осуществление такой замены.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

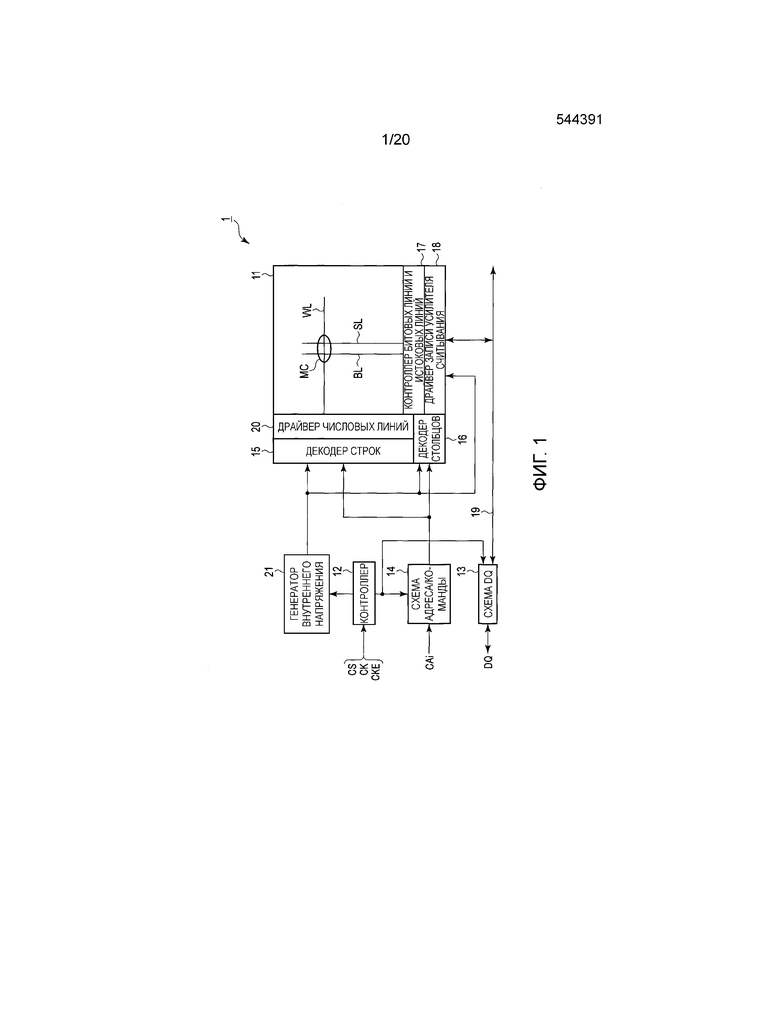

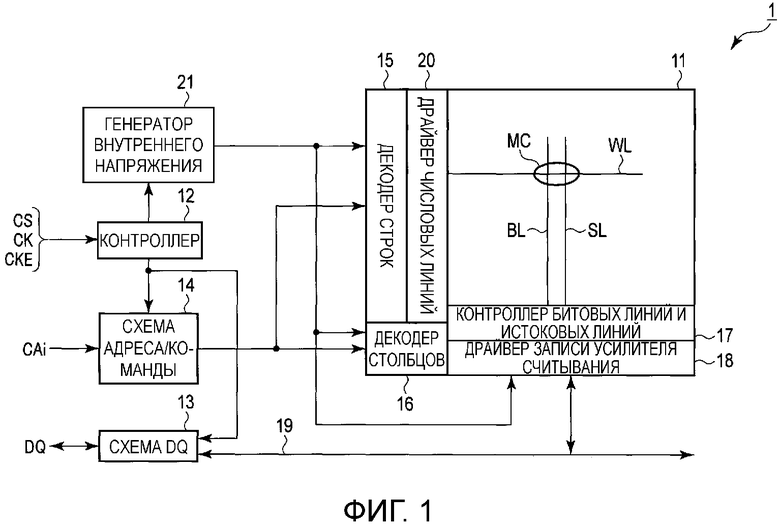

Фиг. 1 - блок-схема, изображающая конфигурацию полупроводникового запоминающего устройства в соответствии с первым вариантом осуществления;

Фиг. 2 - схематичное представление, иллюстрирующее операцию записи, выполняемую в ячейке памяти в полупроводниковом запоминающем устройстве в соответствии с первым вариантом осуществления;

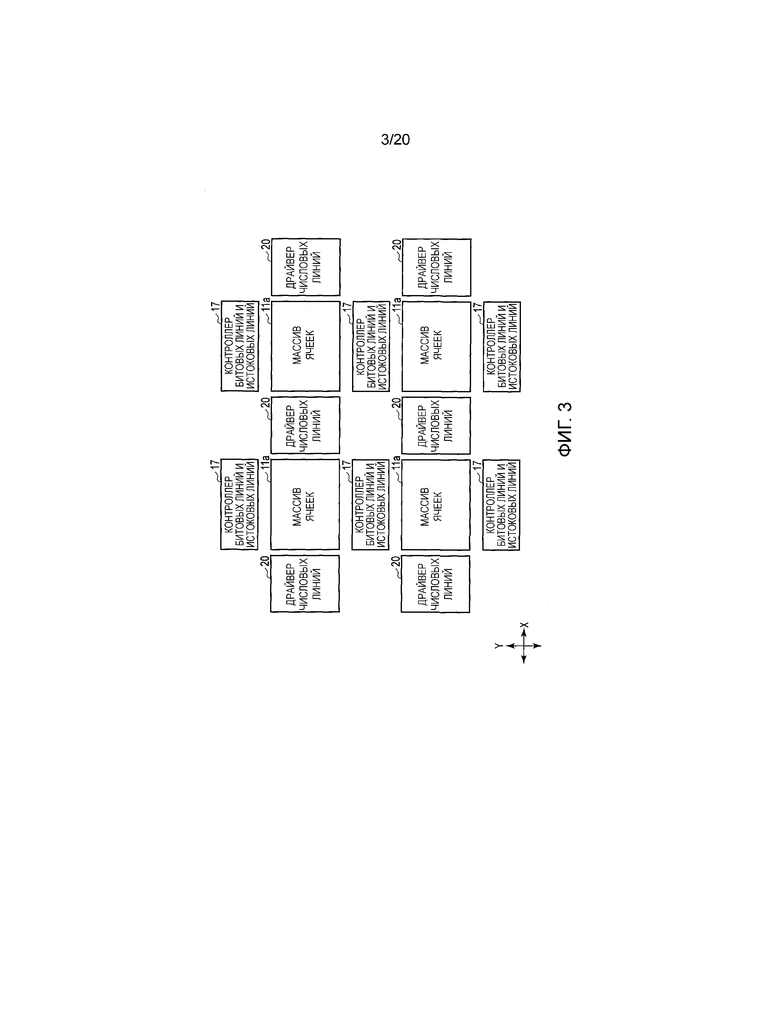

Фиг. 3 изображает пример компоновки ячеек и периферийных схем для массивов ячеек в полупроводниковом запоминающем устройстве в соответствии с первым вариантом осуществления;

Фиг. 4 - блок-схема, иллюстрирующая связь между массивом ячеек и контроллером битовых линий и истоковых линий в полупроводниковом запоминающем устройстве в соответствии с первым вариантом осуществления;

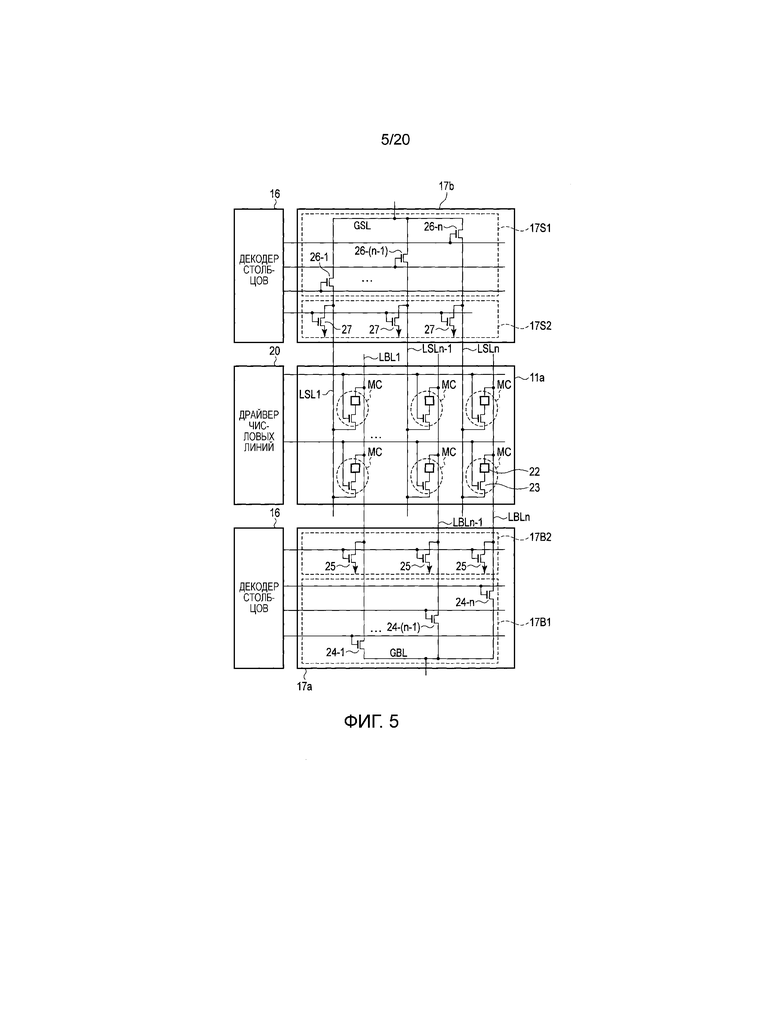

Фиг. 5 - схема соединений, иллюстрирующая взаимосвязь между массивом ячеек и контроллером битовых линий и истоковых линий в полупроводниковом запоминающем устройстве в соответствии с первым вариантом осуществления;

Фиг. 6 - схема, иллюстрирующая связь между усилителем считывания и периферийной схемой для усилителя считывания в полупроводниковом запоминающем устройстве в соответствии с первым вариантом осуществления;

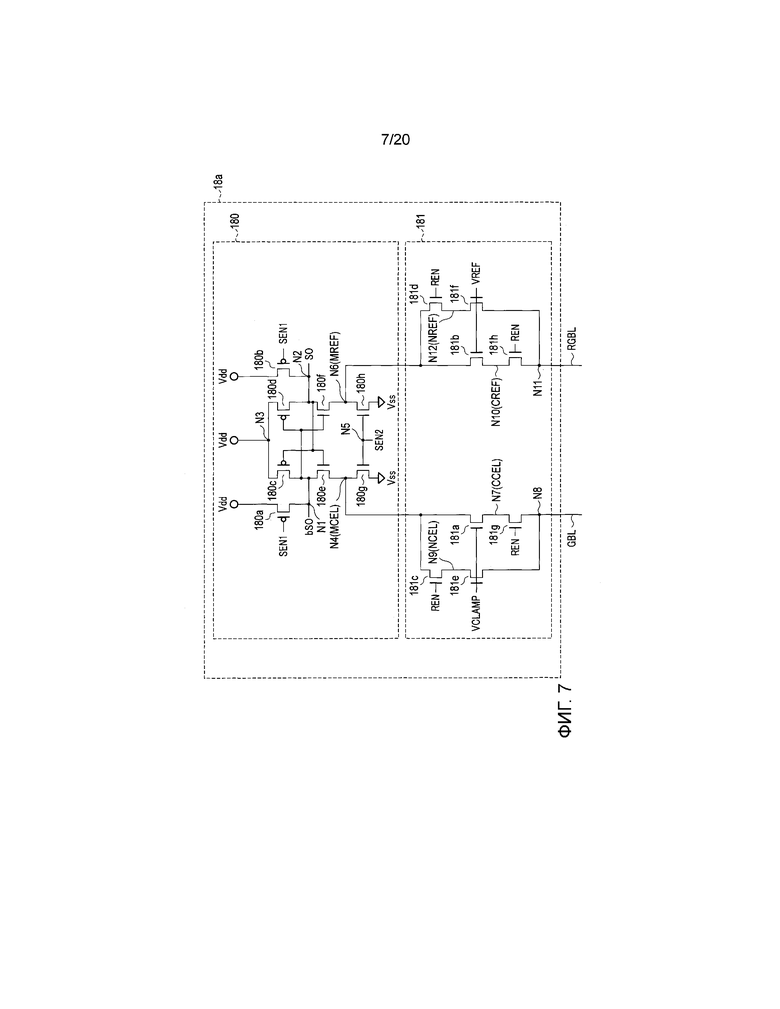

Фиг. 7 - принципиальная схема, изображающая базовую конфигурацию усилителя считывания в полупроводниковом запоминающем устройстве в соответствии с первым вариантом осуществления;

Фиг. 8 - компоновка (топология) преобразователя в полупроводниковом запоминающем устройстве в соответствии с первым вариантом осуществления;

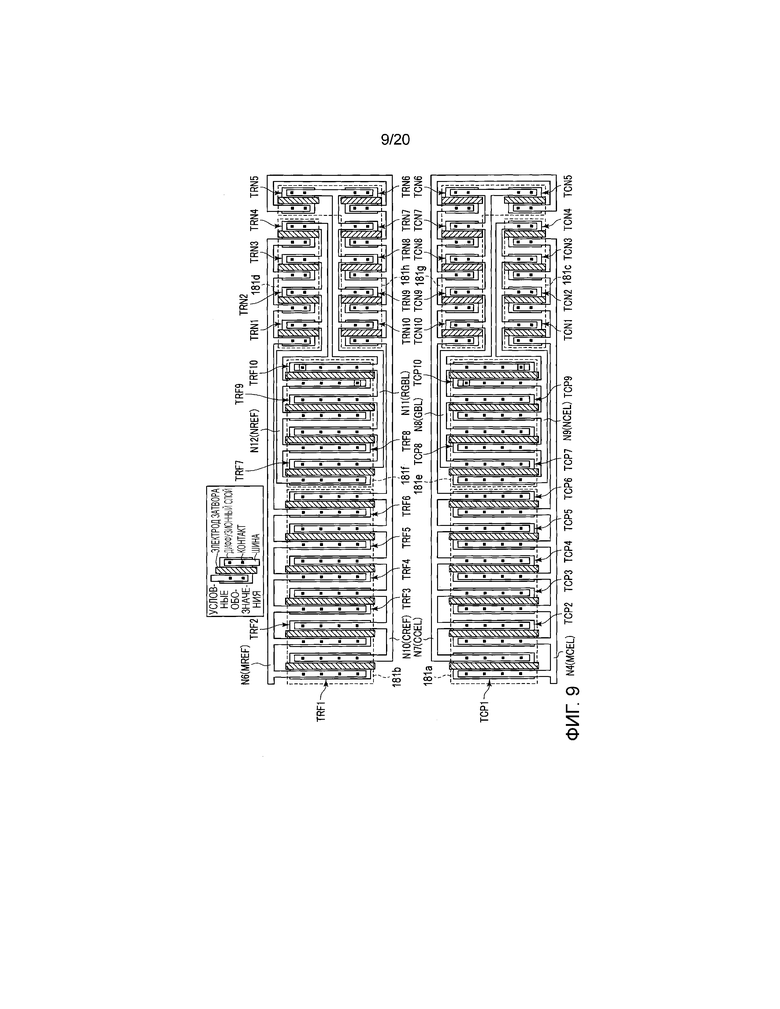

Фиг. 9 - топология преобразователя в полупроводниковом запоминающем устройстве в соответствии с первым вариантом осуществления;

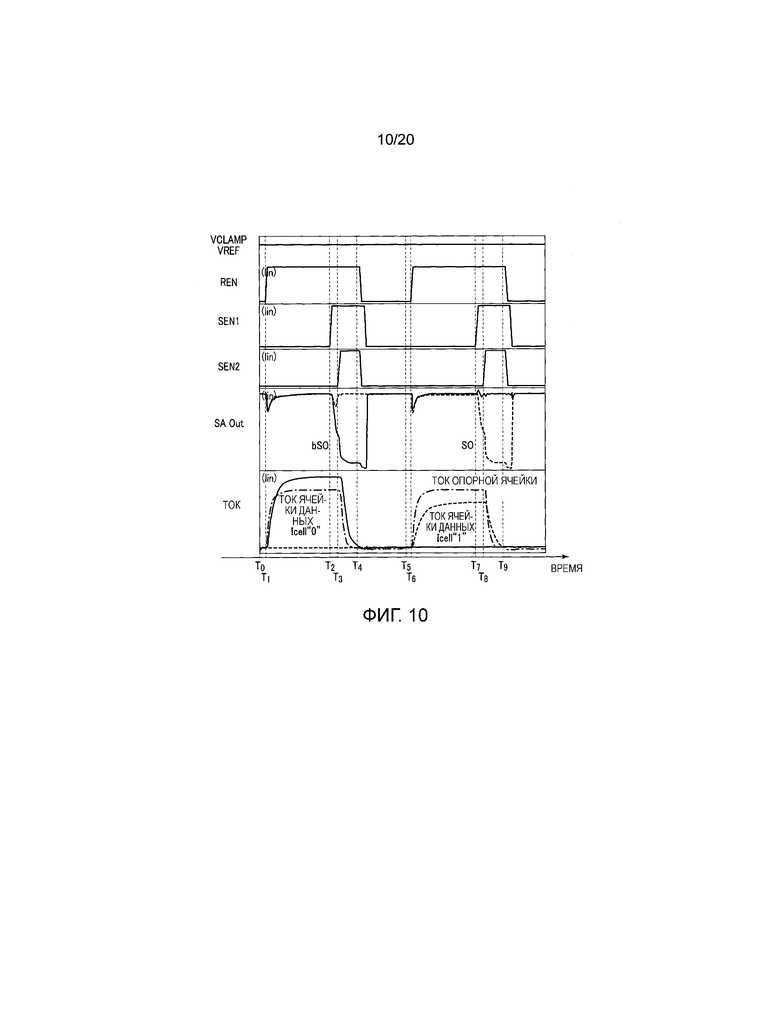

Фиг. 10 - временная диаграмма сигналов, иллюстрирующая операцию считывания в полупроводниковом запоминающем устройстве в соответствии с первым вариантом осуществления;

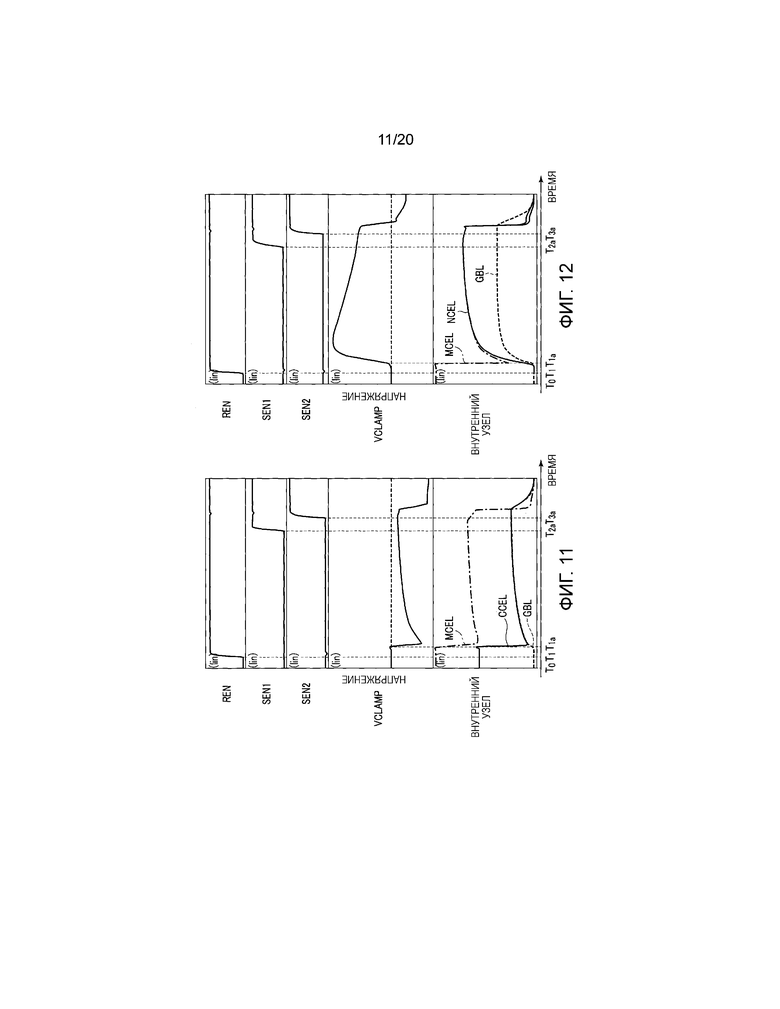

Фиг. 11 - временная диаграмма сигналов, иллюстрирующая операцию считывания в полупроводниковом запоминающем устройстве согласно сравнительному примеру 1 первого варианта осуществления;

Фиг. 12 - временная диаграмма сигналов, иллюстрирующая операцию считывания в полупроводниковом запоминающем устройстве согласно сравнительному примеру 2 первого варианта осуществления;

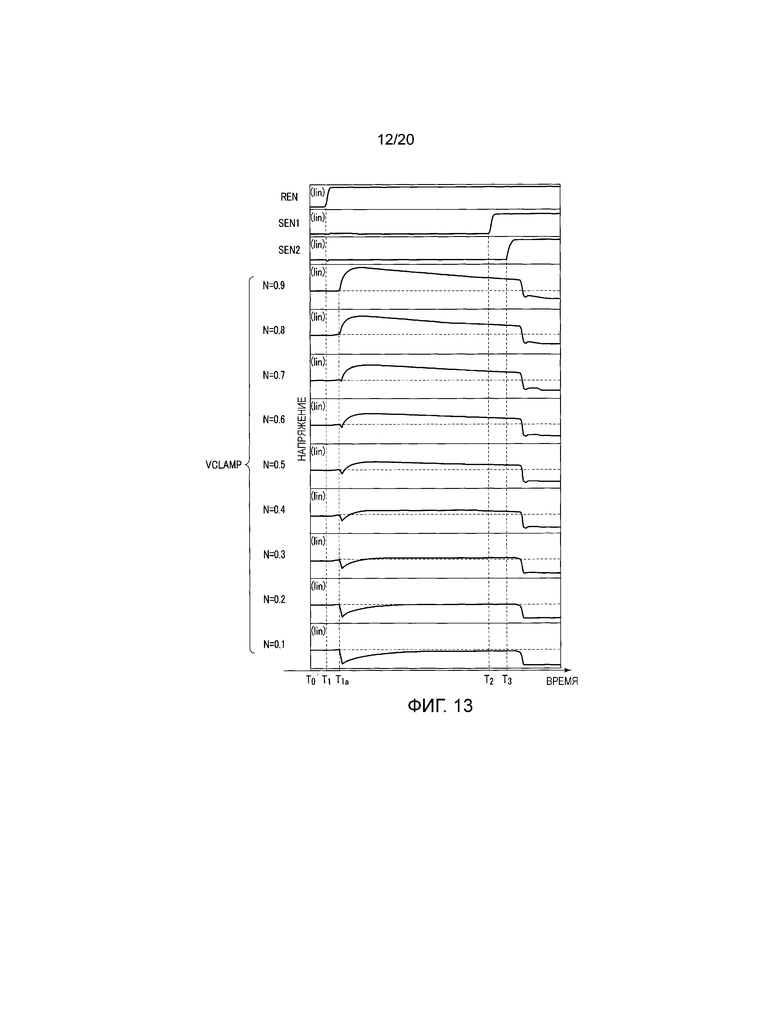

Фиг. 13 - временная диаграмма сигналов, иллюстрирующая операцию считывания в полупроводниковом запоминающем устройстве в соответствии с первым вариантом осуществления;

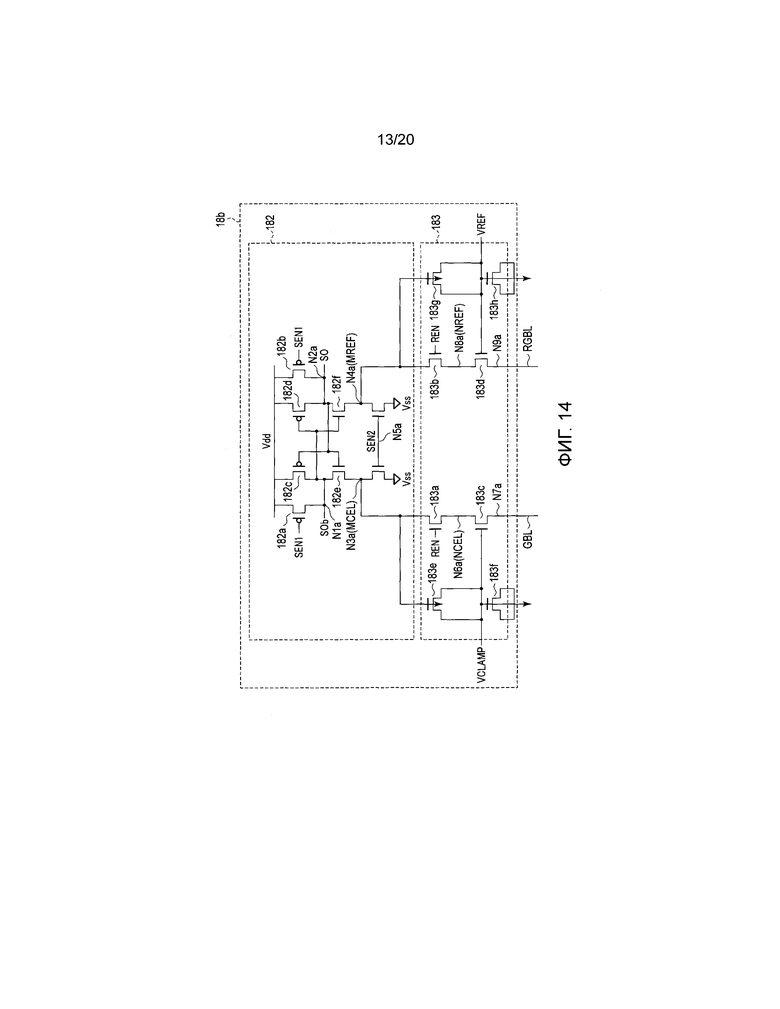

Фиг. 14 - принципиальная схема, изображающая базовую конфигурацию усилителя считывания в полупроводниковом запоминающем устройстве в соответствии со сравнительным примером первого варианта осуществления;

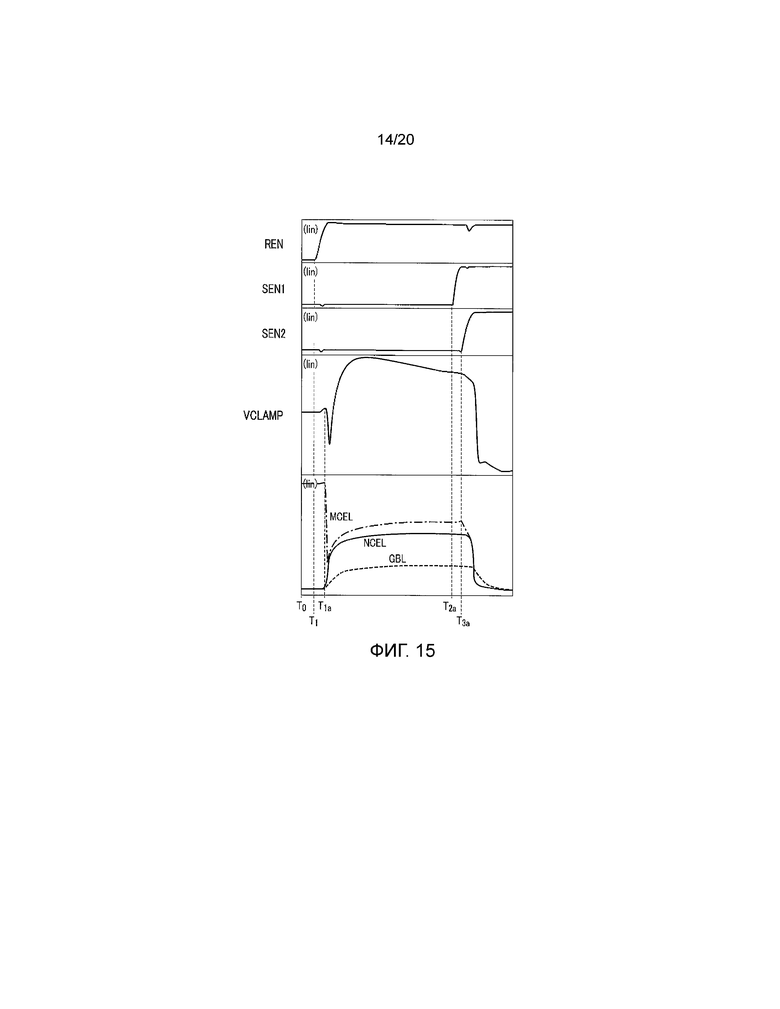

Фиг. 15 - временная диаграмма сигналов, иллюстрирующая операцию считывания в полупроводниковом запоминающем устройстве согласно сравнительному примеру 3 первого варианта осуществления;

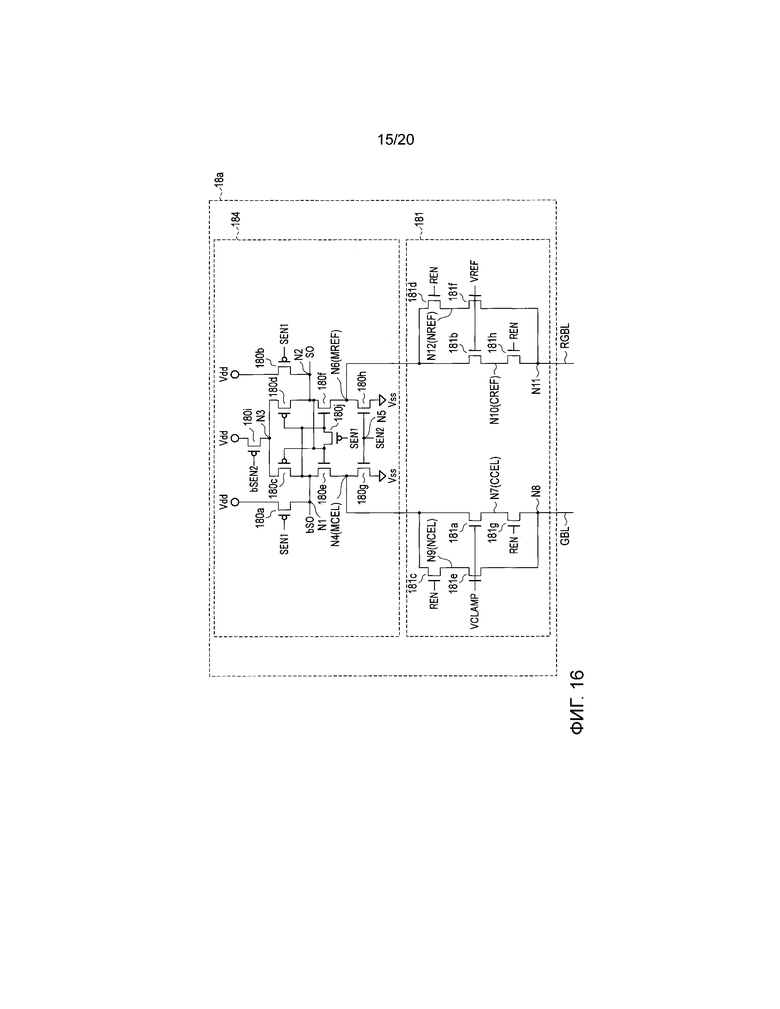

Фиг. 16 - принципиальная схема, изображающая базовую конфигурацию усилителя считывания в полупроводниковом запоминающем устройстве в соответствии со вторым вариантом осуществления;

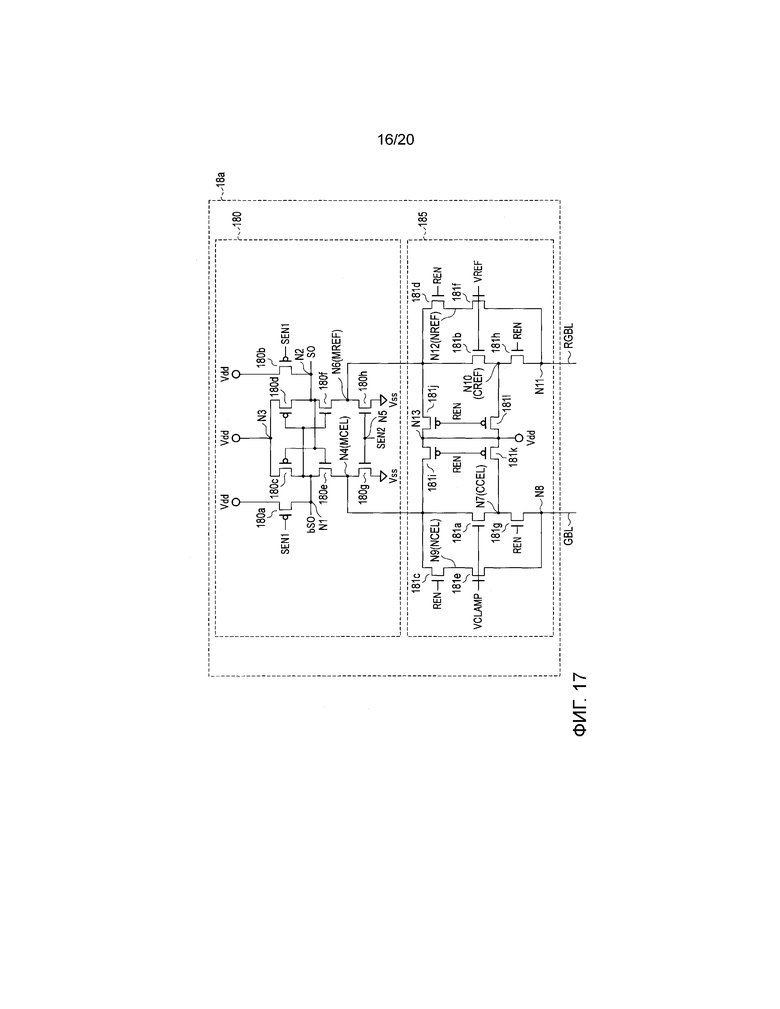

Фиг. 17 - принципиальная схема, изображающая базовую конфигурацию усилителя считывания в полупроводниковом запоминающем устройстве в соответствии с третьим вариантом осуществления;

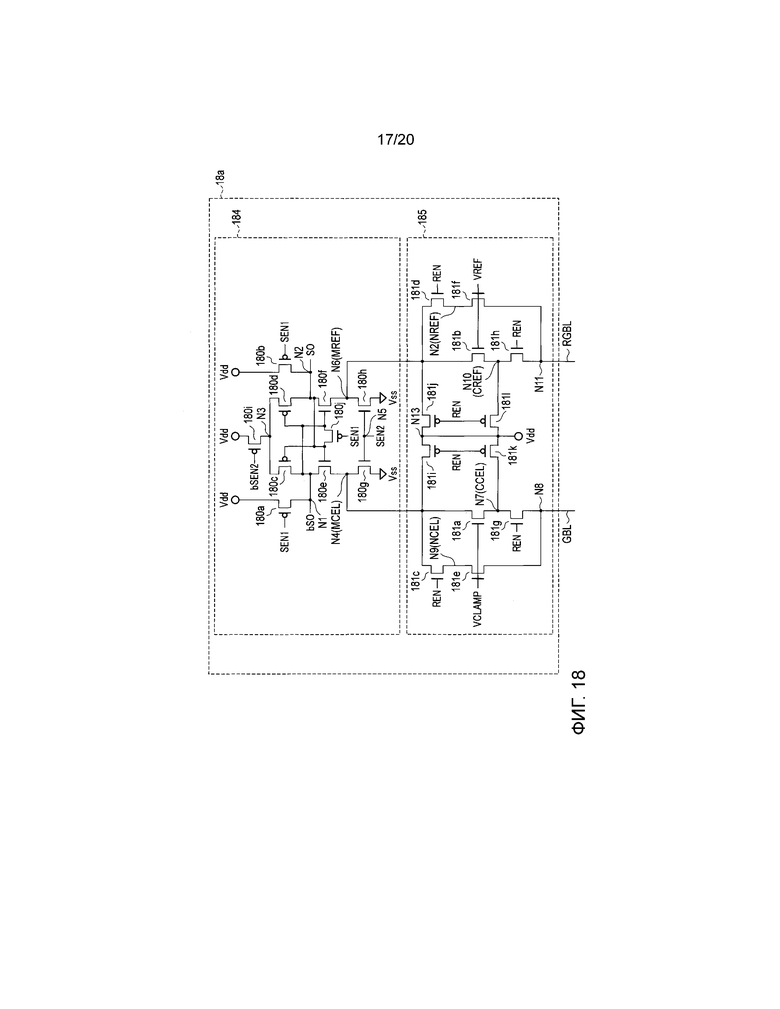

Фиг. 18 - принципиальная схема, изображающая базовую конфигурацию усилителя считывания в полупроводниковом запоминающем устройстве в соответствии с модификацией третьего варианта осуществления;

Фиг. 19 - принципиальная схема, изображающая базовую конфигурацию усилителя считывания в полупроводниковом запоминающем устройстве в соответствии с четвертым вариантом осуществления;

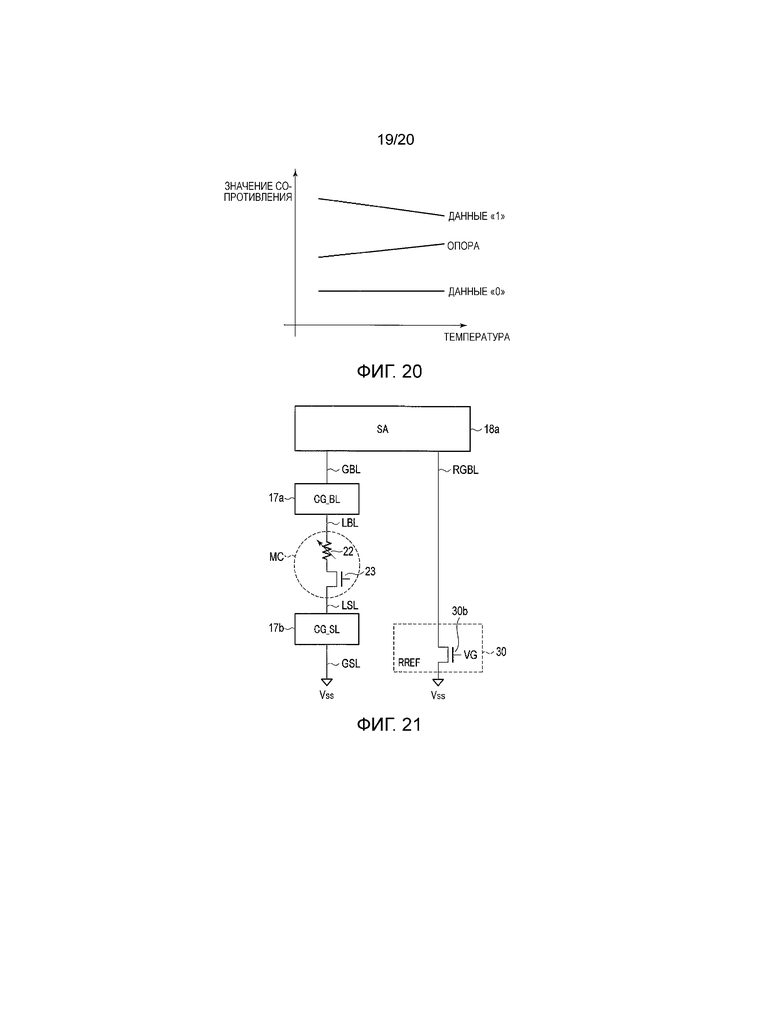

Фиг. 20 - график, иллюстрирующий температурные свойства ячейки памяти и опорной схемы;

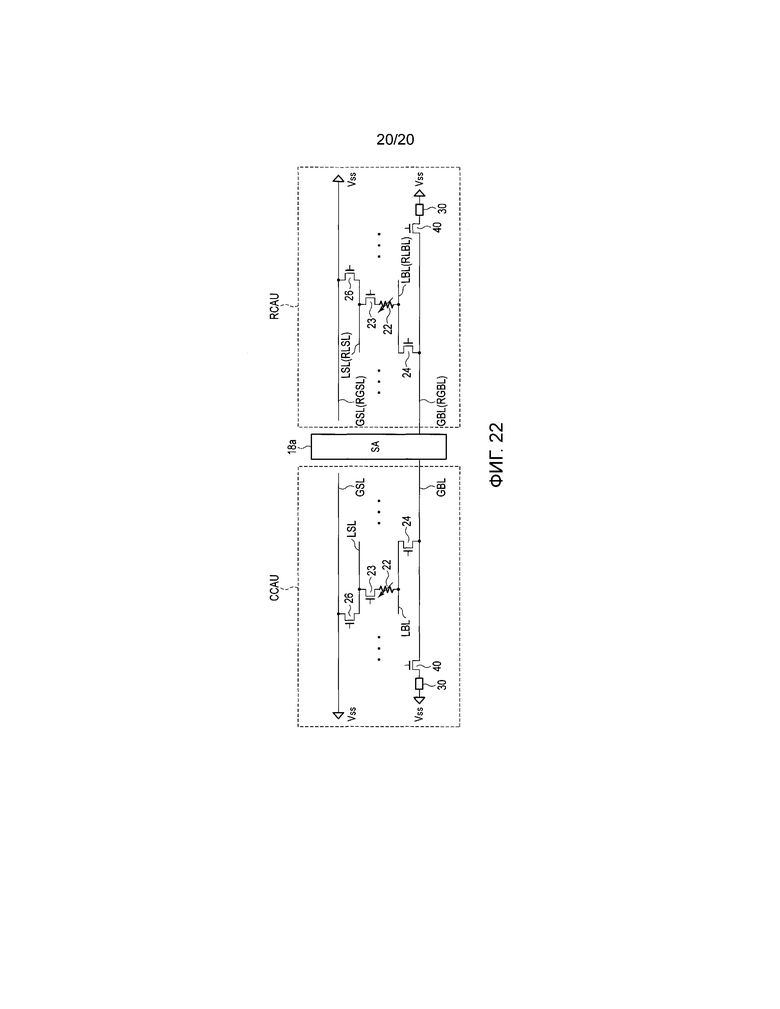

Фиг. 21 - схема, иллюстрирующая связь между усилителем считывания и периферийной схемой для усилителя считывания в полупроводниковом запоминающем устройстве в соответствии с четвертым вариантом осуществления; и

Фиг. 22 - схема, иллюстрирующая связь между усилителем считывания и периферийной схемой для усилителя считывания в полупроводниковом запоминающем устройстве в соответствии с пятым вариантом осуществления.

ПОДРОБНОЕ ОПИСАНИЕ

В общем, согласно одному варианту осуществления, полупроводниковое запоминающее устройство включает в себя ячейку памяти, битовую линию, соединенную с ячейкой памяти, и схему считывания, соединенную с битовой линией, при этом схема считывания включает в себя первый транзистор с первым концом, соединенным с битовой линией, и затвором, на который вводится первый сигнал, второй транзистор с первым концом, соединенным со вторым концом первого транзистора, и затвором, на который вводится второй сигнал, третий транзистор с первым концом, соединенным с битовой линией, и затвором, на который вводится второй сигнал, четвертый транзистор с первым концом, соединенным со вторым концом третьего транзистора, и затвором на который вводится первый сигнал, и усилитель, соединенный со вторым концом второго транзистора и со вторым концом четвертого транзистора.

Варианты осуществления будут описаны ниже со ссылкой на чертежи. Компоненты с практически идентичными функциями и конфигурациями обозначены одинаковыми ссылочными позициями, и повторяющиеся описания приведены только в случае необходимости. Кроме того, варианты осуществления, раскрытые ниже, иллюстрируют устройства и способы для воплощения технических концепций вариантов осуществления, и технические концепции вариантов осуществления не предназначены для ограничения материалов, форм, компоновок и т.п. компонентов, описанных ниже. Различные изменения могут быть внесены в технические концепции вариантов осуществления в объеме формулы изобретения.

(Первый вариант осуществления)

<1-1> Конфигурация полупроводникового запоминающего устройства согласно первому варианту осуществления.

Прежде всего, базовая конфигурация полупроводникового запоминающего устройства в соответствии с первым вариантом осуществления будет кратко описана с использованием фиг. 1.

Полупроводниковое запоминающее устройство 1 согласно первому варианту осуществления включает в себя массив 11 ячеек памяти (далее также просто упоминаемый как массив ячеек), контроллер 12, схему 13 DQ, схему 14 адреса/команды, декодер 15 строк, декодер 16 столбцов, контроллер 17 битовых линий и истоковых линий, драйвер (формирователь сигналов) 18 записи усилителя считывания, драйвер 20 числовых линий и генератор 21 внутреннего напряжения. Для каждого массива 11 ячеек памяти, декодер 16 столбцов генерирует управляющие сигналы для драйвера 20 числовых линий и управляющие сигналы для контроллера 17 битовых линий и истоковых линий.

Массив 11 ячеек памяти представляет собой MRAM и включает в себя множество ячеек МС памяти, расположенных в двумерном порядке в матрице. Каждая из ячеек МС памяти содержит элемент 22 MTJ (не показан на чертежах) и транзистор 23 ячейки (не показан на чертежах). Элемент 22 MTJ представляет собой элемент магнитного туннельного перехода, который сохраняет данные в соответствии с изменением состояния сопротивления и который позволяет переписывать данные в соответствии с током. Транзистор 23 ячейки обеспечен в ассоциации с элементом 22 MTJ и сконфигурирован, чтобы устанавливаться в электрически непрерывное состояние при пропускании тока в соответствующий элемент 22 MTJ.

Множество числовых линий WL проведены в направлении строк, и множество битовых линий BL проведены в направлении столбцов, так что числовые линии WL пересекают битовые линии BL. Две смежные битовые строки BL образуют пару, и ячейка MC памяти обеспечена в ассоциации с точкой пересечения между числовой линией WL и парой битовых линий (в настоящем варианте осуществления упоминаются как битовая линия BL, истоковая линия SL для удобства). Элемент 22 MTJ и транзистор 23 ячейки в каждой ячейке МС памяти соединены между парой битовых линий (например, между BL и SL) последовательно с парой битовых линий. Кроме того, затвор транзистора 23 ячейки соединен с числовой линией WL.

В контроллер 12 вводятся различные внешние управляющие сигналы, например сигнал CS выбора чипа, тактовый сигнал CK и сигнал CKE разрешения тактирования. Контроллер 12 управляет схемой 14 адреса/команды для различения адресов от команд.

Сигнал CAi адреса/команды вводится в схему 14 адреса/команды. Схема 14 адреса/команды переносит сигнал CAi адреса/команды в декодер 15 строк и декодер 16 столбцов.

Декодер 15 строк размещен на противоположных сторонах массива 11 ячеек памяти в направлении числовой линии для декодирования адреса в сигнале CAi адреса/команды, подаваемого схемой 14 адреса/команды.

Декодер 16 столбцов распознает команду и адрес в сигнале CAi адреса/команды на основе внешнего управляющего сигнала для управления контроллером 17 битовых линий и истоковых линий.

Контроллер 17 битовых линий и истоковых линий расположен на противоположных сторонах массива 11 ячеек памяти в направлении битовых линий для управления битовыми линиями BL и истоковыми линиями SL на основе управляющих сигналов от декодера 16 столбцов.

Драйвер 18 записи усилителя считывания расположен в направлении битовых линий массива 11 ячеек памяти. Усилитель считывания соединен с битовыми линиями BL для детектирования тока, протекающего через ячейку МС памяти, соединенную с выбранной числовой линией WL, для считывания данных, сохраненных в ячейке памяти. Драйвер записи соединенным с битовыми линиями BL, чтобы пропускать ток через ячейку памяти, соединенную с выбранной числовой линией WL, для записи данных в ячейку МС памяти.

Кроме того, драйвер 18 записи усилителя считывания включает в себя буфер страницы, не изображенный на чертежах. Буфер страницы хранит данные, считанные усилителем считывания, или данные, принятые через шину 19 данных и схему 13 DQ.

Передача и прием данных между драйвером записи усилителя 18 считывания и внешним I/O-терминалом DQ выполняются через шину 19 данных и схему 13 DQ.

Драйвер 20 числовых линий расположен на противоположных сторонах массива 11 ячеек памяти в направлении числовых линий. Драйвер 20 числовых линий соединен с числовыми линиями и сконфигурирован для приложения напряжения к выбранной числовой линии WL во время считывания данных или записи данных. Более конкретно, драйвер 20 числовых линий сконфигурирован так, чтобы иметь возможность прикладывать напряжение к выбранной числовой линии WL в соответствии с адресом строки, декодированным декодером 15 строк.

Генератор внутреннего напряжения 21 предусмотрен для генерирования внутреннего напряжения (например, напряжения, на которое увеличивается напряжение питания), необходимого для каждой операции в полупроводниковом запоминающем устройстве 1. Генератор 21 внутреннего напряжения также управляется контроллером 12 для выполнения операции повышения напряжения для генерации необходимого напряжения.

<1-2> Конфигурация ячейки МС памяти

Далее будет кратко описана конфигурация ячейки MC памяти в соответствии с первым вариантом осуществления с использованием фиг. 2.

Как показано на фиг. 2, первый конец элемента 22 MTJ в ячейке MC памяти в соответствии с первым вариантом осуществления соединен с битовой линией BL, а второй конец элемента 22 MTJ соединен с первым концом транзистора 23 ячейки. Второй конец транзистора 23 ячейки соединен с истоковой линией SL. Элемент 22 MTJ, использующий TMR (туннельный магниторезистивный) эффект, включает в себя стековую структуру, включающую в себя два ферромагнитных слоя F, P и немагнитный слой (пленку изолирования туннеля) B между ферромагнитными слоями F, P. Элемент 22 MTJ сохраняет цифровые данные в соответствии с изменением магнитного сопротивления, ассоциированным со спино-поляризованным туннельным эффектом. Элемент 22 MTJ может находиться в состоянии низкого сопротивления или в состоянии высокого сопротивления в зависимости от конфигурации намагниченности в двух ферромагнитных слоях F, P. Например, когда состояние низкого сопротивления определено как данные ʺ0ʺ, а состояние высокого сопротивления определено как данные ʺ1ʺ, 1-битовые данные могут быть записаны в элементе 22 MTJ. Естественно, состояние низкого сопротивления может быть определено как данные ʺ1ʺ, а состояние высокого сопротивлением может быть определено как данные ʺ0ʺ.

Например, элемент 22 MTJ сконфигурирован путем последовательной укладки фиксированного слоя (закрепленного слоя) P, туннельного барьерного слоя B, слоя записи (свободного слоя) F. Закрепленный слой Р и свободный слой F образованы из ферромагнитного вещества, а туннельный барьерный слой В образован из изолирующей пленки (например, Al2O3, MgO). Закрепленный слой P представляет собой слой, в котором направление конфигурации намагниченности является фиксированным, а направление конфигурации намагниченности в свободном слое F является переменным. Данные записываются в соответствии с направлением намагниченности.

Когда ток пропускается в направлении стрелки A1 во время записи, направление намагниченности в свободном слое F становится антипараллельным направлению намагниченности в закрепленном слое P (состояние AP), и элемент 22 MTJ устанавливается в состояние высокого сопротивления (данные ʺ1ʺ). Когда ток пропускается в направлении стрелки A2 во время записи, направления намагниченностей в закрепленном слое P и свободном слое F становятся параллельными друг другу (состояние P), и элемент 22 MTJ устанавливается в состояние низкого сопротивления (данные ʺ0ʺ). Таким образом, различные данные могут быть записаны в элемент MTJ в зависимости от направления пропускания тока.

<1-3> Конфигурация массива ячеек памяти

Далее, конфигурация массива ячеек памяти в соответствии с первым вариантом осуществления будет кратко описана с использованием фиг. 3-5.

Как показано на фиг. 3, массив 11 ячеек памяти включает в себя множество массивов 11a ячеек. Контроллеры 17 битовых линий и истоковых линий обеспечены вдоль противоположных концов каждого массива 11a ячеек вдоль направления Х. Два контроллера 17 битовых линий и истоковых линий, расположенные вдоль каждого массива 11а ячеек, используются для управления массивом 11a ячеек.

Кроме того, как показано на фиг. 3, драйвер 20 числовых линий обеспечен вдоль противоположных концов каждого массива 11а ячеек вдоль направления Y. Два драйвера 20 числовых линий, расположенные вдоль каждого массива 11a ячеек, используются для управления массивом 11a ячеек.

Затем, как показано на фиг. 4, контроллер 17 битовых линий и истоковых линий содержит схему 17а выбора битовой линии (CG_BL) и схему 17b выбора истоковой линии (CG_SL).

Схема 17а выбора битовой линии включает в себя переключающие транзисторы 24-1 до 24-n (n является целым числом, равным по меньшей мере 1) для избирательного соединения глобальной битовой линии GBL от драйвера 18 записи усилителя считывания до n локальных битовых линий LBL1-LBLn.

Кроме того, схема 17b выбора истоковой линии включает в себя переключающие транзисторы 26-1 до 26-n для избирательного соединения глобальной истоковой линии GSL от драйвера 18 записи усилителя считывания до n локальных истоковых линий LSL1-LSLn.

Выход от драйвера 20 числовых линий соединен с массивом 11a ячеек для активации числовой линии, соответствующей выбранной ячейке.

Схема 17а выбора битовой линии принимает выходной сигнал от декодера 16 столбцов. В схеме 17а выбора битовой линии на основе выходного сигнала, переключающий транзистор 24-i из n переключающих транзисторов 24-1 до 24-n, который связан с выбранной локальной битовой линией LBLi (i является целым числом, равным по меньшей мере 1), включается. Затем выбранная локальная битовая линия LBLi соединяется с глобальной битовой линией GBL и, таким образом, с драйвером 18 записи усилителя считывания.

Аналогично, схема 17b выбора истоковой линии принимает выходной сигнал от декодера 16 столбцов. В схеме 17b выбора истоковой линии, на основе выходного сигнала, переключающий транзистор 26-i из переключающих транзисторов 26-1 до 26-n, который связан с выбранной локальной истоковой линией LSLi, включается. Затем выбранная локальная истоковая линия LSLi соединяется с глобальной истоковой линией GSL и, таким образом, с драйвером 18 записи усилителя считывания.

Как показано на фиг. 5, схема 17a выбора битовой линии включает в себя схему 17B1 выбора столбца и схему 17B2 разгрузки (разрядки) битовой линии.

Схема 17B1 выбора столбца включает в себя транзисторы ячеек, 24-1 до 24-n, функционирующие как переключающие транзисторы 24-1 до 24-n. Выходной сигнал от декодера 16 столбцов вводится в электрод затвора каждого из транзисторов 24-1 дo 24-n, и глобальная битовая линия GBL соединяется с первым концом каждого из транзисторов ячеек, 24-1 до 24-n. Кроме того, со вторым концом каждого из транзисторов ячеек, 24-1 до 24-n, соединена соответствующая одна из локальных битовых линий LBL1-LBLn.

Схема 17B2 разгрузки битовой линии включает в себя транзисторы 25 сброса, каждый из которых расположен между соответствующим одним из транзисторов ячеек, 24-1 до 24-n, и соответствующей одной из локальных битовых линий LBL1-LBLn. Схема 17B2 разгрузки битовой линии соединяет локальную битовую линию LBL с потенциалом заземления (VSS) на основе сигнала сброса от декодера 16 столбцов. В частности, выходной сигнал от декодера 16 столбцов подается на затвор транзистора 25 сброса. Кроме того, одна из локальных битовых линий LBL1-LBLn подключена к первому концу транзистора 25 сброса, а второй конец транзистора 25 сброса соединен с потенциалом заземления.

Кроме того, как показано на фиг. 5, схема 17b выбора истоковой линии включает в себя схему 17S1 выбора столбца и схему 17S2 разгрузки истоковой линии.

Схема 17S1 выбора столбца включает в себя транзисторы ячеек, 26-1 до 26-n, функционирующие как переключающие транзисторы 26-1 до 26-n. Выходной сигнал от декодера 16 столбцов вводится в электрод затвора каждого из транзисторов ячеек, 26-1 до 26-n, и глобальная истоковая линия GSL соединяется с первым концом каждого из транзисторов ячеек, 26-1 до 26-n. Кроме того, со вторым концом каждого из транзисторов ячеек, 26-1 до 26-n, соединяется соответствующая одна из локальных истоковых линий LSL1-LSLn.

Схема 17S2 разгрузки истоковой линии включает в себя транзисторы 27 сброса, каждый из которых расположен между соответствующим одним из транзистора ячейки, 26-1 до 26-n, и соответствующей одной из локальных истоковых линий LSL1-LSLn. Схема 17S2 разгрузки истоковой линии соединяет локальную истоковую линию LSL с потенциалом заземления на основе сигнала сброса от декодера 16 столбцов. В частности, выходной сигнал от декодера 16 столбцов подается на затвор транзистора 27 сброса. Кроме того, одна из локальных истоковых линий LSL1-LSLn соединена с первым концом транзистора 27 сброса, а второй конец транзистора 27 сброса соединен с потенциалом заземления.

<1-4> Конфигурация усилителя считывания

Усилитель считывания в соответствии с настоящим вариантом осуществления будет описан с использованием фиг. 6 и фиг. 7. Ниже будет описан только усилитель 18a считывания драйвера 18 записи усилителя считывания.

Как показано на фиг. 6, усилитель 18а считывания соединен с ячейкой МС памяти через глобальную битовую линию GBL. Кроме того, усилитель 18а считывания соединен с опорной схемой (RREF) 30 через опорную глобальную битовую линию RGBL. Опорная схема 30 включает в себя, например, резистивный элемент 30а.

Как показано на фиг. 7, усилитель 18а считывания включает в себя преобразователь 181, который преобразует значение сопротивления для ячейки МС памяти и опорной схемы 30 в значения тока, и усилитель 180, который сравнивает и усиливает два выходных сигнала, выведенных из преобразователя 181.

Усилитель 180 включает в себя PMOS-транзисторы 180a, 180b, 180c и 180d и NMOS-транзисторы 180e, 180f, 180g и 180h. Кроме того, преобразователь 181 включает в себя NMOS-транзисторы 181a, 181b, 181c, 181d, 181e, 181f, 181g и 181h.

<1-4-l> Конкретная схемная конфигурация усилителя

Далее будет описан усилитель 180. Источник питания (Vdd) приложен к истоку PMOS-транзистора 180a. Сток PMOS-транзистора 180а соединен с узлом N1. Сигнал ʺSEN1ʺ подается на затвор PMOS-транзистора 180a. Источник питания (Vdd) приложен к истоку PMOS-транзистора 180b. Сток PMOS-транзистора 180a соединен с узлом N2. Сигнал ʺSEN1ʺ подается на затвор PMOS-транзистора 180b. Исток PMOS-транзистора 180c соединен с узлом N3, к которому приложен источник питания (Vdd). Сток PMOS-транзистора 180с соединен с узлом N1. Затвор PMOS-транзистора 180с соединен с узлом N2. Исток PMOS-транзистора 180d соединен с узлом N3, к которому приложен источник питания (Vdd). Сток PMOS-транзистора 180d соединен с узлом N2. Затвор PMOS-транзистора 180d соединен с узлом N1. Сток NMOS-транзистора 180e соединен с узлом N1. Исток NMOS-транзистора 180e соединен с узлом 4 (MCEL). Затвор NMOS-транзистора 180е соединен с узлом N2. Сток NMOS-транзистора 180f соединен с узлом N2. Исток NMOS-транзистора 180f соединен с узлом 6 (MREF). Затвор NMOS-транзистора 180f соединен с узлом N1. Сток NMOS-транзистора 180g соединен с узлом N. Исток NMOS-транзистора 18Og связан с потенциалом заземления (Vss). Затвор NMOS-транзистора 180g соединен с узлом 5, в который вводится сигнал ʺSEN2ʺ. Сток NMOS-транзистора 180h соединен с узлом N6. Исток NMOS-транзистора 180h соединен с потенциалом заземления (Vss). Затвор NMOS-транзистора 180h соединен с узлом 5.

<1-4-2> Конкретная схемная конфигурация преобразователя

Далее будет описан преобразователь 181. Сток NMOS-транзистора 181a (ограничительного транзистора) соединен с узлом N4. Исток NMOS-транзистора 181а соединен с узлом N7 (CCEL). Ограничительный сигнал ʺVCLAMPʺ подается на затвор NMOS-транзистора 181a. Сток NMOS-транзистора 181g (транзистора разрешения считывания) соединен с узлом N7. Исток NMOS- транзистора 181g соединен с глобальной битовой линией GBL через узел N8. Сигнал ʺRENʺ подается на затвор NMOS-транзистора 181g.

Сток NMOS-транзистора 181c (транзистора разрешения считывания) соединен с узлом N4. Исток NMOS-транзистора 181c соединен с узлом N9 (NCEL). Сигнал ʺRENʺ вводится в затвор NMOS-транзистора 181c. Сток NMOS-транзистора 181e (ограничительного транзистора) соединен с узлом N9. Исток NMOS-транзистора 181е соединен с глобальной битовой линией GBL через узел N8. Сигнал ʺVCLAMPʺ подается на затвор NMOS-транзистора 181e.

Сток NMOS-транзистора 181b (ограничительного транзистора) соединен с узлом N6. Исток NMOS-транзистора 181b соединен с узлом N10 (CREF). Сигнал ʺVREFʺ подается на затвор NMOS-транзистора 181b. Сток NMOS-транзистора 181h (транзистора разрешения считывания) соединен с узлом N10. Исток NMOS-транзистора 181h соединен с опорной глобальной битовой линией RGBL через узел N11. Сигнал ʺRENʺ подается на затвор NMOS-транзистора 181h.

Сток NMOS-транзистора 181d (ограничительного транзистора) соединен с узлом N6. Исток NMOS-транзистор 181d соединен с узлом N12 (NREF). Сигнал ʺRENʺ подается на затвор NMOS-транзистора 181d. Сток NMOS-транзистора 181f (транзистора разрешения считывания) соединен с узлом N12. Исток NMOS-транзистора 181f соединен с опорной глобальной битовой линией RGBL через узел N11. Сигнал ʺVREFʺ подается на затвор NMOS-транзистора 181f.

Как описано выше, в преобразователе 181, два пути тока формируются параллельно между глобальной битовой линией GBL и усилителем 180 во время операции считывания. Кроме того, в преобразователе 181, два пути тока формируются параллельно между опорной глобальной битовой линией RGBL и усилителем 180 во время операции считывания.

Два пути тока между глобальной битовой линией GBL и усилителем 180 сконфигурированы таким образом, что положения ограничительного транзистора и транзистора разрешения считывания в одном пути тока противоположны положениям ограничительного транзистора и транзистора разрешения считывания в другом пути тока. Аналогично, два пути тока между опорной глобальной битовой линией RGBL и усилителем 180 сконфигурированы таким образом, что положения ограничительного транзистора и транзистора разрешения считывания в одном пути тока противоположны положениям ограничительного транзистора и транзистора разрешения считывания в другом пути тока. Ниже будет описано, почему ограничительные транзисторы и транзисторы разрешения считывания расположены между глобальной битовой линией GBL и усилителем 180, а также между опорной глобальной битовой линией RGBL так, чтобы образовать два пути тока.

<1-4-2-1> Размер транзистора

Далее будут описаны размеры ограничительных транзисторов и транзисторов разрешения считывания, предусмотренных в преобразователе 181 в соответствии с настоящим вариантом осуществления. В настоящем варианте осуществления, размерное соотношение между NMOS-транзисторами 181a и 181e составляет (1-N):N (0≤N≤1). Кроме того, размерное соотношение между NMOS-транзисторами 181g и 181c равно (1-N):N. Более того, размерное соотношение между NMOS-транзисторами 181b и 181f равно (1-N):N. Кроме того, размерное соотношение между NMOS-транзисторами 181h и 181d равно (1-N):N.

Далее будет кратко описана конфигурация транзистора. Транзистор включает в себя область диффузии примеси (исток или сток), обеспеченную в полупроводниковой подложке, изолирующую пленку затвора, обеспеченную в области, расположенной на канале, который сформирован в полупроводниковой подложке и окружен областью диффузии примеси, и электрод затвора, обеспеченный на изолирующей пленке затвора. В этом отношении, длина области диффузии примеси вдоль направления, ортогонального направлению, в котором сформирован канал, определяется как ширина W транзистора.

В этом случае, ширина W NMOS-транзистора 181a равна W=W0×(1-N) (W0 является положительным числом), а ширина W NMOS-транзистора 181e равна W=W0×N. Аналогичное соотношение существует между вышеописанными другими транзисторами. Другими словами, вышеописанный ʺразмер транзистораʺ является синонимом ширины W транзистора.

NMOS-транзистор 181a не обязательно должен быть одиночным транзистором, но может включать в себя множество транзисторов. Другими словами, соотношение между общей шириной W множества транзисторов, содержащихся в NMOS-транзисторе 181a, и общей шириной W множества транзисторов, обеспеченных в NMOS-транзисторе 181е, может быть (1-N):N. Это также относится к другим транзисторам, предусмотренным в преобразователе 181.

В вышеприведенном описании, размерное соотношение между NMOS-транзисторами 181a и 181e, размерное соотношение между NMOS-транзисторами 181g и 181c, размерное соотношение между NMOS-транзисторами 181b и 181f и размерное соотношение между NMOS-транзисторами 181h и 181d аналогичны. Однако размерное соотношение между NMOS-транзисторами 181a и 181e, размерное соотношение между NMOS-транзисторами 181g и 181c, размерное соотношение между NMOS-транзисторами 181b и 181f и размерное соотношение между NMOS-транзисторами 181h и 181d могут отличаться друг от друга.

Желательно, с учетом эффектов, описанных ниже, чтобы размерное соотношение между NMOS-транзисторами 181a и 181e, размерное соотношение между NMOS-транзисторами 181g и 181c, размерное соотношение между NMOS-транзисторами 181b и 181f и размерное соотношение между NMOS-транзисторами 181h и 181d были аналогичными.

<1-4-2-2> Пример топологии преобразователя

Далее будет описана топология в случае, когда ограничительные транзисторы и транзисторы разрешения считывания включают в себя множество транзисторов. Конкретный пример топологии преобразователя 181 будет описан с использованием фиг. 8. На фиг. 8, межслойная изолирующая пленка и тому подобное опущены для упрощения.

Например, NMOS-транзисторы 181a, 181b, 181c, 181d, 181e, 181f, 181g и 181h согласно настоящему варианту осуществления включают в себя, каждый, множество транзисторов.

Как показано на фиг. 8, NMOS-транзистор 181a включает в себя пять транзисторов TCP1-TCP5. NMOS-транзистор 181е включает в себя пять транзисторов TCP6-TCP10.

Транзисторы TCP1-TCP10 представляют собой транзисторы с аналогичными размерами или свойствами.

NMOS-транзистор 181c включает в себя пять транзисторов TCN1-TCN5. NMOS-транзистор 181g включает в себя пять транзисторов TCN6-TCN10. Транзисторы TCN1-TCN10 представляют собой транзисторы с аналогичными размерами или свойствами.

Как показано на фиг. 8, NMOS-транзистор 181b включает в себя пять транзисторов TRF1-TRF5. NMOS-транзистор 181f включает в себя пять транзисторов TRF6-TRF10. Транзисторы TRF1-TRF10 представляют собой транзисторы с аналогичными размерами или свойствами.

NMOS-транзистор 181d включает в себя пять транзисторов TRN1-TRN5. NMOS-транзистор 181h включает в себя пять транзисторов TRN6-TRN10. Транзисторы TRN1-TRN10 представляют собой транзисторы с аналогичными размерами или свойствами.

Транзисторы TCP1-TCP10, TCN1-TCN10, TRF1-TRF10 и TRN1-TRN10 включают в себя, каждый, область диффузии примеси (исток или сток), обеспеченную в полупроводниковой подложке, изолирующую пленку затвора, обеспеченную в области, расположенной на полупроводниковой подложке и окруженной областью диффузии примеси, и в которой образован канал, и электрод затвора, обеспеченный на изолирующей пленке затвора. Транзисторы соединены с соответствующими узлами через контакты, обеспеченные на области диффузии примеси. Кроме того, узлы и электроды затвора соединены с соответствующими шинами через контакты, не изображенные на чертежах.

Например, отношения соединений между транзисторами TCP1-TCP10, TCN1-TCN10, TRF1-TRF10 и TRN1-TRN10 показаны на фиг. 9. В частности, как показано на фиг. 9, NMOS-транзистор 181a включает в себя шесть транзисторов TCP1-TCP6. NMOS-транзистор 181е включает в себя четыре транзистора TCP7-TCP10. NMOS-транзистор 181c включает в себя четыре транзистора TCN1-TCN4. NMOS-транзистор 181g включает в себя шесть транзисторов TCN5-TCN10. NMOS-транзистор 181b включает в себя шесть транзисторов TRF1-TRF6. NMOS-транзистор 181f включает в себя четыре транзистора TRF7-TRF10. NMOS-транзистор 181d включает в себя четыре транзистора TRN1-TRN4. NMOS-транзистор 181h включает в себя шесть транзисторов TRN5-TRN10.

Как описано выше, в настоящем варианте осуществления могут быть внесены различные изменения в отношения соединений между транзисторами TCP1-TCP10, TCN1-TCN10, TRF1-TRF10 и TRN1-TRN10. Кроме того, различные изменения отношений соединения могут быть выполнены просто путем изменения топологии одного слоя (слоя межсоединений), и, таким образом, изменения могут быть выполнены по мере необходимости. Причина, по которой вносятся изменения в отношения соединения между транзисторами, будет описана ниже.

<1-5> Операция считывания

Базовая операция считывания в полупроводниковом запоминающем устройстве в соответствии с настоящим вариантом осуществления будет описана с использованием фиг. 10. Фиг. 10 иллюстрирует случай, когда данные ʺ0ʺ считываются в течение периода между временем Т0 и временем Т5, и случай, когда данные ʺ1ʺ считываются в течение периода, начинающегося со времени Т6. В операции считывания, описанной ниже, контроллер 12 управляет сигналами.

[Время Т0]

В момент времени T0, контроллер 12 устанавливает уровни сигналов ʺRENʺ, ʺSENʺ и ʺSEN2ʺ на уровень ʺL (Низкий)ʺ и устанавливает сигналы ʺVCLAMPʺ и ʺVREFʺ на уровень ʺH (Высокий)ʺ. В этом отношении, уровень ʺLʺ представляет собой напряжение, которое устанавливает NMOS-транзистор в выключенное состояние, при этом устанавливая PMOS-транзистор во включенное состояние. Кроме того, уровень ʺHʺ представляет собой напряжение, которое устанавливает PMOS-транзистор в выключенное состояние, при этом устанавливая NMOS-транзистор во включенное состояние.

Таким образом, PMOS-транзисторы 180a и 180b и NMOS-транзисторы 180e, 180f, 181a, 181b, 181e и 181f устанавливаются во включенное состояние. Кроме того, PMOS-транзисторы 180c и 180d и NMOS-транзисторы 180g, 180h, 181c, 181d, 181g и 181h устанавливаются в выключенное состояние.

[Время T1]

Во время T1, контроллер 12 повышает уровень сигнала ʺRENʺ от уровня ʺLʺ до уровня ʺHʺ. Это устанавливает NMOS-транзисторы 181c и 181g во включенное состояние, чтобы позволить току ячейки (Icell) протекать от усилителя 18a считывания в ячейку МС памяти. Кроме того, NMOS-транзисторы 181d и 181h устанавливаются во включенное состояние, чтобы позволить опорному току (Iref) протекать от усилителя 18a считывания к опорной схеме 30.

[Время T2]

Во время T2, когда разность между током ячейки (Icell) и опорным током (Iref), как ожидается, достаточна для обнаружения усилителем 180, контроллер 12 повышает уровень сигнала ʺSEN1ʺ от уровня ʺLʺ до уровня ʺHʺ.

Это устанавливает PMOS-транзисторы 180a и 180b в выключенное состояние. Таким образом, ток ячейки (Icell) обуславливает вытягивание заряда из узла N1, а опорный ток (Iref) обуславливает вытягивание заряда из узла N2. В это время разность между сигналом ʺbSOʺ и сигналом ʺSOʺ усиливается в усилителе 180.

Когда данные, хранящиеся в ячейке МС памяти, являются данными ʺ0ʺ, сопротивление уменьшается, увеличивая ток ячейки (Icell) выше опорного тока (Iref). Таким образом, в момент T2 из узла N1 вытягивается больше заряда, чем из узла N2. В результате, PMOS-транзистор 180d устанавливается во включенное состояние, а NMOS-транзистор 180f устанавливается в выключенное состояние, вызывая прикладывание напряжения к узлу N2 через узел N3. Следовательно, узел N2 устанавливается на уровень ʺHʺ, PMOS-транзистор 180c устанавливается в выключенное состояние, и NMOS-транзистор 180e устанавливается во включенное состояние.

[Время T3]

Во время T3, контроллер 12 повышает уровень сигнала ʺSEN2ʺ от уровня ʺLʺ до уровня ʺHʺ.

Это устанавливает NMOS-транзисторы 180g и 180h во включенное состояние, чтобы установить узел N4 и узел N6 на потенциал заземления. Как описано выше, NMOS-транзистор 180e устанавливается во включенное состояние, а NMOS-транзистор 180f устанавливается в выключенное состояние. Таким образом, узел N1 соединяется с потенциалом заземления, и заряд вытягивается из узла N1. Следовательно, сигналы ʺbSOʺ и ʺSOʺ, усиленные на основе данных, фиксируются буфером страницы, не изображенным на чертежах.

[Время T4 и время T5]

В течение периода от времени T4 до времени T5, контроллер 12 понижает уровни сигналов ʺRENʺ, ʺSEN1ʺ и ʺSEN2ʺ от уровня ʺΉʺ до уровня ʺLʺ. Это запускает операцию зарядки узла N1 и узла N2.

[Время T6 до времени T9]

Операция контроллера 12 между временем T6 и временем T9 аналогична описанной выше операции между временем T1 и временем T4 и поэтому не будет описываться.

<1-5-1> Относительно сигнала ʺVCLAMPʺ во время операции считывания

Далее будет описан шум, воздействию которого подвергается сигнал ʺVCLAMPʺ во время вышеописанной операции считывания. Шум, воздействию которого подвергается сигнал ʺVREFʺ во время операции считывания, аналогичен шуму, воздействию которого подвергается сигнал ʺVCLAMPʺ, и поэтому не будет описываться.

Как описано выше, преобразователь 181 в соответствии с настоящим вариантом осуществления имеет два пути тока между усилителем 180 и глобальной битовой линией GBL.

<1-5-2> Сравнительный пример 1

Шум, воздействию которого подвергается сигнал ʺVCLAMPʺ, когда NMOS-транзисторы 181c и 181e не работают во время операции считывания (сравнительный пример 1), будет описан с использованием фиг. 11.

Как показано на фиг. 11, во время операции считывания, когда контроллер 12 увеличивает сигнал ʺRENʺ от уровня ʺLʺ до уровня ʺHʺ, NMOS-транзисторы 181a и 181g образуют путь тока. Заряд, сохраненный в узле N4, вытягивается в глобальную битовую линию GBL. Таким образом, потенциалы узла N4 и узла N7 снижаются.

Это снижает сигнал ʺVCLAMPʺ через емкостную связь между затвором и истоком и между затвором и стоком NMOS-транзистора 181a.

NMOS-транзистор 181a является транзистором, который подает ток в глобальную битовую линию GBL. Сигнал ʺVCLAMPʺ определяет ток, который должен подаваться в глобальную битовую линию GBL, и поэтому нежелательно, чтобы напряжение изменялось из-за шума. Уровень сигнала ʺVCLAMPʺ во время операции считывания желательным образом соответствует такому напряжению, как изображено пунктирной линией на фиг. 11.

Как описано выше, когда NMOS-транзисторы 181c и 181e не работают во время операции считывания, сигнал ʺVCLAMPʺ снижается из-за шума.

<1-5-3> Сравнительный пример 2

Далее будет описан шум, воздействию которого подвергается сигнал ʺVCLAMPʺ, когда NMOS-транзисторы 181a и 181g не работают во время операции считывания (сравнительный пример 2), с использованием фиг. 12.

Как показано на фиг. 12, во время операции считывания, когда контроллер 12 повышает сигнал ʺRENʺ от уровня ʺLʺ до уровня ʺHʺ, NMOS-транзисторы 181c и 18le образуют путь тока. Заряд, сохраненный в узле N4, вытягивается в глобальную битовую линию GBL. Таким образом, потенциалы узла N9 и узла N8 возрастают.

Это повышает сигнал ʺVCLAMPʺ через емкостную связь между затвором и истоком и между затвором и стоком NMOS-транзистора 181е.

Как описано выше, когда NMOS-транзисторы 181a и 18lg не работают во время операции считывания, сигнал ʺVCLAMPʺ повышается из-за шума.

<1-5-4> Соотношение между размером транзистора и шумом, воздействию которого подвергается сигнал ʺVCLAMPʺ

Далее будет описан шум, воздействию которого подвергается сигнал ʺVCLAMPʺ, когда NMOS-транзисторы 181a, 181c, 181e и 181g работают во время операции считывания, с использованием фиг. 13.

Фиг. 13 изображает форму волны напряжения, полученную посредством моделирования, в котором NMOS-транзисторы 181a и 18le имеют одинаковое отношение длины канала и ширины канала (1-N):N (0≤N≤1), и в котором NMOS-транзисторы 181c и 181g имеют одинаковое отношение длины канала и ширины канала (1-N):N, при изменяющемся числовом значении N.

Как показано на фиг. 13, транзисторы в преобразователе 181 расположены так, чтобы формировать два пути тока, соединяющие усилитель 180 и глобальную битовую линию GBL вместе, и ширины каналов транзисторов регулируются, чтобы обеспечить уменьшение шума, воздействию которого подвергается сигнал ʺVCLAMPʺ.

Хотя длины каналов и ширины каналов транзисторов не указаны, NMOS-транзисторы 181a и 181e желательным образом имеют одинаковое отношение длины канала и ширины канала (1-N):N (0≤N≤1), как иллюстрируется в этом примере. Кроме того, NMOS-транзисторы 181c и 181g имеют одинаковое отношение длины канала и ширины канала (1-N):N. Кроме того, отношение ширины канала NMOS-транзисторов 181a и 181e является таким же, как отношение ширины канала NMOS-транзисторов 181c и 181g.

Как описано для фиг. 8 и фиг. 9, вышеописанные результаты моделирования могут быть получены путем изменения схемы межсоединений для каждого транзистора на этапе проектирования.

Вышеприведенное описание также относится к NMOS-транзисторам 181b, 181d, 181f и 181h.

Это позволяет по мере необходимости снижать шум, воздействию которого подвергаются сигнал ʺVCLAMPʺ и сигнал ʺVREFʺ.

<1-6> Полезные эффекты

В соответствии с вышеописанным вариантом осуществления, в преобразователе 181, транзисторы расположены так, чтобы формировать два пути тока, соединяющих усилитель 180 и глобальную битовую линию GBL вместе для регулировки ширины каналов транзисторов.

Во время операции считывания повышение сигнала ʺRENʺ изменяет потенциалы стока и истока ограничительного транзистора. В результате сигналы ʺVCLAMPʺ и ʺVREFʺ изменяются посредством емкостной связи между затвором и истоком и между затвором и стоком NMOS-транзистора 181е. Изменение сигналов ʺVCLAMPʺ и ʺVREFʺ неблагоприятно увеличивает или уменьшает ток ячейки или опорный ток (см. сравнительные примеры 1 и 2, описанные выше).

В полупроводниковом устройстве хранения, которое использует магниторезистивные элементы в качестве ячеек памяти, большой ток ячейки экспоненциально увеличивает вероятность нарушения считывания, а малый ток ячейки увеличивает время, необходимое для формирования сигнала ячейки, тем самым увеличивая время считывания. Следовательно, шум подавляется, чтобы делать приложенное напряжение равным заданному значению, чтобы обеспечить возможность сдерживания вероятности нарушения считывания и увеличения времени считывания.

В качестве способа решения вышеописанной задачи, предлагается сравнительный пример 3, как показано на фиг. 14. Преобразователь 183 в сравнительном примере 3 снабжен емкостями 183e и 183f между узлом N3a и узлом, в который вводится сигнал ʺVCLAMPʺ. Это предназначено для вышеописанного подавления шума, воздействию которого подвергаются сигналы ʺVCLAMPʺ и ʺVREFʺ.

Как описано в сравнительном примере 2, когда нет транзисторов, соответствующих NMOS-транзисторам 181a и 181g, сигнал ʺVCLAMPʺ повышается по мере увеличения сигнала ʺRENʺ.

Емкости 183e и 183f действуют в направлении, в котором сигнал ʺVCLAMPʺ снижается по мере повышения сигнала ʺRENʺ. Таким образом, емкости 183e и 183f сдерживают повышение до некоторой степени (см. фиг. 15). Емкости 183g и 183h, изображенные на фиг. 4, аналогичным образом сдерживают повышение сигнала ʺVREFʺ до некоторой степени.

Однако этот метод шумоподавления требует дополнительных емкостей, что неблагоприятным образом увеличивает площадь.

В усилителе считывания, ограничительные транзисторы являются наиболее чувствительными и наиболее восприимчивыми к шуму, и шум, принимаемый ограничительными транзисторами, должен быть подавлен в достаточной степени. Таким образом, ограничительные транзисторы больше по площади, чем другие транзисторы. Например, размер ограничительных транзисторов 183c и 183d эквивалентен примерно 90% всей площади усилителя считывания.

Чтобы иметь достаточную возможность подавления шума, емкости 183e, 183f, 183g и 183h должны иметь больший размер, чем ограничительные транзисторы. На фиг. 15, площадь емкостей 183e, 183f, 183g и 183h эквивалентна площади ограничительных транзисторов 183c и 183d. Однако даже это не позволяет добиться достаточного шумоподавления. Чтобы добиться достаточного шумоподавления, емкости 183e, 183f, 183g и 183h должны иметь площадь, приблизительно в 10 раз большую, чем площадь ограничительных транзисторов 183c и 183d. Это оказывает большое влияние на площадь чипов.

Однако преобразователь 181 в соответствии с вышеописанным настоящим вариантом осуществления не должен обязательно иметь дополнительные емкости в отличие от сравнительного примера 3. В настоящем варианте осуществления, если сумма площадей ограничительных транзисторов 181a и 181b равна площади ограничительного транзистора 183с, могут быть получены эффекты вышеописанного настоящего варианта осуществления. Кроме того, хотя транзисторы расположены так, чтобы формировать два пути тока между усилителем 180 и глобальной битовой линией GBL, увеличение количества шин не оказывает большого влияния на площадь чипа. Таким образом, по сравнению со сравнительным примером 3, настоящий вариант осуществления может обеспечить полупроводниковое запоминающее устройство, которое может в достаточной степени подавить шум, воздействию которого подвергаются сигналы ʺVCLAMPʺ и ʺVREFʺ, сдерживая при этом увеличение площади схемы.

Кроме того, трудно предоставить больше емкостей с большими площадями, чем необходимо в полупроводниковом запоминающем устройстве, площадь чипа которого должна быть уменьшена. Таким образом, способ в сравнительном примере 3 уменьшает диапазон регулировки шума. В настоящем варианте осуществления, преобразователь 181 конструируется с использованием множества малых транзисторов во время компоновки, и, таким образом, шум может быть отрегулирован детально и в широком диапазоне.

(Второй вариант осуществления)

Второй вариант осуществления будет описан с использованием фиг. 16. Во втором варианте осуществления будет описан случай, когда в вышеописанном усилителе 180 предусмотрены новые транзисторы. Базовая конфигурация и функционирование запоминающего устройства в соответствии со вторым вариантом осуществления аналогичны базовой конфигурации и работе запоминающего устройства в соответствии с вышеописанным первым вариантом осуществления. Таким образом, материал, описанный выше в первом варианте осуществления, и материал, легко выводимый из вышеописанного первого варианта осуществления, не будет описываться.

<2-1> Конфигурация усилителя считывания

Усилитель считывания в соответствии с настоящим вариантом осуществления будет описан с использованием фиг. 16.

Как показано на фиг. 16, усилитель 18а считывания включает в себя преобразователь 181 и усилитель 184, который сравнивает и усиливает два выходных сигнала, выводимых из преобразователя 181.

Усилитель 184 включает в себя PMOS-транзисторы 180a, 180b, 180c, 180d, 180i и 180j и NMOS-транзисторы 180e, 180f, 180g и 180h.

Напряжение Vdd источника питания прикладывается к истоку PMOS-транзистора 180i. Сток PMOS-транзистора 180i соединен с узлом N3. Сигнал ʺbSEN2 (инвертированный сигнал SEN2)ʺ подается на затвор PMOS-транзистора 180i. Исток PMOS-транзистора 180j соединен с узлом N1. Сток PMOS-транзистора 180j соединен с узлом N2. Сигнал ʺSEN1ʺ подается на затвор PMOS-транзистора 180j.

<2-2> Полезные эффекты

В соответствии с настоящим вариантом осуществления, усилитель 184 снабжен PMOS-транзистором 180i. Это позволяет осуществлять отсоединение источника питания от схемы-защелки, содержащий PMOS-транзисторы 180c и 18Od и NMOS-транзисторы 180e и 180f, пока ʺSEN2ʺ не будет установлен на уровень ʺHʺ. Это позволяет предотвратить ситуацию, когда до тех пор, пока сигналы ʺbSOʺ и ʺSOʺ не будут достаточно усилены, часть схемы-защелки работает, чтобы зафиксировать некорректные данные. Таким образом, настоящий вариант осуществления эффективен для подавления ошибок считывания.

Кроме того, обеспечение PMOS-транзистора 180j позволяет устанавливать напряжения сигналов ʺbSOʺ и ʺSOʺ одинаковыми путем короткого замыкания сигналов ʺbSOʺ и ʺSOʺ до момента, предшествующего установке сигнала ʺSEN1ʺ на уровень ʺHʺ, чтобы начать операцию усиления. Например, когда выходные напряжения отличаются друг от друга перед операцией усиления, может произойти ошибка считывания. Таким образом, настоящий вариант осуществления эффективен для подавления ошибок считывания.

Описан усилитель 184, снабженный как PMOS-транзистором 180i, так и PMOS-транзистором 180j. Однако настоящее изобретение не ограничивается этим. В частности, любой из них может быть удален.

(Третий вариант осуществления)

Третий вариант осуществления будет описан с использованием фиг. 17. В третьем варианте осуществления будет описан случай, когда в вышеописанном преобразователе 181 обеспечены новые транзисторы. Базовая конфигурация и функционирование запоминающего устройства в соответствии с третьим вариантом осуществления аналогичны базовой конфигурации и работе запоминающего устройства в соответствии с вышеописанным первым вариантом осуществления. Таким образом, материал, описанный выше в первом варианте осуществления, и материал, легко выводимый из вышеописанного первого варианта осуществления, не будут описываться.

<3-1> Конфигурация усилителя считывания

Усилитель считывания в соответствии с настоящим вариантом осуществления будет описан с использованием фиг. 17.

Как показано на фиг. 17, усилитель 18а считывания включает в себя преобразователь 185 и усилитель 180.

Преобразователь 185 включает в себя NMOS-транзисторы 181a, 181b, 181c, 181d, 181e, 181f, 181g и 180h и PMOS-транзисторы 181i, 181j, 181k и 181l.

Исток PMOS-транзистора 181i соединен с узлом N13, к которому приложено напряжение Vdd источника питания. Сток PMOS-транзистора 181i соединен с узлом N4. Сигнал ʺRENʺ подается на затвор PMOS-транзистор 181i. Исток PMOS-транзистора 181j соединен с узлом N13, к которому приложено напряжение Vdd источника питания. Сток PMOS-транзистора 181j соединен с узлом N6. Сигнал ʺRENʺ подается на затвор PMOS-транзистора 181j. Исток PMOS-транзистора 181k соединен с узлом N13, к которому приложено напряжение Vdd источника питания. Сток PMOS-транзистора 181k соединен с узлом N7. Сигнал ʺRENʺ подается на затвор PMOS-транзистора 181k. Исток PMOS-транзистора 181l соединен с узлом N13, к которому приложено напряжение Vdd источника питания. Сток PMOS-транзистора 1811 соединен с узлом N10. Сигнал ʺRENʺ подается на затвор PMOS-транзистора 181l.

<3-2> Операции

После завершения считывания данных, контроллер 12 устанавливает сигнал ʺRENʺ на уровень ʺLʺ, чтобы установить PMOS-транзисторы 181i, 181j, 181k и 181l во включенное состояние, тем самым заряжая узлы преобразователя 185.

Например, когда PMOS-транзисторы 181i, 181j, 181k и 181l не предусмотрены, узел N4 заряжается через PMOS-транзистор 180a и NMOS-транзистор 180e после завершения считывания. В этом случае, NMOS-транзистор 180e постепенно переходит в режим работы в подпороговой области. Таким образом, требуется много времени для зарядки узла N4. Узел N7 заряжается через PMOS-транзистор 180a и NMOS-транзисторы 180e и 181a. В этом случае, NMOS-транзисторы 180e и 181a постепенно переходят к работе в подпороговой области. Таким образом, требуется гораздо больше времени для зарядки узла N7, чем для зарядки узла N4. Это также относится к узлу N6 и узлу N10.

Если операция считывания запускается перед тем, как узлы N4, N6, N7 и N10 полностью заряжены, формы сигналов узлов отличаются от их форм сигналов в последней операции считывания. В результате, эффект, влияющий на сигнал ʺVCLAMPʺ посредством емкостной связи, также изменяется. Это приводит к ухудшению эффекта уменьшения шума при обеспечении двух путей тока, как описано в первом варианте осуществления.

<3-3> Полезные эффекты

Таким образом, как описано выше, преобразователь 185 снабжен PMOS-транзисторами 181i, 181j, 181k и 181l для обеспечения операции зарядки по пути, отличному от пути с NMOS-транзисторами 180e, 180f, 181a и 181b. Другими словами, операция зарядки для узлов N4, N6, N7 и N10 может быть выполнена с высокой скоростью после завершения операции считывания. Другими словами, временные интервалы между операциями считывания могут быть уменьшены. В результате, операция считывания может быть осуществлена с большей скоростью.

В описанном выше варианте осуществления, преобразователь 185 снабжен PMOS-транзисторами 181i, 181j, 181K и 181l. Однако либо набор PMOS-транзисторов 181i и 181j, либо набор PMOS-транзисторов 181k и 181l может быть удален.

Кроме того, как показано на фиг. 18, усилитель 184 во втором варианте осуществления и преобразователь 185 в третьем варианте осуществления могут быть объединены вместе.

(Четвертый вариант осуществления)

Четвертый вариант осуществления будет описан с использованием фиг. 19. В четвертом варианте осуществления будет описан случай, когда четыре ограничительных транзистора управляются с использованием одного сигнала. Базовая конфигурация и работа запоминающего устройства в соответствии с четвертым вариантом осуществления аналогичны базовой конфигурации и работе запоминающего устройства в соответствии с вышеописанным первым вариантом осуществления. Таким образом, материал, описанный выше в первом варианте осуществления, и материал, легко выводимый из вышеописанного первого варианта осуществления, не будет описываться.

<4-1> Конфигурация усилителя считывания

Усилитель считывания в соответствии с настоящим вариантом осуществления будет описан с использованием фиг. 19.

Как показано на фиг. 19, усилитель 18а считывания включает в себя преобразователь 186 и усилитель 180.

Преобразователь 186 включает в себя NMOS-транзисторы 181a, 181c, 181d, 181e, 181g, 180h, 181m и 181n.

Сток NMOS-транзистора 181m (ограничительного транзистора) соединен с узлом N6. Исток NMOS-транзистора 181m соединен с узлом N1O (CREF). Сигнал ʺVCLAMPʺ подается на затвор NMOS-транзистора 181m. Сигнал ʺVCLAMPʺ является тем же самым, что и сигнал, поступающий на затворы NMOS-транзисторов 181a и 181e. Сток NMOS-транзистора 181n (ограничительного транзистора) соединен с узлом N12 (NREF). Исток NMOS-транзистора 181n соединен с узлом N11. Сигнал ʺVCLAMPʺ подается на затвор NMOS-транзистора 181n.

Как описано выше, преобразователь 186 в соответствии с настоящим вариантом осуществления использует сигнал ʺVCLAMPʺ для управления ограничительными транзисторами 181a и 181e, которые управляют током ячейки, и ограничительными транзисторами 181m и 181n, которые управляют опорным током. Сигнал, подаваемый на затворы ограничительных транзисторов 181m и 181n, отличается от сигнала, подаваемого на затворы ограничительных транзисторов 181b и 181f, описанных в первом варианте осуществления. Однако эти транзисторы имеют сходные структуры.

<4-2> Температурное свойство

Температурное свойство ячейки МС памяти и температурное свойство опорной схемы 30 не обязательно являются одинаковыми. Например, когда опорная схема 30 включает в себя резистивный элемент 30a с фиксированным значением сопротивления, как описано выше с использованием фиг. 6, температурные свойства ячейки МС памяти и опорной схемы 30 отличаются друг от друга в зависимости от температуры, как показано на фиг. 20. Когда ячейка памяти и опорная схема 30 имеют различные температурные свойства, сопротивление опорной схемы 30 не имеет оптимального значения (промежуточного значения между током ячейки для данных ʺ0ʺ и током ячейки для данных ʺ1ʺ) во всем диапазоне рабочих температур.

<4-3> Опорная схема

Таким образом, в настоящем варианте осуществления, для того, чтобы обеспечить регулировку температуры опорной схемы 30, обеспечивается NMOS-транзистор 30b, выполненный как элемент переменного сопротивления, как показано на фиг. 21. Опорная глобальная битовая линия RGBL соединена со стоком NMOS-транзистора 30b. Потенциал заземления соединен с истоком NMOS-транзистора 30b. Сигнал ʺVGʺ вводится в затвор NMOS-транзистора 30b. Сигнал ʺVGʺ генерируется схемой генерации сигнала, не изображенной на чертежах. Схема генерации сигнала генерирует сигнал ʺVGʺ таким образом, что значение сопротивления опорной схемы 30 является оптимальным во всем диапазоне рабочих температур. Кроме того, схема генерации сигнала желательным образом генерирует сигнал ʺVGʺ с использованием повышенного напряжения. Это делает затвор NMOS-транзистора 30b невосприимчивым к изменению напряжения затвор-исток.

Опорная схема 30 включает в себя NMOS-транзистор 30b, но настоящий вариант осуществления не ограничивается этим. Применим любой резистивный элемент, который обеспечивает возможность изменения значения сопротивления в соответствии с изменением температурного свойства ячейки МС памяти.

Как описано выше, когда опорная схема 30 включает в себя элемент переменного сопротивления, усилитель считывания в настоящем варианте осуществления может быть использован эффективным образом.

<4-4> Полезные эффекты

Согласно вышеописанному варианту осуществления, контроллер 12 использует один сигнал ʺVCLAMPʺ для управления двумя ограничительными транзисторами 181a и 181e, которые управляют током ячейки, и двумя ограничительными транзисторами 181m и 181n, которые управляют опорным током. Опорная схема 30 включает в себя элемент переменного сопротивления, который работает в соответствии с температурным свойством ячейки МС памяти.

Использование одного сигнала для работы ограничительных транзисторов повышает стойкость к шуму, оставшемуся после шумоподавления, воздействию которого подвергается сигнал ʺVCLAMPʺ, тем самым увеличивая предел считывания. Кроме того, площадь опорной схемы 30 с NMOS-транзистором 30b меньше, чем площадь опорной схемы 30 с элементом сопротивления.

Четвертый вариант осуществления также применим к вышеописанным второму и третьему вариантам осуществления.

(Пятый вариант осуществления)

Пятый вариант осуществления будет описан с использованием фиг. 22. В пятом варианте осуществления будет описана модификация операции считывания. Базовая конфигурация и функционирование запоминающего устройства в соответствии с пятым вариантом осуществления аналогичны базовой конфигурации и работе запоминающего устройства в соответствии с вышеописанным первым вариантом осуществления. Таким образом, материал, описанный выше в первом варианте осуществления, и материал, легко выводимый из вышеописанного первого варианта осуществления, не будет описываться.

<5-1> Схемная конфигурация

На фиг. 22, схема 17а выбора битовой линии, схема 17b выбора истоковой линии, опорная схема 30 и транзистор 40 изображены как блок CAU массива ячеек. Первый конец транзистора 40 соединен с глобальной битовой линией GBL. Второй конец транзистора 40 соединен с опорной схемой 30.

Установка транзистора 40 в выключенное состояние позволяет считывать и записывать данные в массив 11a ячеек. В настоящем варианте осуществления, блок массива ячеек, который использует массив 11а ячеек в качестве области памяти, обозначен как ʺCCAUʺ.

Установка транзистора 40 во включенное состояние позволяет работать опорной схеме 30. В настоящем варианте осуществления, блок массива ячеек, который обеспечивает возможность работы опорной схемы 30, обозначен как ʺRCAUʺ.

Усилитель 18а считывания соединен с блоком CCAU массива ячеек через глобальную битовую линию GBL. Усилитель 18a считывания соединен с блоком RCAU массива ячеек через опорную глобальную битовую линию RGBL.

Блок CCAU массива ячеек и блок RCAU массива ячеек имеют аналогичные структуры. Однако транзисторы, приводимые в действие блоком CCAU массива ячеек, отличаются от транзисторов, приводимых в действие блоком RCAU массива ячеек. Блок CCAU массива ячеек может стать блоком RCAU массива ячеек, а блок RCAU массива ячеек может стать блоком CCAU массива ячеек, при условии, что приводимые в действие транзисторы выполняют операции, противоположные операциям, показанным ниже.

<5-2> Операции

При выполнении операции считывания на ячейке МС памяти в блоке CCAU массива ячеек, контроллер 12 устанавливает транзистор 40 в блоке CCAU массива ячеек в выключенное состояние. Кроме того, контроллер 12 устанавливает во включенное состояние один из множества транзисторов, который соответствует ячейке МС памяти, на которой выполняется считывание, транзисторов 24, транзисторов 23 и транзисторов 26 в блоке CCAU массива ячеек. Усилитель 18a считывания соединен с ячейками МС памяти через глобальную битовую линию GBL, транзистор 24 и локальную битовую линию LBL в блоке CCAU массива ячеек. Кроме того, усилитель 18а считывания соединен с потенциалом заземления через ячейку ML памяти, транзистор 23, локальную истоковую линию LSL, транзистор 26 и глобальную истоковую линию GSL в блоке CCAU массива ячеек.

При выполнении операции считывания на ячейке МС памяти в блоке CCAU массива ячеек, контроллер 12 устанавливает транзистор 40 в блоке RCAU массива ячеек во включенное состояние. Кроме того, контроллер 12 устанавливает любой один из множества транзисторов 24 в блоке RCAU массива ячеек во включенное состояние. Кроме того, контроллер 12 устанавливает все транзисторы 23 в блоке RCAU массива ячеек в выключенное состояние. В этом случае, транзисторы 26 в блоке RCAU массива ячеек могут находиться во включенном состоянии или в выключенном состоянии. Усилитель 18а считывания соединен с опорной схемой 30 через опорную глобальную битовую линию и транзистор 40 в блоке RCAU массива ячеек. Усилитель 18а считывания соединен с потенциалом заземления через опорную схему 30 в блоке RCAU массива ячеек. Кроме того, усилитель 18а считывания соединен по меньшей мере с одной опорной локальной битовой линией LBL через опорную глобальную битовую линию и транзистор 24 в блоке RCAU массива ячеек.

<5-3> Полезные эффекты

В соответствии с описанным выше вариантом осуществления, в блоке RCAU массива ячеек, который использует опорную схему 30, контроллер 12 устанавливает по меньшей мере один транзистор 24 во включенное состояние и устанавливает все транзисторы 26 в выключенное состояние. Следовательно, в блоке RCAU массива ячеек, паразитная емкость на опорной локальной битовой линии RLBL добавляется к опорной глобальной битовой линии RGBL. В результате паразитная емкость, добавленная к глобальной битовой линии GBL в блоке CCAU массива ячеек, по существу равна паразитной емкости, добавленной к опорной глобальной битовой линии RGBL в блоке RCAU массива ячеек, что позволяет сократить время считывания.

Пятый вариант осуществления также применим к вышеописанным вариантам осуществления с второго по четвертый.

(Модификации и подобное)

В вышеописанных вариантах осуществления, MRAM с использованием магниторезистивных элементов берется в качестве примера полупроводникового запоминающего устройства. Однако варианты осуществления не ограничиваются этим, но применимы к различным типам полупроводниковых запоминающих устройств независимо от того, является ли полупроводниковое запоминающее устройство энергозависимой памятью или энергонезависимой памятью. Кроме того, варианты осуществления применимы к устройствам памяти с изменяемым сопротивлением, принадлежащим к тому же типу, что и MRAМ, например, FeRAM (ферроэлектрическая память с произвольным доступом), PCRAM (память с произвольным доступом с изменением фазового состояния) и ReRA (резистивная память с произвольным доступом).

Кроме того, в некоторых частях вышеописанных вариантов осуществления, транзисторы ограничены NMOS-транзисторами или PMOS-транзисторами. Однако варианты осуществления не ограничиваются ими.

Кроме того, в вышеописанных вариантах осуществления пара битовых линий упоминается как битовая линия BL и истоковая линия SL для удобства. Однако варианты осуществления не ограничиваются таковыми. Пара битовых линий может упоминаться, например, как первая битовая линия и вторая битовая линия.

Хотя были описаны некоторые варианты осуществления, эти варианты осуществления были представлены только в качестве примера и не предназначены для ограничения объема изобретений.

Действительно, описанные здесь новые способы и системы могут быть воплощены во множестве других форм; кроме того, различные пропуски, замены и изменения в форме описанных здесь способов и систем могут быть сделаны без отклонения от сущности изобретений. Прилагаемые пункты формулы изобретения и их эквиваленты предназначены для охвата таких форм или модификаций, которые находятся в пределах объема и сущности изобретений.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТВЕРДОТЕЛЬНОЕ УСТРОЙСТВО ФОРМИРОВАНИЯ ИЗОБРАЖЕНИЙ И СИСТЕМА ФОРМИРОВАНИЯ ИЗОБРАЖЕНИЙ | 2011 |

|

RU2479068C2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА ОСНОВЕ ИЗМЕНЕНИЯ СОПРОТИВЛЕНИЯ | 2014 |

|

RU2620502C2 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2642960C2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ИЗМЕНЕНИЕМ СОПРОТИВЛЕНИЯ | 2016 |

|

RU2702271C2 |

| СИСТЕМА И СПОСОБ РЕГУЛИРОВАНИЯ ПАРАМЕТРОВ СХЕМЫ ПАМЯТИ НА ОСНОВЕ СОПРОТИВЛЕНИЯ | 2009 |

|

RU2465641C2 |

| УСТРОЙСТВО ВОСПРИЯТИЯ ИЗОБРАЖЕНИЙ И СИСТЕМА ФОРМИРОВАНИЯ ИЗОБРАЖЕНИЙ | 2008 |

|

RU2390878C1 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2015 |

|

RU2682387C1 |

| МАГНИТНАЯ ПАМЯТЬ И СПОСОБ УПРАВЛЕНИЯ ЕЮ | 2014 |

|

RU2628221C1 |

| УСИЛИТЕЛЬ СЧИТЫВАНИЯ, ПАМЯТЬ И СПОСОБ УПРАВЛЕНИЯ | 2021 |

|

RU2812300C2 |

| ГЕНЕРАТОР ОПОРНОГО НАПРЯЖЕНИЯ С НИЗКИМ ИМПЕДАНСОМ | 2012 |

|

RU2592719C2 |

Изобретение относится к вычислительной технике. Технический результат заключается в увеличении скорости считывания данных. Полупроводниковое запоминающее устройство содержит ячейку памяти; битовую линию, соединенную с ячейкой памяти; и схему считывания, соединенную с битовой линией, при этом схема считывания содержит первый транзистор с первым концом, соединенным с битовой линией, и затвором, на который вводится первый сигнал; второй транзистор с первым концом, соединенным со вторым концом первого транзистора, и затвором, на который вводится второй сигнал; третий транзистор с первым концом, соединенным с битовой линией, и затвором, на который вводится второй сигнал; четвертый транзистор с первым концом, соединенным со вторым концом третьего транзистора, и затвором, на который вводится первый сигнал; и усилитель, соединенный со вторым концом второго транзистора и со вторым концом четвертого транзистора, при этом отношение ширины канала второго и третьего транзисторов является таким же, как отношение ширины канала первого и четвертого транзисторов. 3 н. и 16 з.п. ф-лы, 22 ил.

1. Полупроводниковое запоминающее устройство, содержащее:

ячейку памяти;

битовую линию, соединенную с ячейкой памяти; и

схему считывания, соединенную с битовой линией,

при этом схема считывания содержит:

первый транзистор с первым концом, соединенным с битовой линией, и затвором, на который вводится первый сигнал;

второй транзистор с первым концом, соединенным со вторым концом первого транзистора, и затвором, на который вводится второй сигнал;

третий транзистор с первым концом, соединенным с битовой линией, и затвором, на который вводится второй сигнал;

четвертый транзистор с первым концом, соединенным со вторым концом третьего транзистора, и затвором, на который вводится первый сигнал; и

усилитель, соединенный со вторым концом второго транзистора и со вторым концом четвертого транзистора,

при этом отношение ширины канала второго и третьего транзисторов является таким же, как отношение ширины канала первого и четвертого транзисторов.

2. Полупроводниковое запоминающее устройство по п. 1, в котором:

размерное соотношение между первым транзистором и четвертым транзистором идентично размерному соотношению между вторым транзистором и третьим транзистором.

3. Полупроводниковое запоминающее устройство по п. 1, дополнительно содержащее:

опорную схему и

опорную битовую линию, соединенную с опорной схемой,

при этом схема считывания содержит:

пятый транзистор с первым концом, соединенным с опорной битовой линией, и затвором, на который вводится первый сигнал;

шестой транзистор с первым концом, соединенным со вторым концом пятого транзистора, вторым концом, соединенным с усилителем, и затвором, на который вводится третий сигнал;

седьмой транзистор с первым концом, соединенным с опорной битовой линией, и затвором, на который вводится третий сигнал; и

восьмой транзистор с первым концом, соединенным со вторым концом седьмого транзистора, вторым концом, соединенным с усилителем, и затвором, на который вводится первый сигнал.

4. Полупроводниковое запоминающее устройство по п. 3, в котором:

размерное соотношение между первым транзистором и четвертым транзистором идентично размерному соотношению между вторым транзистором и третьим транзистором и

размерное соотношение между пятым транзистором и восьмым транзистором идентично размерному соотношению между шестым транзистором и седьмым транзистором.

5. Полупроводниковое запоминающее устройство по п. 3, в котором второй сигнал является сигналом, идентичным третьему сигналу.

6. Полупроводниковое запоминающее устройство по п. 5, в котором опорная схема содержит транзистор.

7. Полупроводниковое запоминающее устройство по п. 3, в котором усилитель содержит:

девятый транзистор первого типа проводимости с первым концом, соединенным со вторым концом второго транзистора и вторым концом четвертого транзистора, вторым концом, соединенным с первым узлом, и затвором, соединенным со вторым узлом;

десятый транзистор второго типа проводимости, отличного от первого типа проводимости, причем десятый транзистор содержит первый конец, соединенный с первым узлом, второй конец, соединенный с третьим узлом, к которому приложено напряжение источника питания, и затвор, соединенный со вторым узлом;

одиннадцатый транзистор первого типа проводимости с первым концом, соединенным со вторым концом шестого транзистора и вторым концом восьмого транзистора, вторым концом, соединенным со вторым узлом, и затвором, соединенным с первым узлом; и

двенадцатый транзистор второго типа проводимости с первым концом, соединенным со вторым узлом, вторым концом, соединенным с третьим узлом, и затвором, соединенным с первым узлом.

8. Полупроводниковое запоминающее устройство по п. 7, в котором усилитель дополнительно содержит:

тринадцатый транзистор с первым концом, к которому приложено напряжение источника питания, вторым концом, соединенным с третьим узлом, и затвором, на который вводится четвертый сигнал; и

четырнадцатый транзистор с первым концом, соединенным с первым узлом, вторым концом, соединенным со вторым узлом, и затвором, на который вводится пятый сигнал.

9. Полупроводниковое запоминающее устройство по п. 3, дополнительно содержащее:

пятнадцатый транзистор с первым концом, соединенным со вторым концом первого транзистора, вторым концом, соединенным с четвертым узлом, и затвором, на который вводится первый сигнал; и

шестнадцатый транзистор с первым концом, соединенным со вторым концом пятого транзистора, вторым концом, соединенным с четвертым узлом, и затвором, на который вводится первый сигнал;

семнадцатый транзистор с первым концом, соединенным со вторым концом второго транзистора, вторым концом, соединенным с четвертым узлом, и затвором, на который вводится первый сигнал; и

восемнадцатый транзистор с первым концом, соединенным со вторым концом шестого транзистора, вторым концом, соединенным с четвертым узлом, и затвором, на который вводится первый сигнал,

при этом с первого по восьмой транзисторы представляют собой транзисторы первого типа проводимости, и

с пятнадцатого по восемнадцатый транзисторы представляют собой транзисторы второго типа проводимости, отличающегося от первого типа проводимости.

10. Полупроводниковое запоминающее устройство, содержащее:

ячейку памяти;

битовую линию, соединенную с ячейкой памяти, и

схему считывания, соединенную с битовой линией,

при этом схема считывания содержит:

усилитель;

первый путь, который соединяет битовую линию и усилитель вместе; и

второй путь, который соединяет битовую линию и усилитель вместе,

при этом первый путь содержит:

первый транзистор с первым концом, соединенным с битовой линией, и затвором, на который вводится первый сигнал; и

второй транзистор с первым концом, соединенным со вторым концом первого транзистора, вторым концом, соединенным с усилителем, и затвором, на который вводится второй сигнал, и

второй путь содержит:

третий транзистор с первым концом, соединенным с битовой линией, и затвором, на который вводится второй сигнал; и

четвертый транзистор с первым концом, соединенным со вторым концом третьего транзистора, вторым концом, соединенным с усилителем, и затвором, на который вводится первый сигнал,

при этом отношение ширины канала второго и третьего транзисторов является таким же, как отношение ширины канала первого и четвертого транзисторов.

11. Полупроводниковое запоминающее устройство по п. 10, в котором:

размерное соотношение между первым транзистором и четвертым транзистором идентично размерному соотношению между вторым транзистором и третьим транзистором.

12. Полупроводниковое запоминающее устройство по п. 10, дополнительно содержащее:

опорную схему и

опорную битовую линию, соединенную с опорной схемой,

при этом схема считывания содержит:

третий путь, который соединяет опорную битовую линию и усилитель вместе; и

четвертый путь, который соединяет опорную битовую линию и усилитель вместе.

13. Полупроводниковое запоминающее устройство по п. 12, в котором третий путь содержит:

пятый транзистор с первым концом, соединенным с опорной битовой линией, и затвором, на который вводится первый сигнал;

шестой транзистор с первым концом, соединенным со вторым концом пятого транзистора, вторым концом, соединенным с усилителем, и затвором, на который вводится третий сигнал, и

четвертый путь содержит:

седьмой транзистор с первым концом, соединенным с опорной битовой линией, и затвором, на который вводится третий сигнал; и

восьмой транзистор с первым концом, соединенным со вторым концом седьмого транзистора, вторым концом, соединенным с усилителем, и затвором, на который вводится первый сигнал.

14. Полупроводниковое запоминающее устройство по п. 13, в котором:

размерное соотношение между первым транзистором и четвертым транзистором идентично размерному соотношению между вторым транзистором и третьим транзистором, и

размерное соотношение между пятым транзистором и восьмым транзистором идентично размерному соотношению между шестым транзистором и седьмым транзистором.

15. Полупроводниковое запоминающее устройство по п. 13, в котором второй сигнал представляет собой сигнал, идентичный третьему сигналу, и

опорная схема содержит транзистор.

16. Полупроводниковое запоминающее устройство по п. 13, в котором усилитель содержит:

девятый транзистор первого типа проводимости с первым концом, соединенным со вторым концом второго транзистора и вторым концом четвертого транзистора, вторым концом, соединенным с первым узлом, и затвором, соединенным со вторым узлом;

десятый транзистор второго типа проводимости, отличного от первого типа проводимости, причем десятый транзистор содержит первый конец, соединенный с первым узлом, второй конец, соединенный с третьим узлом, к которому приложено напряжение источника питания, и затвором, соединенным со вторым узлом;

одиннадцатый транзистор первого типа проводимости с первым концом, соединенным со вторым концом шестого транзистора и вторым концом восьмого транзистора, вторым концом, соединенным со вторым узлом, и затвором, соединенным с первым узлом; и

двенадцатый транзистор второго типа проводимости с первым концом, соединенным со вторым узлом, вторым концом, соединенным с третьим узлом, и затвором, соединенным с первым узлом.

17. Полупроводниковое запоминающее устройство по п. 16, в котором усилитель дополнительно содержит:

тринадцатый транзистор с первым концом, к которому приложено напряжение источника питания, вторым концом, соединенным с третьим узлом, и затвором, на который вводится четвертый сигнал; и

четырнадцатый транзистор с первым концом, соединенным с первым узлом, вторым концом, соединенным со вторым узлом, и затвором, на который вводится пятый сигнал.

18. Полупроводниковое запоминающее устройство по п. 13, дополнительно содержащее:

пятнадцатый транзистор с первым концом, соединенным со вторым концом первого транзистора, вторым концом, соединенным с четвертым узлом, и затвором, на который вводится первый сигнал; и

шестнадцатый транзистор с первым концом, соединенным со вторым концом пятого транзистора, вторым концом, соединенным с четвертым узлом, и затвором, на который вводится первый сигнал;

семнадцатый транзистор с первым концом, соединенным со вторым концом второго транзистора, вторым концом, соединенным с четвертым узлом, и затвором, на который вводится первый сигнал; и

восемнадцатый транзистор с первым концом, соединенным со вторым концом шестого транзистора, вторым концом, соединенным с четвертым узлом, и затвором, на который вводится первый сигнал,

при этом с первого по восьмой транзисторы представляют собой транзисторы первого типа проводимости, и

с пятнадцатого по восемнадцатый транзисторы представляют собой транзисторы второго типа проводимости, отличного от первого типа проводимости.

19. Полупроводниковое запоминающее устройство, содержащее:

первую ячейку памяти;

первую битовую линию, соединенную с первой ячейкой памяти;

первый транзистор, соединенный с первой битовой линией на первом конце первого транзистора;

вторую битовую линию, соединенную со вторым концом первого транзистора;

первую опорную схему, соединенную со второй битовой линией;

вторую ячейку памяти;

третью битовую линию, соединенную со второй ячейкой памяти;

второй транзистор, соединенный с третьей битовой линией на первом конце второго транзистора;

четвертую битовую линию, соединенную со вторым концом второго транзистора;

вторую опорную схему, соединенную с четвертой битовой линией; и

схему считывания, соединенную со второй битовой линией и четвертой битовой линией,

при этом схема считывания содержит:

третий транзистор с первым концом, соединенным с битовой линией, и затвором, на который вводится первый сигнал;

четвертый транзистор с первым концом, соединенным со вторым концом третьего транзистора, и затвором, на который вводится второй сигнал; и

пятый транзистор с первым концом, соединенным с первой битовой линией, и затвором, на который вводится второй сигнал;

шестой транзистор с первым концом, соединенным со вторым концом пятого транзистора, и затвором, на который вводится первый сигнал;

усилитель, соединенный со вторым концом четвертого транзистора и вторым концом шестого транзистора,

при этом отношение ширины канала четвертого и пятого транзисторов является таким же, как отношение ширины канала третьего и шестого транзисторов;

седьмой транзистор с первым концом, соединенным с четвертой битовой линией, и затвором, на который вводится первый сигнал;

восьмой транзистор с первым концом, соединенным со вторым концом седьмого транзистора, вторым концом, соединенным с усилителем, и затвором, на который вводится третий сигнал; и

девятый транзистор с первым концом, соединенным с четвертой битовой линией, и затвором, на который вводится третий сигнал; и

десятый транзистор с первым концом, соединенным со вторым концом девятого транзистора, вторым концом, соединенным с усилителем, и затвором, на который вводится первый сигнал,

при этом отношение ширины канала восьмого и девятого транзисторов является таким же, как отношение ширины канала седьмого и десятого транзисторов, и

при этом, когда данные в первой ячейке памяти считываются с использованием схемы считывания,

первая ячейка памяти, первый транзистор, второй транзистор и вторая опорная схема установлены во включенное состояние, а вторая ячейка памяти и первая опорная схема установлены в выключенное состояние.

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Устройство для закрепления лыж на раме мотоциклов и велосипедов взамен переднего колеса | 1924 |

|

SU2015A1 |

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |