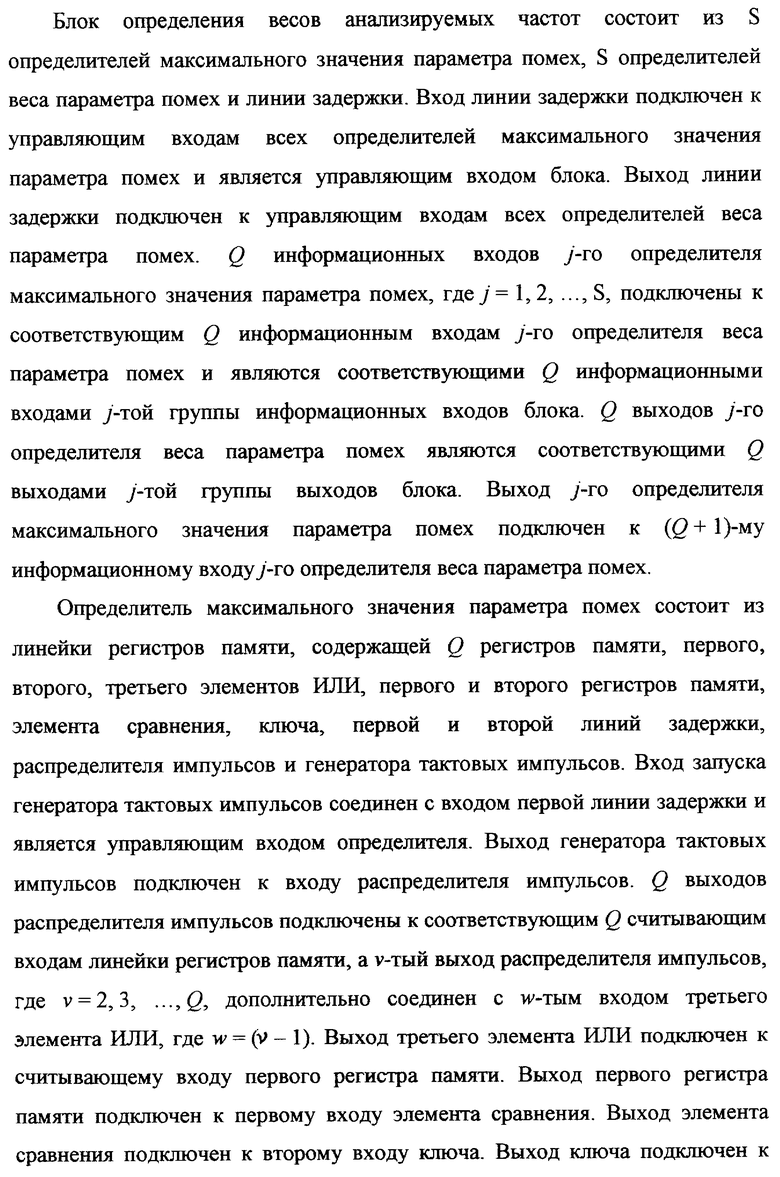

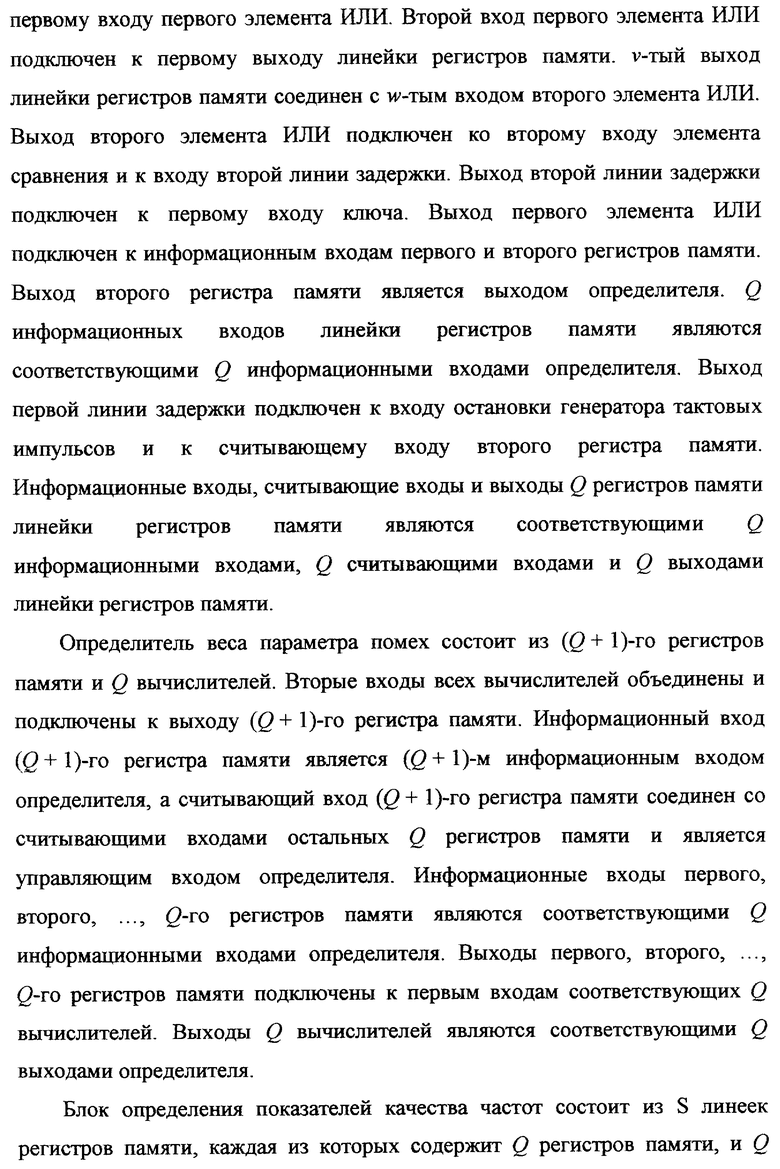

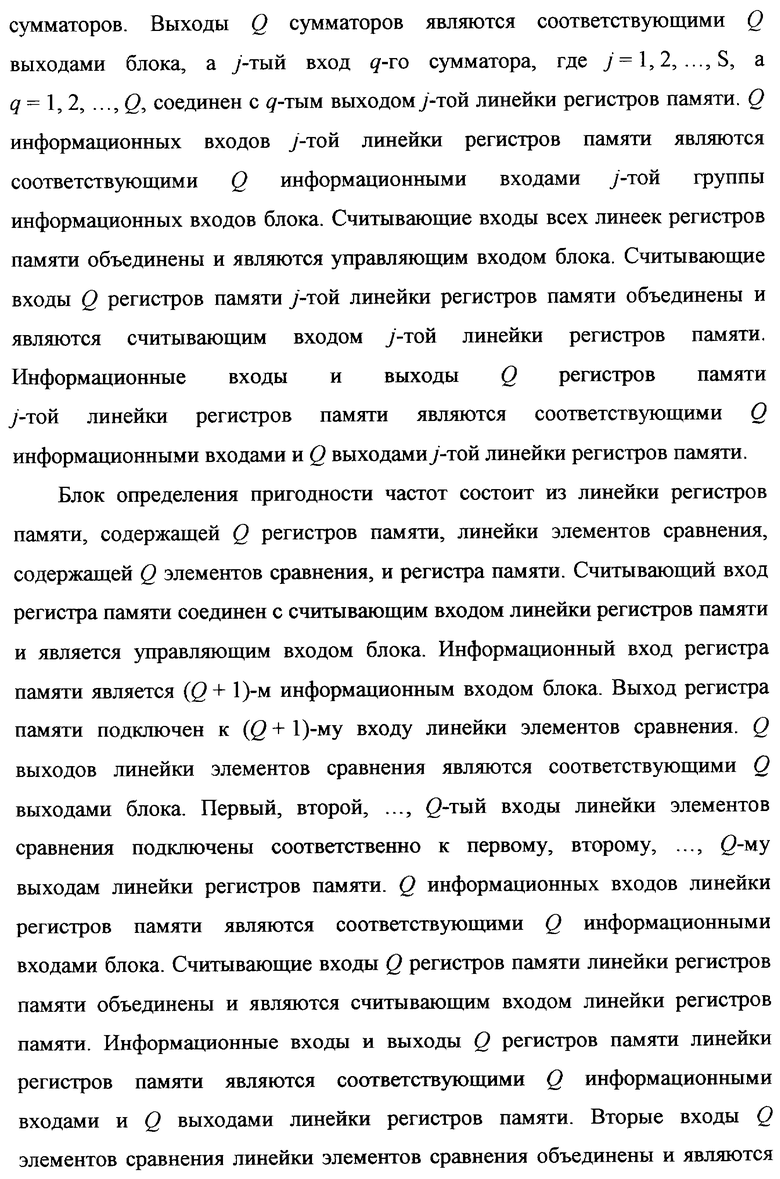

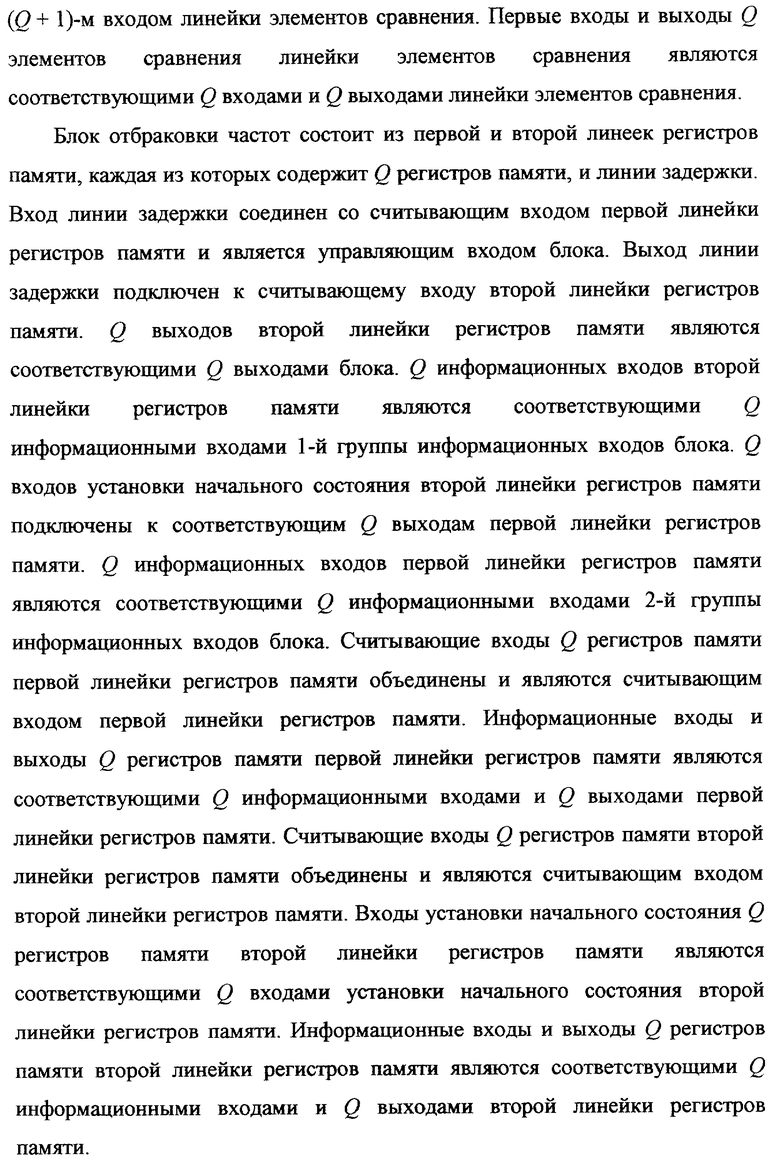

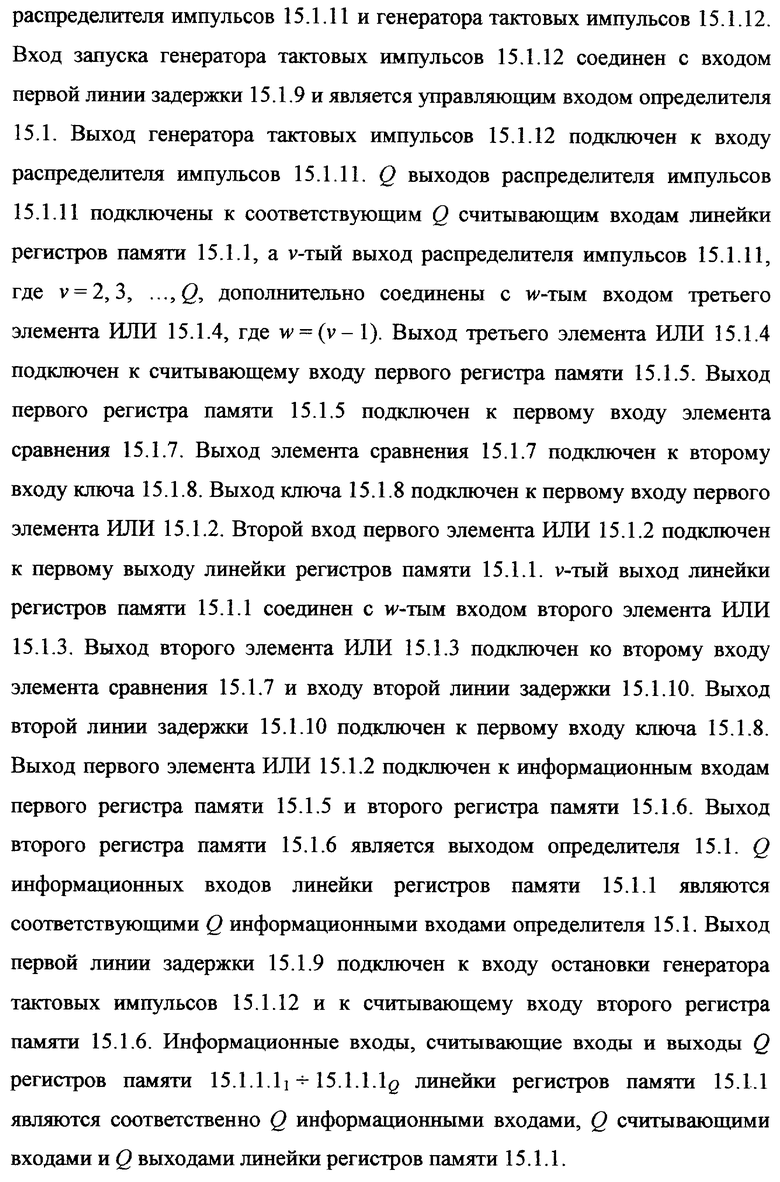

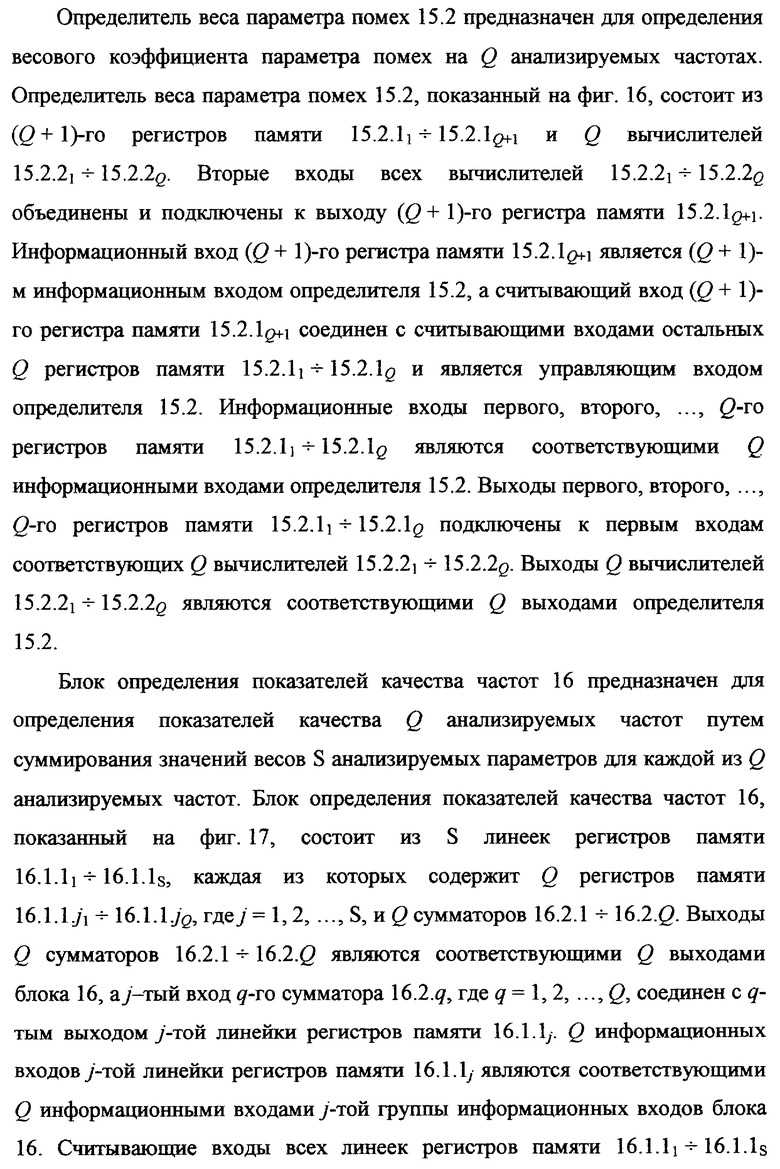

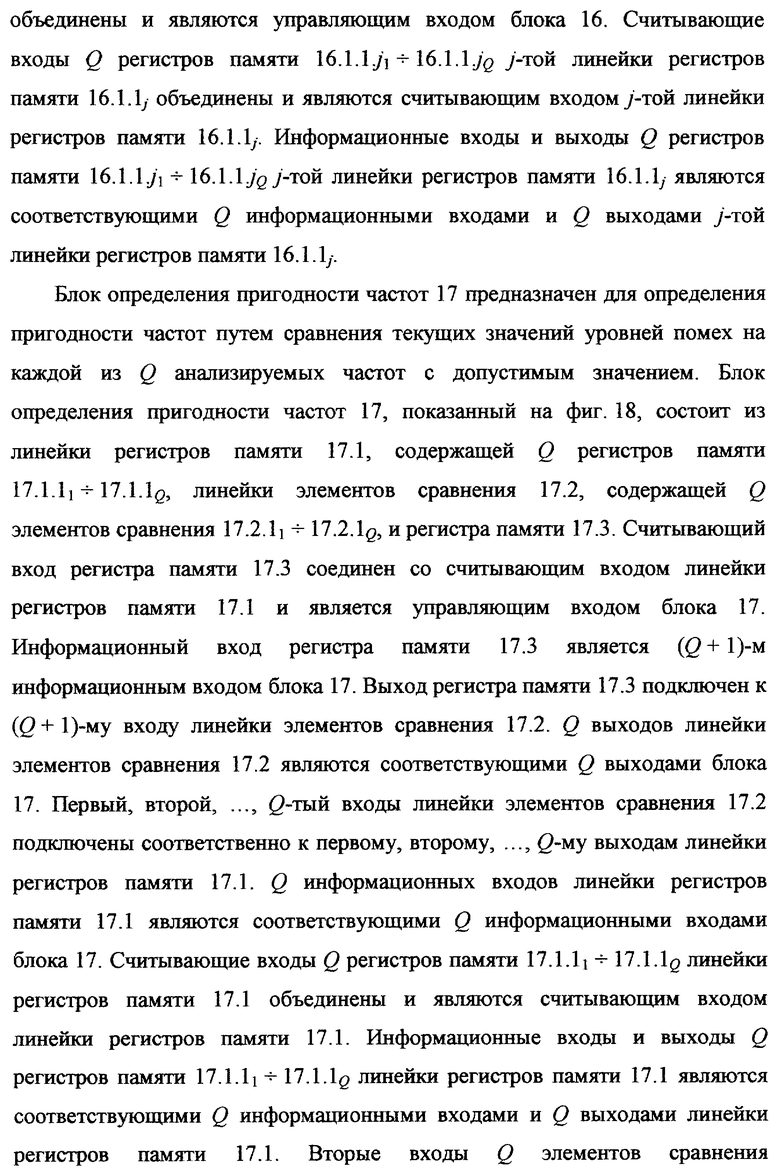

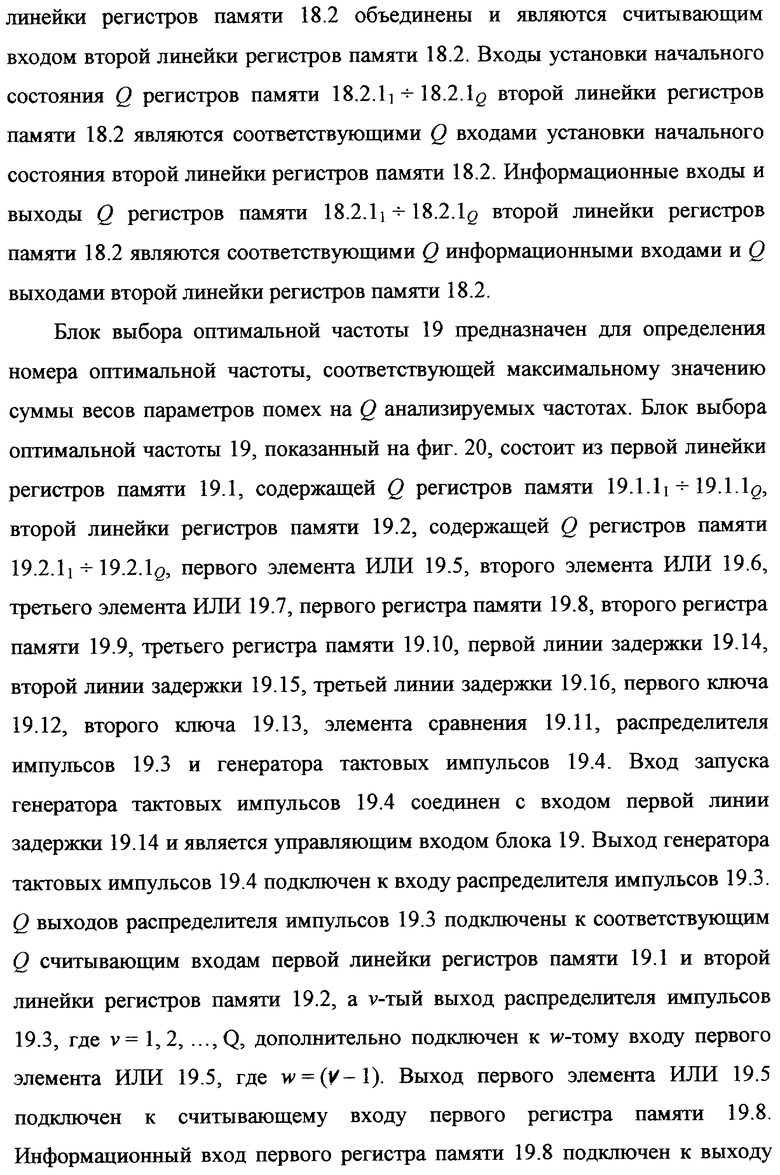

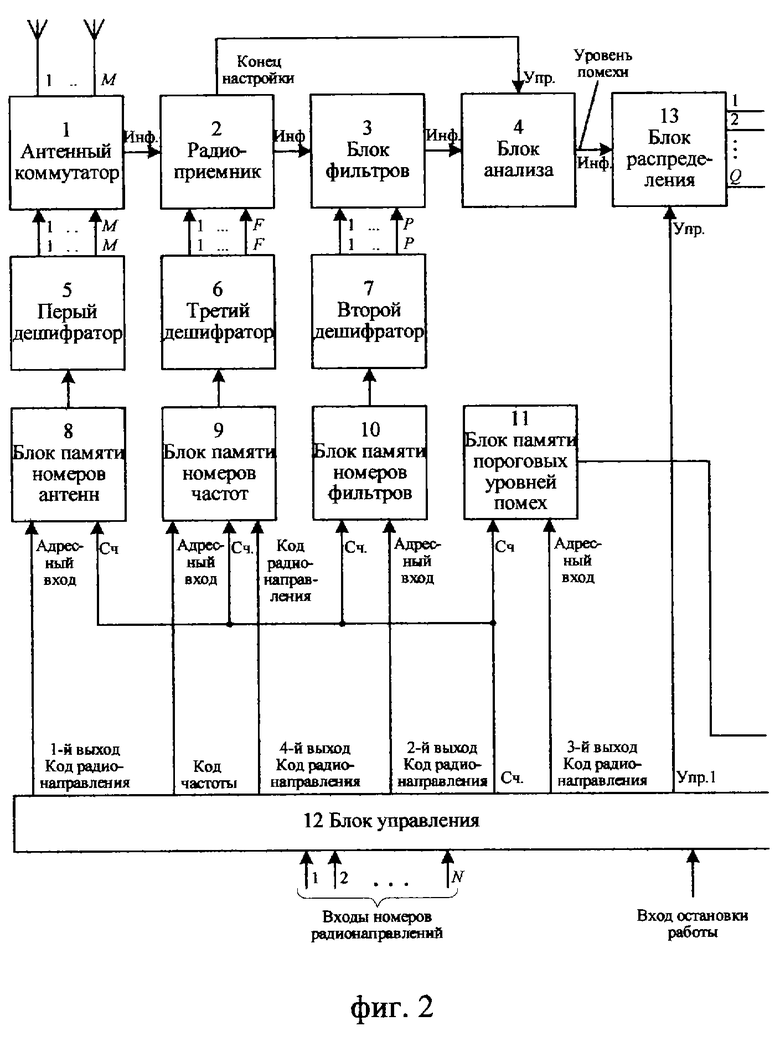

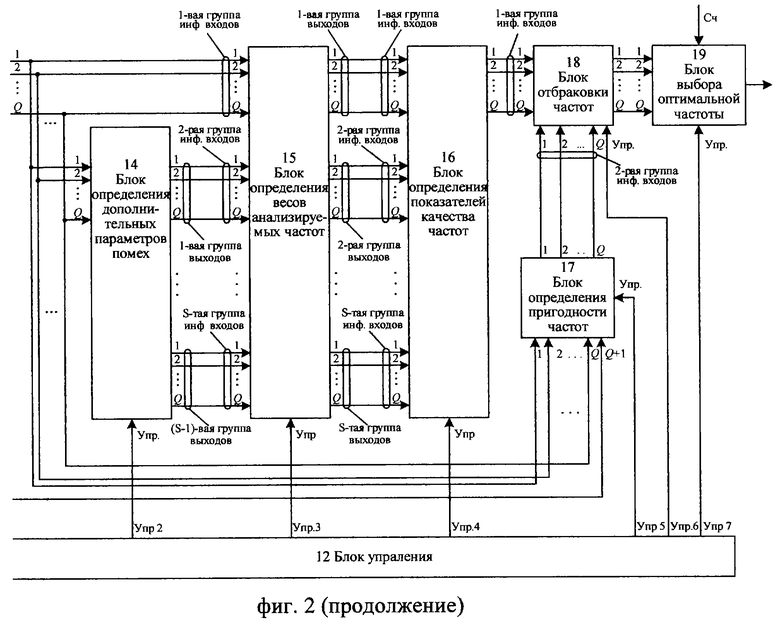

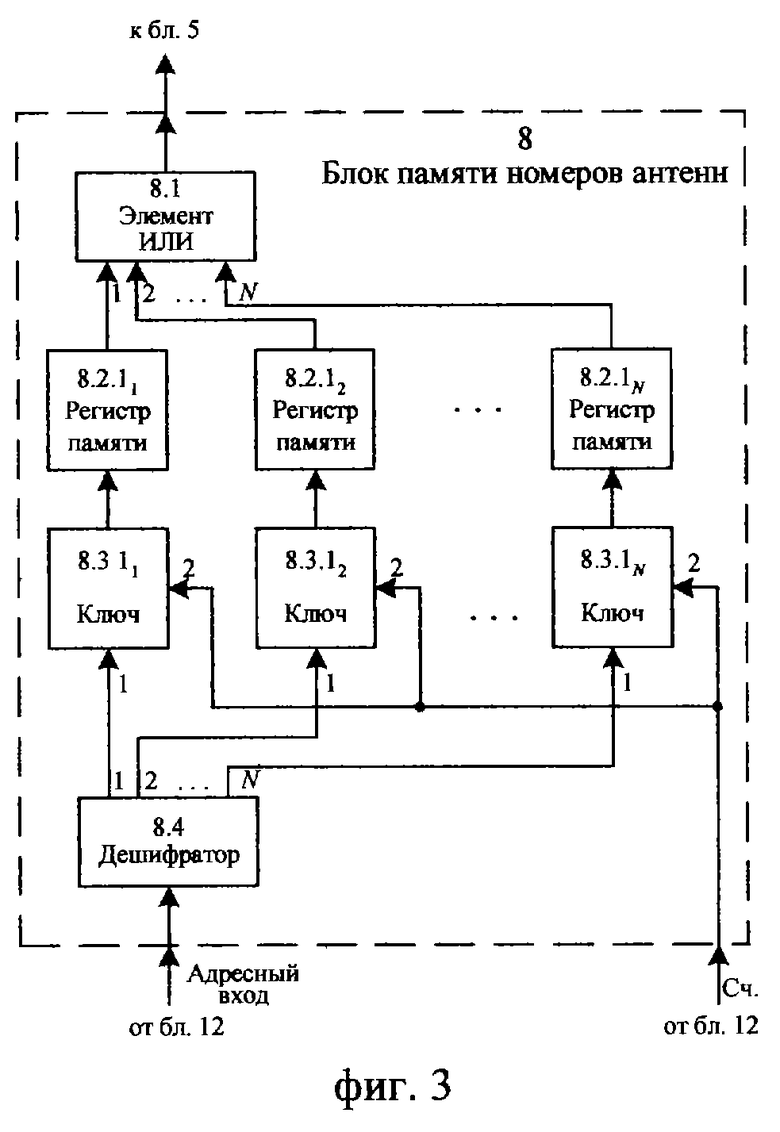

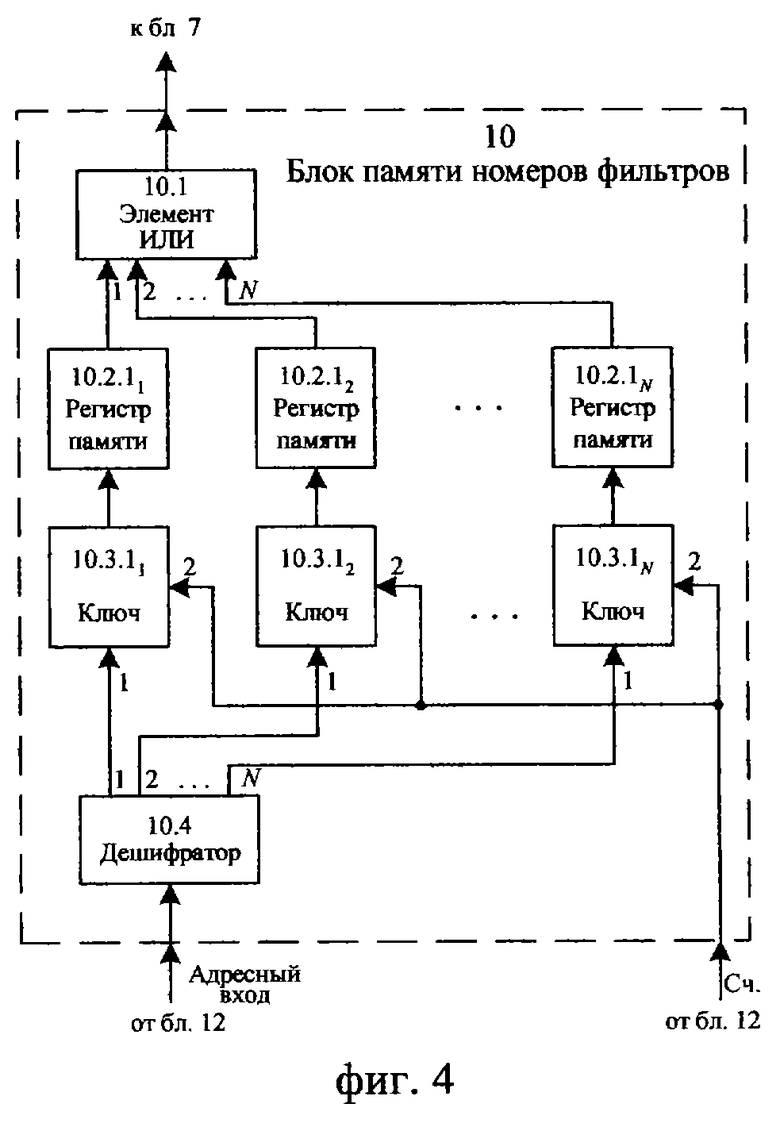

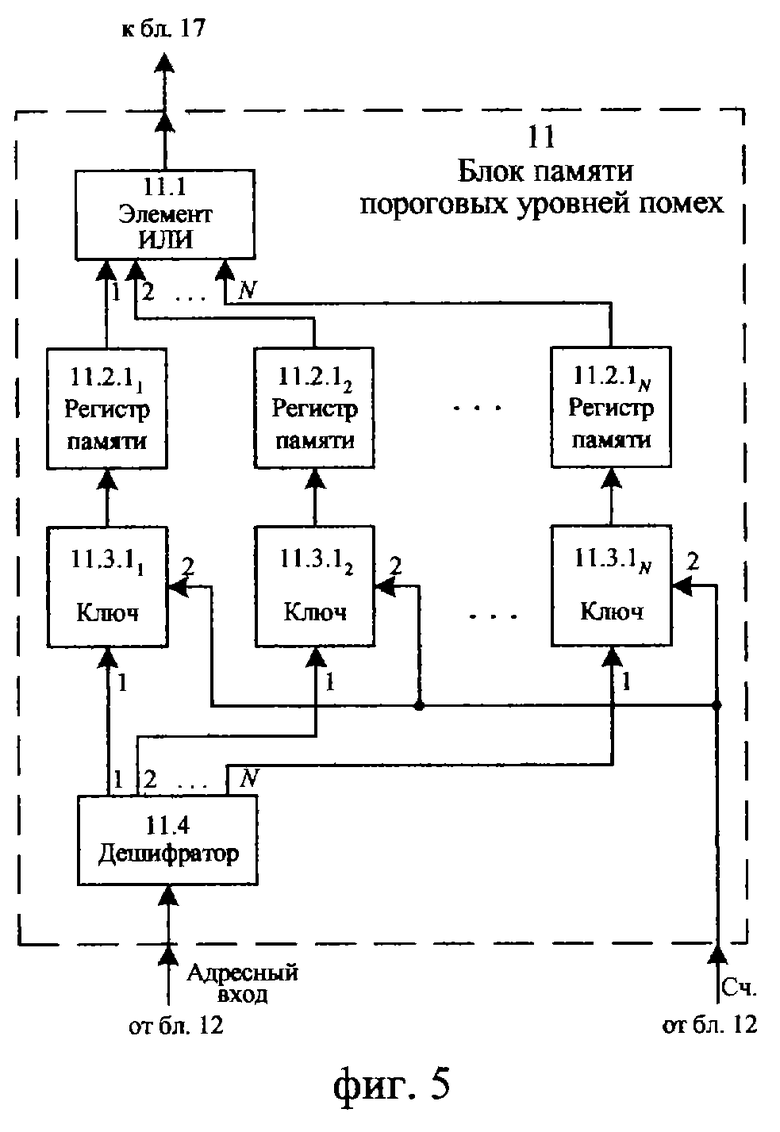

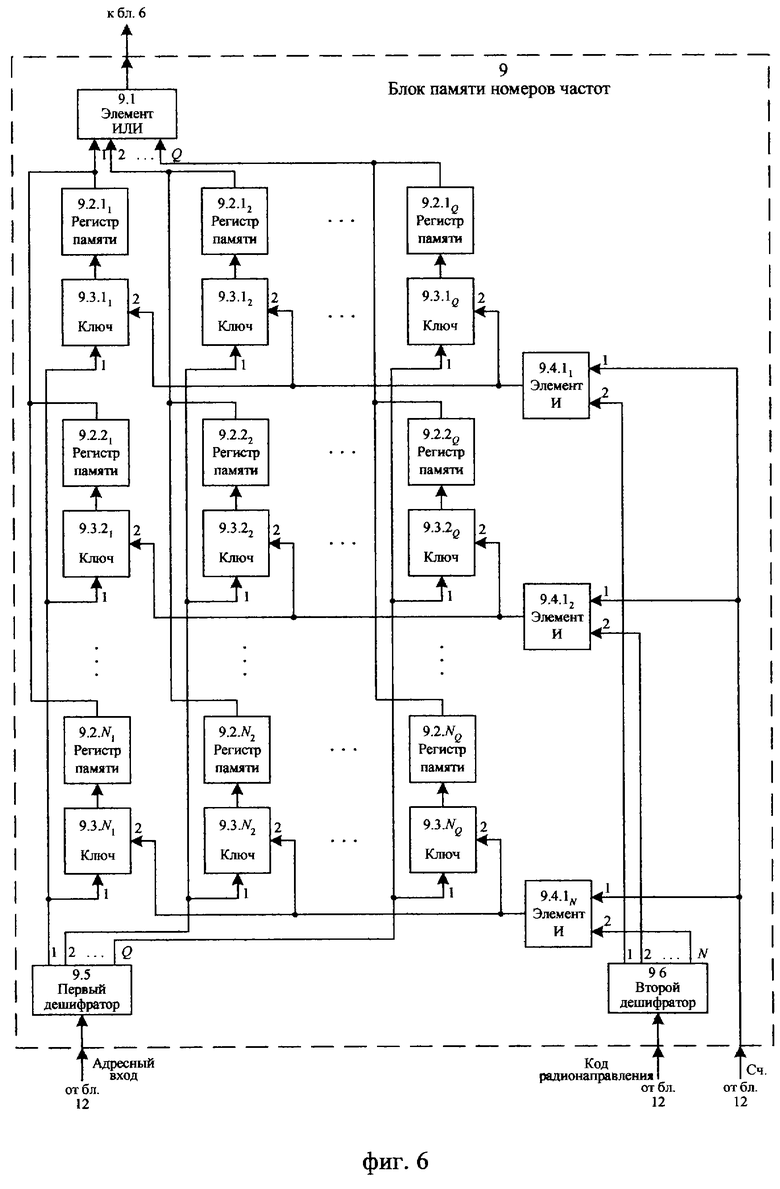

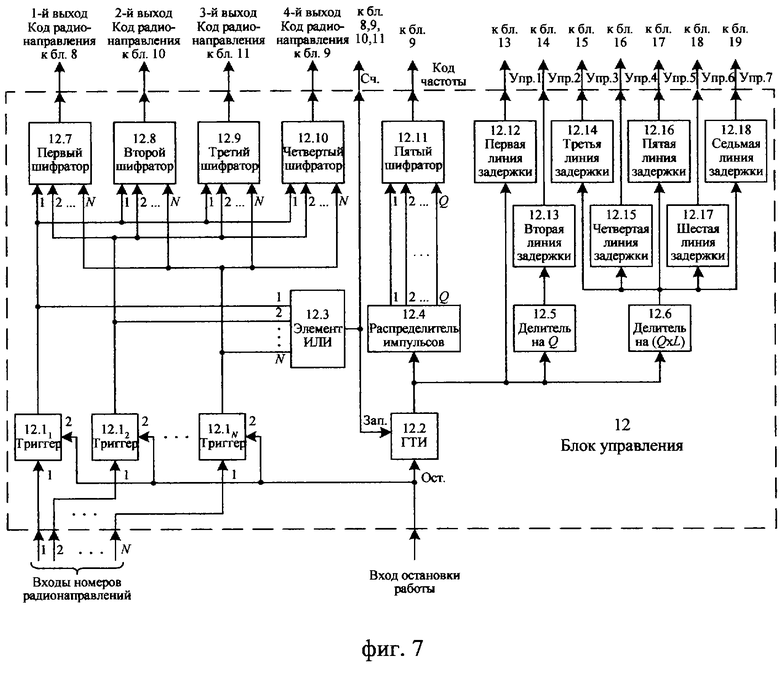

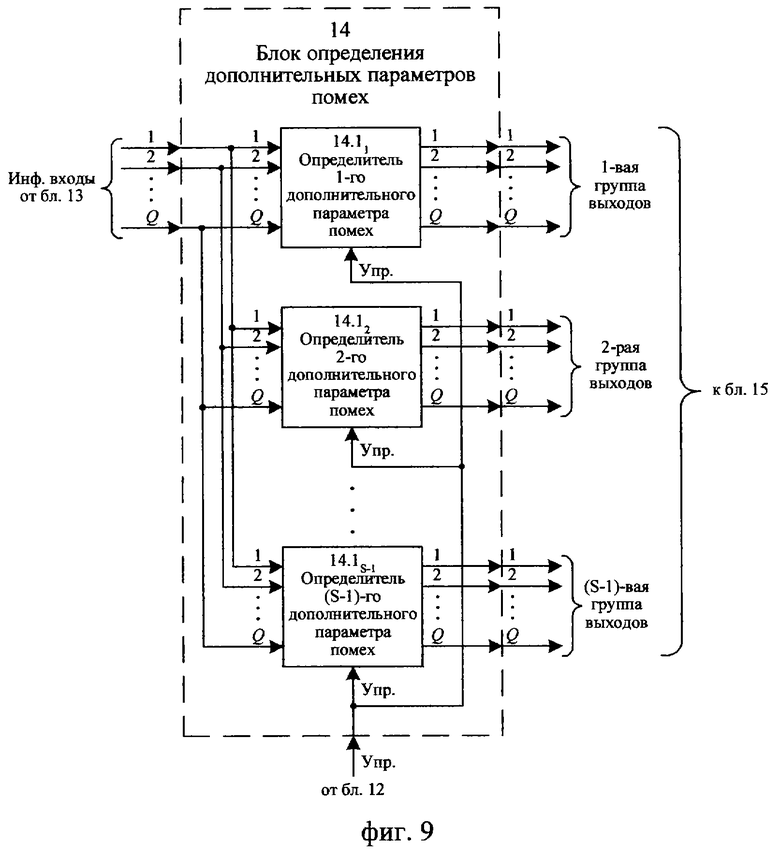

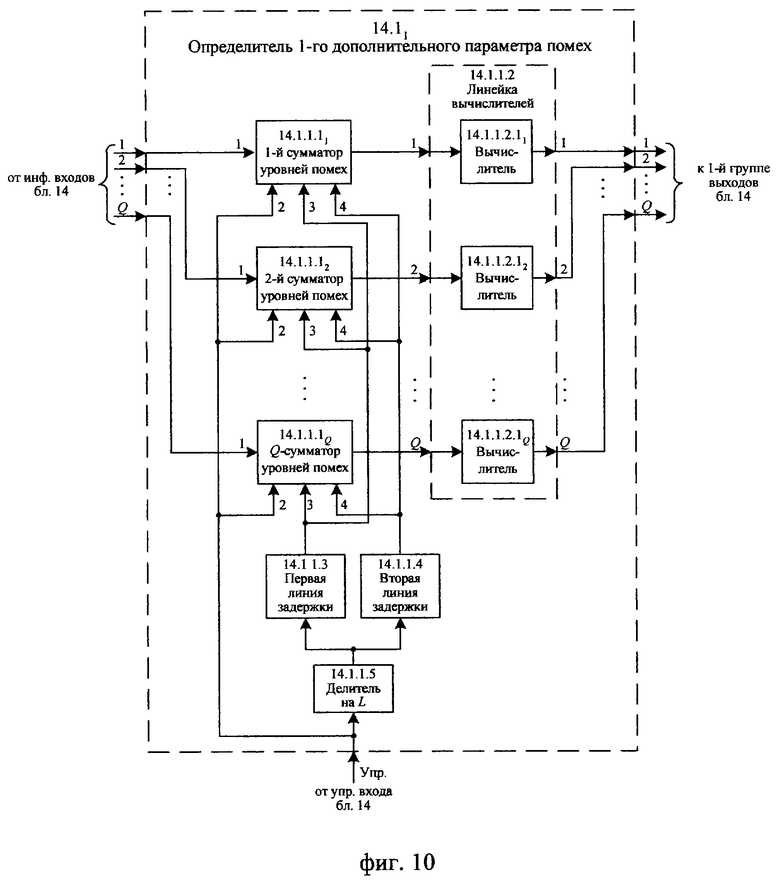

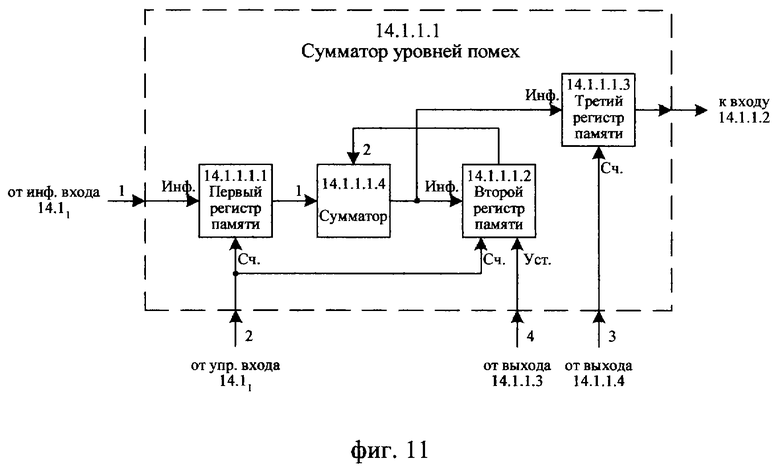

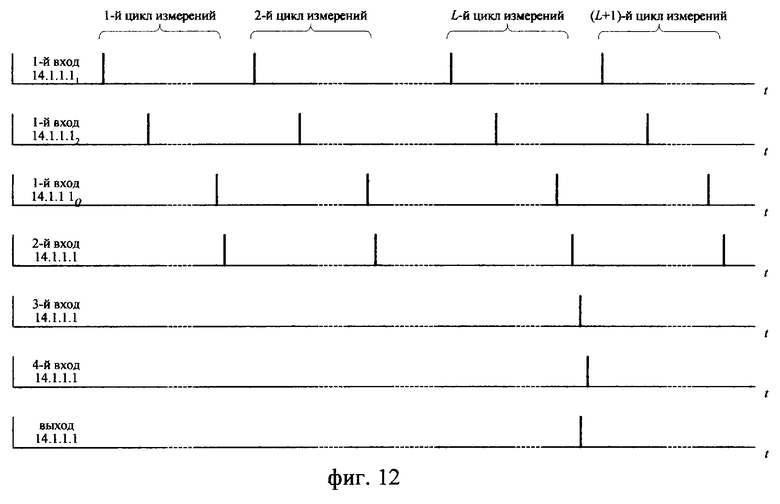

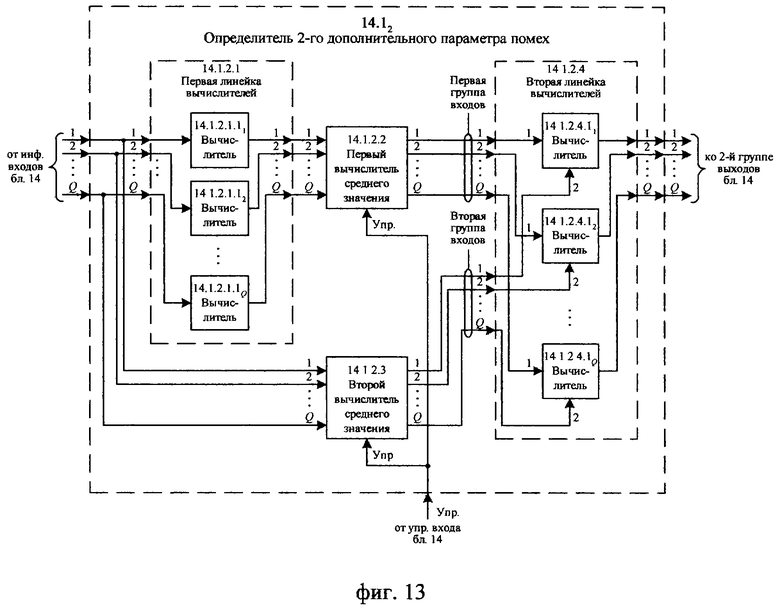

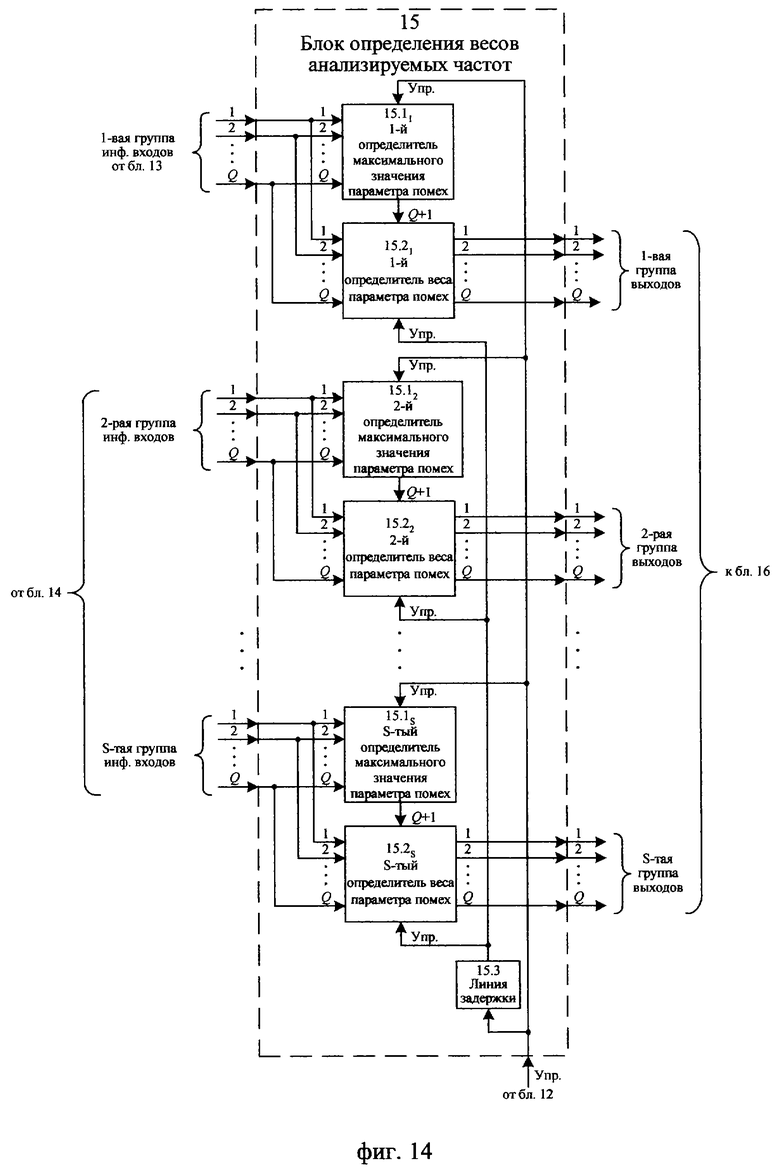

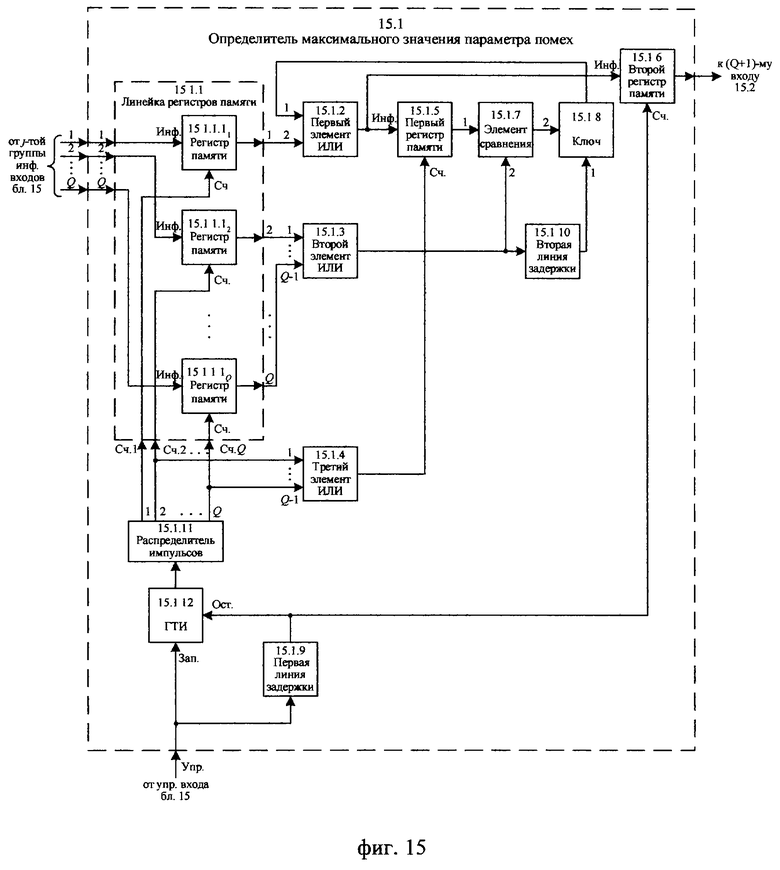

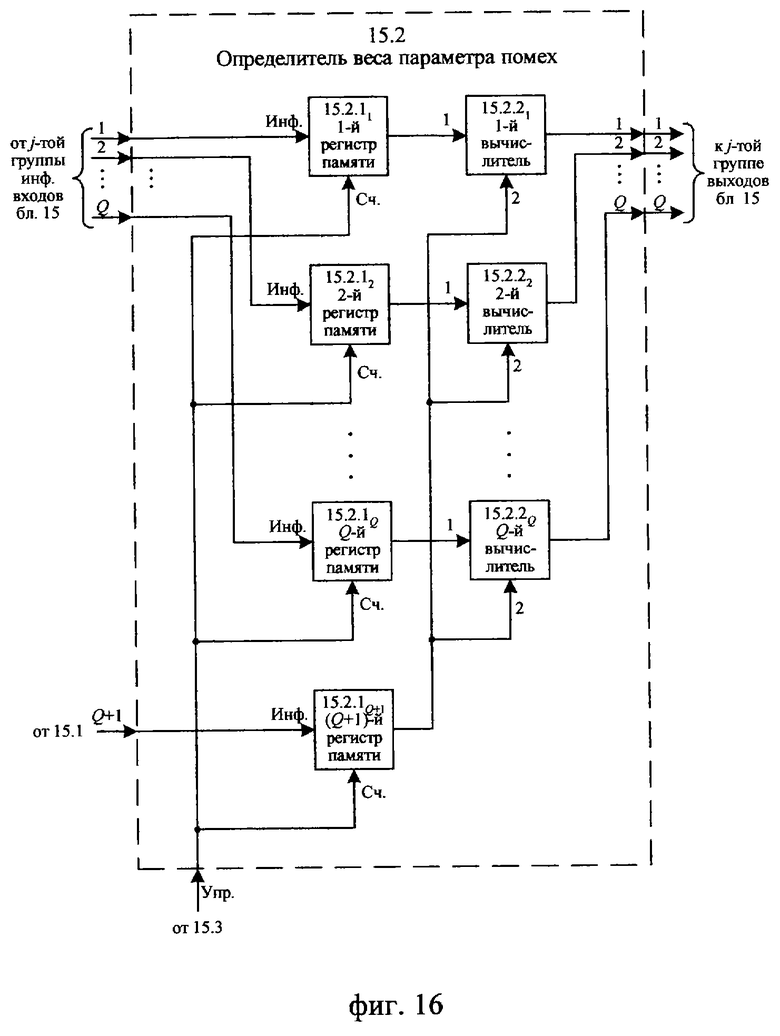

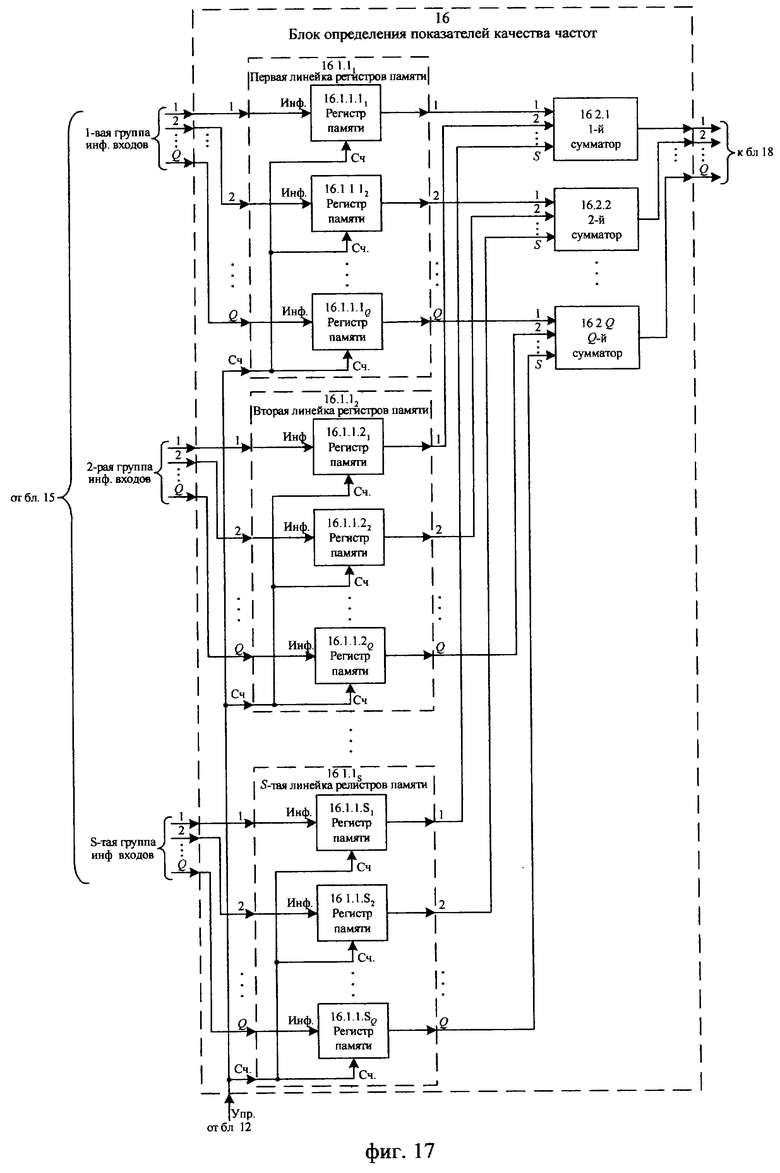

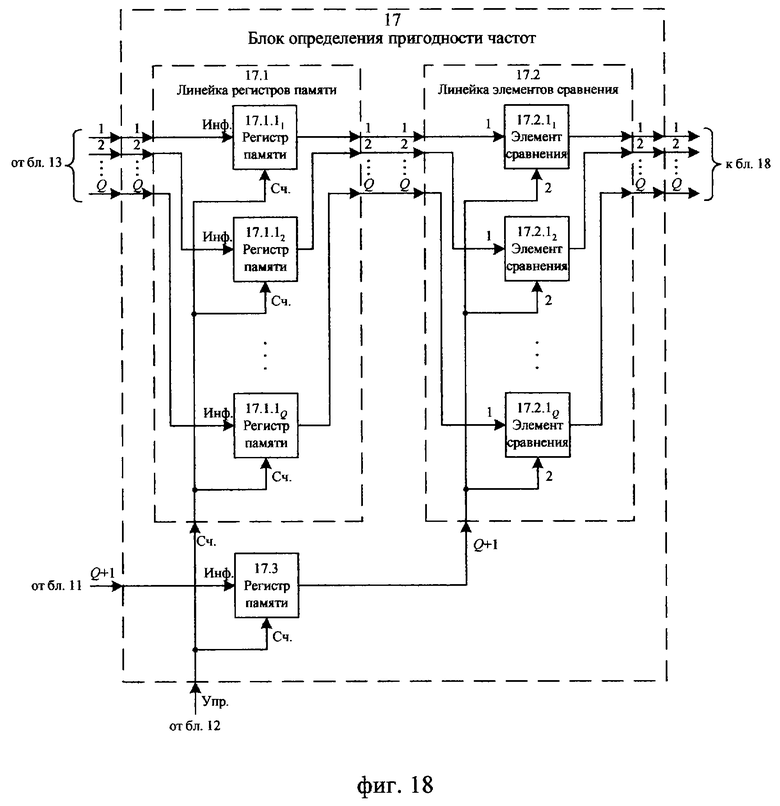

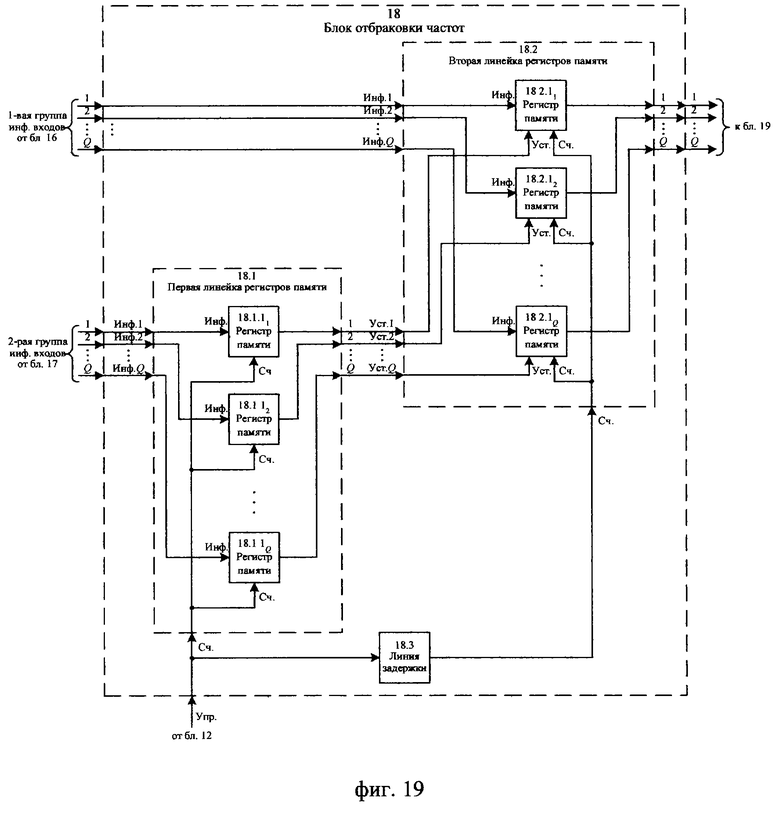

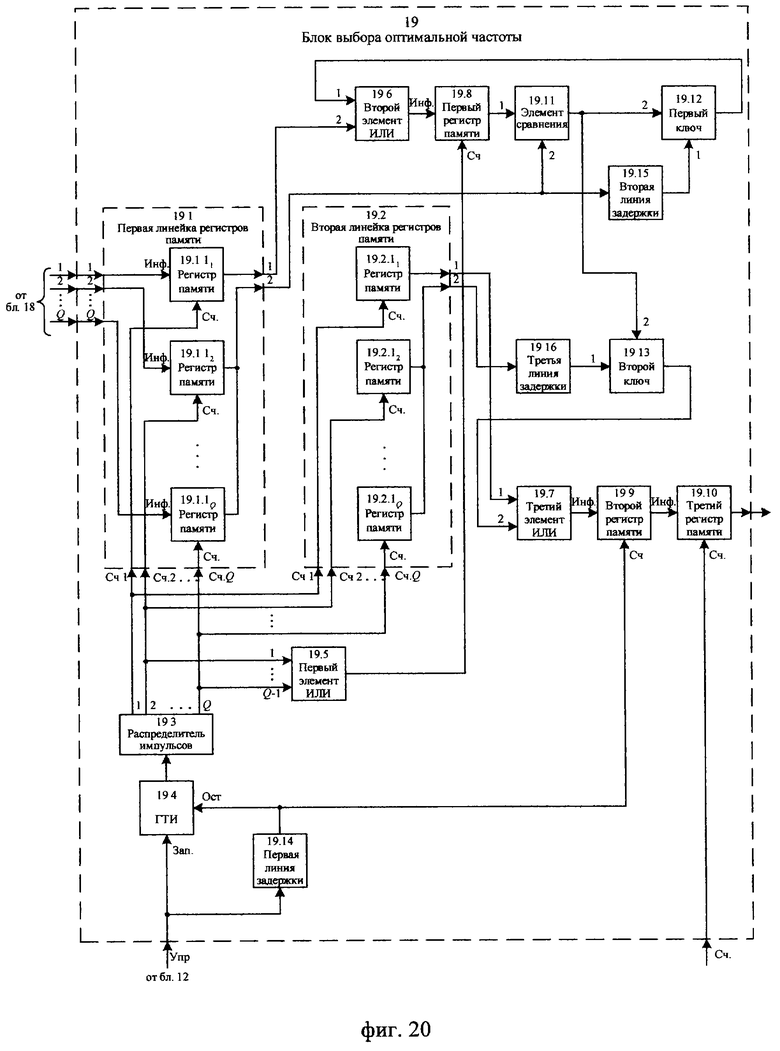

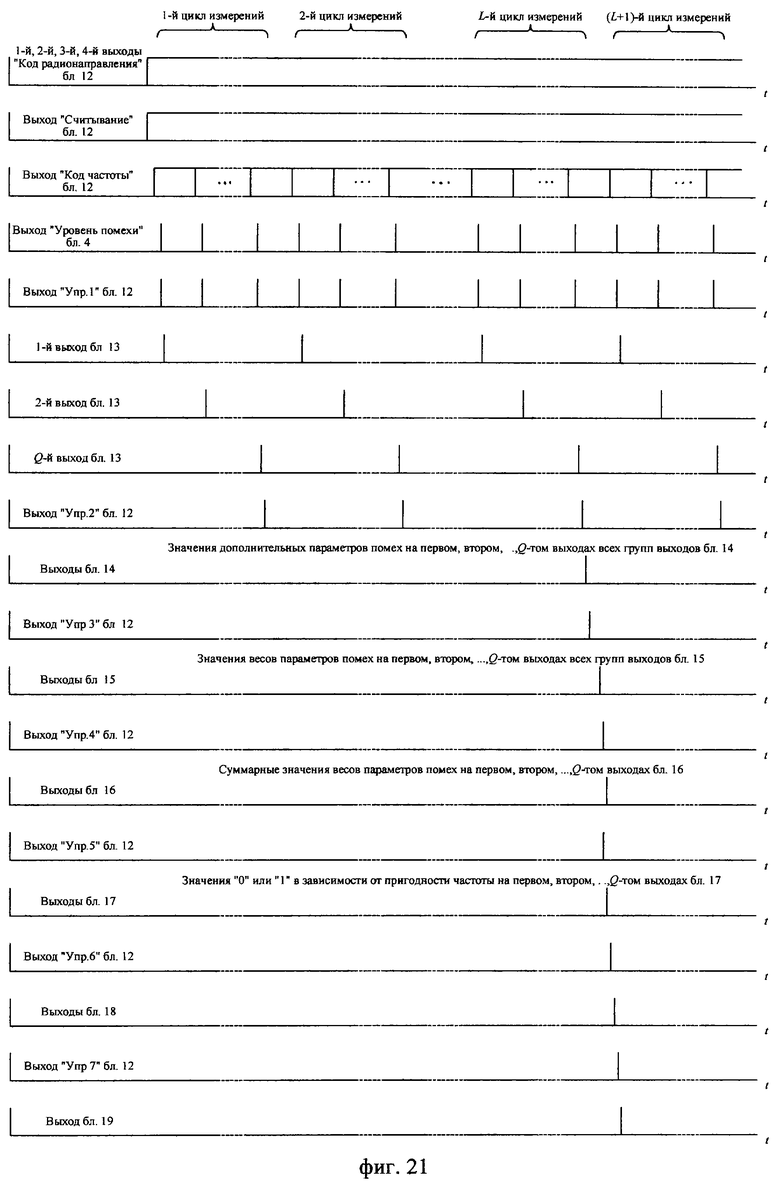

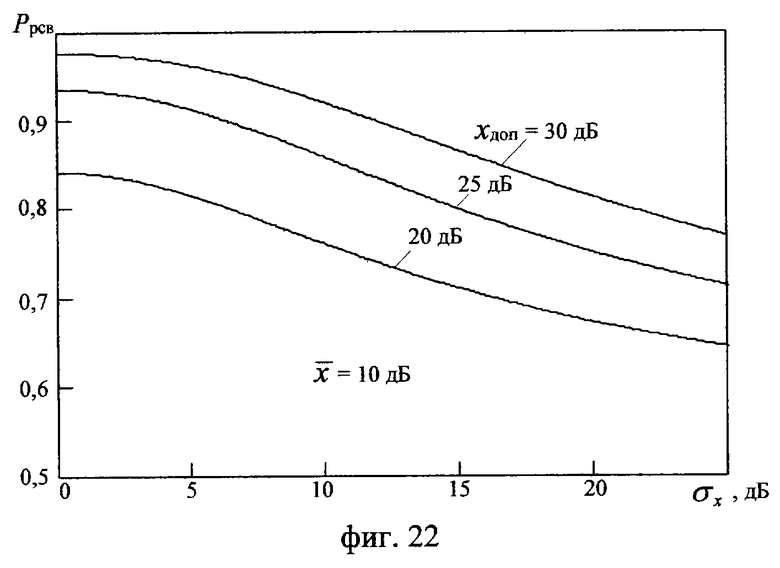

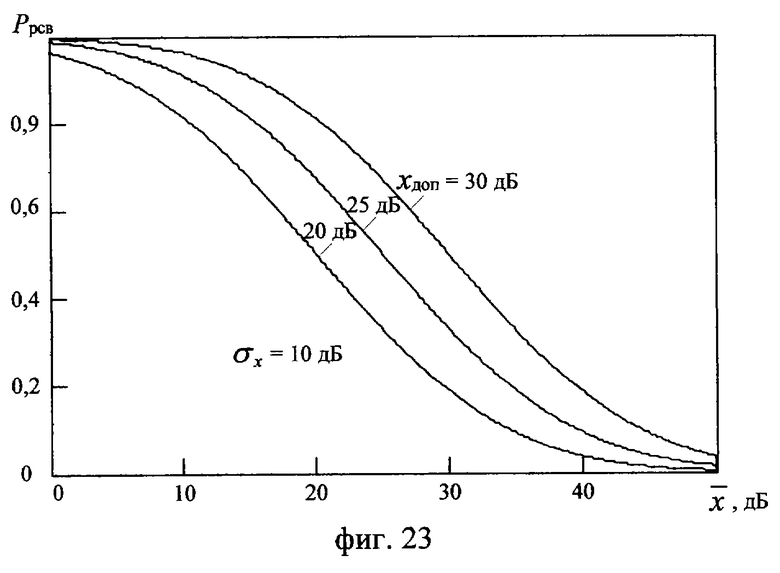

1. Устройство автоматического выбора рабочих частот, содержащее каскадно соединенные по информационным входам антенный коммутатор, радиоприемник, блок фильтров и блок анализа, управляющий вход которого подключен к выходу "Конец настройки" радиоприемника, F управляющих входов которого, где F=2, 3, 4,..., подключены к соответствующим F выходам третьего дешифратора, вход которого подключен к выходу блока памяти номеров фильтров, Р управляющих входов блока фильтров, где Р=2, 3, 4,..., подключены к соответствующим Р выходам второго дешифратора, вход которого подключен к выходу блока памяти номеров фильтров, М антенных входов антенного коммутатора, где М=2, 3, 4..., подключены к соответствующим М антеннам, М управляющих входов антенного коммутатора подключены к соответствующим М выходам первого дешифратора, вход которого подключен к выходу блока памяти номеров антенн, считывающий вход которого подключен к считывающим входам блоков памяти номеров частот, номеров фильтров, пороговых уровней помех и к считывающему выходу блока управления, N входов номеров радионаправлений которого, где N=2, 3, 4,..., являются соответствующими N входами радионаправлений устройства, 1-й, 2-й, 3-й и 4-й выходы "Код радионаправления" блока управления подключены соответственно к адресным входам блока памяти номеров антенн, блока памяти номеров фильтров, блока памяти пороговых уровней помех и к входу "Код радионаправления" блока памяти номеров частот, выход "Код частоты" блока управления подключен к адресному входу блока памяти номеров частот, отличающееся тем, что с целью повышения достоверности выбора рабочих частот дополнительно введены блок распределения, блок определения дополнительных параметров помех, блок определения весов анализируемых частот, блок определения показателей качества частот, блок определения пригодности частот, блок отбраковки частот и блок выбора оптимальной частоты, при этом выход блока анализа подключен к информационному входу блока распределения, Q выходов которого, где Q=2, 3, 4,..., подключены к соответствующим Q информационным входам 1-й группы информационных входов блока определения весов анализируемых частот, к Q информационным входам блока определения пригодности частот и блока определения дополнительных параметров помех, Q выходов i-й группы выходов которого, где i=1, 2,..., (S-1), a S - количество анализируемых параметров помех, подключены к соответствующим Q информационным входам (1+1)-й группы информационных входов блока определения весов анализируемых частот, Q выходов j-й группы выходов которого, где j=1, 2,..., S, подключены к соответствующим Q информационным входам j-й группы информационных входов блока определения показателей качества частот, Q информационных выходов которого подключены к соответствующим Q информационным входам 1-й группы информационных входов блока отбраковки частот, Q выходов которого подключены к соответствующим Q входам блока выбора оптимальной частоты, считывающий вход и выход которого являются соответственно считывающим входом и выходом устройства, Q информационных входов 2-й группы информационных входов блока отбраковки частот подключены к соответствующим Q выходам блока определения пригодности частот, (Q+1)-й информационный вход которого подключен к выходу блока памяти пороговых уровней помех, первый, второй, третий, четвертый, пятый, шестой и седьмой управляющие выходы блока управления подключены к управляющим входам соответственно блоков распределения, определения дополнительных параметров помех, определения весов анализируемых частот, определения показателей качества частот, определения пригодности частот, отбраковки частот и выбора оптимальной частоты, причем вход остановки работы блока управления является входом остановки работы устройства.2. Устройство по п.1, отличающееся тем, что блок управления состоит из генератора тактовых импульсов, распределителя импульсов, элемента ИЛИ, первого, второго, третьего, четвертого и пятого шифраторов, первой, второй, третьей, четвертой, пятой, шестой и седьмой линий задержки, делителя на Q, делителя на (Q×L), где Z=2, 3, 4,..., и N триггеров, первые входы которых являются соответствующими N входами номеров радионаправлений блока, а выходы N триггеров подключены к соответствующим N входам элемента ИЛИ и к соответствующим N входам первого, второго, третьего и четвертого шифраторов, выходы которых являются соответственно 1-м, 2-м, 3-м и 4-м выходами "Код радионаправления" блока, вторые входы всех триггеров объединены и подключены к входу остановки генератора тактовых импульсов, являющемуся входом остановки работы блока, выход элемента ИЛИ подключен к входу запуска генератора тактовых импульсов и является считывающим выходом блока, выход генератора тактовых импульсов подключен к входам первой линии задержки, делителя на Q, делителя на (Q×L) и распределителя импульсов, Q выходов которого подключены к соответствующим Q входам пятого шифратора, выход которого является выходом "Код частоты" блока, выход z-й линии задержки, где z=1, 2,..., 7, является 2-м управляющим выходом блока, выход делителя на Q подключен к входу второй линии задержки, выход делителя на (Q×L) подключен к входам третьей, четвертой, пятой, шестой и седьмой линий задержки.3. Устройство по п.1 или 2, отличающееся тем, что блок распределения состоит из Q ключей и распределителя импульсов, вход которого является управляющим входом блока, а Q его выходов подключены ко вторым входам соответствующих Q ключей, первые входы которых объединены и являются информационным входом блока, а выходы Q ключей являются соответствующими Q выходами блока.4. Устройство по любому из пп.1-3, отличающееся тем, что блок определения дополнительных параметров помех состоит из определителей 1-го, 2-го,... (S-1)-гo дополнительного параметра помех, управляющие входы которых объединены и являются управляющим входом блока, q-е входы определителей 1-го, 2-го,... (S-l)-го дополнительного параметра помех, где q=1, 2,..., Q, объединены и являются q-м информационным входом блока, а Q выходов определителя i-го дополнительного параметра, где i=1, 2,.... (S-1), являются соответствующими Q выходами i-й группы выходов блока.5. Устройство по п.4, отличающееся тем, что определитель 1-го дополнительного параметра помех состоит из Q сумматоров уровней помех, линейки вычислителей, содержащей Q вычислителей, первой линии задержки, второй линии задержки и делителя на L, вход которого соединен со вторыми входами всех сумматоров уровней помех и является управляющим входом определителя, а выход делителя на L соединен с входом первой и второй линий задержки, выход первой линии задержки соединен с третьими входами всех сумматоров уровней помех, выход второй линии задержки соединен с четвертыми входами всех сумматоров уровней помех, первые входы которых являются соответствующими Q информационными входами определителя, выходы всех Q сумматоров уровней помех подключены к соответствующим Q входам линейки вычислителей, Q выходов которой являются соответствующими Q выходами определителя, входы и выходы Q вычислителей линейки вычислителей являются соответствующими Q входами и Q выходами линейки вычислителей.6. Устройство по п.5, отличающееся тем, что сумматор уровней помех состоит из первого, второго, третьего регистров памяти и сумматора, выход которого подключен к информационным входам второго и третьего регистров памяти, а его первый вход подключен к выходу первого регистра памяти, информационный вход которого является первым входом сумматора уровней помех, считывающие входы первого и второго регистров памяти объединены и являются вторым входом сумматора уровней помех, второй вход сумматора подключен к выходу второго регистра памяти, вход установки начального состояния которого является четвертым входом сумматора уровней помех, считывающий вход и выход третьего регистра памяти являются соответственно третьим входом и выходом сумматора уровней помех.7. Устройство по п.4 или 5, отличающееся тем, что определитель 2-го дополнительного параметра помех состоит из первой и второй линеек вычислителей, каждая из которых содержит Q вычислителей, первого и второго вычислителей среднего значения, управляющие входы которых объединены и являются управляющим входом определителя, Q информационных входов первого вычислителя среднего значения подключены к соответствующим Q выходам первой линейки вычислителей, Q входов которой соединены с соответствующими Q информационными входами второго вычислителя среднего значения и являются соответствующими Q информационными входами определителя, Q выходов второго вычислителя среднего значения подключены к соответствующим Q входам второй группы входов второй линейки вычислителей, к первой группе входов которой подключены соответствующие Q выходов первого вычислителя среднего значения, а Q выходов второй линейки вычислителей являются соответствующими Q выходами определителя, входы и выходы Q вычислителей первой линейки вычислителей являются соответствующими Q входами и Q выходами первой линейки вычислителей, первые входы Q вычислителей второй линейки вычислителей являются соответствующими Q входами первой группы входов второй линейки вычислителей, вторые входы Q вычислителей второй линейки вычислителей являются соответствующими Q входами второй группы входов второй линейки вычислителей, выходы Q вычислителей второй линейки вычислителей являются соответствующими Q выходами второй линейки вычислителей.8. Устройство по любому из пп.1-4, отличающееся тем, что блок определения весов анализируемых частот состоит из S определителей максимального значения параметра помех, S определителей веса параметра помех и линии задержки, вход которой подключен к управляющим входам всех определителей максимального значения параметра помех и является управляющим входом блока, а выход линии задержки подключен к управляющим входам всех определителей веса параметра помех, Q информационных входов j-го определителя максимального значения параметра помех, где j=1, 2,..., S, подключены к соответствующим Q информационным входам j-го определителя веса параметра помех и являются соответствующими Q информационными входами j-й группы информационных входов блока, Q выходов j-го определителя веса параметра помех являются соответствующими Q выходами j-й группы выходов блока, причем выход j-го определителя максимального значения параметра помех подключен к (Q+1)-мy информационному входу j-го определителя веса параметра помех.9. Устройство по п.8, отличающееся тем, что определитель максимального значения параметра помех состоит из линейки регистров памяти, содержащей Q регистров памяти, первого, второго, третьего элементов ИЛИ, первого и второго регистров памяти, элемента сравнения, ключа, первой и второй линий задержки, распределителя импульсов и генератора тактовых импульсов, вход запуска которого соединен с входом первой линии задержки и является управляющим входом определителя, выход ГТИ подключен к входу распределителя импульсов, Q выходов которого подключены к соответствующим Q считывающим входам линейки регистров памяти, а v-й выход распределителя импульсов, где v=2, 3,..., Q, дополнительно соединен с w-м входом третьего элемента ИЛИ, где w=(v-1), выход которого подключен к считывающему входу первого регистра памяти, выход которого подключен к первому входу элемента сравнения, выход которого подключен ко второму входу ключа, выход которого подключен к первому входу первого элемента ИЛИ, второй вход которого подключен к первому выходу линейки регистров памяти, v-й выход которой соединен с w-м входом второго элемента ИЛИ, выход которого подключен ко второму входу элемента сравнения и к входу второй линии задержки, выход которой подключен к первому входу ключа, выход первого элемента ИЛИ подключен к информационным входам первого и второго регистров памяти, выход которого является выходом определителя, Q информационных входов линейки регистров памяти являются соответствующими Q информационными входами определителя, выход первой линии задержки подключен к входу остановки генератора тактовых импульсов и к считывающему входу второго регистра памяти, информационные входы, считывающие входы и выходы Q регистров памяти линейки регистров памяти являются соответствующими Q информационными входами, Q считывающими входами и Q выходами линейки регистров памяти.10. Устройство по п.8 или 9, отличающееся тем, что определитель веса параметра помех состоит из (Q+1)-гo регистров памяти и Q вычислителей, вторые входы которых объединены и подключены к выходу (Q+1)-гo регистра памяти, информационный вход которого является (Q+1)-м информационным входом определителя, а считывающий вход (Q+1)-гo регистра памяти соединен с считывающими входами остальных Q регистров памяти и является управляющим входом определителя, информационные входы первого, второго,..., Q-го регистров памяти являются соответствующими Q информационными входами определителя, выходы первого, второго,..., Q-го регистров памяти подключены к первым входам соответствующих Q вычислителей, выходы которых являются соответствующими Q выходами определителя.11. Устройство по любому из пп.1-4, 8, отличающееся тем, что блок определения показателей качества частот состоит из S линеек регистров памяти, каждая из которых содержит Q регистров памяти, и Q сумматоров, выходы которых являются соответствующими Q выходами блока, а j-й вход q-го сумматора, где j=1, 2,..., S, a q=1, 2,..., Q, соединен с q-м выходом j-й линейки регистров памяти, Q информационных входов j-й линейки регистров памяти являются соответствующими Q информационными входами j-й группы информационных входов блока, считывающие входы всех линеек регистров памяти объединены и являются управляющим входом блока, считывающие входы Q регистров памяти j-й линейки регистров памяти объединены и являются считывающим входом j-й линейки регистров памяти, информационные входы и выходы Q регистров памяти j-й линейки регистров памяти являются соответствующими Q информационными входами и Q выходами j-й линейки регистров памяти.12. Устройство по любому из пп.1-4, 8, 11, отличающееся тем, что блок определения пригодности частот состоит из линейки регистров памяти, содержащей Q регистров памяти, линейки элементов сравнения, содержащей Q элементов сравнения, и регистра памяти, считывающий вход которого соединен со считывающим входом линейки регистров памяти и является управляющим входом блока, информационный вход регистра памяти является (Q+1)-м информационным входом блока, а выход регистра памяти подключен к (Q+1)-му входу линейки элементов сравнения, Q выходов которой являются соответствующими Q выходами блока, а ее первый, второй,..., Q-й входы подключены соответственно к первому, второму,..., Q-му выходам линейки регистров памяти, Q информационных входов которой являются соответствующими Q информационными входами блока, считывающие входы Q регистров памяти линейки регистров памяти объединены и являются считывающим входом линейки регистров памяти, информационные входы и выходы Q регистров памяти линейки регистров памяти являются соответствующими Q информационными входами и Q выходами линейки регистров памяти, вторые входы Q элементов сравнения линейки элементов сравнения объединены и являются (Q+1)-м входом линейки элементов сравнения, первые входы и выходы Q элементов сравнения линейки элементов сравнения являются соответствующими Q входами и Q выходами линейки элементов сравнения.13. Устройство по любому из пп.1-4, 8, 11 и 12, отличающееся тем, что блок отбраковки частот состоит из первой и второй линеек регистров памяти, каждая из которых содержит Q регистров памяти, и линии задержки, вход которой соединен со считывающим входом первой линейки регистров памяти и является управляющим входом блока, выход линии задержки подключен к считывающему входу второй линейки регистров памяти, Q выходов которой являются соответствующими Q выходами блока, а Q информационных входов второй линейки регистров памяти являются соответствующими Q информационными входами 1-й группы информационных входов блока, Q входов установки начального состояния второй линейки регистров памяти подключены к соответствующим Q выходам первой линейки регистров памяти, Q информационных входов которой являются соответствующими Q информационными входами 2-й группы информационных входов блока, считывающие входы Q регистров памяти первой линейки регистров памяти объединены и являются считывающим входом первой линейки регистров памяти, информационные входы и выходы Q регистров памяти первой линейки регистров памяти являются соответствующими Q информационными входами и Q выходами первой линейки регистров памяти, считывающие входы Q регистров памяти второй линейки регистров памяти объединены и являются считывающим входом второй линейки регистров памяти, входы установки начального состояния Q регистров памяти второй линейки регистров памяти являются соответствующими Q входами установки начального состояния второй линейки регистров памяти, информационные входы и выходы Q регистров памяти второй линейки регистров памяти являются соответствующими Q информационными входами и Q выходами второй линейки регистров памяти.14. Устройство по любому из пп.1-4, 8, 11, 12 и 13, отличающееся тем, что блок выбора оптимальной частоты состоит из первой и второй линеек регистров памяти, каждая из которых содержит Q регистров памяти, первого, второго и третьего элементов ИЛИ, первого, второго и третьего регистров памяти, первой, второй и третьей линий задержки, первого и второго ключей, элемента сравнения, распределителя импульсов и генератора тактовых импульсов, вход запуска которого соединен с входом первой линии задержки и является управляющим входом блока, выход генератора тактовых импульсов подключен к входу распределителя импульсов, Q выходов которого подключены к соответствующим Q считывающим входам первой и второй линеек регистров памяти, а v-й выход распределителя импульсов, где v=2, 3,..., Q, дополнительно подключен к w-му входу первого элемента ИЛИ, где w=(v-1), выход которого подключен к считывающему входу первого регистра памяти, информационный вход которого подключен к выходу второго элемента ИЛИ, первый и второй входы которого подключены соответственно к выходу первого ключа и к первому выходу первой линейки регистров памяти, Q входов которой являются соответствующими Q входами блока, второй выход первой линейки регистров памяти подключен к входу второй линии задержки и второму входу элемента сравнения, первый вход которого подключен к выходу первого регистра памяти, а выход элемента сравнения подключен ко вторым входам первого и второго ключей, первый вход первого ключа подключен к выходу второй линии задержки, первый вход второго ключа подключен к выходу третьей линии задержки, вход которой подключен ко второму выходу второй линейки регистров памяти, первый выход которой подключен к первому входу третьего элемента ИЛИ, второй вход которого подключен к выходу второго ключа, а выход третьего элемента ИЛИ подключен к информационному входу второго регистра памяти, выход которого подключен к информационному входу третьего регистра памяти, считывающий вход и выход которого являются соответственно считывающим входом и выходом блока, выход первой линии задержки подключен к входу остановки генератора тактовых импульсов и к считывающему входу второго регистра памяти, причем считывающие и информационные входы Q регистров памяти первой линейки регистров памяти являются соответствующими Q считывающими и Q информационными входами первой линейки регистров памяти, выход первого регистра памяти первой линейки регистров памяти является первым выходом первой линейки регистров памяти, выходы второго, третьего,..., Q-го регистров памяти первой линейки регистров памяти объединены и являются вторым выходом первой линейки регистров памяти, считывающие входы Q регистров памяти второй линейки регистров памяти являются соответствующими Q считывающими входами второй линейки регистров памяти, выход первого регистра памяти второй линейки регистров памяти является первым выходом второй линейки регистров памяти, выходы второго, третьего,..., Q-го регистров памяти второй линейки регистров памяти объединены и являются вторым выходом второй линейки регистров памяти.