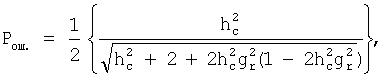

Изобретение относится к технике радиосвязи и может быть использовано для оперативного выбора рабочих частот на пунктах ионосферно-волновой и частотно-диспетчерской службы радиоцентров в условиях изменчивости помеховой обстановки и ограниченности частотного ресурса.

Известны устройства автоматического выбора рабочих частот (см., например, а.с. СССР №1573538, 1987 г., опубл. 23.06.90, бюллетень №23, а.с. СССР №1501284, заявл. 13.05.87, опубл. 15.08.89, бюллетень №30, патент РФ №2220503, заявл. 26.04.2002 г., опубл. 27.12.2003, бюллетень №36).

Устройство по а.с. СССР №1573538 1987 г.содержит соединенные последовательно антенный коммутатор, радиоприемник, блок фильтров, блок анализа, блок выбора частоты и блок оперативной памяти, а также блок управления, блок определения занятости рабочей частоты, блок хранения исходных данных и блок отбраковки частот. Данное устройство производит оценку и выбор рабочих частот на основе последовательного измерения уровней помех на каждой анализируемой частоте и сравнения этого значения с допустимым (пороговым) значением, величина которого определяется заданным качеством связи. При этом в качестве рабочей частоты выбирается частота с минимальным уровнем помех из группы частот, удовлетворяющих заданному качеству связи.

Недостатком известного устройства анализа и выбора рабочих частот является относительно низкая достоверность выбора оптимальных рабочих частот (под оптимальной рабочей частотой понимается такая частота, на которой обеспечивается максимальная длительность работы радиолинии без перестройки на другие частоты).

Устройство автоматического выбора рабочих частот по а.с. СССР №1501284, заявл. 13.05.87, опубл. 15.08.89, бюллетень №30, состоит из антенного блока, приемника, блока фильтров, блока анализа, блока выбора частоты, блока оперативной памяти, блока управления, блока определения занятости рабочей частоты, блока памяти номеров частот, выделенных для каждого радионаправления, блока памяти номеров антенн для каждого радионаправления, блока памяти номеров фильтров, блока памяти пороговых уровней помех, первого дешифратора, второго дешифратора, блока памяти разрешенных для связи частот.

Антенный коммутатор, радиоприемник, блок фильтров и блок анализа соединены последовательно по информационным входам. М антенных входов антенного коммутатора, где М≥2 подключены к соответствующим М антеннам, М управляющих входов антенного блока соединены с соответствующими М выходами первого дешифратора, вход первого дешифратора соединен с выходом блока памяти номеров антенн для каждого радионаправления, F управляющих входов радиоприемника, где F≥2 соединены с соответствующими F выходами третьего дешифратора, выход "Конец настройки" радиоприемника соединен с управляющим входом блока анализа, Р управляющих входов блока фильтров, где Р≥2 соединены с соответствующими Р выходами второго дешифратора, вход второго дешифратора соединен с выходом блока памяти номеров фильтров, первый, второй, и третий выходы "Код радионаправления" блока управления соединены соответственно с адресными входами блока памяти номеров антенн для каждого радионаправления, блока памяти номеров фильтров и блока памяти пороговых уровней помех, выход "Код частоты" блока управления соединен с адресным входом блока памяти номеров частот, четвертый выход "Код радионаправления" блока управления соединен с входами "Код радионаправления" соответственно блока памяти номеров частот и блока определения занятости рабочей частоты, выход "Считывание" блока управления соединен с входами "Считывание" блоков памяти номеров антенн, номеров фильтров, пороговых уровней помех и номеров частот, N входов номеров радионаправлений блока управления, где N≥2 являются входами номеров радионаправления устройства, выходы "Окончание анализа" и "Уровень помехи" блока анализа соединены соответственно с входами "Запись уровня помехи" и "Уровень помех" блока выбора частоты, выход блока памяти номеров частот соединен с входом третьего дешифратора, входом "Частота" блока оперативной памяти и входом "Код текущей частоты" блока определения занятости рабочей частоты, выход блока памяти пороговых уровней помех соединен с входом "Пороговый уровень помехи" блока выбора частоты, выход "Запись порогового уровня" блока управления соединен с входом "Запись порогового уровня" блока выбора частоты, выход "Частота свободна" блока определения занятости рабочей частоты соединен с входом "Разрешение анализа" блока выбора частоты, первый и второй выходы "Конец выбора частоты" блока выбора частоты соединены соответственно с входом "Запись" блока оперативной памяти и с входом "Конец цикла выбора частоты" блока управления. Выход блока оперативной памяти, являющийся выходом устройства, соединен с входом "Номинальное значение выбранной частоты" блока определения занятости рабочей частоты, выход "Считывание выбранной частоты" блока управления соединен с входом "Считывание" блока оперативной памяти и с входом "Начало анализа" блока определения занятости рабочей частоты.

Устройство осуществляет выбор оптимальных рабочих частот путем последовательного измерения уровней мощности помех на анализируемых частотах и сравнения измеренных значений с пороговым значением, величина которого определяется заданным качеством связи. При этом в качестве оптимальной рабочей частоты выбирается частота с минимальным текущим значением уровней помех из группы частот, удовлетворяющих заданному качеству связи.

Недостатком устройства является относительно низкая достоверность выбора оптимальных рабочих частот, обеспечивающих максимальную длительность работы радиолиний без перестройки на другие частоты. Это объясняется учетом при выборе оптимальной рабочей частоты информации только об одном параметре уровней помех - текущем значении уровней помех на анализируемых частотах.

Наиболее близким по технической сущности к заявляемому устройству является устройство автоматического выбора рабочих частот, описанное в патенте РФ №2220503, заявл. 26.04.2002, опубл. 27.12.2003, бюллетень №36.

Устройство автоматического выбора рабочих частот, содержащее каскадно-соединенные по информационным входам антенный коммутатор, радиоприемник, блок фильтров, блок анализа и блок распределения, управляющий вход которого соединен с первым управляющим выходом блока управления, управляющий вход блока анализа подключен к выходу "Конец настройки" радиоприемника, F управляющих входов которого, где F≥2, подключены к соответствующим F выходам третьего дешифратора, вход которого подключен к выходу блока памяти номеров частот, Р управляющих входов блока фильтров, где Р≥2 подключены к соответствующим Р выходам второго дешифратора, вход которого подключен к выходу блока памяти номеров фильтров, М антенных входов антенного коммутатора, где М≥2 подключены к выходам соответствующих М антенн, М управляющих входов антенного коммутатора подключены к соответствующим М выходам первого дешифратора, вход которого подключен к выходу блока памяти номеров антенн, считывающий вход которого подключен к считывающим входам блоков памяти номеров частот, номеров фильтров, блока памяти пороговых уровней помех и к считывающему выходу блока управления, N входов номеров радионаправления которого, где N≥2 являются соответствующими N входами радионаправлений устройства, первый, второй и третий выходы "Код радионаправления" блока управления подключены к адресным входам соответственно блока памяти номеров антенн, блока памяти номеров фильтров, блок памяти пороговых уровней помех, вход "Код радионаправления" блока памяти номеров частот подключен к четвертому выходу "Код радионаправления" блока управления, выход "Код частоты" блока управления подключен к адресному входу блока памяти номеров частот, а вход остановки работы блока управления является входом остановки работы устройства, Q информационных выходов блока распределения, где Q≥2 подключены к соответствующим Q информационным входам первой группы информационных входов блока определения весов анализируемых частот, к Q информационным входам определения пригодности частот и к Q информационным входам блока определения дополнительных параметров помех, Q информационных выходов i-й группы выходов которого, где i=2, 3,..., S, a S - количество анализируемых параметров помех, подключены к соответствующим Q информационным входам i-й группы информационных входов блока определения весов анализируемых частот, Q информационных выходов j-й группы которого, где j=1, 2,..., S, подключены к соответствующим Q информационным входам j-й группы информационных входов блока определения показателей качества частот, Q информационных выходов которого подключены к соответствующим Q информационным входам блока отбраковки частот, вторые Q информационных входов которого подключены к соответствующим Q информационным выходам блока определения пригодности частот, второй информационный вход которого подключен к информационному выходу блока памяти пороговых уровней помех, Q информационных выходов блока отбраковки частот подключены к Q информационным входам блока выбора оптимальной частоты, второй, третий, четвертый, пятый, шестой и седьмой управляющие выходы блока управления подключены к управляющим входам соответственно блока определения дополнительных параметров помех, блока определения весов анализируемых частот, блока определения показателей качества частот, блока отбраковки частот, блока определения пригодности частот, блока выбора оптимальной частоты, при этом считывающий вход блока выбора оптимальной частоты является считывающим входом устройства, а информационный выход является соответственно информационным выходом устройства.

Устройство-прототип осуществляет выбор оптимальных рабочих частот путем последовательного измерения уровней помех и дополнительных параметров помех (математического ожидания, дисперсии уровней помех и др.) на анализируемых частотах и их одновременного учета для формирования значений сумм весовых коэффициентов на Q анализируемых частотах. При этом в качестве оптимальной рабочей частоты выбирается частота с максимальным значением сумм скорректированных весов анализируемых частот.

Недостатком прототипа является относительно низкая достоверность выбора оптимальных частот, так как оптимальная рабочая частота в данном устройстве выбирается по текущему уровню мощности помех на анализируемых частотах меньше порогового и дополнительных параметров помех (математическое ожидание, дисперсии уровней помех), то есть учитывает только энергетическую составляющую помехи и ее статистические характеристики.

Целью изобретения является разработка устройства автоматического выбора рабочих частот, обеспечивающего повышение достоверности выбора оптимальных рабочих частот с соответствующим режимом работы за счет учета кроме энергетической составляющей помехи и ее статистических характеристик частотно-временных различий сигнала и помехи.

Для достижения сформулированной цели в известном устройстве автоматического выбора рабочих частот, содержащем каскадно-соединенные по информационным входам антенный коммутатор, радиоприемник, блок фильтров, блок анализа и блок распределения, управляющий вход которого соединен с девятым управляющим выходом блока управления, управляющий вход блока анализа подключен к выходу "Конец настройки" радиоприемника, F управляющих входов которого, где F≥2, подключены к соответствующим F выходам третьего дешифратора, вход которого подключен к выходу блока памяти номеров частот. Р управляющих входов блока фильтров, где Р≥2, подключены к соответствующим Р выходам второго дешифратора, вход которого подключен к выходу блока памяти номеров фильтров. М антенных входов антенного коммутатора, где М≥2, подключены к выходам соответствующих М антенн. М управляющих входов антенного коммутатора подключены к соответствующим М выходам первого дешифратора. Вход первого дешифратора подключен к выходу блока памяти номеров антенн, считывающий вход которого подключен к считывающим входам блоков памяти номеров частот, номеров фильтров и к считывающему выходу блока управления. N входов номеров радионаправления блока управления, где N≥2, являются соответствующими N входами радионаправлений устройства. Первый, второй и четвертый выходы "Код радионаправления" блока управления подключены к адресным входам соответственно блока памяти номеров антенн, блока памяти номеров фильтров и к входу "Код радионаправления" блока памяти номеров частот. Выход "Код частоты" блока управления подключен к адресному входу блока памяти номеров частот, а вход остановки работы блока управления является входом остановки работы устройства. Q информационных выходов блока распределения, где Q≥2, подключены к соответствующим Q информационным входам первой группы информационных входов блока определения весов анализируемых частот, к Q информационным входам блока определения дополнительных параметров помех. Q информационных выходов i-й группы выходов блока определения дополнительных параметров помех, где i=2, 3,..., S, a S - количество анализируемых параметров помех, подключены к соответствующим Q информационным входам i-й группы информационных входов блока определения весов анализируемых частот. Q информационных выходов j-й группы блока определения весов анализируемых частот, где j=1, 2,..., S, подключены к соответствующим Q информационным входам j-й группы информационных входов блока определения показателей качества частот. Одиннадцатый, двенадцатый, тринадцатый управляющие выходы блока управления подключены к управляющим входам соответственно блоков определения дополнительных параметров помех, определения весов анализируемых частот и определения показателей качества частот. Дополнительно введены блок памяти вероятности ошибки допустимой, блок прогнозируемого значения мощности сигнала, блок определения текущей вероятности ошибочного приема, блок усреднения и сравнения коэффициента взаимного различия при различных видах работы, блок быстрого преобразования Фурье, блок определения условных коэффициентов взаимного различия, блок запоминания коэффициента Фурье помехи, блок запоминания коэффициентов Фурье эталонных сигналов, блок определения пригодности частот, блок запоминания пригодных частот, блок запоминания непригодных частот, блок отбраковки частот с учетом коэффициента различия, блок выбора оптимальной частоты и режима работы. При этом информационный выход блока фильтров подключен к информационному входу блока быстрого преобразования Фурье, информационный выход которого подключен соответственно к информационному входу запоминающего устройства коэффициентов Фурье помехи, управляющий вход которого подключен ко второму управляющему выходу блока управления. Первый управляющий выход блока управления подключен к управляющему входу блока быстрого преобразования Фурье, считывающий выход блока управления подключен к считывающему входу блока памяти вероятности ошибки, а третий выход "Код радионаправления" блока управления подключен к адресному входу блока памяти вероятности ошибки допустимой. Выход блока памяти вероятности ошибки допустимой подключен ко второму входу блока определения пригодности частот, управляющий вход которого подключен к третьему управляющему выходу блока управления, четвертый управляющий выход которого подключен к управляющему входу блока запоминания непригодных частот. Информационный вход блока запоминания непригодных частот подключен к первому информационному выходу блока определения пригодности частот, первый информационный вход которого подключен к информационному выходу блока определения текущей вероятности ошибочного приема. Второй информационный выход блока определения пригодности частот подключен к информационному входу блока запоминания пригодных частот, управляющий вход которого подключен к седьмому управляющему выходу блока управления. Пятый и шестой управляющие выходы блока управления подключены к управляющим входам соответственно блока определения условных коэффициентов взаимного различия и блока определения текущей вероятности ошибочного приема. Информационный выход блока запоминания коэффициентов Фурье помехи подключен к первому информационному входу блока определения условных коэффициентов взаимного различия, второй информационный вход которого подключен к информационному выходу блока запоминания коэффициента Фурье эталонных сигналов. Информационный выход блока определения условных коэффициентов взаимного различия подключен к информационному входу блока усреднения и сравнения коэффициента взаимного различия при различных видах работы, управляющий вход которого подключен к девятому выходу блока управления. Восьмой управляющий выход блока управления подключен к управляющему входу блока запоминания коэффициента Фурье эталонных сигналов. N адресных выходов блока усреднения и сравнения коэффициента взаимного различия подключены к N адресным входам блока выбора оптимальной частоты и режима работы. Информационный выход блока усреднения и сравнения коэффициента взаимного различия при различных видах работы подключен к первому информационному входу блока определения текущей вероятности ошибочного приема. Второй и третий информационные входы блока определения текущей вероятности ошибочного приема подключены к информационным выходам соответственно блока анализа и блока прогнозируемого значения мощности сигнала. К адресному входу блока прогнозируемого значения мощности сигнала подключен пятый выход "Код радионаправления" блока управления. К считывающему входу блока прогнозируемого значения мощности сигнала подключен считывающий выход блока управления. Q выходов блока запоминания пригодных частот подключены к соответствующим Q - входам второй группы информационных входов блока отбраковки частот с учетом дополнительных параметров, управляющий вход которого подключен к четырнадцатому управляющему выходу блока управления. Пятнадцатый управляющий выход блока управления подключен к управляющему входу блока выбора оптимальной частоты и режима работы. Q - входов выбора оптимальной частоты и режима работы подключены к соответствующим Q - выходам блока отбраковки частот с учетом коэффициента различия. Q - входов первой группы информационных входов блока отбраковки частот с учетом коэффициента различия подключены к соответствующим Q информационным выходам блока определения показателей качества частот. При этом считывающий вход блока выбора оптимальной частоты и режима работы является считывающим входом устройства, первый информационный выход которого является соответственно первым информационным выходом устройства о выбранной частоте, а второй информационный выход которого является соответственно вторым информационным выходом устройства о виде работы на выбранной частоте.

Благодаря новой совокупности существенных признаков за счет введения блоков памяти вероятности ошибки допустимой, прогнозируемого значения мощности сигнала, определения текущей вероятности ошибочного приема, усреднения и сравнения коэффициента взаимного различия при различных видах работы, быстрого преобразования Фурье, определения условных коэффициентов взаимного различия, запоминания коэффициента Фурье помехи, запоминания коэффициентов Фурье эталонных сигналов, определения пригодности частот, запоминания пригодных частот, запоминания непригодных частот, отбраковки частот с учетом коэффициента различия, блока выбора оптимальной частоты и режима работы, с помощью которых учитываются частотно-временные характеристики сигнала и помехи. Этим достигается возможность более достоверного выбора оптимальных рабочих частот и режима работы.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественными всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности "новизна". Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень". Заявленное устройство поясняется чертежами:

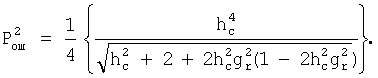

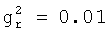

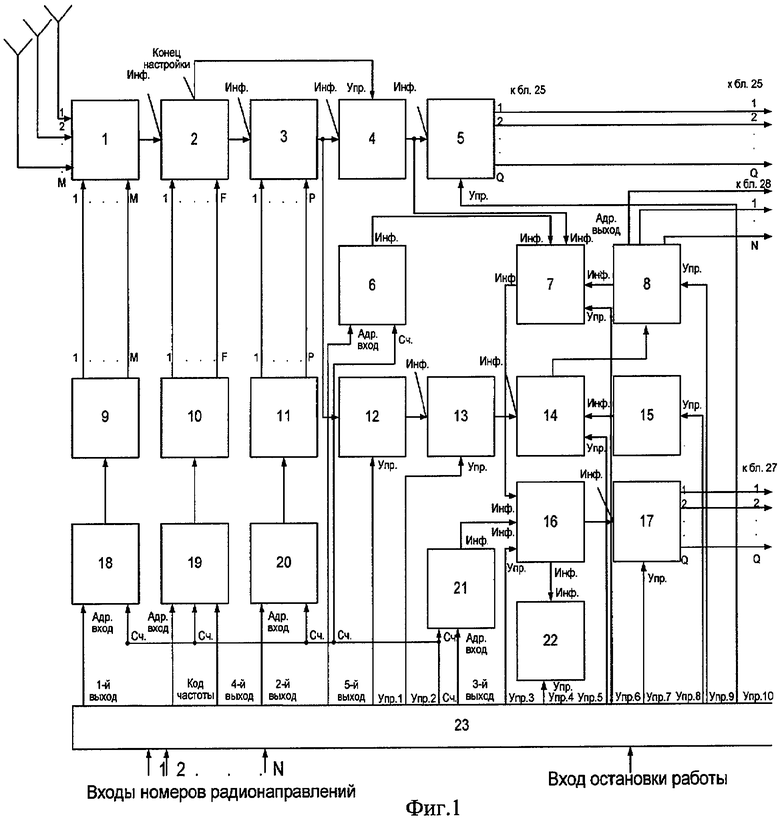

фиг.1 - функциональная схема устройства;

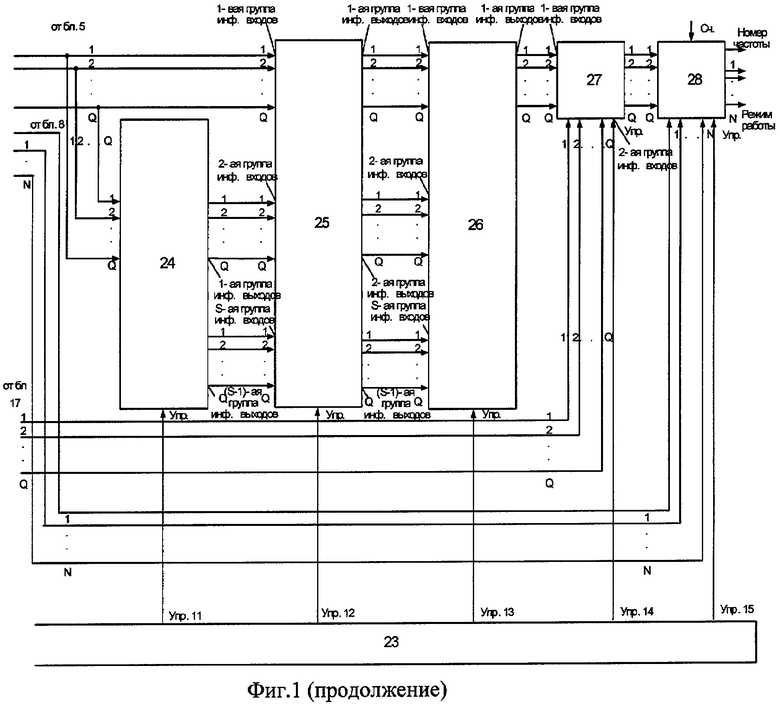

фиг.1 (продолжение) - функциональная схема устройства;

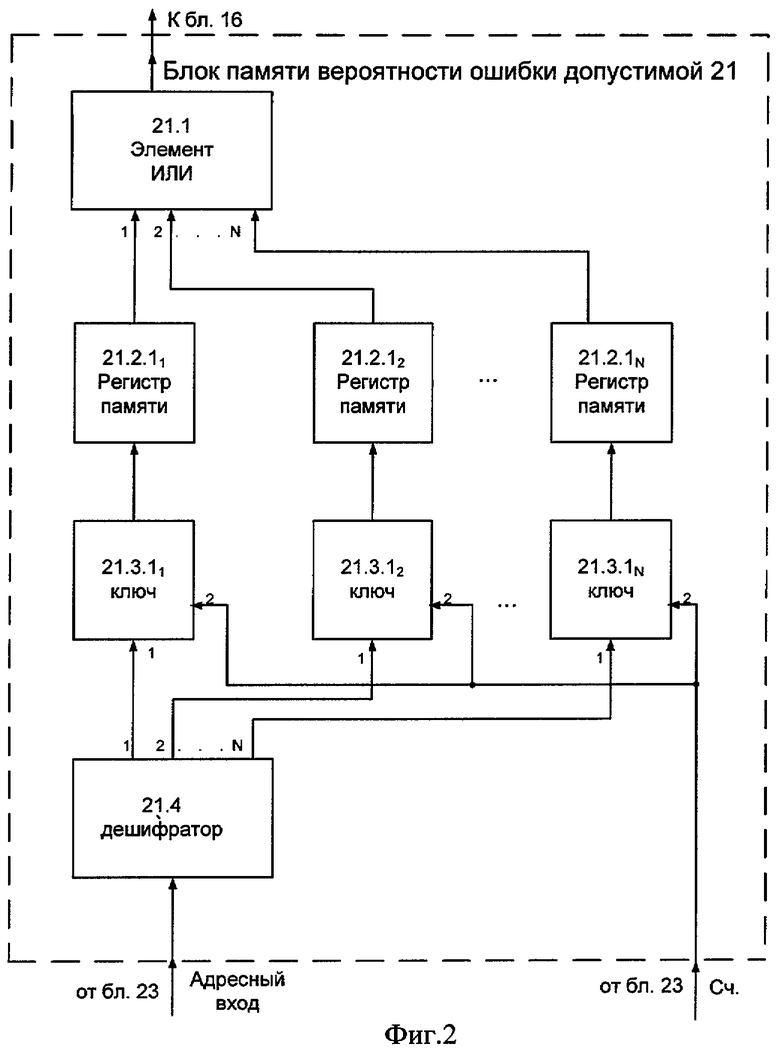

фиг.2 - функциональная схема блока памяти вероятности ошибки допустимой;

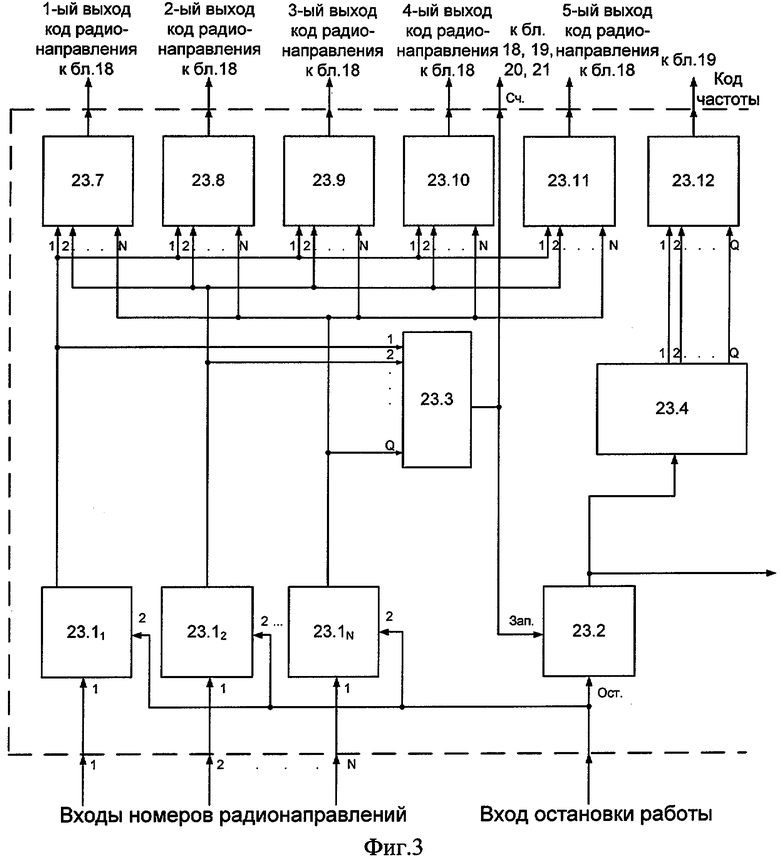

фиг.3 - функциональная схема блока управления;

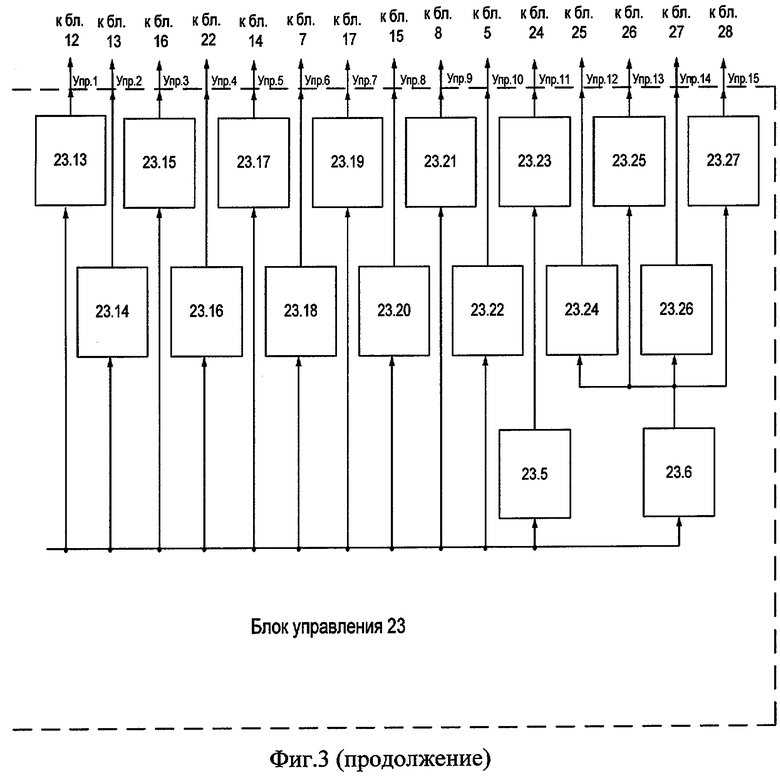

фиг.3 (продолжение) - функциональная схема блока управления;

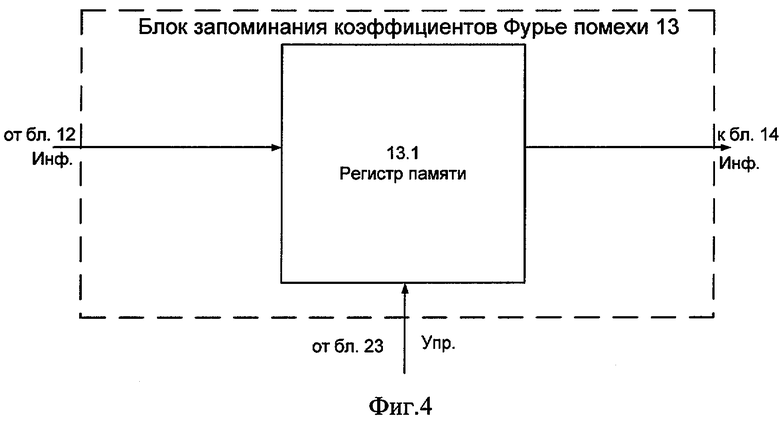

фиг.4 - функциональная схема блока запоминания коэффициентов Фурье помехи;

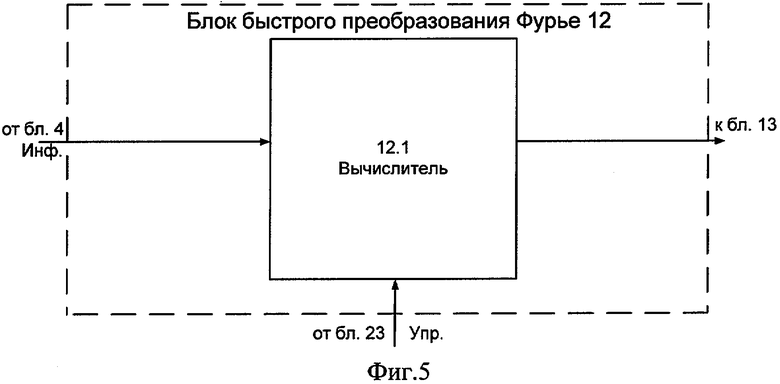

фиг.5 - функциональная схема блока быстрого преобразования Фурье;

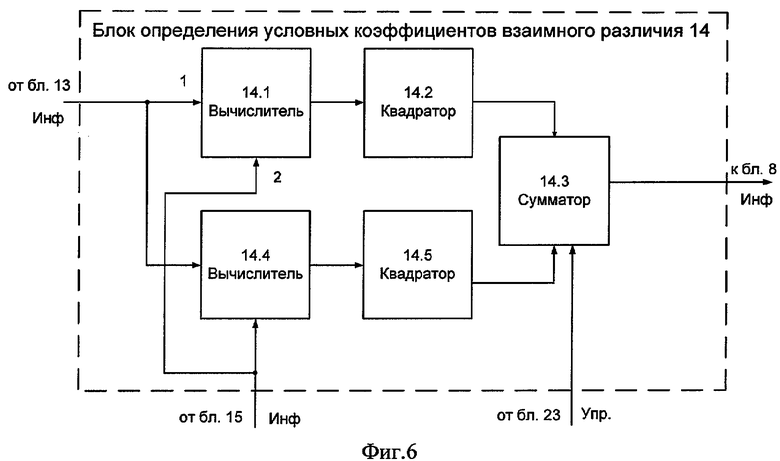

фиг.6 - функциональная схема блока определения условных коэффициентов взаимного различия;

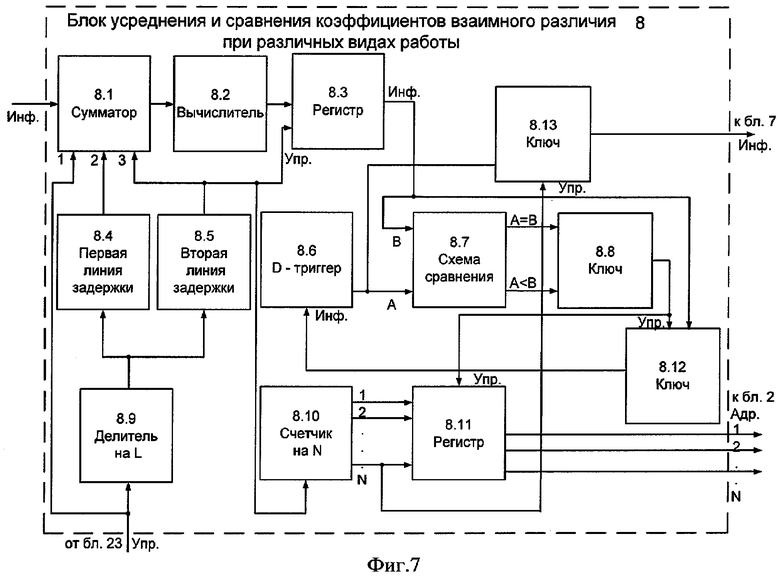

фиг.7 - функциональная схема блока усреднения и сравнения коэффициентов взаимного различия при различных видах работы;

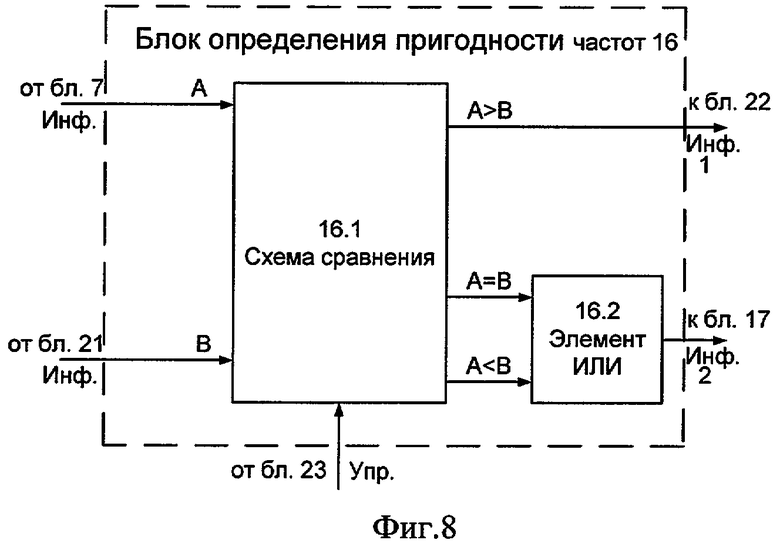

фиг.8 - функциональная схема блока определения пригодности частот;

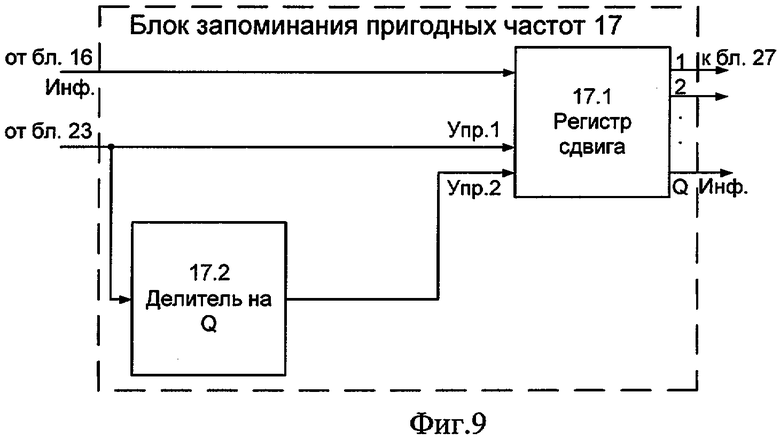

фиг.9 - функциональная схема блока запоминания пригодных частот;

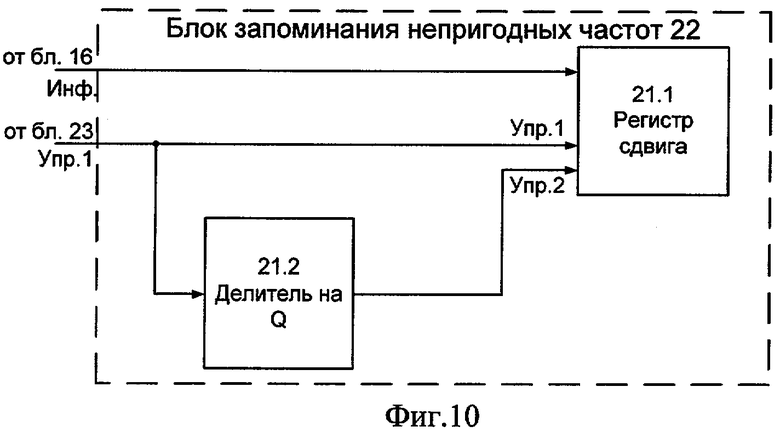

фиг.10 - функциональная схема блока запоминания непригодных частот;

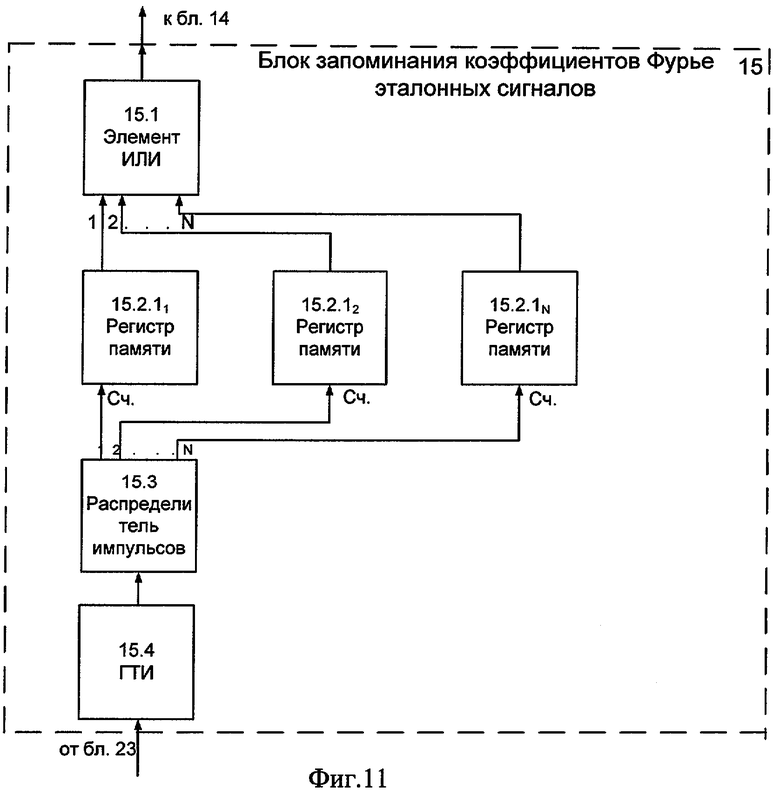

фиг.11 - функциональная схема блока запоминания коэффициентов Фурье эталонных сигналов;

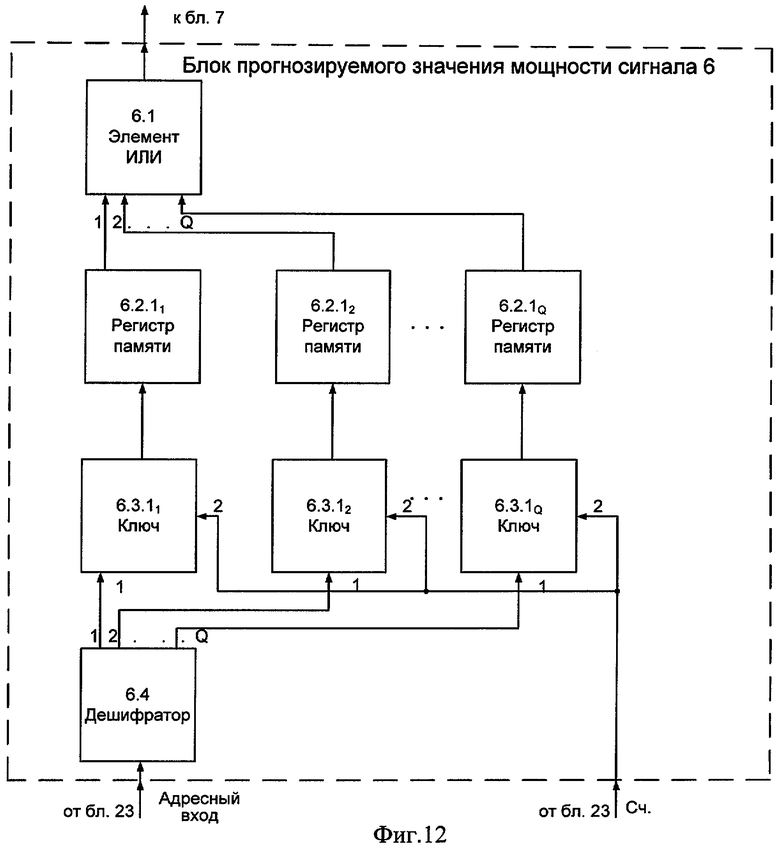

фиг.12 - функциональная схема блока прогнозируемого значения мощности сигнала;

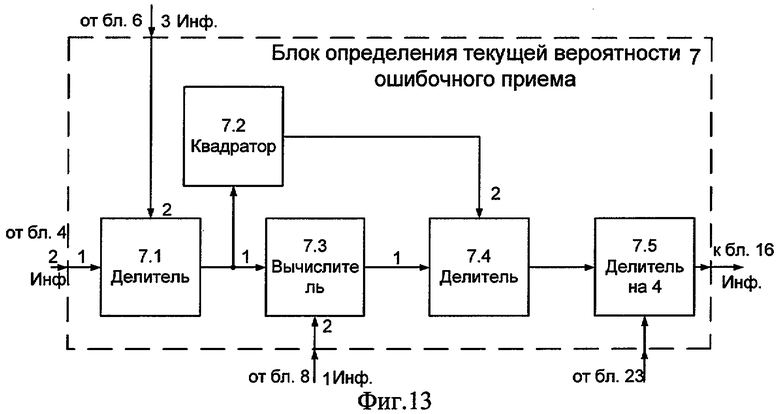

фиг.13 - функциональная схема блока определения текущей вероятности ошибочного приема;

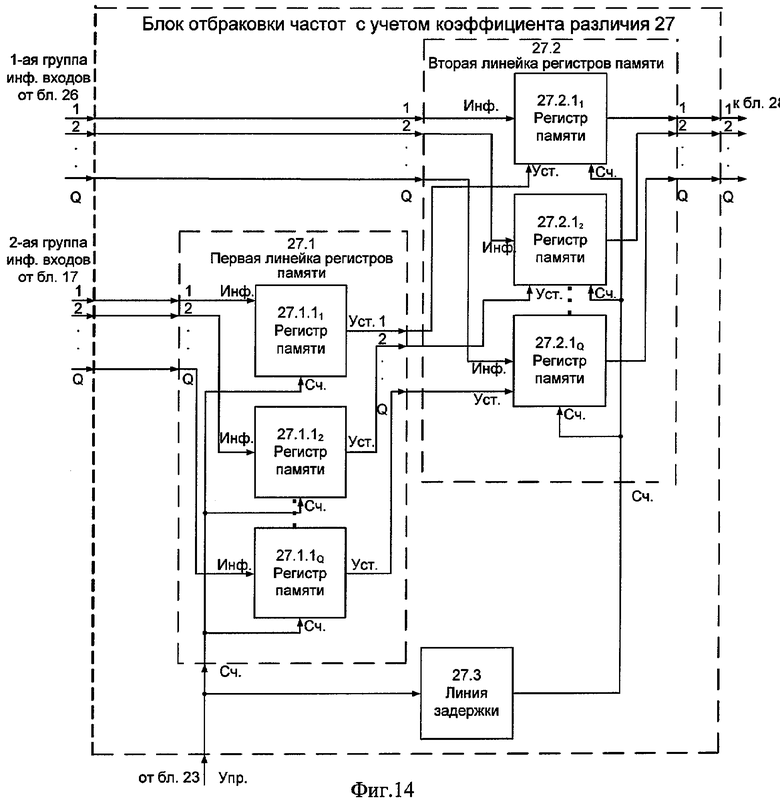

фиг.14 - функциональна схема блока отбраковки частот с учетом коэффициента различия;

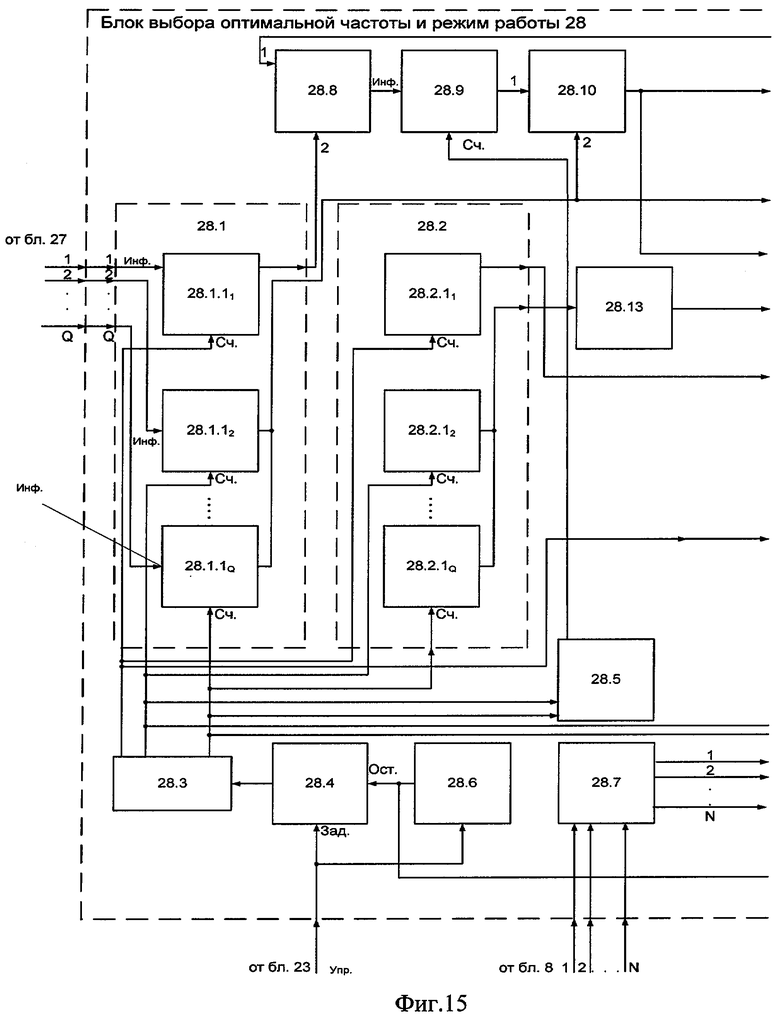

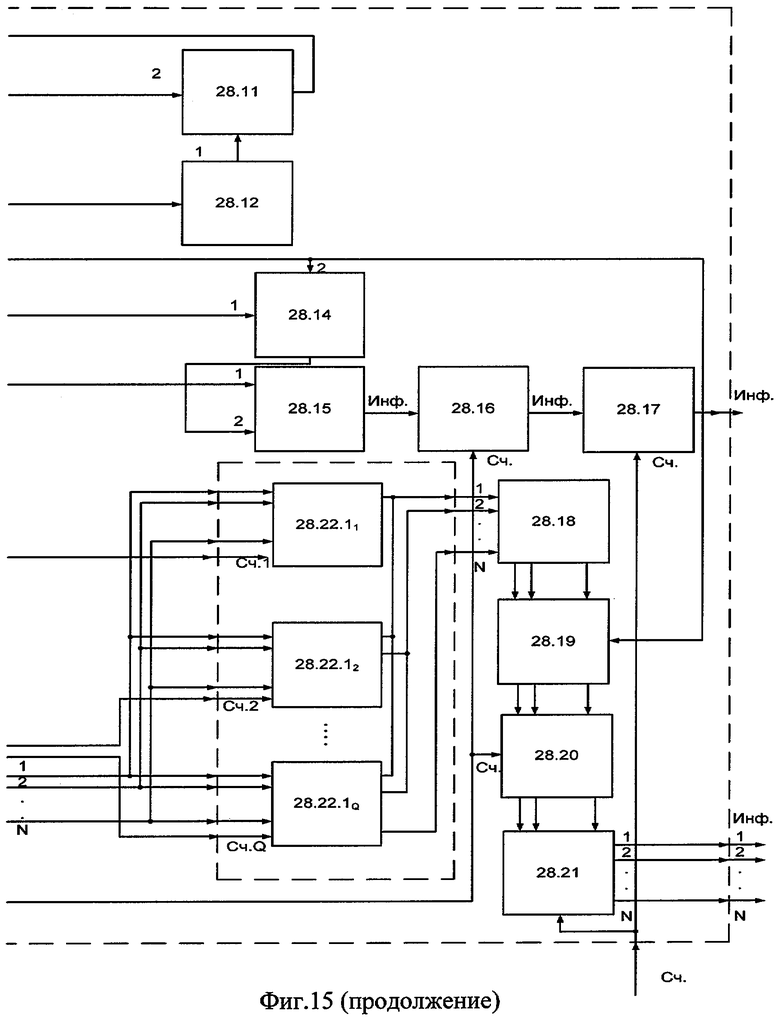

фиг.15 - функциональная схема блока выбора оптимальной частоты и режима работы.

фиг.15 (продолжение) - функциональная схема блока выбора оптимальной частоты и режима работы.

Устройство автоматического выбора рабочих частот, показанное на фиг.1, состоит из антенного коммутатора 1, радиоприемника 2, блока фильтров 3, блока анализа 4, блока распределения 5, блока прогнозируемого значения мощности сигнала 6, блока определения текущей вероятности ошибочного приема 7, блока усреднения и сравнения коэффициентов взаимного различия при различных видах работы 8, первого дешифратора 9, третьего дешифратора 10, второго дешифратора 11, блока быстрого преобразования Фурье 12, блока запоминания коэффициентов Фурье помехи 13, блока определения условных коэффициентов взаимного различия 14, блока запоминания коэффициентов Фурье эталонных сигналов 15, блока определения пригодности частот 16, блока запоминания пригодных частот 17, блока памяти номеров антенн 18, блока памяти номеров частот 19, блока памяти номеров фильтров 20, блока памяти вероятности ошибки допустимой 21, блока запоминания непригодных частот 22, блока управления 23, блока определения дополнительных параметров помех 24, блока определения весов анализируемых частот 25, блока определения показателей качества частот 26, блока отбраковки частот с учетом коэффициента различия 27, блока выбора оптимальной частоты и режима работы 28.

Каскадно-соединенные по информационным входам антенный коммутатор 1, радиоприемник 2, блок фильтров 3, блок анализа 4 и блок распределения 5, управляющий вход которого соединен с девятым управляющим выходом блока управления 23. Управляющий вход блока анализа 4 подключен к выходу "Конец настройки" радиоприемника 2, F управляющих входов которого, где F≥2, подключены к соответствующим F выходам третьего дешифратора 10, вход которого подключен к выходу блока памяти номеров частот 19. Р управляющих входов блока фильтров 3, где Р≥2, подключены к соответствующим Р выходам второго дешифратора 11, вход которого подключен к выходу блока памяти номеров фильтров 20. М антенных входов антенного коммутатора 1, где М≥2, подключены к выходам соответствующих М антенн. М управляющих входов антенного коммутатора 1 подключены к соответствующим М выходам первого дешифратора 9, вход которого подключен к выходу блока памяти номеров антенн 18. Считывающий вход блока памяти номеров антенн 18 подключен к считывающим входам блоков памяти номеров частот 19, номеров фильтров 20, прогнозируемого значения мощности сигнала 6 и к считывающему выходу блока управления 23. N входов номеров радионаправления блока управления 23, где N≥2, являются соответствующими N входами радионаправлений устройства. Первый, второй, третий, четвертый и пятый выходы "Код радионаправления" блока управления 23 подключены к адресным входам соответственно блока памяти номеров антенн 18, блока памяти номеров фильтров 20, блока памяти вероятности ошибки допустимой 21, блока памяти номеров частот 19 и к входу "Код радионаправления" блока прогнозируемого значения мощности сигнала 6. Выход "Код частоты" блока управления 23 подключен к адресному входу блока памяти номеров частот 19, а вход остановки работы блока управления 23 является входом остановки работы устройства. Q информационных выходов блока распределения 5, где Q≥2, подключены к соответствующим Q информационным входам первой группы информационных входов блока определения весов анализируемых частот 25, к Q информационным входам блока определения дополнительных параметров помех 23, Q информационных выходов i-й группы выходов которого, где i=2, 3,..., S, a S+1 - количество анализируемых параметров помех, подключены к соответствующим Q информационным входам i-й группы информационных входов блока определения весов анализируемых частот 25. Q информационных выходов j-й группы блока определения весов анализируемых частот 25, где j=1, 2,..., S, подключены к соответствующим Q информационным входам j-й группы информационных входов блока определения показателей качества частот 26. Одиннадцатый, двенадцатый, тринадцатый, управляющие выходы блока управления 23 подключены к управляющим входам соответственно блоков определения дополнительных параметров помех 24, определения весов анализируемых частот 25 и определения показателей качества частот 26. Информационный выход блока фильтров 3 подключен к информационному входу блока быстрого преобразования Фурье 12, информационный выход которого подключен к информационному входу блока запоминания коэффициентов Фурье помехи 13. Управляющий вход блока запоминания коэффициентов Фурье помехи 13 подключен ко второму управляющему выходу блока управления 23, первый управляющий выход которого подключен к управляющему входу блока быстрого преобразования Фурье 12. Считывающий выход блока управления 23 подключен к считывающему входу блока памяти вероятности ошибки допустимой 21, а третий выход "Код радионаправления" блока управления 23 подключен к адресному входу блока памяти вероятности ошибки допустимой 21, выход блока памяти вероятности ошибки допустимой 21 подключен ко второму информационному входу блока определения пригодности частот 16, управляющий вход которого подключен к третьему управляющему выходу блока управления 23, четвертый управляющий выход блока управления 23 подключен к управляющему входу блока запоминания непригодных частот 22, информационный вход которого подключен к первому информационному выходу блока определения пригодности частот 16. Первый информационный вход блока определения пригодности частот 16 подключен к информационному выходу блока определения текущей вероятности ошибочного приема 7, второй информационный выход блока определения пригодности частот 16 подключен к информационному входу блока запоминания пригодных частот 17, управляющий вход которого подключен к седьмому управляющему выходу блока управления 23. Пятый и шестой управляющие выходы блока управления 23 подключены к управляющим входам соответственно блока определения условных коэффициентов взаимного различия 14 и блока определения текущей вероятности ошибочного приема 7, информационный выход блока запоминания коэффициентов Фурье помехи 13 подключен к первому информационному входу блока определения условных коэффициентов взаимного различия 14. Второй информационный вход блока определения условных коэффициентов взаимного различия 14 подключен к информационному выходу блока запоминания коэффициента Фурье эталонных сигналов 15. Информационный выход блока определения условных коэффициентов взаимного различия 14 подключен к информационному входу блока усреднения и сравнения коэффициента взаимного различия при различных видах работы 8, управляющий вход которого подключен к девятому выходу блока управления 23. N адресных выходов блока усреднения и сравнения коэффициента взаимного различия 8 подключены к N адресным входам блока выбора оптимальной частоты и режима работы 28. Восьмой управляющий выход блока управления 23 подключен к управляющему входу блока запоминания коэффициента Фурье эталонных сигналов 15, информационный выход блока усреднения коэффициента взаимного различия 14 подключен к первому информационному входу блока определения текущей вероятности ошибочного приема 7, второй и третий информационные входы которого подключены к первому информационному выходу блока анализа 4 и к информационному выходу блока прогнозируемого значения мощности сигнала 6. Q выходов блока запоминания пригодных частот 17 подключены к соответствующим Q-входам второй группы информационных входов блока отбраковки частот с учетом коэффициента различия 27, управляющий вход которого подключен к четырнадцатому управляющему выходу блока управления 23, пятнадцатый управляющий выход которого подключен к управляющему входу блока выбора оптимальной частоты и режима работы 28. Q-входов блока выбора оптимальной частоты и режима работы 28 подключены к соответствующим Q-выходам блока отбраковки частот с учетом коэффициента различия 27, Q-входов первой группы информационных входов которого подключены к соответствующим Q информационным выходам блока определения показателей качества частот 26, при этом считывающий вход блока выбора оптимальной частоты и режима работы 28 является считывающим входом устройства. Первый информационный выход блока выбора оптимальной частоты и режима работы 28 является информационным выходом информации о выбранной частоте, второй информационный выход которого является информационным выходом информации о режиме работы.

Антенный коммутатор 1 предназначен для коммутации одной из М антенн к входу радиоприемника 2. В качестве антенного коммутатора 1 может быть использован любой серийно выпускаемый промышленностью антенный коммутатор, принципы построения которого известны и описаны, например, в книге В.Д.Челышева "Приемные радиоцентры" (М.: Связь, 1975, с.219-221, рис.10.13, 10.14), в книге "Автоматизированная радиосвязь с судами" / Под ред. К.А.Семенова (Л.: Судостроение, 1989, с.175-187, рис.4.9), а также реализованный промышленностью антенный коммутатор, схема которого приведена в техническом описании и инструкции по эксплуатации (коммутатор антенный, ТП12.242.036, книга №6, 1976, с.9).

Радиоприемник 2 предназначен для преобразования высокочастотного колебания в первичный электрический сигнал. В качестве радиоприемника 2 может быть использован любой серийно выпускаемый промышленностью радиоприемник, принципы построения которого известны и описаны, например, в книге О.В.Головина "Радиоприемные устройства" (М.: Высшая школа, 1987).

Блок фильтров 3 предназначен для подключения фильтра с требуемой полосой пропускания между выходом радиоприемника 2 и входом "Уровень помехи" блока анализа 4. В качестве блока фильтров 3 может быть использован любой серийно реализованный промышленностью блок фильтров, схема которого приведена в техническом описании устройства автоматического выбора частот (аппаратура Р-015, ТШ1.170.005, книга №1, 1975, с.114-115).

Блок анализа 4 предназначен для преобразования значения напряжения помех в цифровой код. В качестве блока анализа 4 может быть использован любой серийно реализованный промышленностью блок анализа, схема которого приведена в техническом описании на аппаратуру анализа и выбора частот (аппаратура Р-015, ТШ1.170.005, книга №1, 1975, с.72-83, рис.12).

Первый дешифратор 9 предназначен для преобразования сигнала, характеризующего код номера антенны на его входе, в сигнал, характеризующий номер используемой антенны, на одном из его М выходов. Схема дешифратора известна и описана в книге Л.М.Гольденберга, Ю.Т.Поляка, М.X.Поляка "Цифровые устройства на интегральных схемах в технике связи" (М.: Связь, 1979, с.43-47, рис.2.14, 2.15).

Второй дешифратор 11 предназначен для преобразования сигнала, характеризующего код номера фильтра на его входе, в сигнал, характеризующий номер используемого фильтра, на одном из его Р выходов. Схема дешифратора известна и описана в книге Л.М.Гольденберга, Ю.Т.Поляка, М.X.Поляка "Цифровые устройства на интегральных схемах в технике связи" (М.: Связь, 1979, с.43-47, рис.2.14, 2.15).

Третий дешифратор 10 предназначен для преобразования сигнала, характеризующего код анализируемой частоты на его входе, в сигнал, характеризующий номер анализируемой частоты, на одном из его F выходов. Схема дешифратора известна и описана в книге Л.М.Гольденберга, Ю.Т.Поляка, М.X.Поляка "Цифровые устройства на интегральных схемах в технике связи" (М.: Связь, 1979, с.43-47, рис.2.14, 2.15).

Блок памяти номеров антенн 18 предназначен для хранения закодированных значений номеров антенн, закрепленных за каждым из N радионаправлений, обслуживаемых данным устройством автоматического выбора рабочих частот. Схема блока памяти номеров антенн 18 известна и описана в патенте РФ №2220503 и приведена на фиг.3.

Блок памяти номеров фильтров 20 предназначен для хранения закодированных значений номеров фильтров с требуемой полосой пропускания, закрепленных за каждым из N радионаправлений, обслуживаемых данным устройством автоматического выбора рабочих частот. Схема блока памяти номеров фильтров 20 известна и описана в патенте РФ №2220503 и приведена на фиг.4.

Блок памяти вероятности ошибки допустимой 21 предназначен для хранения квадратов допустимых (пороговых) значений вероятности ошибки допустимой каждого из N радионаправлений, обслуживаемых данным устройством автоматического выбора рабочих частот. Схема блока памяти вероятности ошибки допустимой 21 известна и может быть реализована в различных вариантах, например, как показано на фиг.2.

Блок памяти номеров частот 19 предназначен для хранения закодированных значений Q частот, закрепленных за каждым из N радионаправлений, обслуживаемых данным устройством автоматического выбора рабочих частот. Схема блока памяти номеров частот 19 известна и описана в патенте РФ №2220503 и приведена на фиг.6.

Блок управления 23 предназначен для выработки управляющих сигналов и координации работы устройства автоматического выбора рабочих частот. Блок управления 23, показанный на фиг.3, состоит из генератора тактовых импульсов 23.2, распределителя импульсов 23.4, элемента ИЛИ 23.3, первого, второго, третьего, четвертого, пятого и шестого шифраторов 23.1-23.12, первой, второй, третьей, четвертой, пятой, шестой, седьмой, восьмой, девятой, десятой, одиннадцатой, двенадцатой, тринадцатой, четырнадцатой и пятнадцатой линий задержки 23.12-23.27, делителя на Q 23.5, делителя на (Q×L) 23.6 и N триггеров 23.11-23.1N. Первые входы N триггеров 23.11-23.1N являются соответствующими N входами номеров радионаправлений блока 23. Выход n-го триггера 23.1N, где n=1, 2,..., N, подключен к n-му входу элемента ИЛИ 23.3 и к n-му входу первого, второго, третьего, четвертого и пятого шифраторов 23.7-23.11. Выходы первого, второго, третьего, четвертого и пятого шифраторов 23.7-23.11 являются соответственно первым, вторым, третьим, четвертым и пятым выходами "Код радионаправления" блока 23. Вторые входы всех n триггеров 23.11-23.1N объединены и подключены к входу остановки генератора тактовых импульсов 23.2, являющемуся входом остановки работы блока 23.Выход элемента ИЛИ 23.3 подключен к входу запуска генератора тактовых импульсов 232.2 и является выходом "Считывание" блока 23. Выход генератора тактовых импульсов 23.2 подключен к входам первой линии задержки 23.12, делителя на Q 23.5, делителя на (Q×L) 23.6 и распределителя импульсов 23.4. Q выходов распределителя импульсов 23.4 подключены к соответствующим Q входам шестого шифратора 23.12. Выход шестого шифратора 23.12 является выходом "Код частоты" блока 23. Выходы первой, второй, третьей, четвертой, пятой, шестой, седьмой, восьмой, девятой, десятой, одиннадцатой, двенадцатой, тринадцатой, четырнадцатой и пятнадцатой линий задержки 23.13-23.27 являются первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым, девятым, десятым, одиннадцатым, двенадцатым, тринадцатым, четырнадцатым и пятнадцатым управляющими выходами блока 23. Выход делителя на Q 23.5 подключен к входу одиннадцатой линии задержки 23.23. Выход делителя на (Q×L) 23.6 подключен к двенадцатой, тринадцатой, четырнадцатой и пятнадцатой линий задержки 23.24-23.27.

Блок распределения 5 предназначен для распределения поступающих на его вход сигналов между Q его выходами. Схема блока распределения 5 известна и описана в патенте РФ №2220503 и приведена на фиг.8.

Блок определения дополнительных параметров помех 24 предназначен для определения (S-1)-го дополнительного параметра помех на Q анализируемых частотах. Схема блока определения дополнительных параметров помех 24 известна и описана в патенте РФ №2220503 и приведена на фиг.9.

Блок определения весов анализируемых частот 25 предназначен для определения веса измеряемых параметров помех на каждой из Q анализируемых частот. Схема блока определения весов анализируемых частот 25 известна и описана в патенте РФ №2220503 и приведена на фиг.14.

Блок определения показателей качества частот 26 предназначен для определения показателей качества Q анализируемых частот путем суммирования значений весов S анализируемых параметров для каждой из Q анализируемых частот. Схема блока определения показателей качества частот 26 известна и описана в патенте РФ №2220503 и приведена на фиг.17.

Блок запоминания коэффициентов Фурье помехи 13 предназначен для запоминания отсчетов коэффициентов Фурье помехи. Блок запоминания коэффициентов Фурье помехи 13, показанный на фиг.4, состоит из регистра памяти 13.1, информационный вход которого является соответствующим информационным входом информационного входа блока 13. Информационный выход регистра памяти 13.1 является соответствующим информационным выходом блока 13.

Блок быстрого преобразования Фурье 12 предназначен для разложения сигнала, поступающего на его вход, на гармонические составляющие. Блок быстрого преобразования Фурье 12, показанный на фиг.5, состоит из вычислителя 12.1, информационный вход которого является соответствующим информационным входом информационного входа блока 12. Информационный выход вычислителя 12.1 является соответствующим информационным выходом блока 12. Управляющий вход вычислителя 12.1 является соответствующим управляющим входом блока 12.

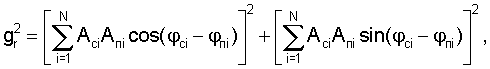

Блок определения условных коэффициентов взаимного различия 14 предназначен для вычисления коэффициента взаимного различия. Блок определения условных коэффициентов взаимного различия 14, показанный на фиг.6, состоит из двух вычислителей 14.1, 14.4, двух квадраторов 14.2, 14.5, сумматора 14.3 и инвертора 14.6. Объединенные первые информационные входы вычислителей 14.1, 14.4 являются первыми информационными входами блока 14. Второй информационный вход вычислителя 14.1 объединен с информационным входом инвертора 14.6 и является вторым информационным входом блока 14. Информационный выход инвертора 14.6 является вторым информационным входом вычислителя 14.4, информационный выход вычислителя 14.1 и вычислителя 14.4 является информационным входом квадраторов 14.2 и 14.5, информационный выход которых является информационным входом сумматора 14.3, управляющий вход которого является соответствующим управляющим входом блока 14. Информационный выход сумматора 14.3 является соответствующим информационным выходом блока 14.

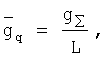

Блок усреднения и сравнения коэффициента взаимного различия при различных видах работы 8 предназначен для усреднения коэффициентов взаимно различия структуры сигнала и помехи в частотно-временной области и определения наименьшего коэффициента с учетом режимов работы, а также его адреса. Блок усреднения и сравнения коэффициента взаимного различия структуры сигнала и помехи при различных режимах работы 8, показанный на фиг.7, состоит из сумматора 8.1, вычислителя 8.2, регистра 8.3, первой и второй линии задержки 8.4 и 8.5, D-триггера 8.6, схемы сравнения 8.7, делителей на L 8.9 и на N 8.10, регистра 8.11, ключей 8.12 и 8.13, элемента ИЛИ 8.8. Информационный вход сумматора 8.1 является информационным входом блока 8 сумматора 8.1, информационный выход которого является информационным входом вычислителя 8.2, информационный выход которого является информационным входом регистра 8.3, объединенный информационный выход которого является информационным входом ключа 8,8 и "В" входом схемы сравнения 8.7. Информационный выход ключа 8.12 является информационным входом D-триггера 8.6, информационный выход которого является входом "А" схемы сравнения 8.7. Выходы "А=В" и "А<В" схемы сравнения 8.7 являются входами элемента ИЛИ 8.8, а его выход объединен и является управляющим входом ключа 8.12 и регистра 8.11. Объединенный управляющий вход сумматора 8.1 делителя на L 8.8 является управляющим входом блока 8, управляющий выход делителя на L 8.9 является объединенным управляющим входом первой и второй линии задержки 8.4 и 8.5, управляющий выход первой линии задержки 8.4 является вторым управляющим входом сумматора 8.1, управляющий выход второй линии задержки 8.5 является объединенным третьим управляющим входом сумматора 8.1 и управляющим входом регистра 8.3 и счетчика на N 8.10. N адресных выходов счетчика на N являются входами регистра 8.11, N выходов которого являются адресным выходом блока. N-й выход счетчика 8.10 является управляющим входом ключа 8.13, информационный выход которого является информационным выходом блока.

Блок определения пригодности частот 16 предназначен для сравнения квадрата текущей вероятности ошибочного приема с квадратом вероятности ошибки допустимой, которая хранится в блоке 21. Блок определения пригодности частот 16, показанный на фиг.8, состоит из схемы сравнения 16.1 и элемента ИЛИ 16.2. Информационные входы А и В схемы сравнения 16.1 являются информационными входами блока 16. Информационный выход А>В схемы сравнения 16.1 является первым информационным выходом блока 16, информационные выходы А=В и А<В схемы сравнения 16.1 являются информационными входами элемента ИЛИ 16.2, информационный выход которого является вторым информационным выходом блока 16, управляющий вход схемы сравнения 16.1 является управляющим входом блока 16.

Блок запоминания пригодных частот 17 предназначен для запоминания пригодных частот. Блок запоминания пригодных частот 17, показанный на фиг.9, состоит из регистра сдвига, преобразующего последовательный код в параллельный 17.1 и делителя на Q 17.2. Информационный вход регистра сдвига 17.1 является информационным входом блока 17, а Q информационных выходов регистра сдвига 17.1 является Q информационными выходами блока 17. Управляющий вход блока 17 является объединенным управляющим входом делителя на Q 17.2 и первым управляющим входом регистра сдвига 17.1. Управляющий выход делителя на Q 17.2 является вторым управляющим входом регистра сдвига 17.1

Блок запоминания непригодных частот 21 предназначен для запоминания непригодных частот. Блок запоминания непригодных частот 21, показанный на фиг.10, состоит из регистра сдвига, преобразующего последовательный код в параллельный 21.1, и делителя на Q 21.2. Информационный вход регистра сдвига 21.1 является информационным входом блока 21, а Q информационных выходов регистра сдвига 21.1 является Q информационными выходами блока 21. Управляющий вход блока 21 является объединенным управляющим входом делителя на Q 21.2 и первым управляющим входом регистра сдвига 21.1. Управляющий выход делителя на Q 21.2 является вторым управляющим входом регистра сдвига 21.1.

Блок запоминания коэффициентов Фурье эталонных сигналов 15 предназначен для запоминания коэффициентов Фурье эталонных сигналов при различных режимах работы. Блок запоминания коэффициентов Фурье эталонных сигналов 15, показанный на фиг.11, состоит из элемента ИЛИ 15.1, линейки регистров памяти 15.2.11-15.2.1N, распределителя импульсов 15.3, генератора тактовых импульсов 15.4. Управляющий вход генератора тактовых импульсов 15.4 является управляющим входом блока запоминания коэффициентов Фурье эталонных сигналов 15. Информационный выход генератора тактовых импульсов 15.4 является информационным входом распределителя импульсов 15.3, N информационных выходов которого являются информационными входами линейки регистров памяти 15.2.11-15.2.1N, N информационных выходов которой являются N информационными входами элемента ИЛИ 15.1, информационный выход которого является информационным выходом блока 15.

Блок прогнозируемого значения мощности сигнала 6 предназначен для хранения прогнозируемого значения мощности сигнала N направлений. Блок прогнозируемого значения мощности сигнала 6, показанный на фиг.12, состоит из элемента ИЛИ 6.1, дешифратора 6.4, линейки регистров памяти 6.2.11-6.2.1N, линейки регистров ключей 15.3.11-15.3.1N. Адресный вход дешифратора 6.4 является адресным входом блока 6. Адресные выходы дешифратора являются управляющими входами линейки ключей 6.3.11-6.3.1N, выходы которой являются управляющими входами линейки регистров памяти 6.2.11-6.2.1N, N информационных выходов которой являются N информационными входами элемента ИЛИ 6.1, информационный выход которого является информационным выходом блока 6. Считывающий вход блока 6 является объединенным считывающим входом линейки ключей 6.3.11-6.3.1N.

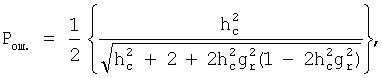

Блок определения текущей вероятности ошибочного приема 7 предназначен для вычисления текущей вероятности ошибочного приема. Блок определения текущей вероятности ошибочного приема 7, показанный на фиг.13, состоит из делителя 7.1, квадратора 7.2, вычислителя 7.3, делителя 7.4. и делителя на 4 7.5. Первый информационный вход делителя 7.1 является первым информационным входом блока 7, второй информационный вход которого является вторым информационным входом блока 7. Информационный выход делителя 7.1 является объединенным первым входом вычислителя 7.3 и информационным входом квадратора 7.2. Третий информационный вход блока 7 является вторым информационным входом вычислителя 7.3. Информационный выход квадратора 7.2 является вторым информационным входом делителя 7.4. Информационный выход вычислителя 7.3 является первым информационным входом делителя 7.4, информационный выход которого является информационным входом делителя на 4 7.5, информационный выход которого является информационным выходом блока 7 делителя на два 7.4, информационный выход которого является информационным выходом блока 7. Управляющий вход делителя на два 7.4 является управляющим входом блока 7.

Блок отбраковки частот с учетом коэффициента различия 27 предназначен для исключения из анализа тех частот, на которых не выполняется требование по обеспечению заданного качества связи, т.е. вероятность ошибочного приема больше допустимой. Блок отбраковки частот 27, показанный на фиг.14, состоит из первой линейки регистров памяти 27.1, содержащей Q регистров памяти 27.1.11-27.1.1Q, второй линейки регистров памяти 27.2, содержащей Q регистров памяти 27.2.11-27.2.1Q, и линии задержки 27.3. Вход линии задержки 27.3 соединен со считывающим входом первой линейки регистров памяти 27.1 и является управляющим входом блока 27. Выход линии задержки 27.3 подключен к считывающему входу второй линейки регистров памяти 27.2. Q выходов второй линейки регистров памяти 27.2 являются соответствующими Q выходами блока 27. Q информационных входов второй линейки регистров памяти 27.2 являются соответствующими Q информационными входами первой группы информационных входов блока 27. Q входов установки начального состояния второй линейки регистров памяти 27.2 подключены к соответствующим Q выходам первой линейки регистров памяти 27.1. Q информационных входов первой линейки регистров памяти 27.1 являются соответствующими Q информационными входами 27 группы информационных входов блока 27. Считывающие входы Q регистров памяти 27.2.11-27.2.1Q первой линейки регистров памяти 27.1 объединены и являются считывающим входом первой линейки регистров памяти 27.1. Информационные входы и выходы Q регистров памяти 27.1.11-27.1.1Q первой линейки регистров памяти 27.1 являются соответствующими Q информационными входами и Q выходами первой линейки регистров памяти 27.1. Считывающие входы Q регистров памяти 27.2.11-27.2.1Q второй линейки регистров памяти 27.2 объединены и являются считывающим входом второй линейки регистров памяти 27.2. Входы установки начального состояния Q регистров памяти 27.2.11-27.2.1Q второй линейки регистров памяти 27.2 являются соответствующими Q входами установки начального состояния второй линейки регистров памяти 27.2. Информационные входы и выходы Q регистров памяти 27.2.11-27.2.1Q второй линейки регистров памяти 27.2 являются соответствующими Q информационными входами и Q выходами второй линейки регистров памяти 27.2.

Блок выбора оптимальной частоты и режима работы 28 предназначен для определения номера оптимальной частоты, соответствующей максимальному значению суммы весов параметров помех на Q анализируемых частотах и оптимального режима работы на ней. Блок выбора оптимальной частоты и режима работы 28, показанный на фиг.15, состоит из первой линейки регистров памяти 28.1, содержащей Q регистров памяти 28.1.11-28.1.1Q, второй линейки регистров памяти 28.2, содержащей Q регистров памяти 28.2.11-28.2.1Q, третьей линейки регистров памяти 28.22, содержащей Q регистров памяти 28.22.11-28.22.1Q, первого элемента ИЛИ 28.5, второго элемента ИЛИ 28.8, третьего элемента ИЛИ 28.15, первого регистра памяти 28.5, второго регистра памяти 28.16, третьего регистра памяти 28.17, четвертого регистра памяти 28.20, пятого регистра памяти 28.21, первой линии задержки 28.6, второй линии задержки 28.12, третьей линии задержки 28.13, четвертой линии задержки 28.7, пятой линии задержки 28.18, первого ключа 28.11, второго ключа 28.14, третьего ключа 28.19, элемента сравнения 28.10, распределителя импульсов 28.3 и генератора тактовых импульсов 28.4, элемента сравнения 28.10. Вход запуска генератора тактовых импульсов 28.4 соединен с входом первой линии задержки 28.6 и является управляющим входом блока 28. Выход генератора тактовых импульсов 28.4 подключен к входу распределителя импульсов 28.3, Q выходов которого подключены к соответствующим Q считывающим входам первой линейки регистров памяти 28.1, второй линейки регистров памяти 28.2, третьей линейки регистров памяти 28.22, a ν-й выход распределителя импульсов 28.3, где ν=1, 2,..., Q, дополнительно подключен к w-му входу первого элемента ИЛИ 28.5, где w=(ν-1). Выход первого элемента ИЛИ 28.5 подключен к считывающему входу первого регистра памяти 28.9, информационный вход которого подключен к выходу второго элемента ИЛИ 28.8, первый и второй входы которого подключены соответственно к выходу первого ключа 28.11 и к первому выходу первой линейки регистров памяти 28.1, Q информационных входов которой являются соответствующими Q информационными входами блока 28. Второй выход первой линейки регистров памяти 28.1 подключен к входу второй линии задержки 28.12 и к второму входу элемента сравнения 28.10, первый вход которого подключен к выходу первого регистра памяти 28.9, а выход подключен ко вторым входам первого ключа 28.11, второго ключа 28.14 и третьего ключа 28.19. Первый вход первого ключа 28.11 подключен к выходу второй линии задержки 28.12. Первый вход второго ключа 28.14 подключен к выходу третьей линии задержки 28.13, вход которой подключен ко второму выходу второй линейки регистров памяти 28.2., первый выход которой подключен к первому входу третьего элемента ИЛИ 28.15. Второй вход которого подключен к выходу второго ключа 28.14, а выход третьего элемента ИЛИ 28.15 подключен к информационному входу второго регистра памяти 28.16, выход которого подключен к информационному входу третьего регистра памяти 28.17, считывающий вход и выход которого являются соответственно считывающим входом и выходом блока 28. Выход первой линии задержки 28.6 подключен к входу остановки генератора тактовых импульсов 28.4 и к считывающим входам второго регистра памяти 28.16 и четвертого регистра памяти 28.20. Считывающие и информационные входы Q регистров памяти 28.l.l1-28.1.1Q первой линейки регистров памяти 28.1 являются соответствующими Q считывающими и Q информационными входами первой линейки регистров памяти 28.1. Выход первого регистра памяти 28.1.1.1 первой линейки регистров памяти 28.1 является первым выходом первой линейки регистров памяти 28.1. Выходы второго, третьего,..., Q-го регистров памяти 28.1.2-28.1.1Q первой линейки регистров памяти 28.1 объединены и являются вторым выходом первой линейки регистров памяти 28.1. Считывающие входы Q регистров памяти 28.2.11-28.2.1Q второй линейки регистров памяти 28.2 являются соответствующими Q считывающими входами второй линейки регистров памяти 28.2. Выход первого регистра памяти 28.2.1.1 второй линейки регистров памяти 28.2 являются первым выходом второй линейки регистров памяти 28.2. Выходы второго, третьего,..., Q-го регистров памяти 28.2.1.2-28.2.1Q второй линейки регистров памяти 28.2 объединены и являются вторым выходом второй линейки регистров памяти 28.2. N входов четвертой линии задержки 28.7 являются адресными входами блока. N информационных входов регистра памяти 28.22.11, объединенных с информационными входами регистров памяти 28.22.12-28.22.1Q, являются информационными выходами четвертой линии задержки 28.7. N информационных выходов регистра памяти 28.22.12-28.22.1Q объединены и являются информационными выходами третьей линейки регистров памяти 28.22, информационные выходы которой являются информационными входами пятой линии задержки 28.18, информационные выходы которой являются информационными входами третьего ключа 28.19, информационные выходы которого являются информационными входами четвертого регистра памяти 28.20, информационные выходы которого являются информационными входами пятого регистра памяти 28.21, N информационных выходов которого являются вторыми информационными выходами блока 28, а считывающий пятого регистра памяти 28.21 является считывающим входом блока 28.

Схемы шифраторов 23.7-23.11 и дешифраторов 18.4, 20.4, 21.4, 19.5. 19.6, 6.4, используемых в предлагаемом устройстве автоматического выбора рабочих частот, известны и описаны, например, в книге Л.М.Гольденберга "Импульсные и цифровые устройства" (М.: Связь, 1973, с.462-468, рис.10.11, 10.12, с.446-450, рис.10.3), в книге Л.М.Гольденберга, Ю.Т.Поляка, М.X.Поляка "Цифровые устройства на интегральных схемах в технике связи" (М.: Связь, 1979, с.43-47, рис.2.14, 2.15), в книге Б.П.Даниленко, И.И.Манкевича "Отечественные и зарубежные магнитофоны: схемы и ремонт. Справочное пособие" (Минск: Беларусь, 1994, с.299-306, рис.5.16, 5.18).

Схемы ключей 6.3.11-6.3.1Q, 21.3.11-21.3.1N, 28.11, 28.14, 28.19, 8.12, 8.13 известны и описаны, например, в книге Л.М.Гольденберга "Импульсные и цифровые устройства" (М.: Связь, 1973, с.60-64, рис.2.1, 2.2). Схемы распределителя импульсов 13.2 известны и описаны, например, в книге Л.М.Гольденберга "Импульсные и цифровые устройства" (М.: Связь, 1973, с.47-63, рис.2.28-2.30).

Элементы ИЛИ 6.1, 15.1, 16.2, 21.1, 23.3, 28.15, 28.5, 28.8, 8.8 могут быть реализованы, как описано, например, в книге В.И.Шляпобергского "Основы техники передачи дискретных сообщений" (М.: Связь, 1973, с.44,48-50, рис.2.4, 2.7, 2.8).

Схемы триггеров 23.11-23.1N, 8.6 известны и описаны, например, в книге В.В.Старыгина, Л.С.Щарева "Основы вычислительной микропроцессорной техники и программирования" (М.: Высшая школа, 1989, с.83, рис.5.10), в книге Л.М.Гольденберга "Импульсные и цифровые I устройства" (М.: Связь, 1973, с.279-282, рис.4.20, 4.21), в книге Б.П.Даниленко, И.И.Манкевича "Отечественные и зарубежные магнитофоны: схемы и ремонт. Справочное пособие" (Минск: Беларусь, 1994, с.287-291, рис.5.6-5.8).

Схемы регистров памяти 6.2.11-6.2.1Q, 13.1, 15.2.11-15.2.1N, 16.1.1.11-16.1.1.1Q, 16.1.1.21-16.1.1.2Q,..., 16.1.1.21-16.1.1.2Q,..., 16.1.1.S1-16.1.1.SQ, 21.2.11-21.2.1N, 27.1.11-27.1.1Q, 27.2.11-27.2.1Q, 28.1.11-28.1.1.Q, 28.2.11-28.2.1Q, 28.9, 28.16, 28.17, 28.20, 28.21, 28.22.1Q-28.22.1Q, 8.3, 8.11 известны и описаны, например, в книге Л.М.Гольденберга, Ю.Т.Поляка, М.X.Поляка "Цифровые устройства на интегральных схемах в технике связи" (М.: Связь, 1979, с.43-47, рис.2.14, 2.15), в книге Л.М.Гольденберга "Импульсные и цифровые устройства" (М.: Связь, 1973, с.446-450, рис.10.3).

Схемы генераторов тактовых импульсов 15.4, 28.4 известны и описаны, например, в книге Л.М.Гольденберга, Ю.Т.Поляка, М.X.Поляка "Цифровые устройства на интегральных схемах в технике связи" (М.: Связь, 1979, с.72-76, рис.3.14).

Схемы распределителей импульсов 15.3, 28.3 известны и описаны, например, в книге Л.М.Гольденберга "Импульсные и цифровые устройства" (М.: Связь, 1973, с.47-63, рис.2.28-2.30).

Схемы делителя на Q 17.3, 21.3, 23.5, делителя на L 8.9, делитель на N 8.10, делитель на четыре 7.5 известны и описаны, например, в книге А.В.Рыжкова, В.Н.Попова "Синтезаторы частот в технике радиосвязи" (М.: Радио и связь, 1991, с.137-142, рис.5.3-5.6) в книге В.Ванасевича "Синтезаторы частот. Теория и проектирование" (М.: Связь, 1979, с.260-271, рис.6.24-6.29).

Схемы линий задержки 8.4. 8.5, 27.3, 28.6. 28.7, 28.12, 28.13. 28.18 известны и могут быть реализованы на D-триггерах, как описано, например, в книге Л.М.Гольденберга, Ю.Т.Поляка, М.X.Поляка "Цифровые устройства на интегральных схемах в технике связи" (М.: Связь, 1979, с.36, рис.2.3а), в книге Б.П.Даниленко, И.И.Манкевича "Отечественные и зарубежные магнитофоны: схемы и ремонт.Справочное пособие" (Минск: Беларусь, 1994, с.291-292, рис.5.9-5.11), в книге Л.М.Гольденберга "Импульсные и цифровые устройства" (М.: Связь, 1973, с.286-287, рис.4.24).

Схемы элементов сравнения 16.1, 8.7, 28.10 известны и описаны, например, в книге У.Титце, К.Шенка "Полупроводниковая схемотехника" (М.: Мир, 1982, с.329-331, рис.19.21-19.25).

Схемы сумматоров 14.3 известны и описаны, например, в книге У.Титце, К.Шенка "Полупроводниковая схемотехника" (М.: Мир, 1982, с.331-339, рис.19.26-19.37).

Схемы вычислителей 8.2, реализующих процедуру деления на L, известны и описаны, например, в книге У.Титце, К.Шенка "Полупроводниковая схемотехника" (М.: Мир, 1982, с.339-341, рис.19.38).

Схемы вычислителей 14.2. 14.5. 7.2, реализующих процедуру возведения в квадрат поступающих на их вход значений, известны и описаны, например, в книге У.Титце, К.Шенка "Полупроводниковая схемотехника" (М.: Мир, 1982, с.339-341, рис.19.38).

Схемы вычислителей 14.1, 14.4, реализующих процедуру умножения и сложения поступающих на их вход значений, известны и описаны, например, в книге У.Титце, К.Шенка "Полупроводниковая схемотехника" (М.: Мир, 1982, с.339-341, рис.19.38).

Схемы вычислителей 7.1, 7.3, 7.4 реализующих процедуры умножения, сложения, вычитания или деления поступающих на их вход значений, известны и могут быть реализованы на АЛУ КР1533ИП3.

Схема вычислителя 14.3, реализующего процедуру сложения поступающих на их вход значений, известны и описаны, например, в книге Е.П.Угрюмова "Цифровая схемотехника, 2-е издание" - СПб.: "БХВ-Петербург", 2004, рис.2.28.

Схема вычислителя 12.1, реализующего быстрое преобразование Фурье, может быть реализована на микросхемах ADSP- TS001, ADSP- 2189M или ADSP- 21160, схемы которых известны и описаны на сайте http://www.analog.com.

Схемы регистров сдвига 17.1, 21.1, реализующих процедуру преобразования последовательного кода в параллельный, известны и описаны, например, в книге "Микросхемы ТТЛ": Справочник, Том. 2-М.: ДМК, 2001. - стр.382-383.

Устройство автоматического выбора рабочих частот радиоприема работает следующим образом.

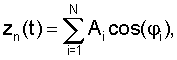

Для анализа частот в одном из N радионаправлений, обслуживаемых данным устройством, на один из n входов номеров радионаправлений блока управления 23, где n=1, 2,..., N, поступает сигнал. Например, если анализируются частоты для радионаправления №2, т.е. n=2, то сигнал поступает на второй вход номеров радионаправлений блока управления 23. При поступлении этого сигнала на первом, втором, третьем и четвертом выходах "Код радионаправления" блока управления 23 появляются сигналы, характеризующие код номера радионаправления, от которого поступил запрос на анализ и выбор рабочей частоты. Эти сигналы поступают соответственно на адресные входы блока памяти номеров антенн 18, блока памяти номеров фильтров 20, блока памяти вероятности ошибки допустимой 21, блока прогнозируемого значения мощности сигнала 6 и на вход "Код радионаправления" блока памяти номеров частот 19 для выбора необходимой для данного радионаправления антенны, фильтра, порогового (допустимого) значения вероятности ошибки на анализируемых частотах и для выбора группы частот, закрепленных за данным радионаправлением. Данные сигналы присутствуют на адресных входах указанных блоков в течение временного интервала анализа всех частот данного радионаправления. Одновременно с этим на считывающем выходе блока управления 23 появляется сигнал, который поступает на считывающие входы блока памяти номеров антенн 18, блока памяти номеров частот 19, блока памяти номеров фильтров 20, блока памяти вероятности ошибки допустимой 21 и блока прогнозируемого значения мощности сигнала 6. Данный сигнал присутствует на считывающих входах указанных блоков в течение временного интервала анализа всех частот данного радионаправления и обеспечивает разрешение считывания информации, записанной в этих блоках. Под воздействием сигналов, поступающих на адресный вход и вход "Считывание" блока памяти номеров антенн 18, на его выходе формируется сигнал, характеризующий код номера антенны, закрепленной за n-м радионаправлением, который поступает на вход первого дешифратора 9. С одного из М выходов первого дешифратора 9 преобразованный сигнал, характеризующий номер используемой антенны, поступает на соответствующий управляющий вход антенного коммутатора 1 и обеспечивает подключение необходимой антенны к входу радиоприемника 2. Сигнал, характеризующий код номера фильтра с необходимой полосой пропускания, с выхода блока памяти номеров фильтров 20 поступает на вход второго дешифратора 11. С одного из Р выходов второго дешифратора 11 преобразованный сигнал, характеризующий номер используемого фильтра, поступает на соответствующий управляющий вход блока фильтров 3 и обеспечивает подключение необходимого фильтра к выходу радиоприемника 2. Сигнал, характеризующий квадрат вероятности ошибки допустимой на анализируемых частотах данного радионаправления, с выхода блока памяти вероятности ошибки допустимой 21 поступает на первый информационный вход блока определения пригодности частот 16, где записывается в регистр памяти для его последующего сравнения с квадратами текущих значений вероятности ошибки допустимой на анализируемых частотах, поступающих с блока 7, а сигнал, характеризующий прогнозируемое значение мощности сигнала на анализируемых частотах данного радионаправления, с выхода блока прогнозируемого значения мощности сигнала 6 поступает на третий информационный вход блока определения текущей вероятности ошибочного приема 7. Под воздействием сигналов, поступающих на адресный вход "Код радионаправления" и вход "Считывание" блока памяти номеров частот 19, в блоке 19 осуществляется подготовка к выбору группы частот, закрепленных за n-м радионаправлением. На выходе "Код частоты" блока управления 23 формируется сигнал, характеризующий код первого порядкового номера анализируемой частоты. Этот сигнал поступает на адресный вход блока памяти номеров частот 19 для выбора соответствующего кода номинала первой анализируемой частоты, закрепленной за n-м радионаправлением. На выходе блока памяти номеров частот 19 появляется сигнал, характеризующий код номинала первой анализируемой частоты, который поступает на вход третьего дешифратора 10. На одном из F выходов третьего дешифратора 10 формируется сигнал, характеризующий номер заранее подготовленной частоты радиоприемника 2. Этот сигнал поступает на соответствующий управляющий вход радиоприемника 2 и обеспечивает его настройку на заданную частоту. По окончании настройки радиоприемника 2 на заданную частоту на его выходе "Конец настройки" формируется сигнал окончания настройки, который подается на управляющий вход блока анализа 4. На информационный вход блока анализа 4 и на информационный вход блока быстрого преобразования Фурье 12 с информационного выхода радиоприемника 2 через один из выбранных фильтров блока фильтров 3 поступает напряжение помехи на анализируемой частоте. В блоке анализа 4 осуществляется измерение уровня помехи на анализируемой частоте в заданной полосе частот, определяемой выбранным фильтром. В результате этого на первом и втором информационном выходе "Уровень помехи" блока анализа 4 появляется сигнал, характеризующий значение уровня помехи на анализируемой частоте. Этот сигнал с информационного выхода поступает на информационный вход блока распределения 5 и блока определения текущей вероятности ошибочного приема 7. С выхода блока быстрого преобразования Фурье 12 появляется информация о коэффициентах Фурье помехи, которая поступает на блок запоминания коэффициентов Фурье помехи 13 и по поступлении управляющего импульса упр.2 с блока управления 23 происходит запись информации в регистр памяти блока запоминания коэффициентов Фурье помехи 13, с информационного выхода которого информация поступает на второй информационный вход блока определения условных коэффициентов взаимного различия 14, одновременно с ним на третий информационный вход блока определения условных коэффициентов взаимного различия 14 поступает информация о коэффициентах Фурье эталонных сигналов с блока запоминания коэффициентов Фурье эталонных сигналов 15, где по поступлении управляющего импульса упр.5 с блока управления 23, где происходит вычисление коэффициентов взаимного различия структуры сигнала и помехи в частотно-временной области. В блоке запоминания коэффициентов Фурье эталонных сигналов 15 по поступлении управляющего импульса упр.8 с блока управления 23 происходит выдача коэффициентов Фурье эталонных сигналов в блок определения условных коэффициентов взаимного различия 14, которые записаны в регистрах памяти и соответствуют различным видам эталонных сигналов. С информационного выхода блока определения условных коэффициентов взаимного различия 14 информация о текущем коэффициенте взаимного различия поступает на первый информационный вход блока усреднения и сравнения коэффициента взаимного различия при различных видах работы 8, где происходит усреднение и сравнение коэффициентов взаимного различия структуры сигнала и помехи в частотно-временной области при N различных видах сигнала, в результате сравнения на выходе блока усреднения и сравнения коэффициента взаимного различия при различных видах работы 8 и по поступлении управляющего импульса упр.9 с блока управления 23 происходит выдача информации о наименьшем значении коэффициента взаимного различия структуры сигнала и помехи в частотно-временной области, которая поступает на второй информационный вход блока определения текущей вероятности ошибочного приема 7, а с N адресных выходов блока усреднения и сравнения коэффициента взаимного различия при различных видах работы 8 информация об адресе наименьшего значения коэффициента взаимного различия структуры сигнала и помехи в частотно-временной области поступает на адресный вход блока выбора оптимальной частоты и режима работы 28. Далее через интервал времени Δt на выходе "Код частоты" блока управления 23 появляется сигнал, под воздействием которого осуществляется перестройка радиоприемника 2 на следующую анализируемую частоту и измерение уровня помехи на этой частоте в блоке анализа 4. Измеренные текущие значения уровня помехи на новой частоте поступают на информационный вход блока распределения 5 с интервалом Δt. В дальнейшем процесс измерения уровней помех повторяется на каждой из Q анализируемых частот данного радионаправления. Таким образом, измеренные текущие значения уровней помех на каждой анализируемой частоте в дискретные моменты времени tk с временным интервалом Δt=tk+1-tk, где k=1, 2,..., с выхода "Уровень помехи" блока анализа 4 поступают на информационный вход блока распределения 5. Одновременно с поступлением сигналов, характеризующих значения уровней помех на анализируемых частотах, на управляющий вход блока распределения 5 поступают импульсы с первого управляющего выхода блока управления 23, под воздействием которых в блоке распределения 5 обеспечивается распределение поступающих на его информационный вход сигналов между Q его выходами. Значения уровней помех с Q выходов блока распределения 5 поступают на соответствующие Q информационных входов блока определения дополнительных параметров помех 24, а также на соответствующие Q информационных входов первой группы информационных входов блока определения весов анализируемых частот 25, где записываются в соответствующие регистры памяти этих блоков. По окончании очередного l-го цикла обхода всех Q анализируемых частот, где l=1, 2,..., L, a L=2, 3, 4,... (конкретное значение L выбирается исходя из требований к точности определения дополнительных параметров помех), и записи значений уровней помех на этих частотах в регистры памяти блока определения дополнительных параметров помех 24 с двенадцатого управляющего выхода блока управления 23 поступает импульс на управляющий вход блока определения дополнительных параметров помех 24, под воздействием которого в блоке определения дополнительных параметров помех 24 производится подготовка к определению дополнительных параметров помех на Q анализируемых частотах. Процесс подготовки определения дополнительных параметров помех в блоке определения дополнительных параметров помех 24 осуществляется L раз. По окончании L-го цикла обхода всех Q анализируемых частот в блоке определения дополнительных параметров помех 24 осуществляется определение значений дополнительных параметров помех на Q анализируемых частотах. Такими параметрами, в частности, являются средние значения, дисперсия уровней помех, интервал корреляции процесса изменения уровней помех во времени и др. Значения дополнительных параметров помех, сформированные в блоке определения дополнительных параметров помех 24, с Q выходов (S-1) групп выходов данного блока, где S - общее количество анализируемых параметров помех, поступают на соответствующие Q входов второй, третьей,..., S-й групп информационных входов блока определения весов анализируемых частот 25 и записываются в регистрах памяти этого блока. Количество групп выходов блока определения дополнительных параметров помех 24 соответствует количеству анализируемых дополнительных параметров уровней помех на Q анализируемых частотах. Количество групп информационных входов блока определения весов анализируемых частот 25 соответствует общему количеству анализируемых параметров уровней. По окончании записи значений дополнительных параметров помех в регистры памяти блока определения весов анализируемых частот 25 с двенадцатого управляющего выхода блока управления 23 поступает импульс на управляющий вход блока определения весов анализируемых частот 25, под воздействием которого в данном блоке производится определение весов основного параметра (текущих значений уровней помех) и дополнительных параметров уровней помех на каждой из Q анализируемых частот. Эти величины весов с Q выходов первой, второй,..., S-й групп выходов блока определения весов анализируемых частот 25 поступают на соответствующие Q входов первой, второй,..., S-той групп информационных входов блока определения показателей качества частот 26 и записываются в регистрах памяти этого блока. По окончании записи значений весов S параметров помех на Q анализируемых частотах в регистры памяти блока определения показателей качества частот 26 с четырнадцатого управляющего выхода блока управления 23 поступает импульс на управляющий вход блока определения показателей качества частот 26. Под воздействием этого импульса в блоке определения показателей качества частот 26 производится определение показателей качества Q анализируемых частот путем суммирования значений весов S анализируемых параметров для каждой из Q анализируемых частот. Полученные значения сумм весов с Q выходов блока определения показателей качества частот 26 поступают на соответствующие Q информационные входы первой группы информационных входов блока отбраковки частот с учетом коэффициента различия 27 и записываются в соответствующие регистры памяти этого блока. По окончании L-го цикла обхода всех Q анализируемых частот и записи информации о значениях сумм весов на Q анализируемых частотах, поступающей с блока определения показателей качества частот 26, и информации о пригодности анализируемых частот, поступающей с блока запоминания пригодных частот с учетом текущих значений вероятности ошибочного приема в регистры памяти блока отбраковки частот с учетом коэффициента различия 27 с четырнадцатого управляющего выхода блока управления 23 поступает импульс на управляющий вход блока отбраковки частот с учетом коэффициента различия 27, под воздействием которого в блоке отбраковки частот с учетом коэффициента различия 27 осуществляется отбраковка непригодных частот с учетом суммы весов анализируемых частот и режимом работы на этой частоте. При этом с q-го выхода блока отбраковки частот с учетом коэффициента различия 27 на q-й информационный вход группы информационных входов блока выбора оптимальной частоты и режима работы 28 поступают пригодные частоты по сумме весов. Таким образом, в результате определения пригодности частот в блоке выбора оптимальной частоты и режима работы 28 имеется информация о пригодных частотах и оптимальных режимах работы на них. Эта информация постоянно обновляется по окончании L-го цикла измерения уровней помех на Q анализируемых частотах. Скорректированные значения сумм весов для каждой из Q анализируемых частот с Q выходов блока отбраковки частот с учетом коэффициента различия 27 поступают на соответствующие Q информационных входов блока выбора оптимальной частоты и режима работы 28, где записываются в регистрах памяти. По окончании записи скорректированных значений сумм весов параметров помех в блок выбора оптимальной частоты и режима работы 28 с пятнадцатого управляющего выхода блока управления 23 поступает импульс на управляющий вход блока выбора оптимальной частоты и режима работы 28, под воздействием которого в этом блоке определяется номер оптимальной частоты, соответствующей максимальному значению суммы весов измеренных параметров частот и оптимальный режим работы на этой частоте. По окончании очередного L-го цикла обхода всех Q частот через интервал времени, равный (Q×L×Δt), информация о номере оптимальной частоты обновляется.

Таким образом, в процессе анализа выделенных для связи Q частот в блоке выбора оптимальной частоты и режима работы 28 имеется информация о номере оптимальной частоты, на которой обеспечивается максимальная вероятность радиосвязи с заданным качеством, а также имеется возможность использования непригодных частот с учетом коэффициента взаимного различия структуры сигнала и помехи в частотно-временной области путем изменения режима работы на этой частоте. По сигналу, поступающему от блока управления радиолинией на считывающий вход блока выбора оптимальной частоты и режима работы 28, производится считывание информации о номере оптимальной частоты и оптимальном режиме работы на ней, хранящейся в блоке выбора оптимальной частоты и режима работы 28.

Работа всего устройства координируется блоком управления 23.

Для остановки работы устройства автоматического выбора рабочих частот на вход остановки работы блока управления 23 поступает сигнал, под воздействием которого производится остановка работы устройства.

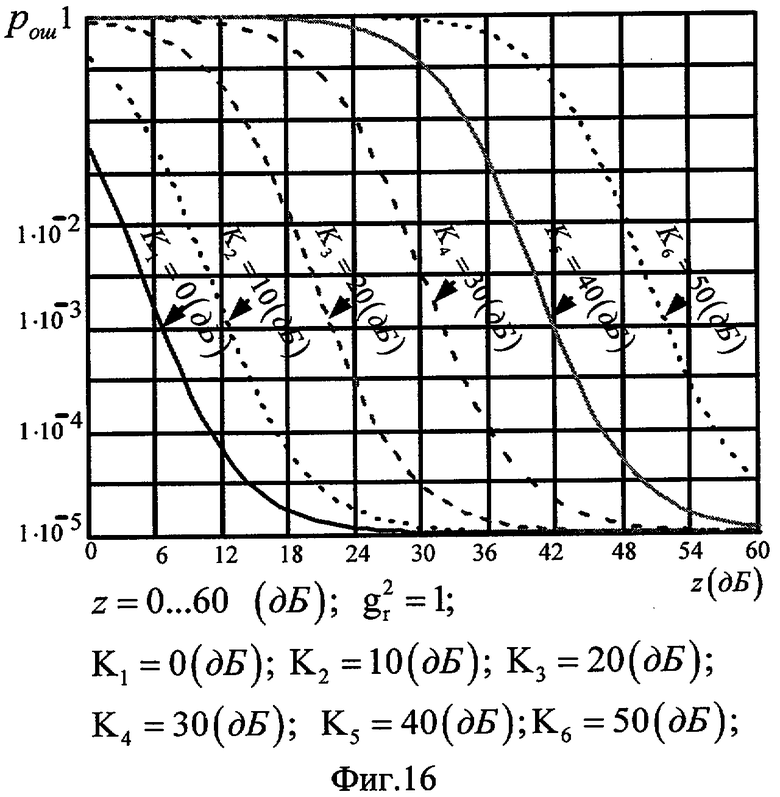

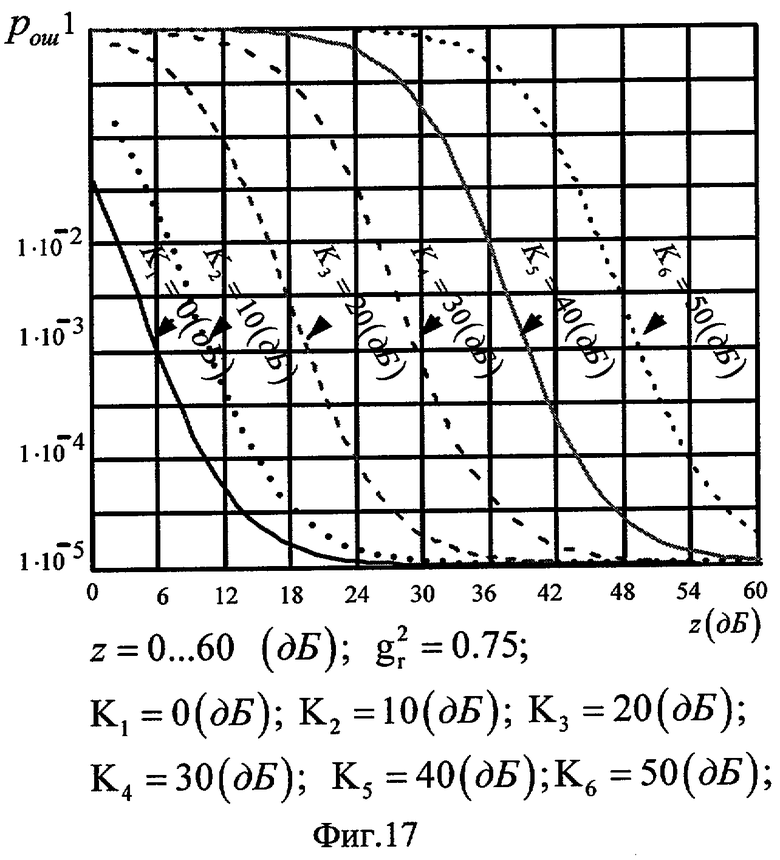

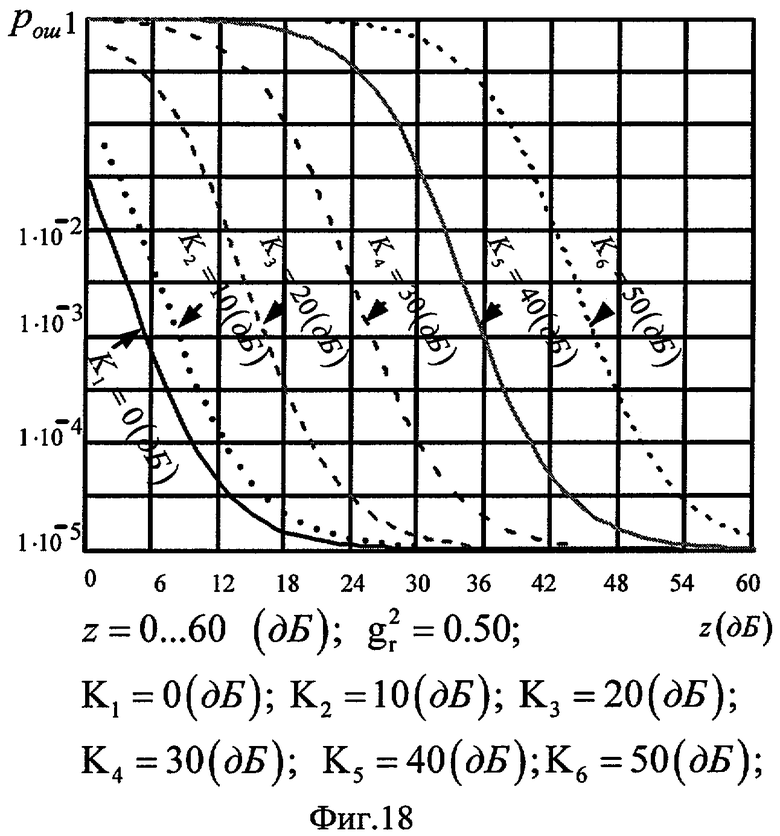

Блок управления 23 работает следующим образом. Сигнал на анализ и выбор рабочей частоты для одного из N радионаправлений, обслуживаемых устройством автоматического выбора рабочих частот, поступает на n-й вход номеров радионаправлений блока управления 23, где n=1, 2,..., N. Этот сигнал подается на первый вход n-го триггера 23.1n и переводит этот триггер в состояние "1". Сигнал, соответствующий состоянию "1", с выхода триггера 23.1n поступает на n-й вход первого шифратора 23.7, второго шифратора 23.8, третьего шифратора 23.9 и четвертого шифратора 23.10, на выходах которых формируются коды номера радионаправления, от которого поступил запрос на анализ и выбор рабочей частоты. Код номера радионаправления с выходов первого шифратора 23.7, второго шифратора 23.8, третьего шифратора 23.9 и четвертого шифратора 23.10 поступает соответственно на первый, второй, третий и четвертый выходы "Код радионаправления" блока управления 23. Одновременно с этим сигнал с выхода триггера 23.1n через элемент ИЛИ 23.3 поступает на выход "Считывание" блока управления 23 и на вход запуска генератора тактовых импульсов 23.2, запуская его. Генератор тактовых импульсов 23.2 формирует импульсы с интервалом времени Δt, определяемым временем между соседними измерениями уровней помех на анализируемых частотах. Данные импульсы поступают на входы делителя на Q 23.5, делителя на (Q×L) 23.6, через первую, вторую, третью, четвертую, пятую, шестую, седьмую, восьмую, девятую, десятую, одиннадцатую линию задержки 23.12-23.22 на первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый управляющий выход блока управления 23, а также на вход распределителя импульсов 23.4, построенного по принципу распределения импульсов кольцевого типа. Распределитель импульсов 23.4 обеспечивает поочередное распределение поступающих на его вход импульсов между Q его выходами. При этом при поступлении на вход распределителя импульсов 23.4 (Q+1)-го импульса от генератора тактовых импульсов 23.2 импульс появляется на первом выходе распределителя импульсов 23.4. В дальнейшем процесс распределения импульсов повторяется. Импульс с q-го выхода распределителя импульсов 23.4, где q=1, 2,..., Q, поступает на q-й вход пятого шифратора 23.11, на выходе которого формируется код порядкового номера анализируемой частоты, который поступает на выход "Код частоты" блока управления 23. Делитель на Q 23.5 и делитель на (Q×L) 23.6 обеспечивают появление поступающей на их вход последовательности импульсов соответственно Q и на (Q×L). Далее с выхода на делителя на Q 23.5 импульсная последовательность через двенадцатую линию задержки 23.23 поступает на двенадцатый управляющий выход блока управления 23, а с выхода на делителя на (Q×L) 23.6 - через тринадцатую, четырнадцатую, пятнадцатую, шестнадцатую линии задержки 23.24-23.27 соответственно на тринадцатый, четырнадцатый, пятнадцатый, шестнадцатый управляющие выходы блока управления 23. Длительности первой, второй, третьей, четвертой, пятой, шестой, седьмой, восьмой, девятой, десятой, одиннадцатой, двенадцатой, тринадцатой, четырнадцатой, пятнадцатой, шестнадцатой линий задержки 23.12-23.27 выбраны таким образом, чтобы импульсы управления подавались на управляющие входы соответствующих блоков устройства автоматического выбора рабочих частот одновременно с поступлением сигналов на информационные входы данных блоков (см. фиг.21). Для остановки работы блока управления 23 на его вход остановки работы поступает сигнал, который подается на вторые входы всех триггеров 23.1,-23.1N, переводя их в нулевое состояние, а также на вход остановки генератора тактовых импульсов 23.2, обеспечивая его остановку.