Изобретение относится к радиотехнике и может использоваться в радиолокационных станциях (далее РЛС) обнаружения и сопровождения целей, в которых производится когерентная обработка сигналов.

Известен способ селекции движущихся целей (СДЦ) (патент РФ №2035051), где сущность заключается в том, что в способе обработки сигналов для селекции движущихся целей для каждого элемента дальности М последовательных отсчетов эхо-сигналов умножают на М отсчетов, соответствующих весовому коэффициенту (К), опорных функций и сигналы, полученные в результате умножения, независимо суммируют, каждый из К суммарных сигналов умножают на отсчет соответствующей опорной функции, суммируют их между собой и результат суммирования вычитают из отчета эхо-сигнала.

Недостатком известного способа является сложность синхронизации при работе в реальном времени, т.е. необходимо управлять адресом, применять порядок следования эхо-сигналов. Сложные преобразования, применение большого количества базисных функций усложняют реализацию способа. Кроме того, известный способ не исключает наличия «слепых скоростей».

Наиболее близким аналогом (прототипом) предлагаемого технического решения является способ, основанный на использовании эффекта Доплера (Вишин Г.М. Селекция движущихся целей. М.: Военное издательство Министерства обороны СССР, 1966, стр.21-23.)

Недостатком известного способа является невозможность определения сигнала в зонах «слепых» скоростей.

Известно устройство для обнаружения сигналов (а.с. СССР №535739), содержащее элемент задержки и первый ранговый обнаружитель. Однако в данном устройстве слабые сигналы подавляются сильным сигналом при его появлении в диапазоне элементов разрешения за слабым сигналом.

Известно устройство обнаружения радиолокационных сигналов (а.с. СССР №762560), содержащее линию задержки, блоки вычисления максимального значения, многоканальный регистр сдвига, аналого-цифровой преобразователь, логический блок, синхронизатор, многоканальные регистры сдвига, сумматор и решающий блок. Недостатком устройства является сложность конструкции и ненадежность.

Наиболее близким аналогом (прототипом) предлагаемого технического решения является устройство для подавления пассивных помех (а.с. СССР №743208), содержащее два канала, каждый из которых состоит из трех основных перемножителей, сумматора и последовательно соединенных фазового детектора, аналого-цифрового преобразователя, первого и второго блоков памяти, причем первые входы фазовых детекторов каналов объединены, а выходы первого блока памяти и аналого-цифрового преобразователя подключены соответственно ко входу первого основного перемножителя и первому входу сумматора, второй и третий входы которого соединены соответственно с выходами второго и третьего основных перемножителей, при этом на вторые входы фазовых детекторов поданы опорные сигналы, вычислительный блок и последовательно соединенные блок измерения и усреднения межпериодного сдвига фазы помехи и функциональный преобразователь, а в каждый канал введены два дополнительных перемножителя, причем первый вход первого дополнительного перемножителя одного канала соединен с выходом второго блока памяти другого канала, первый вход и выход второго дополнительного перемножителя соединены соответственно с выходом второго блока памяти и одним из дополнительных входов сумматора, другой дополнительный вход которого соединен с выходом первого дополнительного перемножителя, а вторые входы дополнительных перемножителей соединены с выходами вычислительного блока, ко входу которого подключен выход блока измерения и усреднения междупериодного сдвига фазы помехи, входы которого соединены соответственно с выходами аналого-цифровых преобразователей и первых блоков памяти, при этом выход первого основного перемножителя одного канала подключен к первому входу третьего основного перемножителя этого же канала и первому входу второго основного перемножителя другого канала, а вторые входы вторых и третьих основных перемножителей соединены с выходами функционального преобразователя, при этом блок измерения и усреднения междупериодного сдвига фазы помехи содержит последовательно соединенные деталь, функциональный преобразователь и логический блок, соответствующие входы которого соединены со входами двигателя, а также два канала, каждый из которых состоит из первого накопителя, первого перемножителя и последовательно соединенных второго накопителя, второго перемножителя и усредняющего сумматора, выход которого подключен к соответствующему входу делителя, при этом второй вход усредняющего сумматора одного канала соединен с выходом первого перемножителя другого канала, входы которого соединены с выходами первого и второго накопителей, причем входы накопителей являются входами блока измерения и усреднения междупериодного сдвига фазы помехи, выходом которого является выход логического блока, при этом вычислительный блок содержит последовательно соединенные блок памяти, сумматор и функциональный преобразователь, выходы которого являются выходами вычислительного блока, входом которого является вход блока памяти, соединенный с вторым входом сумматора.

Однако известное цифровое устройство не обеспечивает достаточной эффективности подавления пассивных помех.

Задачей, на решение которой направлено предполагаемое изобретение, является улучшение эффективности СДЦ в зоне «слепых» скоростей при вобуляции периода повторения за счет отличия сигнала от цели и пассивной помехи по знакам суммы и разности эхо-сигналов в зоне «слепых» скоростей, что обеспечивает упрощение способа обработки сигналов для СДЦ.

Техническими результатами, достигаемыми при реализации заявленного изобретения являются, в частности, избежание выноса на экран информации о пассивных помехах и улучшение наблюдаемости полезных сигналов, в том числе и на фоне пассивной помехи, а также сокращение конструктивных элементов, которое позволяет повысить надежность устройства и его экономичность. Кроме того, техническим результатом является упрощение вычисления в новой структурной электрической схеме устройства обработки сигнала, увеличение вероятности обнаружения цели на фоне пассивной помехи, появление возможности освободиться от неоднозначных сигналов.

Влияние на достижение указанных технических результатов оказывают нижеперечисленные существенные признаки. Способ обработки сигнала, состоящий в обнаружении цели при двукратной селекции движущихся целей с вобуляцией периода повторения, заключается в изменении частоты и фазы сигнала, отраженного от цели, относительно частоты и фазы сигнала пассивной помехи, учитывающий ширину спектра пассивной помехи и расширение спектра за счет вращения антенны и движения платформы. При вобуляции периода повторения учитывают направление векторов разности фаз сигнала, отраженного от цели, и сигнала, отраженного от пассивной помехи, причем направление вектора разности фаз сигнала, отраженного от цели, полученного в зоне «слепых» скоростей, противоположно направлению вектора разности фаз сигнала, отраженного от пассивной помехи.

Устройство для обработки сигнала, содержащее два канала, каждый из которых состоит из последовательно соединенных фазового детектора, аналого-цифрового преобразователя, первого и второго блоков памяти, причем первые входы фазовых детекторов каналов объединены, а на вторые входы фазовых детекторов поданы опорные сигналы, отличающееся тем, что в него введены первый и второй блоки вычитания в оба канала соответственно, первый и второй сумматоры в каждый канал соответственно, первый, второй и третий блок вычислителя модуля, пятый и шестой блок вычитания, интегратор, пятый и шестой сумматоры, дешифратор, первый, второй и третий умножители, первая, вторая, третья и четвертая схема сравнения, логический элемент «2И-НЕ», логический элемент «И», причем в каждом канале аналого-цифровой преобразователь соединен с первыми входами первого сумматора и с первыми входами первого блока вычитания соответственно, в каждом канале выходы первого блока памяти - цифровой линии задержки соединены со вторыми входами первого блока вычитания и первого сумматора, с первыми входами второго блока вычитания и второго сумматора соответственно, выходы второго блока памяти - цифровой линии задержки соединены со вторыми входами второго блока вычитания и второго сумматора соответственно, выходы первых блоков вычитания первого и второго каналов соединены с первым и вторым входами первого блока вычислителя модуля соответственно, выходы вторых блоков вычитания первого и второго каналов соединены с первым и вторым входами второго блока вычислителя модуля соответственно, выходы знакового разряда первого и второго блоков вычитания первого и второго каналов и первого и второго сумматоров, первого и второго каналов соединены со входом дешифратора, выходы вторых блоков памяти - цифровых линий задержки первого и второго каналов соединены с первым и вторым входами третьего блока вычислителя модуля соответственно, выход третьего блока вычислителя модуля соединен с первыми входами первого и третьего умножителей, выход интегратора соединен со вторым входом первого умножителя, а на второй вход третьего умножителя вводится постоянный коэффициент q, выход первого умножителя соединен со вторым входом шестого блока вычитания, выход шестого блока вычитания соединен со вторым входом второй схемы сравнения и со входом интегратора, выход второго блока вычислителя модуля соединен с первыми входами третьей и четвертой схем сравнения, с первым входом шестого блока вычитания и с первым входом пятого сумматора, выход первого блока вычислителя модуля соединен со вторым входом пятого сумматора и с первым входом второго умножителя, на второй вход которого введен постоянный коэффициент l, а выход соединен с входом пятого блока вычитания и первым входом шестого сумматора, выход третьего умножителя соединен со вторыми входами пятого блока вычитания и шестого сумматора, а также с первым входом второй схемы сравнения, а выходы пятого блока вычитания и шестого сумматора подключены ко вторым входам третьей и четвертой схем сравнения соответственно, выход пятого сумматора соединен с первым входом первой схемы сравнения, на второй вход которой подан с выхода третьего умножителя сигнал, умноженный на два за счет смещения разрядной сетки, а выход подключен к первому входу логического элемента «2И-НЕ», выход дешифратора соединен со вторым входом логического элемента «2И-НЕ», выходы второй, третьей, четвертой схем сравнения соединены со вторым, третьим и четвертым входами логического элемента «И» и выход логического элемента «2И-НЕ» соединен с первым входом логического элемента «И», выход логического элемента «И» является выходом устройства Y.

Возможность увеличивать вероятность обнаружения цели на фоне пассивной помехи в процессе обнаружения за счет перехода на другую частоту повторения импульсов с другой вобуляцией периода повторения применительно к скорости цели, а также возможность находить оптимальную наблюдаемость на экране индикатора за счет адаптации к ширине спектра помехи, сужая или расширяя зону режекции применительно к помеховой обстановке с учетом сокращения конструктивных элементов, позволяет повысить надежность устройства и его экономичность.

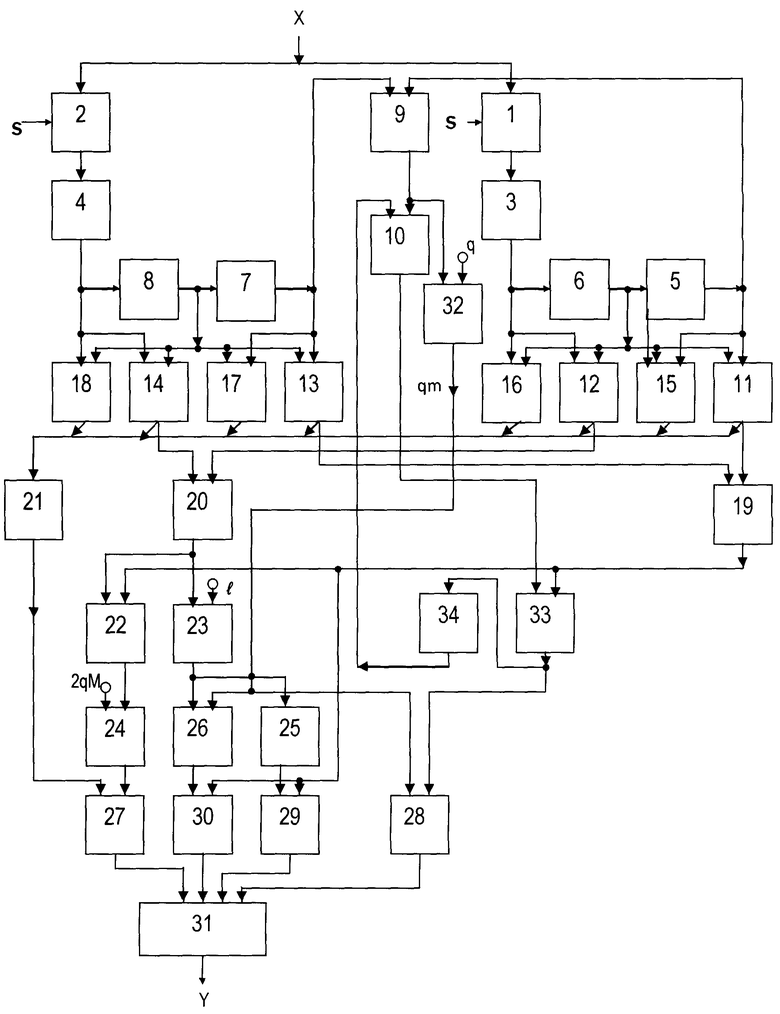

На чертеже представлено устройство, реализующее предлагаемый способ.

Способ обработки сигнала состоит в обнаружении цели при двукратной СДЦ с вобуляцией периода повторения. Сущность предлагаемого способа заключается в изменении частоты и фазы сигнала, отраженного от цели, относительно частоты и фазы сигнала от пассивной помехи, учитывающий ширину спектра пассивной помехи и расширение спектра за счет вращения антенны и движения платформы. При вобуляции периода повторения учитывают направление векторов разности фаз сигнала, отраженного от цели, и фаз сигнала, отраженного от пассивной помехи, причем направление вектора разности фаз сигнала, отраженного от цели, полученного в зоне «слепых» скоростей, противоположно направлению вектора разности фаз сигнала, отраженного от пассивной помехи. При таком положении векторов эхо-сигналов от скоростной цели имеется отличие от расположения векторов эхо-сигналов от пассивной помехи, т.е. имеется отличие по совокупности знаков суммы и разности векторов.

Устройство содержит: входы когерентного гетеродина S, фазовые детекторы 1, 2, аналогово-цифровые преобразователи 3, 4, блоки памяти - цифровые линии задержки на период Т1 - 5, 7 и блоки памяти - цифровые линии задержки на период Т2 - 6, 8, вычислители модуля 9, 19, 20, умножители 10, 23, 32, блоки вычитания 11, 12, 13, 14, 25, 33, сумматоры 15, 16, 17, 18, 22, 26, дешифратор 21, схемы сравнения 24, 28, 29, 30, логический элемент «2И-НЕ» 27, логический элемент «И» 31 с выходом Y, интегратор 34.

Устройство для реализации способа обработки сигнала, содержит два канала. Каждый канал состоит из последовательно соединенных фазового детектора 1, 2, аналого-цифрового преобразователя 3, 4, первого и второго блоков памяти - цифровых линий задержки 5, 6, 7, 8, причем первые входы фазовых детекторов 1, 2 каналов объединены, а на вторые входы фазовых детекторов 1, 2 поданы опорные сигналы. В устройство для реализации способа обработки сигнала введены первые 12, 14 и вторые 11, 13 блоки вычитания в оба канала соответственно, первые 16, 18 и вторые 15, 17 сумматоры в каждый канал соответственно, первый, второй и третий блок вычислителя модуля 9, 19, 20, пятый и шестой блок вычитания 25, 33, интегратор 34, пятый и шестой сумматоры 22, 26, дешифратор 21, первый, второй и третий умножители 10, 23, 32, первая, вторая, третья и четвертая схема сравнения 24, 28, 29, 30, логический элемент «2И-НЕ» 27, логический элемент «И» 31. Причем в каждом канале аналого-цифровой преобразователь 3,4 соединен с первыми входами первого сумматора 16, 18 и с первыми входами первого блока вычитания 12, 14 соответственно. В каждом канале вторыми входами первого блока вычитания 12, 14 и первого сумматора 16, 18, с первыми входами второго блока вычитания 11, 13 и второго сумматора 15, 17 соответственно. Выходы второго блока памяти - цифровой линии задержки 5,7 соединены со вторыми входами второго блока вычитания 11, 13 и второго сумматора 15, 17 соответственно, выходы первых блоков вычитания 12, 14 первого и второго каналов соединены с первым и вторым входами первого блока вычислителя модуля 20 соответственно, выходы вторых блоков вычитания 11, 13 первого и второго каналов соединены с первым и вторым входами второго блока вычислителя модуля 19 соответственно, выходы знакового разряда первых 12, 14 и вторых 11, 13 блоков вычитания первого и второго каналов и первых 16, 18 и вторых 15, 17 сумматоров первого и второго каналов соединены со входом дешифратора 21, выходы вторых блоков памяти - цифровых линий задержки 5, 7 первого и второго каналов соединены с первым и вторым входами третьего блока вычислителя модуля 9 соответственно, выход третьего блока вычислителя модуля 9 соединен с первыми входами первого и третьего умножителей 10, 32, выход интегратора 34 соединен со вторым входом первого умножителя 10, а на второй вход третьего умножителя 32 вводится постоянный коэффициент q, выход первого умножителя 10 соединен со вторым входом шестого блока вычитания 33, выход шестого блока вычитания 33 соединен со вторым входом второй схемы сравнения 28 и со входом интегратора 34, выход второго блока вычислителя модуля 19 соединен с первыми входами третьей и четвертой схем сравнения 29, 30 с первым входом шестого блока вычитания 33 и с первым входом пятого сумматора 22. Выход первого блока вычислителя модуля 20 соединен со вторым входом пятого сумматора 22 и с первым входом второго умножителя 23, на второй вход которого введен постоянный коэффициент l, а выход соединен с входом пятого блока вычитания 25 и первым входом шестого сумматора 26, выход третьего умножителя 32 соединен со вторыми входами пятого блока вычитания 25 и шестого сумматора 26, а также с первым входом второй схемы сравнения 28, а выходы пятого блока вычитания 25 и шестого сумматора 26 подключены ко вторым входам третьей и четвертой схем сравнения 29, 30 соответственно, выход пятого сумматора 22 соединен с первым входом первой схем сравнения 24, на второй вход которой подан с выхода третьего умножителя 32 сигнал, умноженный на два за счет смещения разрядной сетки (связь на чертеже не показана), а выход подключен к первому входу логического элемента «2И-НЕ» 27. Выход дешифратора 21 соединен со вторым входом логического элемента «2И-НЕ» 27, выходы второй, третьей и четвертой схем сравнения 28, 29, 30 соединены со вторым, третьим и четвертым входами логического элемента «И» 31 и выход логического элемента «2И-НЕ» 27 соединен с первым входом логического элемента «И» 31, выход логического элемента «И» 31 является выходом устройства Y.

Устройство, реализующее способ, работает следующим образом. На первые входы фазовых детекторов 1, 2 поступает информационный эхо-сигнал на частоте когерентного гетеродина, на вторые входы S фазовых детекторов 1, 2 подается опорное напряжение когерентного гетеродина со сдвигом на 90°. При этом информационный эхо-сигнал разбивается на квадратуры. С выходов фазовых детекторов 1, 2 видеосигналы поступают на аналого-цифровые преобразователи 3, 4, где дескретизируются по времени и преобразуются в цифровую форму. Затем цифровые сигналы поступают на первые блоки памяти - цифровые линии задержки (запоминающие устройства) 6, 8. Сначала записывается первый сигнал и задерживается на период Т1. В момент записи второго сигнала происходит считывание первого сигнала, который затем поступает во вторые блоки памяти - цифровые линии задержки (запоминающее устройство) 5, 7 и задерживается на период Т2.

Адреса блоков памяти - цифровых линий задержек вырабатываются от тактовой частоты в самих блоках памяти - цифровых линиях задержки и обеспечивают последовательную запись сигналов всех элементов дальности каждого периода повторения. В момент прихода третьего сигнала считывается первый сигнал, задержанный на (Т1+Т2), и второй сигнал, задержанный на T1. Все три сигнала одновременно поступают в суммарно-разностную схему обработки. Тройки квадратурных составляющих сигналов с амплитудами U1, U2, U3 поступают на блоки вычитания 11, 12, 13, 14 и сумматоры 15, 16, 17, 18, где вычисляются разности и суммы проекций векторов: (a1-a2) 11, (а2-а3) 12, (a1+a2) 15, (а2+а3) 16, (b1-b2) 13, (b2-b3) 14, (b1+b2) 17, (b2+b3) 18.

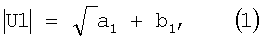

Составляющие первого импульса с двух квадратур, задержанные на время T1+T2, поступают на вычислитель модуля 9, где вычисляется амплитуда первого импульса по формуле:

где a1, b1 - проекции вектора U1, соответствующие квадратурам. Амплитуды импульсов U1, U2, U3 равны, поэтому для нормирования выбран модуль амплитуды первого импульса U1, который проходит приемный тракт в то время, когда нет неоднозначных сигналов. Обозначим |U1|=М.

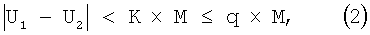

При этом признаком пассивной помехи является выражение

причем К поступает с интегратора 34. Модуль М умножается на коэффициент К в умножителе 10. Интегратор 34 за определенное время накапливает К, определяемый минимальным значением остатка выходного напряжения на блоке вычитания 33. Время адаптации к пассивной помехе не превышает максимального времени, определяемого динамическим диапазоном устройства и устанавливается с учетом длительности зондирующего сигнала. Обычно пассивные помехи, например берег или облака, имеют большую отражающую поверхность, чем цель. И за время облучения пассивной помехи интегратор набирает определенный весовой коэффициент, который практически не изменяется за малое время воздействия сигнала от движущейся цели, т.е. происходит селекция помехи и цели.

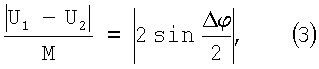

В зависимости от ширины спектра пассивной помехи соответственно модулю разности сигналов |U1-U2| весовой коэффициент автоматически перестраивается под необходимую зону режекции, определяемую из отношения

где Δφ - разность фаз между  и

и  для данной ширины спектра пассивной помехи с учетом вращения антенны.

для данной ширины спектра пассивной помехи с учетом вращения антенны.

Если РЛС установлена на корабле и корабль движется, то происходит расширение спектра сигнала, отраженного от пассивной помехи, за счет движения корабля. При адаптивной подстройке весового коэффициента к спектру пассивной помехи учитывается также и скорость движения корабля, т.е. независимо от того, движется ли помеха относительно корабля или корабль относительно помехи.

Для дисперсии доплеровского спектра δcmax=100 Гц и периода повторения Тп=1,4 мс сдвиг фазы составляет Δφ=50°. Для δmin=20 Гц, соответственно Δφ=10°. Исходя из этого К может плавно изменяться от Кmax=1 (при Δφ=60°) до Кmin = 3×2-4 (при Δφ=10°).

Выражение пассивной помехи (2) анализируется на обычной схеме сравнения 28, после чего сигнал о наличии пассивной помехи поступает на логический элемент «И» 31.

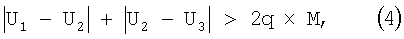

Модуль разности двух сигналов |U1-U2| вычисляется на вычислителе модуля 19, на выходы которого поступают с блоков вычитания 11, 13 двух квадратур значения (а1-а2), (b1-b2). Модуль разности |U2-U3| вычисляется на вычислителе модуля 20, на выходы которого поступают с блоков вычитания 12, 14 двух квадратур значения (а2-а3), (b2-b3). На сумматоре 22 производится суммирование модулей разности: (|U1-U2|)+(|U2-U3|). На умножителе 32 происходит умножение q×M. На схеме сравнения 24 происходит сравнение:

где коэффициент q определяет модуль максимальной разности фаз за счет шумового отклонения векторов при заданном соотношении «сигнал / шум». Например, при соотношении «сигнал/шум»: Uc/Uш=25,

при |Uc|=1 значение q=|Uш|=2-5.

Если модули разности фаз сигналов (U1-U2), (U2-U3) не превышают заданного шумового разброса векторов, указанные разности фаз могут принимать любой знак. При этом со схем сравнения 24 через логический элемент «2И-НЕ» 27 выдается сигнал отсутствия цели на логический элемент «И» 31, к которому через логический элемент «2И-НЕ» 27 подключается и знаковый дешифратор 21. Знаковый дешифратор 21, который анализирует направление и очередность векторов U1, U2, U3 за счет знаков суммы и разности проекций, поступающих на дешифратор 21 с сумматоров 15, 16, 17 и 18 и блоков вычитания 11, 12, 13 и 14. Дешифратор 21 построен на постоянном запоминающем устройстве (ПЗУ), состоящем из микросхем 556РТ5, прошитых согласно данным таблице.

Согласно данной таблице учитывается положение векторов в зонах «слепых» скоростей амплитудно-частотной характеристики (АЧХ) двукратной СДЦ. При несовпадении вырабатывается признак пассивной помехи.

В умножителе 23 модуль разности амплитуд |U2-U3| умножается на коэффициент l, равный l=T1/Т2 и учитывающий вобуляцию периода повторения зондирующих импульсов. Коэффициент l можно менять при изменении вобуляции периода повторения зондирующих импульсов или автоматически менять согласно программе работы станции. В сумматоре 26 вычисляется сумма: l×|U2-U3|+q×M, а в блоке вычитания 25 - разность: l×|U2-U3|-q×M.

Затем в схемах сравнения 30 и 29 происходит сравнение:

При этом учитывается отклонение векторов за счет шумового отклонения векторов в области нуля скоростной характеристики и выдается признак пассивной помехи на логический элемент «И» 31. При совпадении всех перечисленных выше четырех признаков пассивной помехи на входах логического элемента «И» 31 на его выходе формируется сигнал, поступающий на выход Y и указывающий на наличие пассивной помехи, в которой отсутствует цель. Таким образом, можно избежать выноса на экран информации о пассивных помехах и улучшить наблюдаемость полезных сигналов, в том числе и на фоне пассивной помехи.

Возможность изменения параметра l при изменении вобуляции периода повторения в процессе работы станции позволяет увеличить вероятность обнаружения цели на фоне пассивной помехи.

Возможность адаптироваться под ширину спектра пассивной помехи, т.е. накапливать коэффициент К в процессе работы станции, позволяет находить оптимальную наблюдаемость на экране индикатора с учетом реальной ширины спектра пассивной помехи и с учетом различных метеорологических условий. В связи с тем, что в вычислениях участвует модуль первого импульса |U1|, появляется возможность освободиться от неоднозначных сигналов.

В зоне первой «слепой» скорости векторы U1, U2, U3 занимают такое положение, при котором модули разности фаз |U1-U2|, |U2-U3| минимальны, и обнаружитель может принять скоростную цель за пассивную помеху. Но при таком положении векторов эхо-сигналов от скоростной цели имеется отличие от расположения векторов эхо-сигналов от пассивной помехи, т.е. имеется отличие по совокупности знаков суммы и разности векторов.

Блоки вычитания 11, 12, 13, 14, 25 и 33 построены согласно стр.326-328 М.А.Карцев, В.А.Брин. Вычислительные системы и синхронная арифметика, М.: Радио и связь, 1981. Сумматоры 15, 16, 17, 18, 22, и 26 построены по схеме согласно а.с. СССР №1469503. Интегратор 34 состоит из известного сумматора, идентичного одному из 15, 16, 17, 18, 22, 26, указанного выше, регистра в обратной связи и знакового коррелятора на элементе «НЕ». Вычислители модулей 9, 19, 20 построены по схеме согласно а.с. СССР №1501052. Умножители 10, 23, 32 построены по схеме согласно а.с. СССР №1474640. Схемы сравнения 28, 29 и 30 построены на микросхемах 533СП1, выполняющих функцию сравнения.

Таким образом, положительный эффект от использования предлагаемого технического решения заключается в сокращении оборудования за счет упрощения вычисления в новой структурной электрической схеме устройства, которое позволяет повысить надежность и экономичность устройства, упрощение вычисления в новой структурной электрической схеме устройства, увеличение вероятности обнаружения цели на фоне пассивной помехи, устранение неоднозначных сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СИГНАЛА | 2012 |

|

RU2498343C1 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

| Устройство селекции движущихся целей для радиолокатора с вобуляцией периода повторения | 1984 |

|

SU1841287A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СЛОЖНЫХ СИГНАЛОВ | 1988 |

|

SU1841042A1 |

| ВЫЧИСЛИТЕЛЬ ДЛЯ АДАПТИВНОГО РЕЖЕКТИРОВАНИЯ ПОМЕХ | 2015 |

|

RU2582871C1 |

| АДАПТИВНЫЙ ВЫЧИСЛИТЕЛЬ ДЛЯ РЕЖЕКТИРОВАНИЯ ПОМЕХ | 2015 |

|

RU2582874C1 |

| Селектор эхо-сигнала движущихся целей для двухчастотного радиолокатора | 1984 |

|

SU1841292A1 |

| АДАПТИВНЫЙ РЕЖЕКТОР ПАССИВНЫХ ПОМЕХ | 2015 |

|

RU2599621C1 |

| АДАПТИВНЫЙ РЕЖЕКТОРНЫЙ ФИЛЬТР | 2015 |

|

RU2579998C1 |

| ДОПЛЕРОВСКИЙ ФАЗОМЕТР ПАССИВНЫХ ПОМЕХ | 2014 |

|

RU2550315C1 |

Изобретение относится к радиотехнике и может использоваться в радиолокационных станциях обнаружения и сопровождения целей. Способ обработки сигнала состоит в обнаружении цели при двукратной СДЦ с вобуляцией периода повторения, заключается в изменении частоты и фазы сигнала, отраженного от цели, относительно частоты и фазы сигнала пассивной помехи. Устройство для обнаружения сигналов содержит два канала, каждый из которых состоит из последовательно соединенных фазового детектора, аналого-цифрового преобразователя, двух блоков памяти - цифровых линий задержки. В устройство введены шесть блоков вычитания, шесть сумматоров, первого, второго и третьего блоков вычислителя модуля, пятого и шестого блоков вычитания, интегратора, пятого и шестого сумматора, дешифратора, первого, второго и третьего умножителя, первой, второй, третьей и четвертой схемы сравнения, логического элемента «2И-НЕ», логического элемента «И». Перечисленные средства соединены между собой определенным образом. Достигаемым техническим результатом является исключение попадания на экран информации о пассивных помехах и улучшение наблюдаемости полезных сигналов, сокращение конструктивных элементов. 2 н.п. ф-лы, 1 ил.

1. Способ обработки сигнала, состоящий в обнаружении цели при двукратной селекции движущихся целей с вобуляцией периода повторения, заключающийся в изменении частоты и фазы сигнала, отраженного от цели, относительно частоты и фазы сигнала пассивной помехи, учитывающий ширину спектра пассивной помехи и расширение спектра за счет вращения антенны и движения платформы, отличающийся тем, что при вобуляции периода повторения учитывают направление векторов разности фаз сигнала, отраженного от цели, и фаз сигнала, отраженного от пассивной помехи, причем направление вектора разности фаз сигнала, отраженного от цели, полученного в зоне «слепых» скоростей, противоположно направлению вектора разности фаз сигнала, отраженного от пассивной помехи.

2. Устройство для обработки сигнала, содержащее два канала, каждый из которых состоит из последовательно соединенных фазового детектора, аналого-цифрового преобразователя, первого и второго блоков памяти, причем первые входы фазовых детекторов каналов объединены и являются информационными входами эхо-сигнала, а на вторые входы фазовых детекторов поданы опорные сигналы, отличающееся тем, что в него введены первый и второй блоки вычитания в оба канала соответственно, первый и второй сумматоры в каждый канал соответственно, первый, второй и третий блоки вычислителя модуля, пятый и шестой блоки вычитания, интегратор, пятый и шестой сумматоры, дешифратор, первый, второй и третий умножители, первая, вторая, третья и четвертая схемы сравнения, логический элемент «2И-НЕ», логический элемент «И», причем в каждом канале аналого-цифровой преобразователь соединен с первыми входами первого сумматора и с первыми входами первого блока вычитания соответственно, в каждом канале выходы первого блока памяти - цифровой линии задержки соединены со вторыми входами первого блока вычитания и первого сумматора, с первыми входами второго блока вычитания и второго сумматора соответственно, выходы второго блока памяти - цифровой линии задержки соединены со вторыми входами второго блока вычитания и второго сумматора соответственно, выходы первых блоков вычитания первого и второго каналов соединены с первым и вторым входами первого блока вычислителя модуля соответственно, выходы вторых блоков вычитания первого и второго каналов соединены с первым и вторым входами второго блока вычислителя модуля соответственно, выходы знакового разряда первого и второго блоков вычитания первого и второго каналов и первого и второго сумматоров, первого и второго каналов соединены со входом дешифратора, выходы вторых блоков памяти - цифровых линий задержки первого и второго каналов соединены с первым и вторым входами третьего блока вычислителя модуля соответственно, выход третьего блока вычислителя модуля соединен с первыми входами первого и третьего умножителей, выход интегратора соединен со вторым входом первого умножителя, а на второй вход третьего умножителя вводится постоянный коэффициент q, выход первого умножителя соединен со вторым входом шестого блока вычитания, выход шестого блока вычитания соединен со вторым входом второй схемы сравнения и с входом интегратора, выход второго блока вычислителя модуля соединен с первыми входами третьей и четвертой схем сравнения, с первым входом шестого блока вычитания и с первым входом пятого сумматора, выход первого блока вычислителя модуля соединен со вторым входом пятого сумматора и с первым входом второго умножителя, на второй вход которого введен постоянный коэффициент 1, а выход соединен с входом пятого блока вычитания и первым входом шестого сумматора, выход третьего умножителя соединен со вторыми входами пятого блока вычитания и шестого сумматора, а также с первым входом второй схемы сравнения, выходы пятого блока вычитания и шестого сумматора подключены к вторым входам третьей и четвертой схем сравнения соответственно, выход пятого сумматора соединен с первым входом первой схемы сравнения, на второй вход которой подан с выхода третьего умножителя сигнал, умноженный на два за счет смещения разрядной сетки, а выход подключен к первому входу логического элемента «2И-НЕ», выход дешифратора соединен с вторым входом логического элемента «2И-НЕ», выходы второй, третьей, четвертой схем сравнения соединены с вторым, третьим и четвертым входами логического элемента «И» и выход логического элемента «2И-НЕ» соединен с первым входом логического элемента «И», выход логического элемента «И» является выходом устройства Y.

| ВИШИН Г.М | |||

| Селекция движущихся целей | |||

| - М.: Воениздат МО СССР, 1966, с.21-23 | |||

| СПОСОБ И УСТРОЙСТВО СЕЛЕКЦИИ СИГНАЛОВ НАДВОДНОЙ ЦЕЛИ В МОНОИМПУЛЬСНОЙ РЛС | 2004 |

|

RU2278397C2 |

| УСТРОЙСТВО СЕЛЕКЦИИ ДВИЖУЩИХСЯ ЦЕЛЕЙ | 1994 |

|

RU2091809C1 |

| СПОСОБ СЕЛЕКЦИИ ДВИЖУЩИХСЯ ЦЕЛЕЙ В ОДНОЧАСТОТНОМ РАДИОЛОКАТОРЕ С ВОБУЛЯЦИЕЙ ЧАСТОТЫ ПОВТОРЕНИЯ И ЧЕРЕСПЕРИОДНЫМ ВЫЧИТАНИЕМ СИГНАЛОВ НА ПРОМЕЖУТОЧНОЙ ЧАСТОТЕ | 1964 |

|

SU1840641A1 |

| УСТРОЙСТВО СЕЛЕКЦИИ МАЛОВЫСОТНЫХ МАЛОСКОРОСТНЫХ ВОЗДУШНЫХ ЦЕЛЕЙ И ДВИЖУЩИХСЯ НАЗЕМНЫХ ЦЕЛЕЙ В КОГЕРЕНТНОЙ БОРТОВОЙ РАДИОЛОКАЦИОННОЙ СТАНЦИИ | 2005 |

|

RU2298809C9 |

| WO 2006017265 A3, 17.01.2008 | |||

| US 5402131 A, 28.03.1995 | |||

| US 4121212 A, 17.10.1978 | |||

| EP 1884801 A1, 06.02.2008 | |||

| WO 2005001508 A1, 06.01.2005. | |||

Авторы

Даты

2011-01-20—Публикация

2009-04-23—Подача