75

.

оо сх

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных системах, где требуется загщ- та внешней памяти ЗКМ от ошибок.

Цель изобретения - упрощение устройства и повьпчение быстродействия за счет уменьшения начальной задержки при перемежении символов кода Ри- да-Соломона.

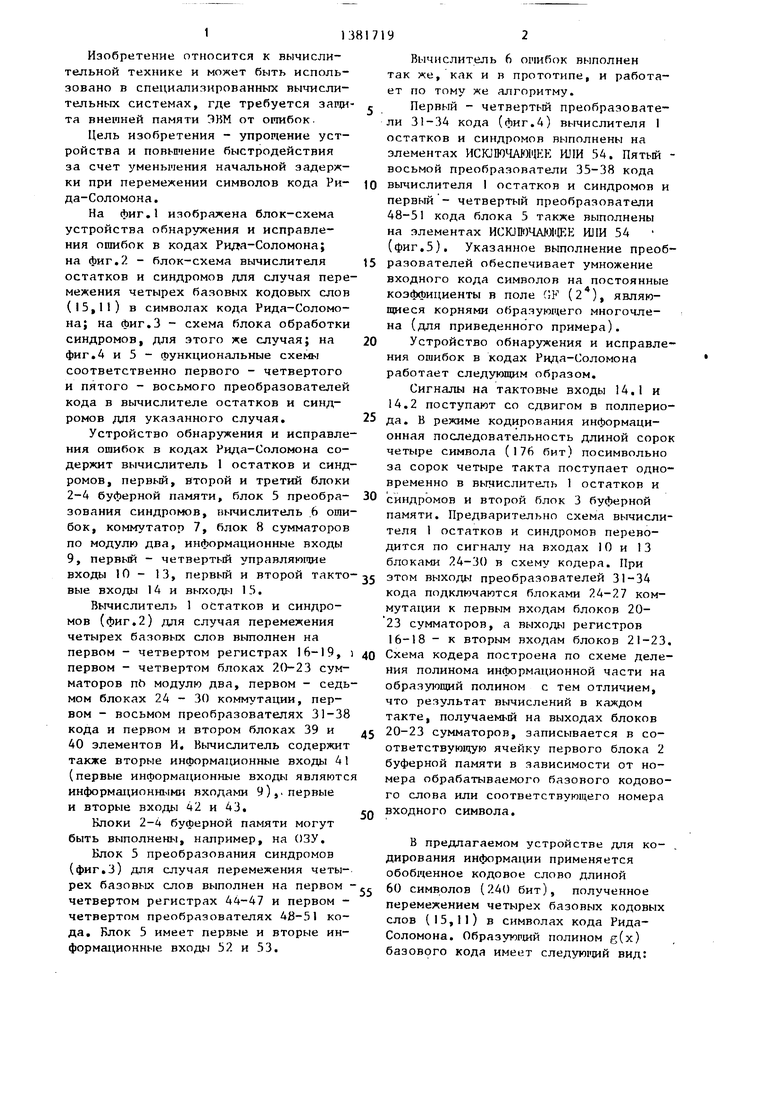

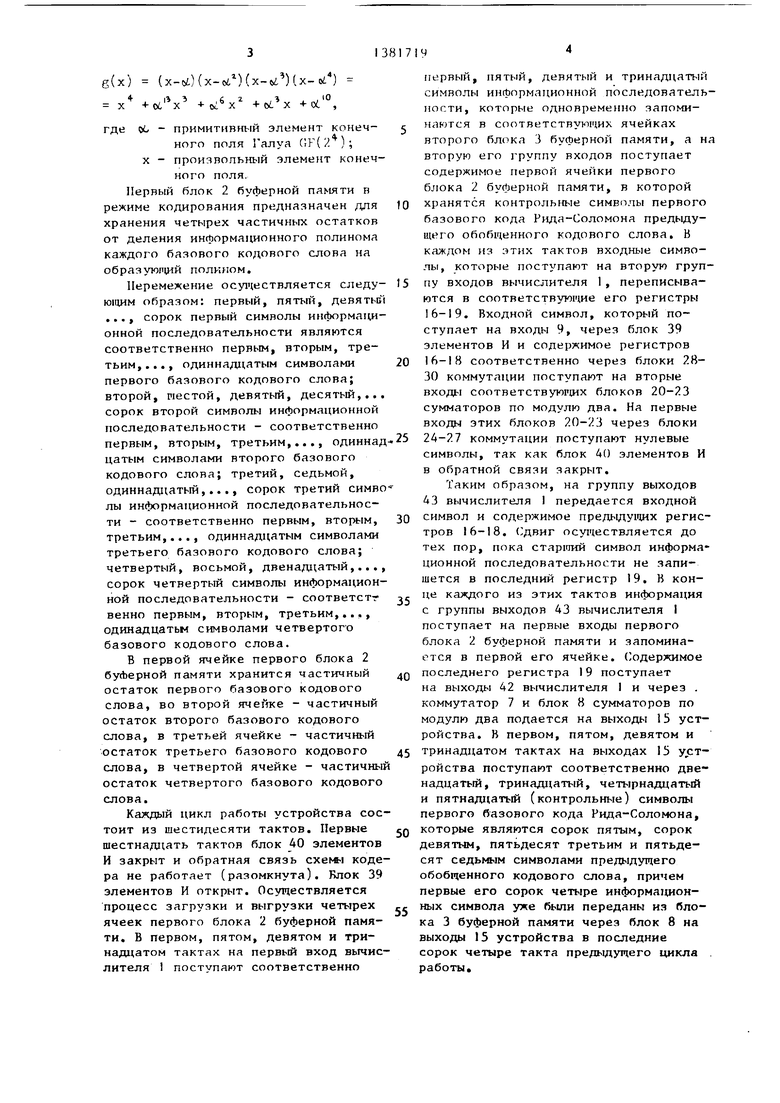

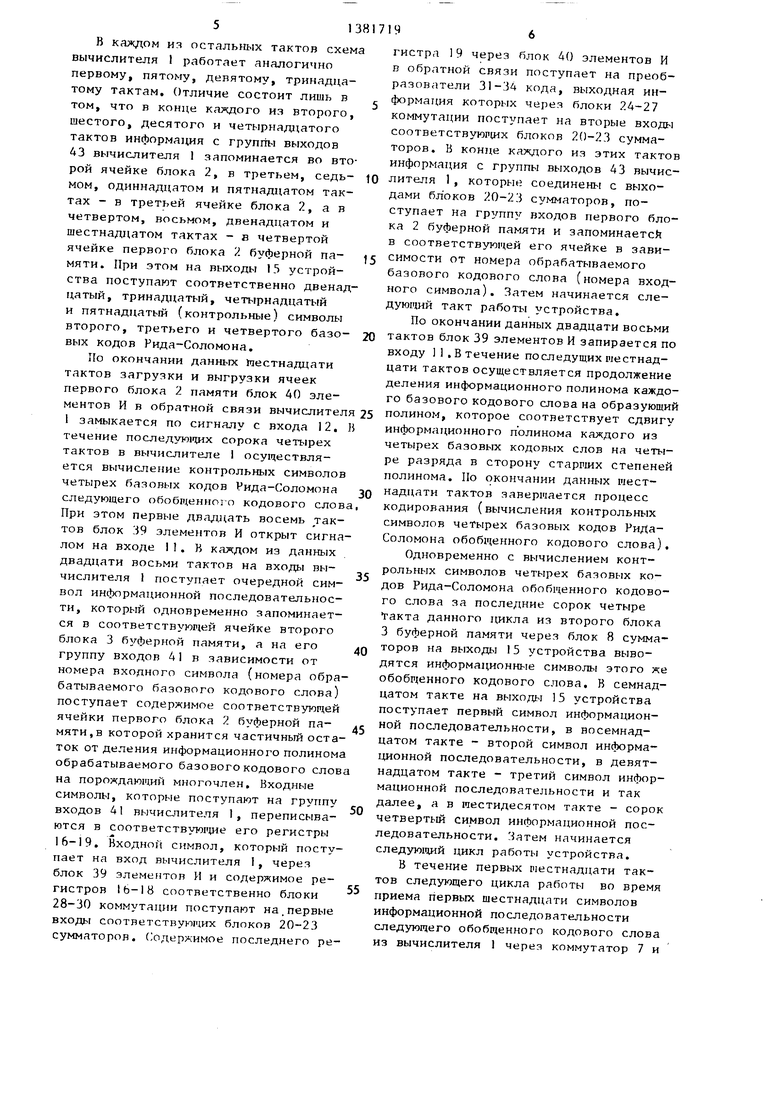

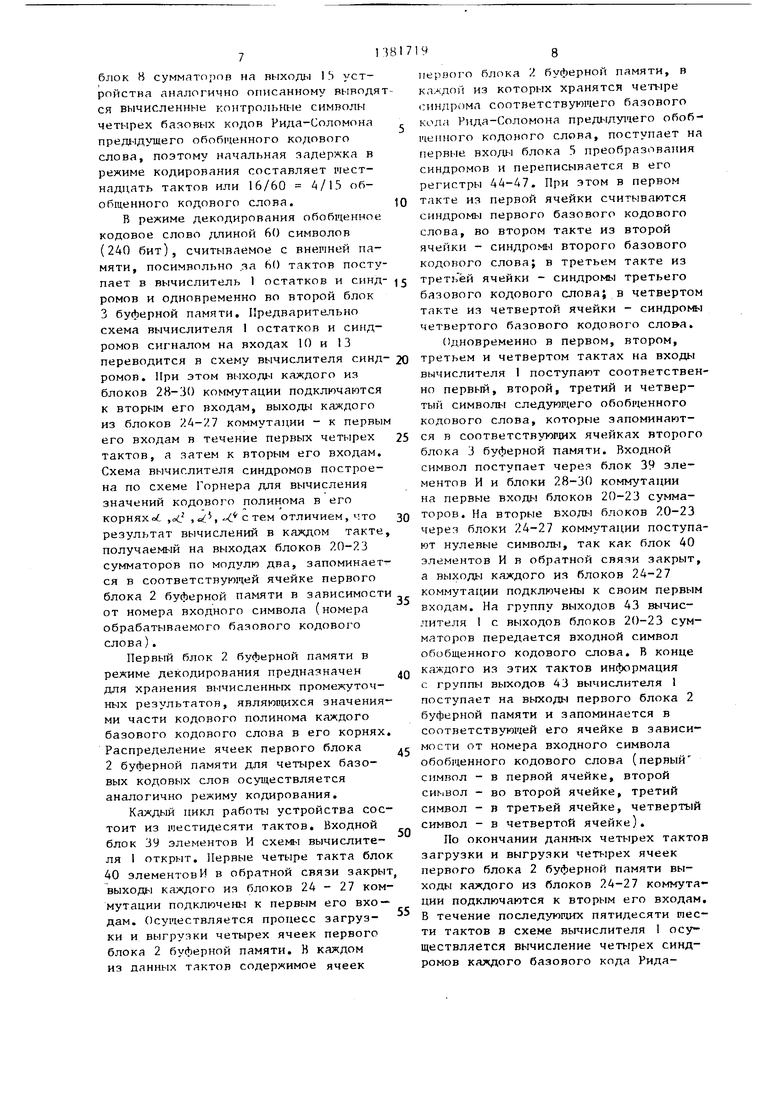

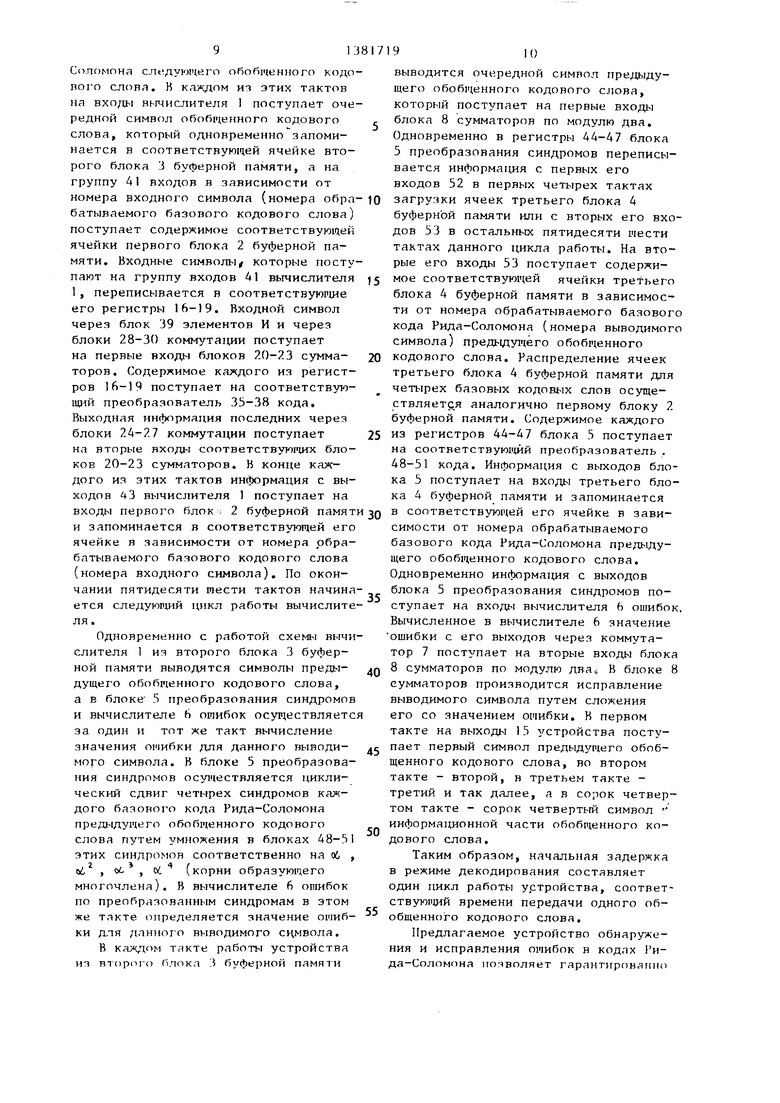

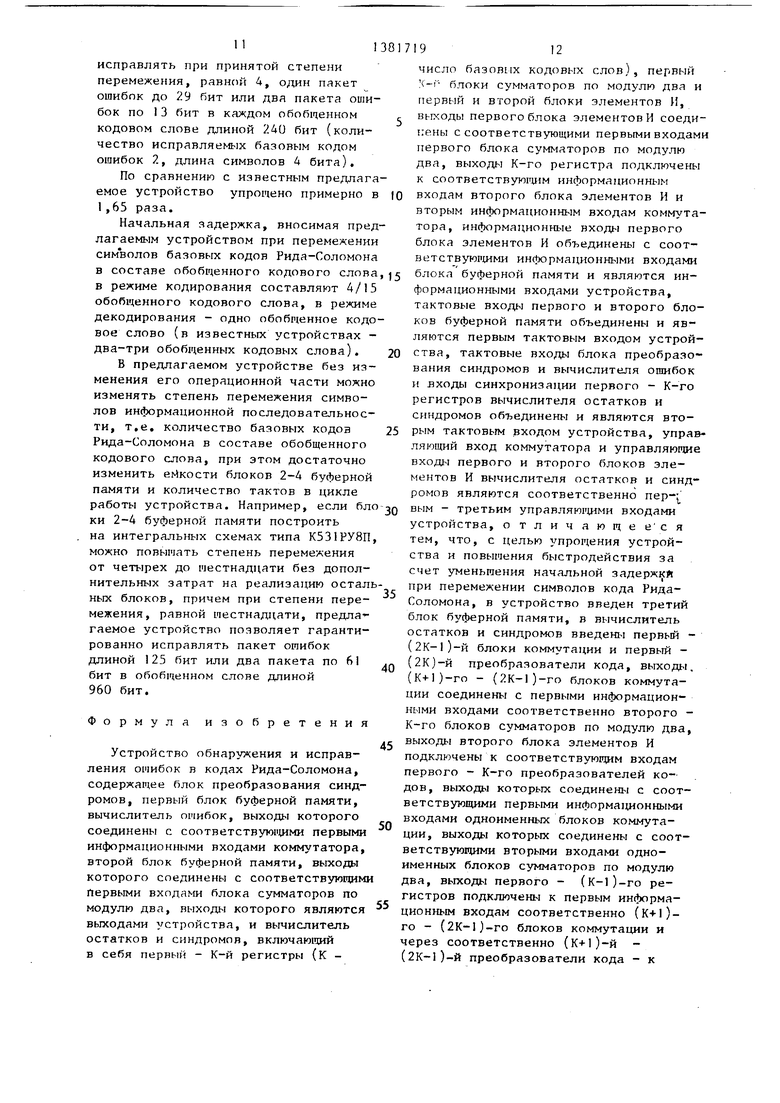

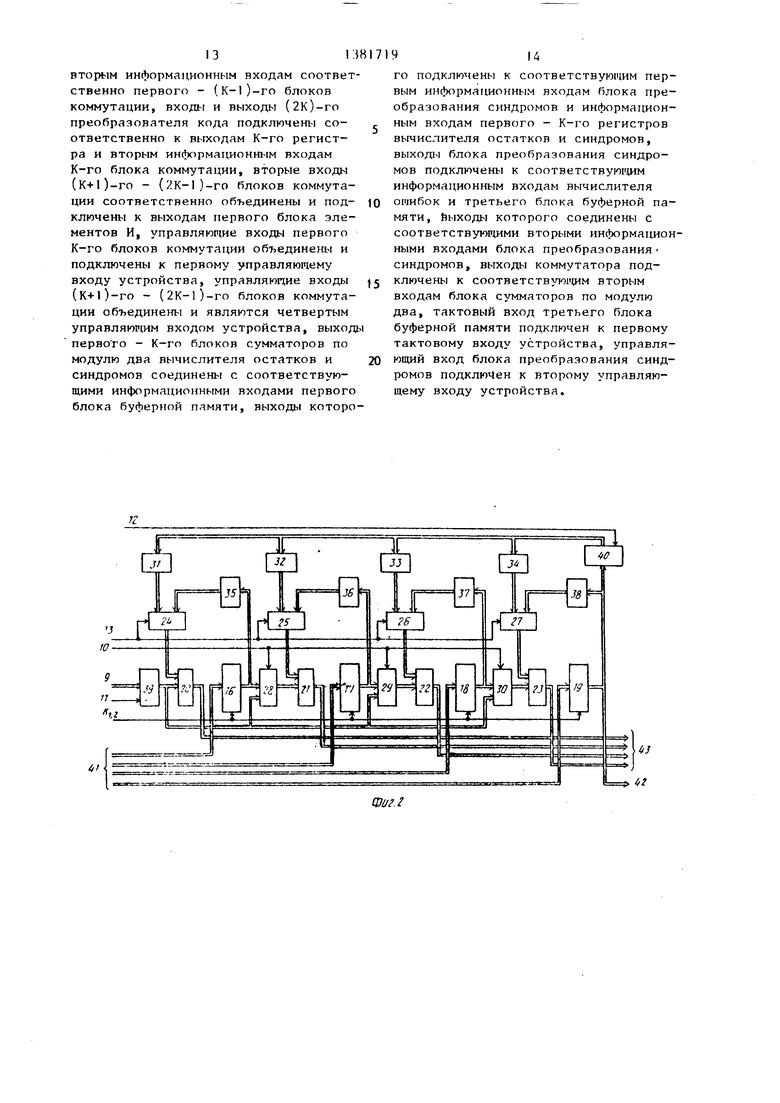

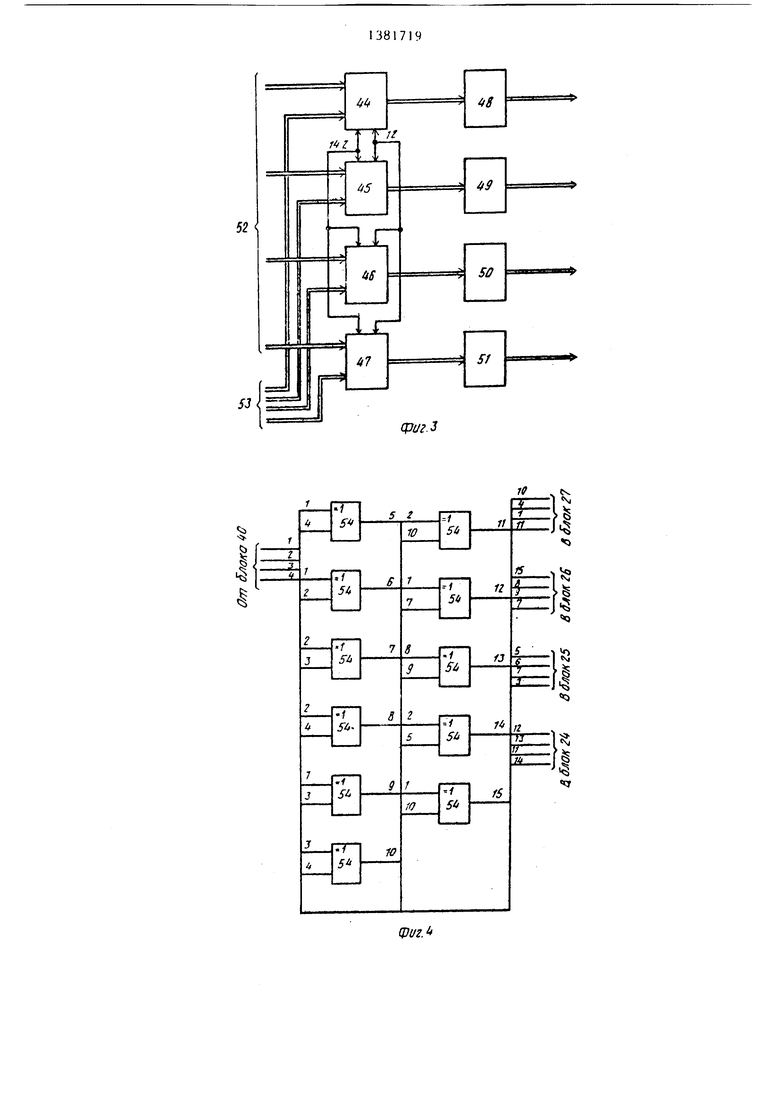

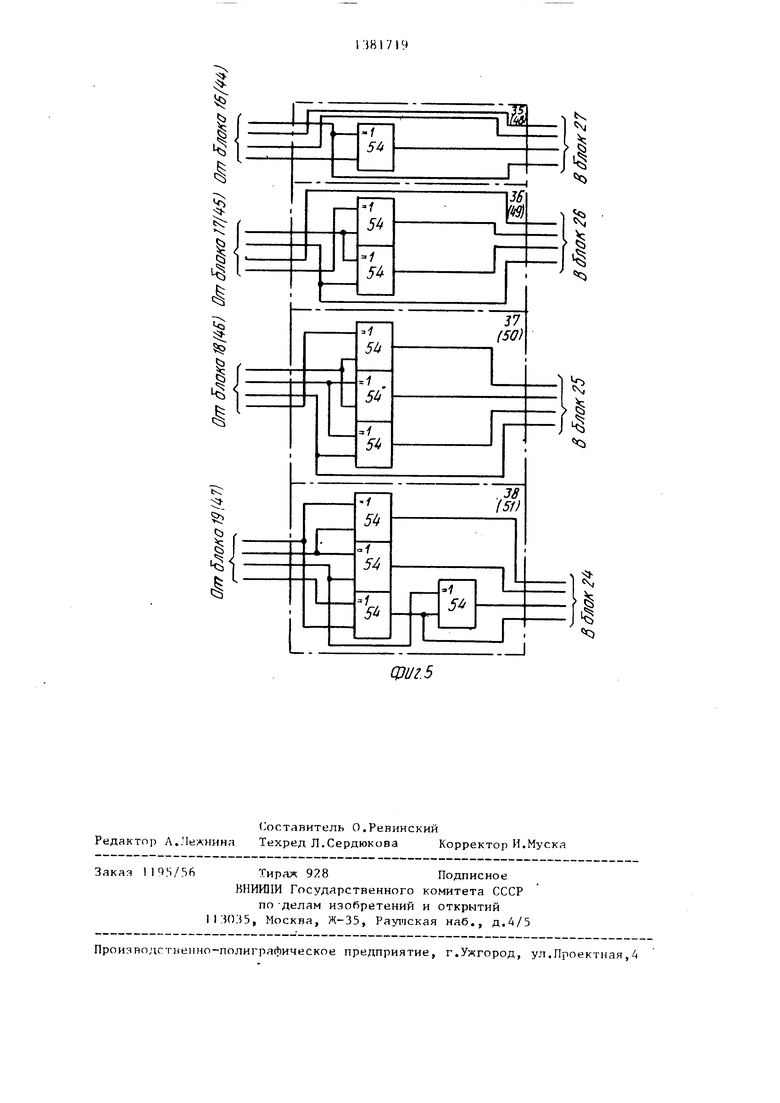

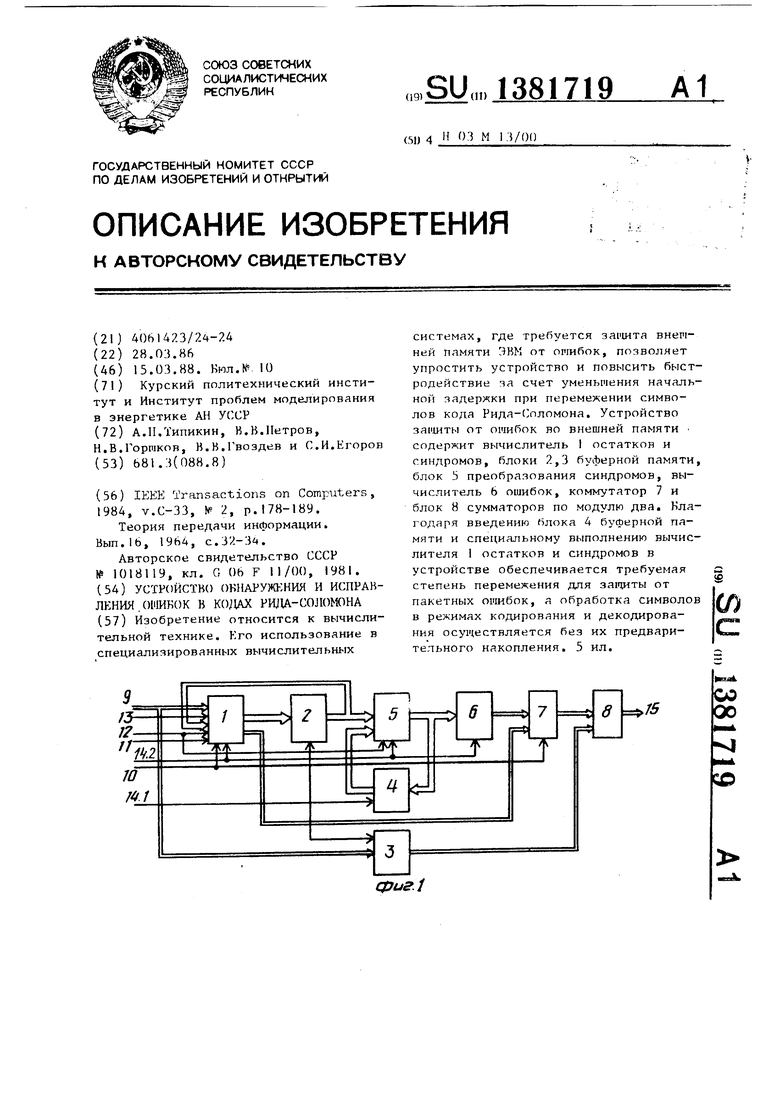

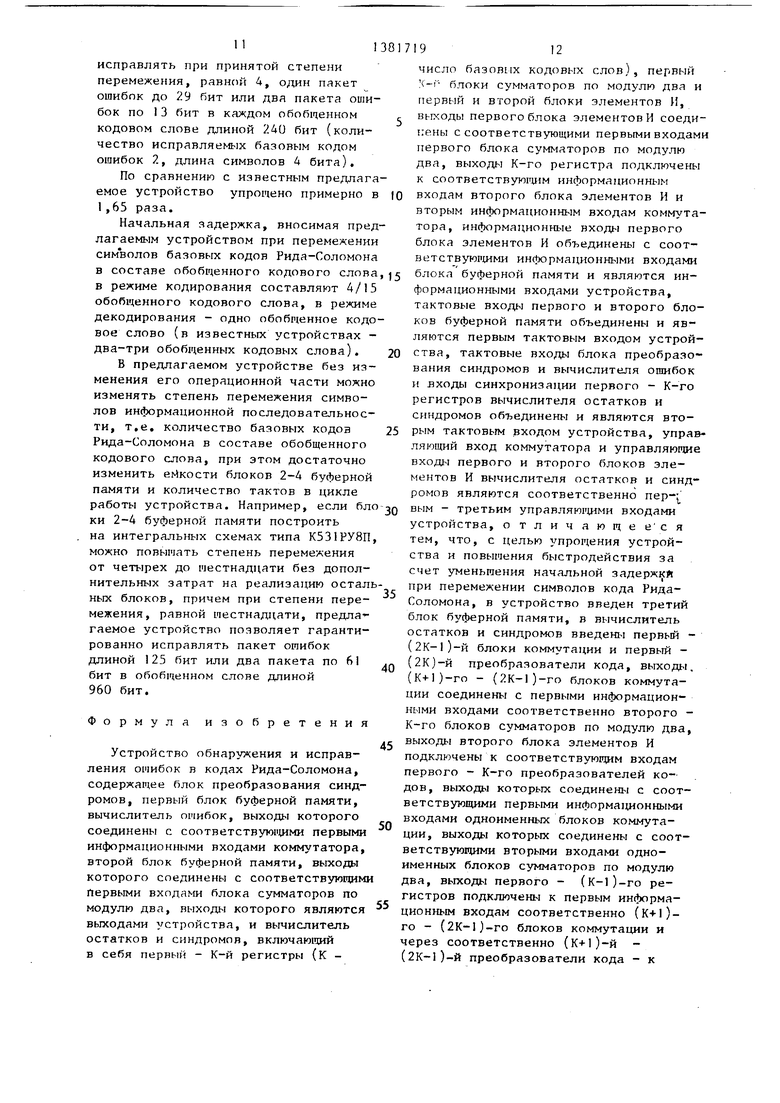

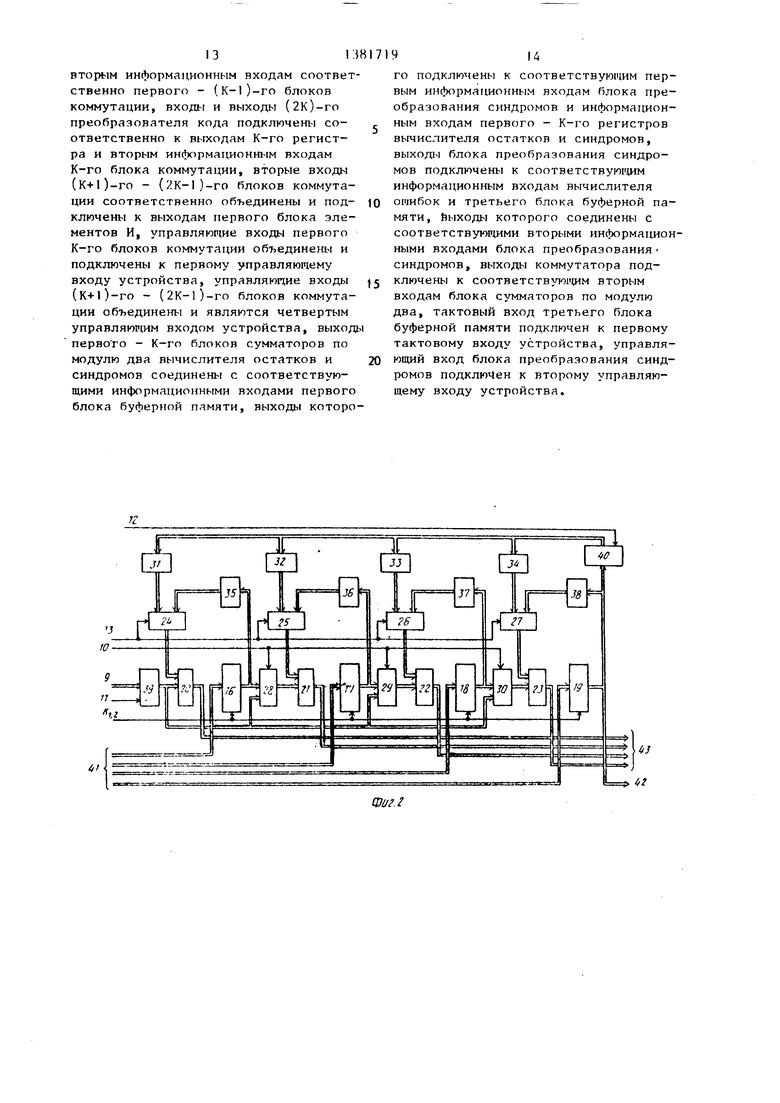

На фиг.1 изображена блок-схема устройства обнаружения и исправления ошибок в кодах Рида-Соломона; на фиг.2 - блок-схема вычислителя остатков и синдромов для случая пере- межения четырех базовых кодовых слов (15,11) в символах кода Рида-Соломона; на фиг.З - схема блока обработки синдромов, для этого же случая; на фиг.4 и 5 - функциональные схемы соответственно первого - четвертого и пятого - восьмого преобразователей кода в вычислителе остатков и синдромов для указанного случая.

Устройство обнаружения и исправления ошибок в кодах Рида-Соломона содержит вычислитель 1 остатков и синдромов, первый, второй и третий блоки 2-4 буферной памяти, блок 5 преобра- зования синдромов, вычислитель ,6 ошибок, коммутатор 7, блок 8 сумматоров по модулю два, информационные входы 9, первый - четвертый управляющие входы 10 - 13, первый и второй тактовые входы 14 и выходы 15,

Вычислитель 1 остатков и синдромов (фиг.2) для случая перемежения четырех базовых слов выполнен на первом - четвертом регистрах 16-19, первом - четвертом блоках 2()-23 сумматоров nt модулю два, первом - седьмом блоках 24 - 30 коммутации, первом - восьмом преобразователях 31-38 кода и первом и втором блоках 39 и 40 элементов И, Вычислитель содержит также вторые информационные входы 41 (первые информационные входы являютс информационными входами 9),. первые и вторые входы 42 и 43,

Клоки 2-4 буферной памяти могут быть выполнены, например, на ОЗУ.

Блок 5 преобразования синдромов (фиг.З) для случая перемежения четырех базовых слов выполнен на первом четвертом регистрах 44-47 и первом - четвертом преобразователях 48-51 кода. Клок 5 имеет первые и вторые информационные входы 52 и 53.

Q

5 0 5

0 c

0 е

0

Вычислитель 6 ошибок выполнен так же, как и в прототипе, и работает по тому же алгоритму.

Первый - четвертый преобразователи 31-34 кода (фиг.4) вычислителя 1 остатков и синдромов выполнены на элементах ИСЮПОЧАПЩЕК ИЛИ 54. Пятый - восьмой преобразователи 35-38 кода вычислителя 1 остатков и синдромов и первый - четвертый преобразователи 48-51 кода блока 5 также выполнены на элементах ИСЮВОЧАРВДЕ ИЛИ 54 (фиг.5). Указанное выполнение преобразователей обеспечивает умножение входного кода символов на постоянные коэффициенты в поле (IF (2 ), являющиеся корнями образующего многочлена (для приведенного примера).

Устройство обнаружения и исправления ошибок в кодах Рида-Соломона работает следующим образом.

Сигналы на тактовые входы 14.1 и 14.2 поступают со сдвигом в полпериода. В режиме кодирования информационная последовательность длиной сорок четыре символа (176 бит) посимвольно за сорок четыре такта поступает одновременно в вычислитель 1 остатков и синдромов и второй блок 3 буферной памяти. Предварительно схема вычислителя 1 остатков и синдромов переводится по сигналу на входах IО и 13 блоками 24-30 в схему кодера. При этом выходы преобразователей 31-34 кода подключаются блоками 24-27 коммутации к первым входам блоков 20- 23 сумматоров, а выходы регистров 16-18 - к вторым входам блоков 21-23. Схема кодера построена по схеме деления полинома информационной части на образующий полином с тем отличием, что результат вычислений в каждом такте, получаемый на выходах блоков 20-23 сумматоров, записывается в со- ответствую1чую ячейку первого блока 2 буферной памяти в зависимости от номера обрабатываемого базового кодового слова или соответствующего номера входного символа.

В предлагаемом устройстве для ко- . дирования информации применяется обобщенное кодовое слово длиной 60 символов (240 бит), полученное перемежением четырех базовых кодовых слов (15,11) в символах кода Рида- Соломона. Образующий полином g(x) базового кода имеет следуюг й вид:

g(x) (x-ci)(x-)()(x-oi ) - x oc °,

где oC - примитивный элемент конеч-

ного поля Галуа (;К(2 ); X - произвольный элемент конечного поля.

Первый блок 2 буферной памяти в режиме кодирования предназначен для хранения четырех частичных остатков от деления информационного полинома каждого базового кодового слова на образуто1ций полином.

Иеремежение осутцествляется следу- Ю1ЦИМ образом: первый, пятый, девятьв ..., сорок первый символы информационной последовательности являются соответственно первым, вторым, третьим,.,., одиннадцатым символами первого базового кодового слова; второй, шестой, девятый, десятый,.. сорок второй символы информаиионной последовательности - соответственно

первым, вторым, третьим одиннад

иатым символами второго базового кодового слова; третий, седьмой, одиннадцатый,..., сорок третий симво лы информаиионной последовательности - соответственно первым, вторым,

третьим одиннадиятым символами

третьего базового кодового слова; четвертый, восьмой, двенадцатый,... сорок четвертый символы информаиионной последовательности - соответстг венно первым, вторым, третьим,..,, одинадцатьм символами четвертого базового кодового слова.

В первой ячейке первого блока 2 буАерной памяти хранится частичный остаток первого базового кодового слова, во второй ячейке - частичный остаток второго базового кодового слова, в третьей ячейке - частичный остаток третьего базового кодового слова, в четвертой ячейке - частичны остаток четвертого базового кодового слова.

Каждый цикл работы устройства состоит из шестидесяти тактов. Первые шестнадцать тактов блок 40 элементов И закрыт и обратная связь схеь«-1 кодера не работает (разомкнута). Блок 39 элементов И открыт. Осуществляется процесс загрузки и выгрузки четырех ячеек первого блока 2 буферной памяти. В первом, пятом, девятом и тринадцатом тактах на первый вход вычислителя 1 поступают соответственно

первый, пятый, девятый и тринадцатый символьЕ информационной последовательности, которые одновременно запоминаются в соответствукицих ячейках второго блока 3 буферной памяти, а н вторую его группу входов поступает содержимое первой ячейки первого блока 2 буферной памяти, в которой хранятся контрольные символы первого базового кода Рида-Соломона предыдущего обобщенного кодового слова. В каждом из этих тактов входные символы, которые поступают на вторую группу входов вычислителя 1, переписываются в соответствующие его регистры 16-19. Входной символ, который поступает на входы 9, через блок 39 элементов И и содержимое регистров 16-18 соответственно через блоки 28- 30 коммутации поступают на вторые входы соответствуюгшх блоков 20-23 сумматоров по модулю два. На первые входы этих блоков 20-23 через блоки 24-27 коммутации поступают нулевые символы, так как блок 40 элементов И в обратной связи закрыт.

Таким образом, на группу выходов 43 вычислителя 1 передается входной символ и содержимое предыдуищх регистров 16-18. (двиг осу1цествляется до тех пор, пока старший символ информационной последовательности не запишется в последний регистр 19. В конце каждого из этих тактов информация с группы выходов 43 вычислителя I поступает на первые входы первого блока 2 буферной памяти и запоминается в первой его ячейке. (Содержимое последнего регистра 19 поступает на выходы 42 вычислителя 1 и через . коммутатор 7 и блок 8 сумматоров по модулю два подается на выходы 15 устройства. В первом, пятом, девятом и тринадцатом тактах на выходах 15 устройства поступают соответственно двенадцатый, тринадцатый, четырнадцатый и пятнадцатый (контрольные) символы первого базового кода Рида-Соломона, которые являются сорок пятым, сорок девятым, пятьдесят третьим и пятьдесят седьмым символами предыдущего обобщенного кодового слова, причем первые его сорок четыре информа1Д1он- ных символа уже были переданы из блока 3 буферной памяти через блок 8 на выходы 15 устройства в последние сорок четыре такта предыдущего цикла работы.

513

В каждом ия осталымх тактов схема вычислителя I работает аналогично первому, пятому, девятому, тринадцатому тактам. Отличие состоит лишь в том, что в конце каждого из второго, шестого, десятого и четырнадцатого тактов информа1шя с группы выходов 43 вычислителя 1 запоминается во второй ячейке блока 2, в третьем, седьмом, одиннадцатом и пятнадцатом тактах - в третьей ячейке блока 2, а в четвертом, восьмом, двенадцатом и шестнадцатом тактах - в четвертой ячейке первого блока 2 буферной памяти. При этом на выходы 15 устройства поступают соответственно двенадцатый, тринадцатый, четырнадцатый и пятнадцатый (контрольные) символы второго, третьего и четвертого базовых кодов Рида-Соломона.

По окончании данных Шестнадцати тактов загрузки и выгрузки ячеек первого блока 2 памяти блок 40 элементов И в обратной связи вычислителя 1 замыкается по сигналу с входа 12. В течение последую1 шх сорока четырех тактов в вычислителе 1 осуществляется вычисление контрольных символов четырех базовых кодов Рида-Соломона следующего обобщенног о кодового слова При этом первые двадцать восемь ак- тов блок 39 элементов И открыт сигналом на входе 11. В каждом из данных двадцати восьми тактов на входы вычислителя 1 поступает очередной символ информационной последовательности, который одновременно запоминается в соответствующей ячейке второго блока 3 буферной памяти, а на его группу входов 41 в зависимости от номера входного символа (номера обрабатываемого базового кодового слова) поступает содержимое соответствующей ячейки первого блока 2 буферной па- мяти,в которой хранится частичный остаток от деления информационного полинома обрабатываемого базового кодового слов на порождающий многочлен. Входные символы, которые поступают на группу входов 41 вычислителя 1, переписываются в соответствую1 Д1е его регистры 16-19. Входной символ, который поступает на вход вычислителя I, через блок 39 элементов И и содержимое регистров 16-18 соответственно блоки 28-30 коммутации поступают на.первые входы соответствующих блоков 20-23 сумматоров. (Содержимое последнего ре

o

5

0

17

5 Q дс

5

0

196

гистра 19 через блок 40 элементов И в обратной связи поступает на преобразователи 31-34 кода, выходная информация которых через блоки 24-27 коммутации поступает на вторые входы соответствуюР1их блоков 20-23 сумматоров. В конце каждого из этих тактов информация с группы выходов 43 вычислителя 1, которые соединены с выходами блоков 20-23 сумматоров, поступает на группу входов первого блока 2 буферной памяти и запоминаетсй в соответствующей его ячейке в зависимости от номера обрабатываемого базового кодового слова (номера входного символа). Затем начинается следующий такт работы устройства.

По окончании данных двадцати восьми тактов блок 39 элементов И запирается по входу 1 , В течение последущих шестнадцати тактов осуществляется продолжение деления информационного полинома каждого базового кодового слова на образующий полином, которое соответствует сдвигу информационного полинома каждого из четырех базовых кодовых слов на четыре разряда в сторону старгшх степеней полинома. По окончании данных шестнадцати тактов завершается процесс кодирования (вычисления контрольных символов четырех базовых кодов РиДа- Соломона обобщенного кодового слова).

Одновременно с вычислением контрольных символов четырех базовых кодов Рида-Соломона обобщенного кодового слова за последние сорок четыре такта данного цикла из второго блока 3 буферной памяти через блок 8 сумматоров на выходы 15 устройства выводятся информационные символы этого же обобр енного кодового слова. В семнадцатом такте на выхода: 15 устройства поступает первый символ информационной последовательности, в восемнадцатом такте - второй символ информационной последовательности, в девятнадцатом такте - третий символ информационной последовательности и так далее, а в шестидесятом такте - сорок четвертый символ информационной последовательности. начинается следую1чий цикл работы устройства.

В течение первых ршстнадцати тактов следующего цикла работы во время приема первых шестнадцати символов информационной последовательности следующего обобщенного кодового слова из вычислителя 1 через коммутатор 7 и

блок 8 сумматоров на выходы 1 .S устройства аналогично описанному выводятся вычисленные контрольные символы четырех базовых кодов Рида-Соломона предыдущего обоб1ценного кодового слова, поэтому начальная задержка в режиме кодирования составляет шестнадцать тактов или 16/60 А/15 обобщенного кодового слова.

В режиме декодирования обобщенное кодовое слово длиной 60 символов (240 бит), считываемое с внешней памяти, посимвольно .за 60 тактов поступает в вычислитель 1 остатков и синд- ромов и одновременно во второй блок 3 буферной памяти, Иредваритапьно схема вычислителя I остатков и синдромов сигналом на входах 10 и 13 переводится в схему вычислителя синд- ромов. При этом выходы каждого из блоков 28-30 коммутации подключаются к вторым его входам, выходы каждого из блоков 7Л- А1 коммутации - к первым

его входам в течение первых четырех тактов, а затем к вторым его входам. Схема вычислителя синдромов построена по схеме Горнера для вычисления значений кодового полин ома в его корняхоС с ,а, с тем отличием, что результат вычислений в каждом такте получаемый на выходах блоков 20-.3 сумматоров по модулю два, запоминает ся в соответствующей ячейке первого блока 2 буферной памяти в зависимости от номера входного символа (номера обрабатываемого базового кодового слова).

Первый блок 2 буферной памяти в режиме декодирования предназначен для хранения вычисленных промежуточных результатов, являюпщхся значениями части кодового полинома каждого базового кодового слона в его корнях. Распределение ячеек первого блока 2 буферной памяти для четырех базовых кодовых слов осуществляется аналогично режиму кодирования.

Каждый цикл работы устройства состоит из шестидесяти тактов. Входной блок 39 элементов И схемы вычислителя 1 открыт. Первые четыре такта блок 40 элементов И в обратной связи закрыт выходы каждого из блоков 24-27 коммутации подключены к первым его входам. Осуществляется процесс загрузки и выгрузки четырех ячеек первого блока 2 буферной памяти. Н каждом из данных тактов содержимое ячеек

j 0

5

0

5

0

5

0

первого блока 2 буферной памяти, в каждой из которых хранятся четыре синдрома соответствующего базового кода Рида-Соломона предыдуччего обобщенного кодового слова, поступает на первые входы блока 3 преобразования синдромов и переписывается в его регистры 44-47. При этом в первом такте из первой ячейки считываются синдромы первого базового кодового слова, во втором такте из второй ячейки - синдромы второго базового кодового слова; в третьем такте из треть ёй ячейки - синдромы третьего базового кодового слова; в четвертом такте из четвертой ячейки - синдромы четвертого базового кодового слова.

Одновременно в первом, втором, третьем и четвертом тактах на входы вычислителя 1 поступают соответственно первый, второй, третий и четвертый символы следующего обоб1ченного кодового слова, которые запоминаются в соответствуюг1их ячейках второго блока 3 буферной памяти. Входной символ поступает через блок 39 элементов И и блоки 28-30 коммутации на первые входы блоков 20-23 сумматоров. На вторые входы блоков 20-23 через блоки 24-27 коммутации поступают нулевые символы, так как блок 40 элементов И в обратной связи закрыт, а выходы каз«сдого из блоков 24-27 коммутации подключены к своим первым входам. На группу выходов 43 вычислителя 1 с выходов блоков 20-23 сумматоров передается входной символ обобщенного кодового слова. В конце каждого из этих тактов информация с группы выходов 43 вычислителя 1 поступает на выходы первого блока 2 буферной памяти и запоминается в соответствующей его ячейке в зависимости от номера входного символа обоб1ценного кодового слова (первый символ - в первой ячейке, второй сиь.вол - во второй ячейке, третий символ - в третьей ячейке, четвертый символ - в четвертой ячейке).

По окончании данных четырех тактов загрузки и выгрузки четырех ячеек первого блока 2 буферной памяти выходы каждого из блоков 24-27 коммутации подключаются к вторым его входам. В течение последуюгцтх пятидесяти шести тактов в схеме вычислителя 1 осуществляется вычисление четырех синдромов каждого базового кода РидаСоломона следуклчего обобщен}1ого кодового слова. В каждом из этих тактов на входы вычислителя 1 поступает очередной символ обобщенного кодового слова, который одновременно запоминается в соответствующей ячейке второго блока 3 буферной памяти, а на группу 41 входов в зависимости от номера входного символа (номера обрабатываемого базового кодового слова) поступает содержимое соответствуюь ей ячейки первого блока 2 буферной памяти. Входные символы которые поступают на группу входов 41 вычислителя 1 , переписывается в соответству1орц1е его регистры 16-19. Входной символ через блок 39 элементов И и через блоки 28-30 ком гутации поступает на первые входы блоков 20-23 сумматоров. Содержимое каждого из регистров 16-19 поступает на соответствующий преобразователь 35-38 кода. Выходная информация последних через блоки 24-27 коммутации поступает на вторые входы соответствукичих блоков 20-23 су шаторов. В конце каждого ия этих тактов информация с выходов 43 вычислителя 1 поступает на входы первого блок 2 буферной памят и запоминается в соответствующей его ячейке в зависимости от номера обрабатываемого базового кодового слова (номера входного символа). По окончании пятидесяти тести тактов начинается следуюгц1Й цикл работы вычислителя.

Одновременно с работой схемы вычислителя 1 ия второго блока 3 буферной памяти выводятся символы предыдущего обобщенного кодового слова, а в блоке 5 преобразования синдромов и вычислителе 6 ошибок осугдествляетс за один и тот же такт вычисление значения ошибки для данного выводи- MOf-Q символа. В блоке 5 преобразования синдромов осутчествляется циклический сдвиг четырех синдромов каждого базового кода Рида-Соломона пред1чдущего обобхценного кодового слова путем умножения в блоках 48-31 этих синдромов соответственно на (Л , oi , (корни образующего многочлена). В вычислителе 6 ошибок по преобразованным синдромам в этом же такте определяется значение ошибки для данног о выводимого символа.

В каждом такте работы устройства из впорот о Плока 3 буферной памяпи

5

0

5

0

5

0

5

0

5

выводится очередной символ предыдущего обоб1ценного кодового слова, который поступает на первые входы блока 8 сумматоров по модулю два. Одновременно в регистры 44-47 блока 5 преобразования синдромов переписывается информация с первых его входов 52 в первых четырех тактах загрузки ячеек третьего блока 4 буферной памяти или с вторых его входов 53 в остальных пятидесяти шести тактах данного цикла работы. На вторые его входы 53 поступает содержимое соответствующей ячейки третьего блока 4 буферной памяти в зависимости от номера обрабатываемого базового кода Рида-Соломона (номера выводимого символа) предыду1цего обобщенного кодового слова. Распределение ячеек третьего блока 4 буферной памяти для четырех базовых кодовых слов осуществляется аналогично первому блоку 2 буферной памяти. Содержимое каждого из регистров 44-47 блока 5 поступает на соответствую1 щй преобразователь , 48-51 кода. Информация с выходов блока 5 поступает на входы третьего блока 4 буферной памяти и запоминается в соответствующей его ячейке в зависимости от номера обрабатываемого базового кода Рида-Соломона предыдущего обобщенного кодового слова. Одновременно информация с выходов блока 5 преобразования синдромов поступает на входы вычислителя 6 ошибок. Вычисленное в вычислителе 6 значение ощибки с его выходов через коммутатор 7 поступает на вторые входы блока 8 сумматоров по модулю два о В блоке 8 сумматоров производится исправление выводимого символа путем сложения его со значением опибки. В первом такте на выходы 15 устройства поступает первый символ предыдущего обобщенного кодового слова, во втором такте - второй, в третьем такте - третий и так далее, а в сорок четвертом такте - сорок четвертый символ информационной части обобщенного кодового слова.

Таким образом, начальная задержка в режиме декодирования составляет один цикл работы устройства, соответ- ствуюнщй времени передачи одного обобщенного кодового слова.

Предлагаемое устройство обнаружения и исправления ошибок в кодах 1 и- да-Солом :)на позволяет гарантированно

11

исправлять при принятой степени перемежепия, равнс)й 4, один пакет ошибок до 29 бит или два пакета ошибок по 13 бит в каждом обобщенном кодовом слове длиной .40 бит (количество исправляемых базовым кодом ошибок 2, длина символов 4 бита),

По сравнению с известным предлагаемое устройство упрощено примерно в 1,65 раза.

Начальная задержка, вносимая предлагаемым устройством при перемежении сим волов базовых кодов Рида-Соломона в составе обоб1ценного кодового слова в режиме кодирования составляют 4/15 обобщенного кодового слова, в режиме декодирования - одно обобщенное кодовое слово (в известных устройствах - два-три обобщенных кодовых слова).

В предлагаемом устройстве без изменения его операционной части можно изменять степень перемежения символов информационной последовательности, т.е. количество базовых кодов Рида-Соломона в составе обобщенного кодового слова, при этом достаточно изменить еМкости блоков 2-4 буферной памяти и количество тактов в цикле

число базових кодовых слов), первы -Г- блоки сумматоров по модулю два первый и второй блоки элементов И, выходы первого блока элементов И соед нены с соответствующими первыми вход первого блока сумматоров по модулю два, выходы К-го регистра подключе к соответствуюгдим информационным входам второго блока элементов И и вторым информационным входам комму тора, информационные входь первого блока элементов И объединены с соо ветствуюпшми информационными входа блока буферной памяти и являются и формационными входами устройства, тактовые входы первого и второго бл ков буферной памяти объединены и яв ляются первым тактовым входом устро ства, тактовые входы блока преобраз вания синдромов и вычислителя ошибо и входы синхронизации первого - К-г регистров вычислителя остатков и синдромов объединены и являются вто рым тактовым входом устройства, упр ляюцщй вход коммутатора и управляющ входы первого и второго блоков элементов И вычислителя остатков и син ромов являются соответственно перработы устройства. Например, если бло- jQ вым - третьим управляющими входами

ки 2-4 буферной памяти построить на интегральных схемах типа К531РУ8П, можно повышать степень перемежения от четырех до шестнадцати без дополнительных затрат на реализацию остальных блоков, причем при степени перемежения, равной шестнадцати, предла- гаемое устройство позволяет гарантированно исправлять пакет ошибок длиной 125 бит или два пакета по 61 бит в обобщенном слове длиной 960 бит.

35

40

устройства, отличающее ся тем, что, с целью упрощения устройства и повышения быстродействия за счет уменьшения начальной задержки при перемежении символов кода Рида- Соломона, в устройство введен трети блок буферной памяти, в вычислитель остатков и синдромов введены первый (2К-1)-й блоки коммутации и первый (2К)-й преобразователи кода, выход ()-го - (2К-1)-го блоков коммута ции соединены с первыми информацион ными входами соответственно второго К-го блоков сумматоров по модулю дв выходы второго блока элементов И подключены к соответствующим входам первого - К-го преобразователей кодов, выходы которых соединены с соот ветствующими первыми информатцюнными входами одноименных блоков коммутации, выходы которых соединены с соот ветствующими вторыми входами одноименных блоков сумматоров по модулю два, выходы первого - (К-1)-го регистров подключены к первым информационным входам соответственно (K-t-l)- го - {2К-1)-го блоков коммутации и через соответственно (К+1)-й - (2К-1)-й преобразователи кода - к

Формула изобретения

Устройство обнаружения и исправления ошибок в кодах Рида-Соломона, содержащее блок преобразования синдромов, первый блок буферной памяти, вычислитель ошибок, выходы которого соединены с соответствую1 щми первыми информационными входами коммутатора, второй блок буферной памяти, выходы которого соединены с соответствующим Первыми входами блока сумматоров по модулю два, выходы которого являются выходами устройства, и вычислитель остатков и синдромов, включающий в себя первый - К-й регистры (К 10

58171912

число базових кодовых слов), первый -Г- блоки сумматоров по модулю два и первый и второй блоки элементов И, выходы первого блока элементов И соединены с соответствующими первыми входами первого блока сумматоров по модулю два, выходы К-го регистра подключены к соответствуюгдим информационным входам второго блока элементов И и вторым информационным входам коммутатора, информационные входь первого блока элементов И объединены с соот- ветствуюпшми информационными входами блока буферной памяти и являются информационными входами устройства, тактовые входы первого и второго блоков буферной памяти объединены и являются первым тактовым входом устройства, тактовые входы блока преобразования синдромов и вычислителя ошибок и входы синхронизации первого - К-го регистров вычислителя остатков и синдромов объединены и являются вторым тактовым входом устройства, управ- ляюцщй вход коммутатора и управляющие входы первого и второго блоков элементов И вычислителя остатков и синдромов являются соответственно пер20

25

jQ вым - третьим управляющими входами

5

0

5

0

5

устройства, отличающее ся тем, что, с целью упрощения устройства и повышения быстродействия за счет уменьшения начальной задержки при перемежении символов кода Рида- Соломона, в устройство введен третий блок буферной памяти, в вычислитель остатков и синдромов введены первый - (2К-1)-й блоки коммутации и первый - (2К)-й преобразователи кода, выходы. ()-го - (2К-1)-го блоков коммутации соединены с первыми информационными входами соответственно второго - К-го блоков сумматоров по модулю два, выходы второго блока элементов И подключены к соответствующим входам первого - К-го преобразователей кодов, выходы которых соединены с соответствующими первыми информатцюнными входами одноименных блоков коммутации, выходы которых соединены с соответствующими вторыми входами одноименных блоков сумматоров по модулю два, выходы первого - (К-1)-го регистров подключены к первым информационным входам соответственно (K-t-l)- го - {2К-1)-го блоков коммутации и через соответственно (К+1)-й - (2К-1)-й преобразователи кода - к

13i

вторым информационным входам соответственно первого - (K-l)-ro блоков коммутации, входы и выходы (2К)-го преобразователя кода подключены со- ответственно к выходам К-го регистра и вторым информационным входам К-го блока коммутации, вторые входы (К+1)-го - (.К-1)-го блоков коммутации соответственно объединены и под- ключены к выходам первого блока элементов И, управляюр;ие входы первого К-го блоков коммутации объединены и подключены к первому управляющему входу устройства, управляющие входы (К+1)го - (2K-l)-ro блоков коммутации объедине1ты и являются четвертым управляющим входом устройства, выход перво го - К-го блоков сумматоров по модулю два вычислителя остатков и синдромов соединены с соответствующими информационными входами первого блока буферной памяти, выходы которо

4

14

го подключены к соответствующим первым информационным входам блока преобразования синдромов и информационным входам первого - К-го регистров вычислителя остатков и синдромов, выходы блока преобразования синдромов подключены к соответствую1 Д1м информационным входам вычислителя ошибок и третьего блока буферной памяти, йыходы которого соединены с соответствующими вторыми информационными входами блока преобразования синдромов, выходы коммутатора подключены к соответствую1 №1м вторым входам блока сумматоров по модулю два, тактовый вход третьего блока буферной памяти подключен к первому тактовому входу устройства, управляющий вход блока преобразования синдромов подключен к второму управляющему входу устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство защиты от ошибок внешней памяти | 1981 |

|

SU1018119A1 |

| Устройство для исправления ошибок | 1987 |

|

SU1432787A1 |

| Устройство кодирования и вычисления синдромов помехоустойчивых кодов для коррекции ошибок во внешней памяти ЭВМ | 1989 |

|

SU1656689A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| Устройство коррекции двойных ошибок с использованием кода Рида-Соломона | 1988 |

|

SU1662010A1 |

| Устройство для декодирования линейных кодов | 1985 |

|

SU1287297A1 |

| Устройство для вычисления синдромов кода Рида-Соломона | 1990 |

|

SU1751860A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КАСКАДНОГО КОДА РИДА-СОЛОМОНА | 1993 |

|

RU2036512C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КОДОВ РИДА-СОЛОМОНА | 2006 |

|

RU2314639C1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

Изобретение относится к вычислительной технике. Кго использование в специализированных вычислительных системах, где требуется заишта внешней памяти ЭВМ от ошибок, позволяет упростить устройство и повысить быстродействие за счет уменьшения начальной задержки при перемежении символов кода Рида-(уОломона. Устройство заищты от ошибок во внешней памяти содержит вычислитель 1 остатков и синдромов, блоки 2,3 буферной памяти, блок 5 преобразования синдромов, вычислитель 6 ошибок, коммутатор 7 и блок 8 сумматоров по модулю два. Ьла- годаря введению блока 4 буферной памяти и специальному выполнению вычислителя 1 остатков и синдромов в устройстве обеспечивается требуемая степень перемежения для за1титы от пакетных ошибок, а обработка символов в режимах кодирования и декодирования осуществляется без их предварительного накопления. 5 ил. ;о

52

SJ

(fft/г.з

I

«Ъ

«Ci

ери г. 5

| IEEE Transactions on Computers, 1984, v.C-33, fp 2, p.178-189 | |||

| Теория передачи информации | |||

| Вып | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Устройство защиты от ошибок внешней памяти | 1981 |

|

SU1018119A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-15—Публикация

1986-03-28—Подача