Изобретение относится к области автоматического регулирования и может быть использовано в корректирующих устройствах следящих систем, в преобразовательных устройствах и измерительных приборах.

Известно интегрирующее устройство с усилителем постоянного тока, в котором резистор включен последовательно с инвертирующим входом усилителя, а конденсатор включен в цепь обратной связи между выходом усилителя и его инвертирующим входом [1].

Недостатком известного устройства является его низкая точность.

Известно интегрирующее устройство, содержащее операционный усилитель, вход которого через первый ключ соединен с источником сигнала, интегрирующий конденсатор, первый вывод которого соединен с входом операционного усилителя непосредственно, а второй вывод через второй ключ - с выходом операционного усилителя, а также третий ключ, включенный между входом и выходом операционного усилителя [2].

Однако указанное устройство имеет низкую точность, обусловленную тем, что не обеспечивается полная компенсация дрейфа нуля на выходе устройства.

Наиболее близким по технической сущности и достигаемому результату к заявляемому изобретению является устройство для интегрирования, которое содержит два блока интегрирования, блок дифференцирования, блок сравнения и сумматор [3].

Указанное устройство имеет низкую точность, обусловленную тем, что не обеспечивается для второго блока интегрирования компенсация изменения выходного сигнала от влияния дестабилизирующих факторов: изменения в процессе работы постоянной времени, коэффициента усиления усилителя постоянного тока, дрейфа остаточного напряжения усилителя и тока утечки конденсатора.

Заявляемое изобретение решает задачу создания устройства, лишенного вышеперечисленных недостатков. Техническим результатом, достигаемым при использовании заявляемого изобретения, является повышение точности интегрирования за счет компенсации дестабилизирующих факторов на выходной сигнал.

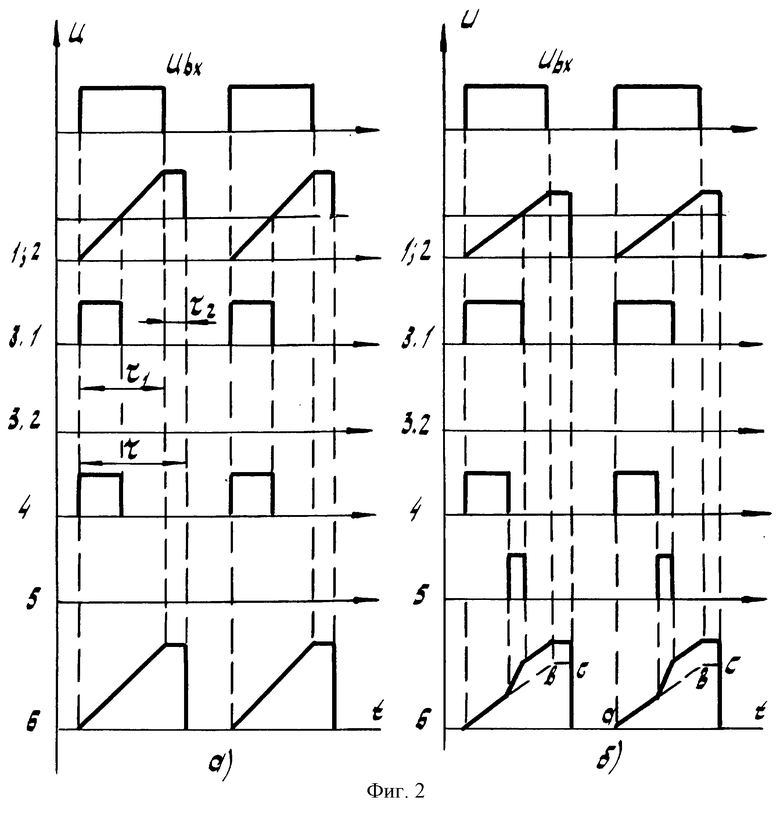

Поставленная цель достигается тем, что в интегрирующее устройство, содержащее два блока интегрирования, вход одного блока интегрирования является входом устройства, введены источник образцового напряжения, формирователь образцового временного интервала, блок сравнения длительностей импульсов и формирователь импульсов, первый вход которого подсоединен к выходу первого блока интегрирования, информационный вход которого соединен с первым информационным входом второго блока интегрирования, выход источника образцового напряжения подключен ко второму входу формирователя импульсов, второй выход которого подсоединен одновременно к управляющим входам первого и второго блоков интегрирования, а первый вход непосредственно и через формирователь образцового временного интервала соединен с первым и вторым входами блока сравнения длительностей импульсов соответственно, выход которого подключен ко второму информационному входу второго блока интегрирования, выход которого подсоединен к выходу устройства.

Сопоставительный анализ с прототипом показывает, что заявляемое интегрирующее устройство отличается тем, что в него дополнительно введены источник образцового напряжения, формирователь образцового временного интервала, блок сравнения длительностей импульсов и формирователь импульсов, первый вход которого подсоединен к выходу первого блока интегрирования, информационный вход которого соединен с первым информационным входом второго блока интегрирования, выход источника образцового напряжения подключен ко второму входу формирователя импульсов, второй выход которого подсоединен одновременно к управляющим входам первого и второго блоков интегрирования, а первый выход непосредственно и через формирователь образцового временного интервала соединен с первым и вторым входами блока сравнения длительностей импульсов соответственно, выход которого подключен ко второму информационному входу второго блока интегрирования, выход которого подсоединен к выходу устройства.

Таким образом, заявляемое интегрирующее устройство соответствует критерию изобретения "новизна".

Сравнение заявляемого технического решения с другими техническими решениями в данной области не позволило выявить в них признаки, отличающие заявляемое интегрирующее устройство от прототипа. Это позволяет сделать вывод о соответствии критерию "Изобретательский уровень".

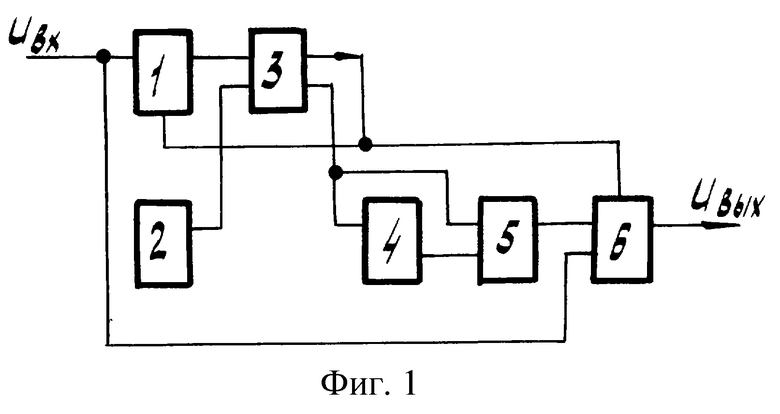

На фиг.1 приведена структурная схема интегрирующего устройства, на фиг.2 а, б - временные диаграммы, поясняющие его работу.

Интегрирующее устройство содержит два блока интегрирования 1, 6, источник образцового напряжения 2, формирователь импульсов 3, формирователь образцового временного интервала 4, блок сравнения длительностей импульсов 5. Информационный вход первого блока интегрирования 1 и первый информационный вход второго блока интегрирования 6 соединены с входом устройства. Выход источника образцового напряжения 2 подключен ко второму входу формирователя импульсов 3, первый вход которого подсоединен к выходу первого блока интегрирования 1. Первый выход формирователя импульсов 3 соединен одновременно с управляющими входами блоков интегрирования 1, 6. Второй выход формирователя импульсов 3 подключен непосредственно и через формирователь образцового временного интервала 4 к первому и второму входам блока сравнения длительностей импульсов 5. Выход блока сравнения длительностей 5 соединен со вторым входом блока интегрирования 6, выход которого подсоединен к выходу устройства.

Заявляемое изобретение представляет собой систему автоматического регулирования по отклонению.

Для защиты выхода интегрирующего устройства от перегрузки в качестве датчика выходного сигнала используется блок интегрирования 1.

Рассмотрим работу интегрирующего устройства для случая, когда входной сигнал имеет форму прямоугольных импульсов. Входной сигнал подается на информационный вход первого и на первый информационный вход второго блоков интегрирования 1 и 6, характеристики которых идентичны и изменяются идентично (синхронно) в процессе эксплуатации от воздействия дестабилизирующих факторов. Выходной сигнал блока интегрирования 1 и образцовое напряжение с выхода блока 2 поступают на первый и второй входы формирователя импульсов 3, на первом выходе которого формируется прямоугольный импульс (3.1), начало которого совпадает с моментом начала интегрирования входного сигнала, а конец - с моментом перехода с низкого уровня на высокий сигнала 1 через уровень сигнала 2. Передним фронтом этого импульса запускается формирователь образцового временного интервала, на выходе которого формируется образцовый импульс, длительность которого равна длительности импульса на первом выходе формирователя импульсов 3 при отсутствии дестабилизирующих факторов. На втором выходе формирователя импульсов 3 формируется импульс (3.2) с задержкой на время τ относительно переднего фронта импульса (3.1). Этим импульсом блоки интегрирования 1 и 6 сбрасываются в исходное состояние. Длительность τ определяется по следующей формуле

τ = τ1+τ2, (1)

где τ1 - время изменения уровня выходного сигнала блока интегрирования 1;

τ2 - время записи сигнала 6, определяемое назначением интегрирующего устройства.

Входные импульсы имеют постоянный уровень. Сигналы с первого выхода формирователя импульсов 3 и формирователя образцового временного интервала 4 поступают на первый и второй входы блока сравнения длительностей импульсов 5, на выходе которого снимаются импульсы, длительности которых равны разности длительностей импульсов 3 и 4 с соответствующим знаком. Сигнал на выходе блока 5 равен нулю при отсутствии влияния дестабилизирующих факторов. Этот случай приведен на фиг.2а. Если дестабилизирующие факторы действуют в сторону уменьшения уровня выходного сигнала блоков интегрирования, то знак выходного сигнала блока 5 совпадает со знаком входного сигнала интегрирующего устройства. Этот режим приведен на фиг.2б. Выходной сигнал блока 5 поступает на второй информационный вход блока интегрирования 6, который компенсирует влияние дестабилизирующих факторов на выходной сигнал интегрирующего устройства. На фиг. 2б линией а-b-с показано изменение выходного сигнала интегрирующего устройства, если бы отсутствовала компенсация изменения выходного сигнала от дестабилизирующих факторов.

Введение источника образцового напряжения, формирователя импульсов, формирователя образцового временного интервала и блока сравнения длительностей импульсов с соответствующими связями выгодно отличает предлагаемое техническое решение от прототипа, так как позволяет повысить точность работы интегрирующего устройства.

Источники информации

1. Кобринский Н. Е. Математические машины непрерывного действия. М., 1954.

2. Патент Японии 48 - 15588, 97/8/В2, кл. G 06 G 7/00, 1973.

3. Авторское свидетельство 542199, G 06 G 7/18, 05.01.77.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО ДВУХТАКТНОГО ИНТЕГРИРОВАНИЯ | 2012 |

|

RU2521305C2 |

| УСТРОЙСТВО ДЛЯ ДИНАМИЧЕСКОГО ТОРМОЖЕНИЯ ТРЕХФАЗНОГО АСИНХРОННОГО ЭЛЕКТРОДВИГАТЕЛЯ | 2002 |

|

RU2227364C2 |

| ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2002 |

|

RU2228540C1 |

| СПОСОБ ИЗМЕРЕНИЯ ИЗНОСА РЕЖУЩЕГО ИНСТРУМЕНТА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2354955C1 |

| СПОСОБ И УСТРОЙСТВО ДВУХТАКТНОГО ИНТЕГРИРОВАНИЯ С КОМПЕНСАЦИЕЙ ПОГРЕШНОСТЕЙ | 2013 |

|

RU2523939C1 |

| УСТРОЙСТВО ДЛЯ ОГРАНИЧЕНИЯ КРУТЯЩЕГО МОМЕНТА НА ВАЛУ АСИНХРОННОГО ЭЛЕКТРОДВИГАТЕЛЯ | 2004 |

|

RU2259003C1 |

| Устройство для ограничения крутящего момента на валу электродвигателя | 1982 |

|

SU1056351A1 |

| Фазовый компаратор | 1982 |

|

SU1094141A2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КРУТЯЩЕГО МОМЕНТА НА ВАЛУ ЭЛЕКТРОДВИГАТЕЛЯ | 2004 |

|

RU2269752C1 |

| Устройство для контроля крутящего момента на валу электродвигателя | 1979 |

|

SU964492A2 |

Изобретение относится к автоматике для использования в корректирующих устройствах следящих систем, в преобразовательных и измерительных устройствах. Технический результат заключается в повышении точности за счет компенсации дестабилизирующих факторов. Устройство (У) содержит блоки интегрирования (БИ) (1) и (6), вход БИ (1) является входом У, формирователь импульсов (ФИ) (3), первый вход которого подсоединен к выходу БИ (1), информационный вход которого соединен с первым информационным входом БИ (6), выход источника образцового напряжения (2) подключен ко второму входу ФИ (3), второй выход которого подсоединен одновременно к управляющим входам БИ (1) и (6), а первый выход - непосредственно и через формирователь образцового временного интервала (4) соединен с первым и вторым входами блока сравнения длительностей импульсов (БСДИ) (5) соответственно. Выходной сигнала БСДИ (5) поступает на вход БИ (6) и компенсирует влияние дестабилизирующих факторов. 2 ил.

Интегрирующее устройство, содержащее два блока интегрирования, вход одного блока интегрирования является входом устройства, отличающееся тем, что в него введены источник образцового напряжения, формирователь образцового временного интервала, блок сравнения длительностей импульсов и формирователь импульсов, первый вход которого подсоединен к выходу первого блока интегрирования, информационный вход которого соединен с первым информационным входом второго блока интегрирования, выход источника образцового напряжения подключен ко второму входу формирователя импульсов, второй выход которого подсоединен одновременно к управляющим входам первого и второго блоков интегрирования, а первый выход - непосредственно и через формирователь обрацового временного интервала соединен с первым и вторым входами блока сравнения длительностей импульсов соответственно, выход которого подключен ко второму информационному входу второго блока интегрирования, выход которого подсоединен к выходу устройства.

| Устройство для интегрирования | 1975 |

|

SU542199A1 |

| ИНТЕГРАТОР ПЕРИОДИЧЕСКИХ НАПРЯЖЕНИЙ | 1999 |

|

RU2149448C1 |

| Интегрирующее устройство | 1989 |

|

SU1624484A1 |

| US 3742202, 26.06.1973 | |||

| ЩЕРБАКОВ В.И | |||

| и др | |||

| Электронные схемы на операционных усилителях | |||

| Справочник | |||

| - Киев: Технiка, 1983, с.74, рис.4.7а. | |||

Авторы

Даты

2004-01-27—Публикация

2002-07-22—Подача