:о 1

AfJf

в

| название | год | авторы | номер документа |

|---|---|---|---|

| ФАЗОВЫЙ КОМПАРАТОР | 2005 |

|

RU2282935C1 |

| ФАЗОВЫЙ КОМПАРАТОР | 2003 |

|

RU2240646C1 |

| Фазовый компаратор | 1979 |

|

SU845279A1 |

| Частотно-фазовый детектор | 1990 |

|

SU1775844A1 |

| ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2006 |

|

RU2300170C1 |

| Цифровой интегрирующий вольтметр | 1983 |

|

SU1093984A2 |

| Устройство для импульсно-фазового управления тиристором | 1987 |

|

SU1467694A1 |

| Цифровой интегрирующий вольтметр | 1985 |

|

SU1267272A1 |

| Цифровой фазометр | 1985 |

|

SU1298687A2 |

| Устройство для контроля крутящего момента на валу электродвигателя | 1981 |

|

SU972276A1 |

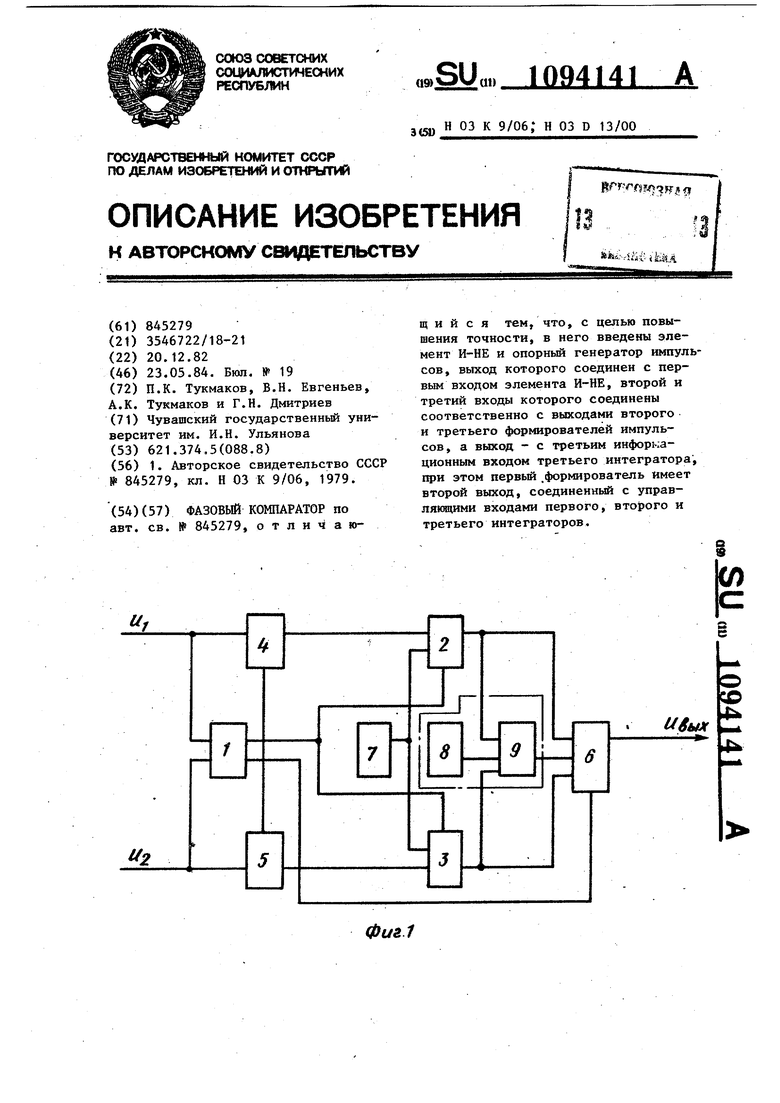

ФАЗОВЫЙ КОМПАРАТОР по авт. св. № 845279, отличающийся тем, что, с целью повышения точности, в него введены элемент И-НЕ и опорный генератор импульсов, выход которого соединен с первым входом элемента И-НЕ, второй и третий входы которого соединены соответственно с выходами второго и третьего формирователей импульсов, а выход - с третьим инфоркационным входом третьего интегратора, гфи этом первый ,формирователь имеет второй выход, соединенный с управляющими входами первого, второго и третьего интеграторов.

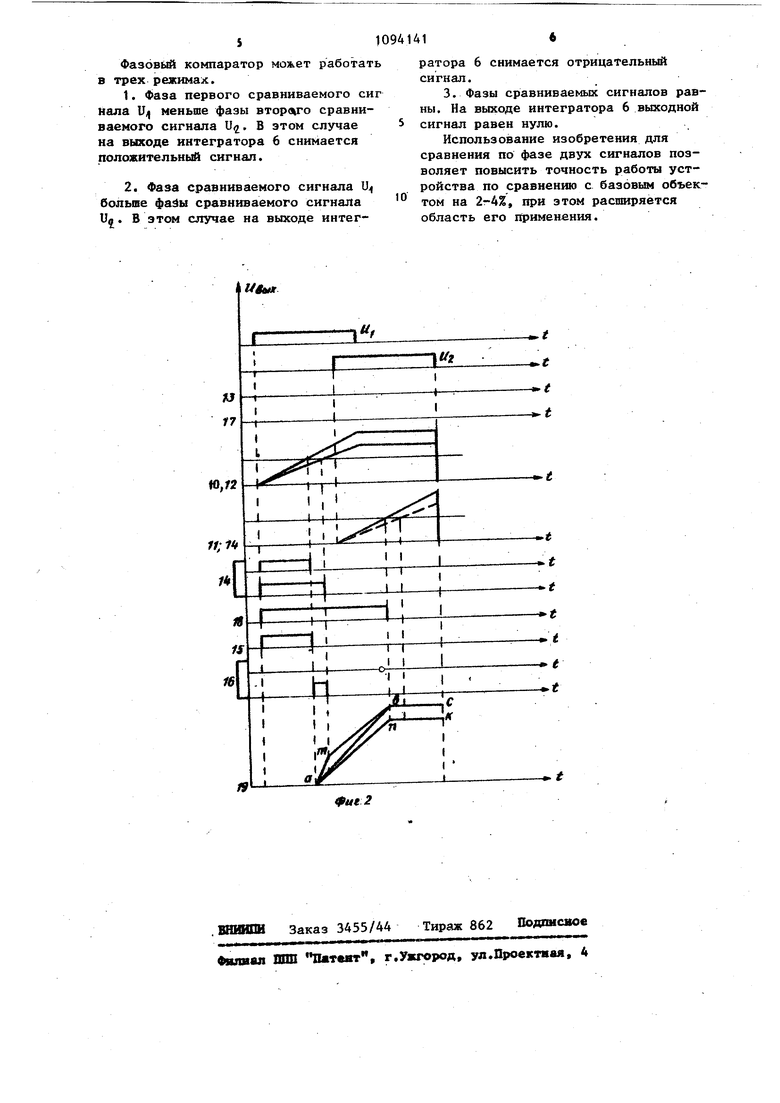

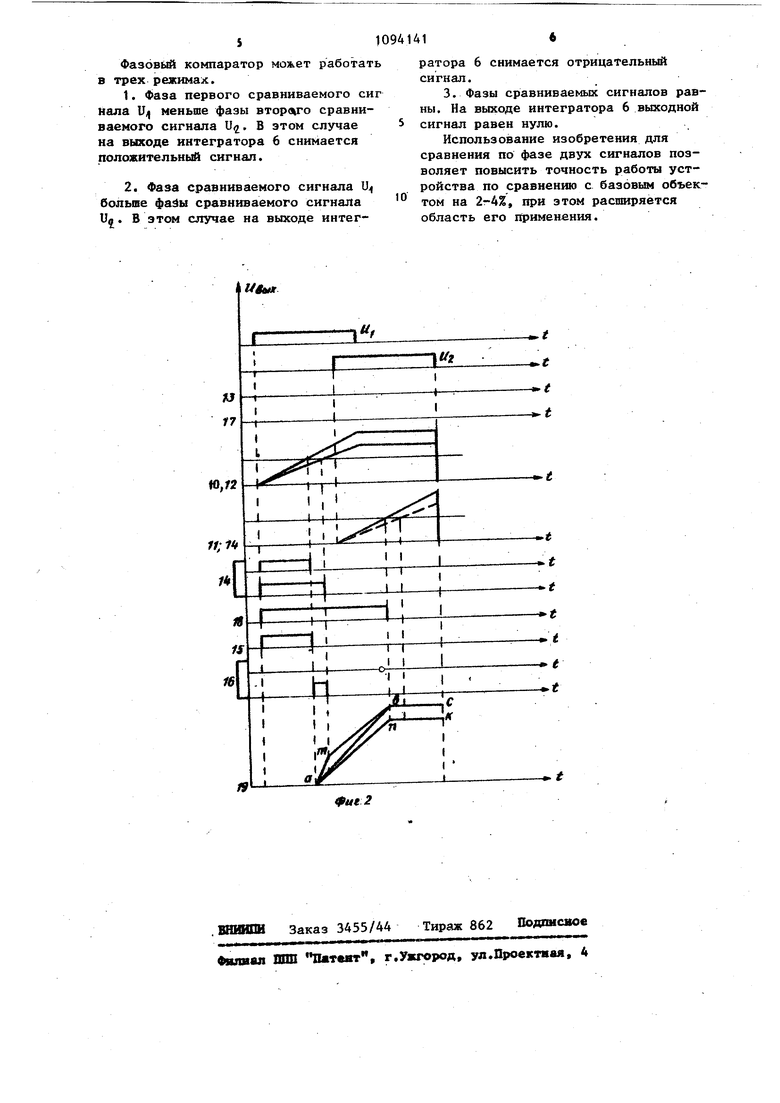

Фил.1 I Изобретение относится к измерите ной технике и может быть использова но в автоматизированных системах уп равления технологическим) процессами при фаяовом методе формирования управлякяцего или информационного сигнала. По основному авт. св. № 845279 известен фазовый компаратор, содержащий три интегратора, входы первого и второго из которых соединет ны с формирователями, источник опор ного напряжения, два формирователя временных интервалов (формирователи импульсов) и формирователь импульсов , первый и второй входы которого соединены с входами первого и второ го интеграторов соответственно, выход - с управляющими входами формирователей временных интервалов (второго и третьего формир1ователвй импульсов), первые входы которых со динены соответственно с выходами первого и второго интеграторов, вторые входы - с выходом источника опорного напряжения, а их выходы с первым и вторым входами третьего интегратора соответственно, выход которого соединен с выходной клеммой фазового компаратора 1J . Однако этот компаратор имеет низ кую точность, которая обусловлена нестабильностью его коэффИ1Щвнта передачи из-за наличия разброса пар метров элементов (непостоянство уро ней сигналов, коэффициентов передачи или усиления, непостоянство величииы токов утечки интегрируняцих конденсаторов и т.д., в том числе изменение перечисленных параметров времени/ т.е. в процессе эксплуатации) и блоков. Целью изобретения является повышение точности работы фазового компаратора путем устранения влияния не с абильности коэффициента передачи иа уровень выходного сигнала устройч:тва. Поставленная цель достигается тем что в фазовый компаратор, содержап й три интегратора, информационные входы первого и второго из которых соединены с входнь ш клеммами устройства, источник, опорного напряжения и три формирователя импульсов, первый, и второй входы первого из которых соединены с информационными входами первого и второго интеграторов соответственно,.выход которого 41 подключен одновременно к управляющим входам второго и третьего формирователей импульсов, первые входы которых подсоединены соответственно к выходам первого и второго.интеграторов, вторые входы - одновременно к выходу источника опорного напряжения, а их выходы - к первому и второму информационным входам третьего интегратора соответственно, выход которого соединен с выходной клеммой фазового компаратора, введены элемент И-НЕ и опорный генератор импульсов, выход которого соединен с первым входом элемента И-НЕ, вто-рой и третий входы которого соединены с выходами второго и третьего формирователей импульсов, а выход с третьим информационным входом третьего интегратора, при этом первый формирователь имеет второй выход, соединеннь1Й с управляющими входами первого, второго и третьего интеграторов. На фиг. 1 приведена структурная схема фазового компаратора; на г. 2 - временные диаграммы, пояснякяцие его работу для случая, когда фаза первого сравниваемого сигнала и меньше фазы второго сигнала V. Фазовьй компаратор содержит три формирователя 1-3 импульсов, три интегратора 4-6, источник 7 опорного напряжения, опорный генератор 8 импульсов и элемент И-НЕ 9. Информационные входы интеграторов 4 и 5 соединены с входными клемг-. мами устройства. Первый и второй входы формирователя 1 импульсов соеданены с информационными входами интеграторов 4 и 5, управляющие входы которых связаны с первьт выходом формирователе; 1 импульсов. Второй выход формирователя 1 импульсов подключей к управляющем входам формиррвате/1ей 2 и 3 иьшульсов, первые входы которых подсоединешл к выходам интегратрров 4 и 5 соответственно. Выход источника 7 ойорного напряжения соединен с вторыми входами формирователей 2 и 3 импульсов, выходы которых подключены к первому и второму информацион1шм входам интегратора 6 соответственно. Выход опорного генератора 8 импульсов подсоединен к первому входу элемента И-НЕ 9, второй и третий входы которого соединены соответственно с выходами формирователей 2 и 3 импульсов.

Выход элемента И-НЕ 9 подключен к третьему информационноь у входу интегратора 6, управляющий вход которого соединен с первым выходом формирователя 1 импульсов, а выход - с выходной клеммой фазового компаратора.

Устройство работает следующим образом.

Сигналы U;| и Uji, фазы которых сравниваются между собой, поступают на первый и второй входы формирователя 1 импульсов, а также на информационные входы интеграторов 4 и 5, с выходов которых из-за нестабильности коэффициента передачи снимаются разные уровни сигналов ( 1 ) при неизменных входных сигналах:

5:

и.., К,| U|dt K, (1)

J

и,г. ч| ,

о

где i 2-3; j 1-2;

Ц и коэффи1щенты передачи интегратора 4(5) (k,, k . Равенства выражений (1) и (2) добиваются .в результате использования дополнительного сигнала U длительности t , котор й суммируется с вход ным сигналом U интегратора 6.

k Uj-tTj- (k Uj-Cj ) О (3)

(4)

Sj

5)

Uof

Преобразовав выражение (3) с учетом выражений (4) и (5), получаем:

(6)

Длительность выходного сигнала элемента 9 изменяется именно согласно закону (6).

Сигналы 10 и 11 (4№1г. 2) поступают на первые входы формирователей . 2 и 3 импульсов, на вторые входы которых подается опорное напряжение с выхода источника 7. Начало импульса на выходе формирователя 2 (3) совпадает с моментом прихода на его управлякиций вход импульса с второго

1414

выхода формирователя 1, т.е. в момент перехода с низкого уровня на высокий уровень сравниваемого сигнала меньшей фазы, а конец - с моментом равенства уровней сигналов 10, 11 и 12 На выходе опорного генератора 8 импульсов снимается импульс, начало которого синхронизировано относительно сигнала 13, а длительность

его выбирается равной длительности сигнала 14, когда козффициент передачи интегратора 4 равен исходному значению. Сигналы 14 и 15 подаются на первьй и второй входы элемента

И-НЕ 9, на выходе которого формируется сигнал 16, длительность которого равна разности длительностей сигналов 14 и 15. Выходной сигнал блока 9 подается на третий информацион7

ный вход интегратора 6 и тем самым устраняется влияние нестабильности коэффициента передачи на уровень выходного сигнала фазового компаратора. Интеграторы 4-6 сбрасываются с

помощью сигнала 17, поданного с первого выхода первого формирователя 1 импульсов, который формируется в момент перехода с высокого уровня на низкий уровень сравниваемого сигнала 18 большей фазы (U или Ug).

На фиг. 2 приведены изменения выходного сигнала фазового компарато- ; pk для трех случаев. Выходной сигнал 19 изменяется по линии а-Ь, когда коэффициент передачи равен Ц. Из-за наличия разброса qapaiMeTpoB элементов (непостоянство уровней сигналов, коэффициентов передачи или усиления, непостоянство величины

утечки интегрирукицих конденсаторов и т.д., в том числе изменение перечисленных параметров во времени, т.е. в процессе эксплуатации) коэффициент передачи устройства уменьшается до величины k и изменение выходного сигнала происходит по линии а-п, т.е. уровень выходного сигнала уменьшается при неизменных параметрах входных сигналов Ц и Uj. Подача дополнительного сигнала (при коэффициенте передачи k|3TOT сигнал равен нулю)р-длительность которого изменяется согласно выражению (6), вос танавливает уровень выходного сигнала

до первоначального значения. Выходной сигнал фазового компаратора в этом случае изображается линией S - m - Ь.

Фазовый компаратор может работать 8 трех режимах.

Использование изобретения для сравнения по фазе двух сигналов позволяет повысить точность работы устройства по сравнению с базовым объектом на 2-4%, при зтом расширяется область его применения.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Фазовый компаратор | 1979 |

|

SU845279A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-05-23—Публикация

1982-12-20—Подача