не компенсируется динамическая ошибка интегратора, которая может быть значительной. Кроме того, известное устройство не выдерживает длительной работы.

Цель изобретения - повышение точности интегрирования путем компенсации не только статической, но и динамической ошибки интегрирования, и расширение диапазона.

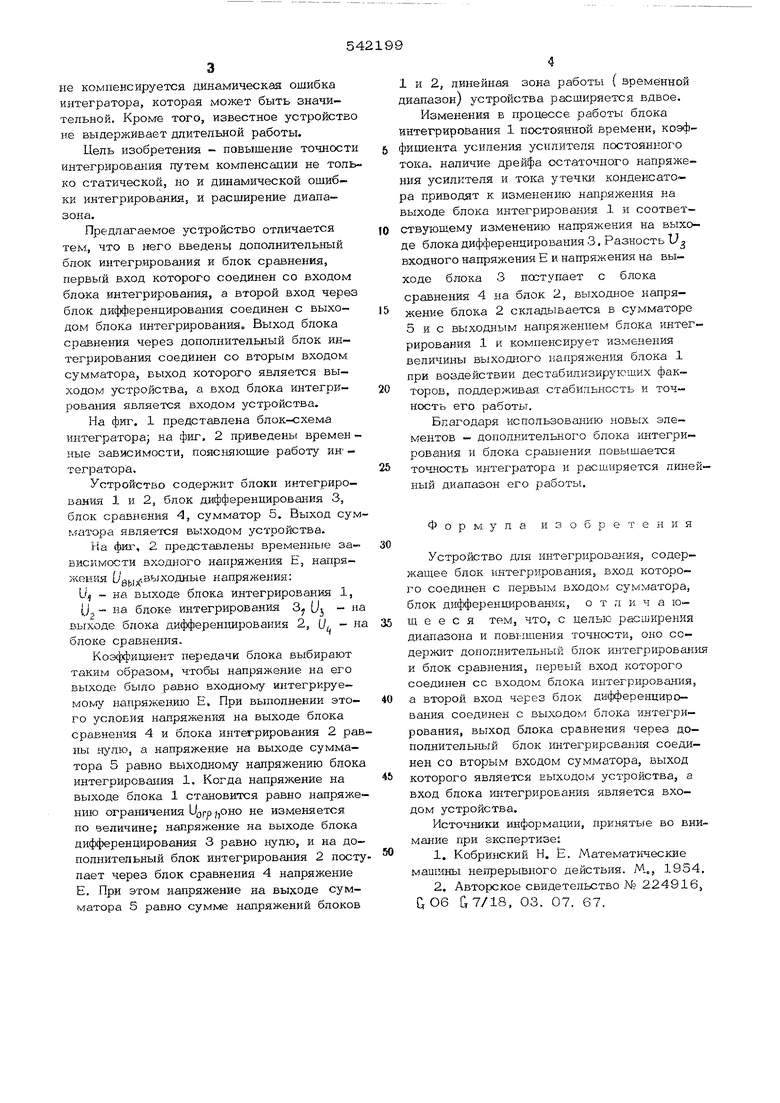

Предлагаемое устройство отличается тем, что в него введены дополнительный опок интегрирования и блок сравнения, первый вход которого соединен со входом блока интегрирования, а второй вход через блок дифференцирования соединен с выходом блока интегрирования,, Выход блока сравнения через дополнительный блок интегрирования соединен со вторым входом сумматора, выход которого является выходом устройства, а вход блока интегрирования является входом устройства.

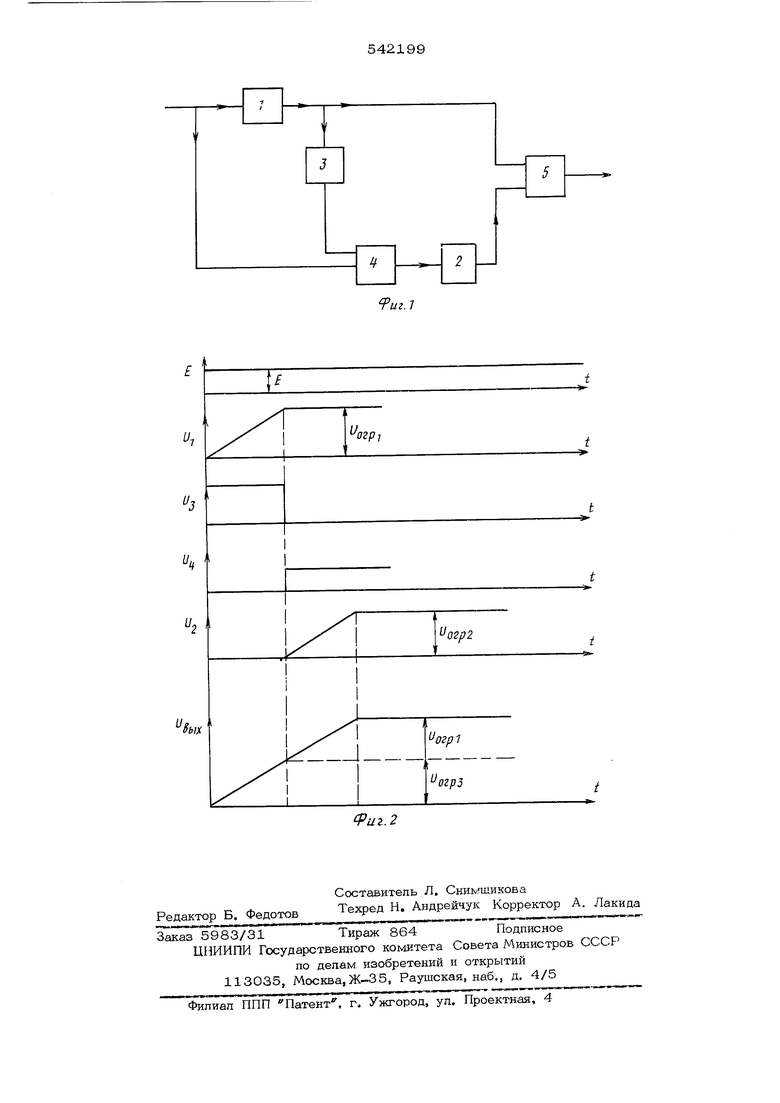

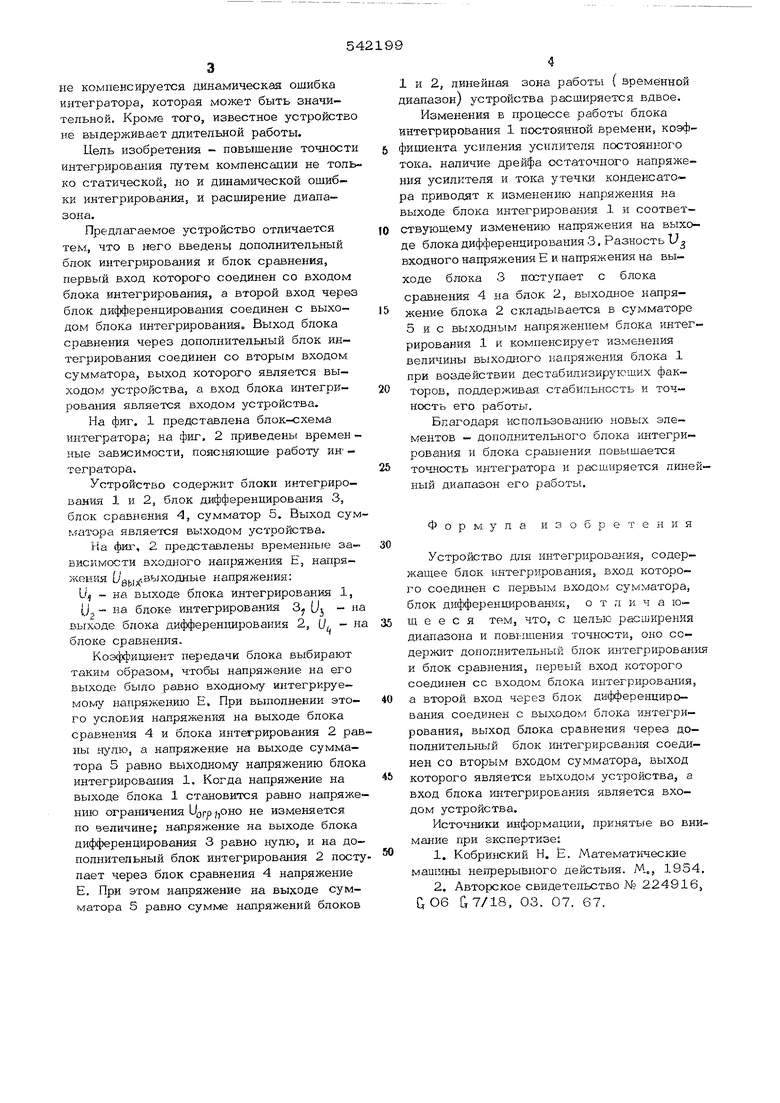

На фиг. 1 представлена блок-схема интегратора; на фиг. 2 приведены времен ные зависимости, поясняющие работу ин тегратора.

Устройство содержит блохи интегрирования 1 и 2, блок дифференцирования 3, блок сравнения 4, сумматор 5. Выход сумMciTOpa является выходом устройства.

На фю, 2 представлены временные зависимости входного напряжения Е, напряжения (70|.|.(-,выходные напряжения: L, на выходе блока интегрирования 1, и - на блоке интегрирования 3j (Jj - на выходе блока дифференцирования 2, (J, н блоке сравнения.

Коэффищюнт передачи блока выбирают таким образом, чтобы напряжение на его выходе было равно входному интегрируе- MOjvry напряжению Е. При выполнении этого условия напряжения на выходе блока сравнения 4 и блока интегрирования 2 равны 1-р,лю, а напряжение на выходе сумматора 5 равно выходному напряжению блока интегрирования 1, Когда напряжение на выходе блока 1 становится равно напряжению ограничения Uopp;,oHo не изменяется по величине; напряжение на выходе блока дифференцирования 3 равно , и на дополнительный, блок интегрирования 2 поступает через блок сравнения 4 напряжение Е. При этом напряжение на выходе сумматора 5 равно сумме напряжений блоков

1 и 2, линейная зона работы { временной диапазон) устройства расширяется вдвое.

Изменения в процессе работы блока интегрирования 1 постоянной времени, коэффициента усиления усилителя постоянного тока, наличие дрейфа остаточного напряжения усилителя и тока утечки, конденсатора приводят к изменению напряжения на выходе блока интeгpиpoвшiия 1 и соответствующему изменению напряжения на выходе блока дифференцирования 3. Разность U входного напряжения Е и напряжения на выходе блока 3 поступает с блока сравнения 4 на блок 2, выходное напряжение блока 2 складывается в сумматоре 5 и с выходным напряжением блока интегрирования 1 и компенсирует изменения величины выходного напряжения блока 1 при воздействии дестабилизирующих факторов, поддерживая стабильность и точность его работы.

Благодаря использованию новых элементов - дополнительного блока интегрирования и блока сравнения повышается точность интегратора и расширяется линейный диапазон его работы.

Ф о р м. у п а изобретения

Устройство для интегрирования, содержащее блок интегрирования, вход которого соединен с первым входом сумматора, блок дифференцирования, о т л и ч а ю-

щ е е с я тем, что, с целью расширения диапазона и повышения точности, оно содержит дополнительный блок интегрирования и блок сравнения, первый вход которого соединен ее входом, блока интегрирования,

а второй вход через блок дифференцирования соединен с выходом блока интегрирования, выход блока сравнения через дополнительный блок интегрирования соединен со вторым входом сумматора, выход

которого является выходом устройства, а вход блока интегрирования является входом устройства.

Источники информации, принятые во внимание при экспертизе

1. Кобринский Н. Ё. Математические

машины непрерывного действия. М., 1954. 2. Авторское свидетельство № 224916, С, 06 &7/18, 03. 07. 67.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой интегратор | 1982 |

|

SU1037280A1 |

| ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНЫЙ РЕГУЛЯТОР С ОГРАНИЧЕНИЯМИ ВЫХОДНЫХ СИГНАЛОВ | 1999 |

|

RU2156992C1 |

| СПОСОБ И УСТРОЙСТВО ДВУХТАКТНОГО ИНТЕГРИРОВАНИЯ | 2012 |

|

RU2521305C2 |

| Устройство для импульсного регулирования | 1977 |

|

SU697967A1 |

| ИНТЕГРАТОР | 1990 |

|

RU2020580C1 |

| СПОСОБ И УСТРОЙСТВО ДВУХТАКТНОГО ИНТЕГРИРОВАНИЯ С КОМПЕНСАЦИЕЙ ПОГРЕШНОСТЕЙ | 2013 |

|

RU2523939C1 |

| Устройство для определения частотных характеристик систем автоматического управления и регулирования | 1985 |

|

SU1339499A2 |

| Аналого-цифровой интегратор | 1980 |

|

SU866563A1 |

| ПРОПОРЦИОНАЛЬНО-ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНЫЙ РЕГУЛЯТОР С ОГРАНИЧЕНИЯМИ ВЫХОДНЫХ СИГНАЛОВ | 1998 |

|

RU2120654C1 |

| СПОСОБ ЧАСТОТНОЙ МОДУЛЯЦИИ КОЛЕБАНИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2015 |

|

RU2595638C1 |

Авторы

Даты

1977-01-05—Публикация

1975-07-01—Подача