Предлагаемое изобретение относится к радиолокации и может быть использовано в импульсных радиолокационных станциях для устранения приема эхосигналов, приходящих по боковым лепесткам (БЛ) диаграммы направленности (ДНА).

В настоящее время в РЛ приемниках в качестве канала обнаружения широко используется помехозащищенная типовая схема обработки, состоящая из последовательно соединенных “ограничителя-оптимального фильтра-детектора-некогерентного накопителя” [3]. Данная схема обработки сигналов является одноканальной и обеспечивает достаточно хорошее качество стабилизации уровня ложных тревог или приеме на фоне произвольного вида помех, особенно при включении на ее выходе специальных схем, осуществляющих дополнительную стабилизацию уровня ложных тревог [4].

Данное устройство является наиболее близким по технической сущности к заявляемому объекту и выбрано в качестве прототипа.

Однако применение такой обработки не исключает прием ложных сигналов по БЛ ДН, что приводит к неоднозначности определения азимутального направления на цель, т.е. к увеличению общего числа уровня ложных тревог. В связи с этим представляется актуальным рассмотрение возможности улучшения качества стабилизации уровня ложных тревог в одноканальной типовой схеме обработки эхосигналов за счет исключения приема эхосигналов по боковым лепесткам диаграммы направленности антенной системы.

Целью настоящего изобретения является улучшение подавления приема эхосигналов по боковым лепесткам диаграммы направленности антенны, за счет снижения чувствительности приема эхосигналов по боковым лепесткам.

Поставленная цель достигается тем, что в известной схеме, взятой за прототип, содержащей последовательно соединенные ограничитель, оптимальный фильтр, детектор, некогерентный накопитель, устройство ВПС и ключ, управляемый вход которого соединен с управляющим выходом ВПС, выход является выходом всего устройства. Согласно изобретению ко входу ограничителя подключен выход блока подавления приема ПБЛ ДНА, управляемый вход которого соединен с выходом блока формирования управляющего напряжения, а вход последнего подключен к основному входу блока подавления ПБЛ ДНА и является входом всего устройства.

Схема, взятая за прототип, полностью защищена авторским свидетельством №266965 от 04.01.88 г.

Сущность изобретения заключается в выделении в линейной части приемника сигналов, принимаемых в главном луче основного канала (ОК) ДНА, и формировании через обзор по этим сигналам управляющего напряжения в виде азимутальных стробов, протяженность которых зависит от амплитуды сигнала в области главного луча ОК. Это управляющее напряжение изменяет чувствительность приема эхосигналов таким образом, чтобы максимально возможные азимутальные боковые лепестки от "сильных" сигналов не обнаруживались на выходе приемного устройства.

Сопоставительный анализ с прототипом показывает, что заявленное приемное устройство содержит блоки подавления приема по БЛ ДН антенны и формирования управляющего напряжения, что соответствует критерию изобретения "новизна".

Сопоставительный анализ с другими техническими решениями показал, что отсутствуют технические решения со сходными признаками, отличающими заявленное техническое решение от прототипа, что позволяет сделать вывод о соответствии технического решения критерию изобретения "существенные отличия".

Изложенная сущность изобретения будет понятна из приведенного описания и графических материалов.

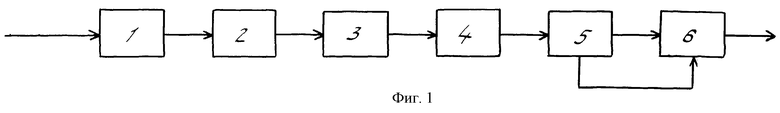

Нa фиг.1 представлена структурная схема типового РЛ приемника, выбранного в качестве прототипа.

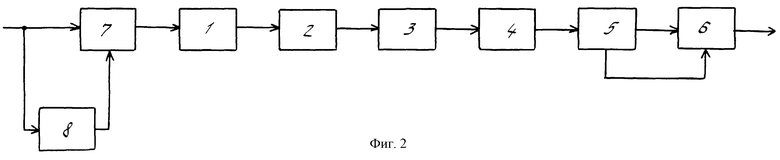

На фиг.2 приведена структурная схема заявленного устройства по п.1 формулы изобретения.

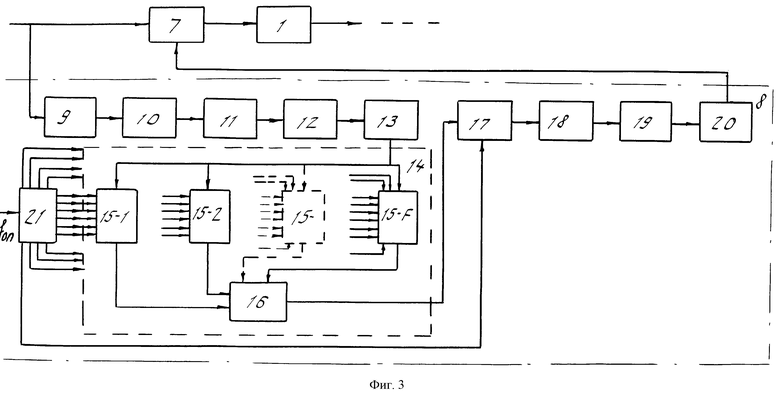

На фиг.3 приведена функциональная схема заявленного устройства по п.1 формулы изобретения.

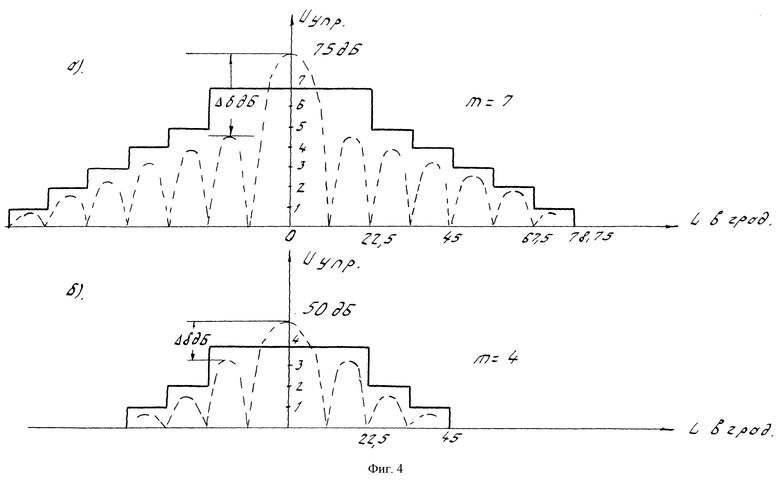

На фиг.4 представлены импульсные характеристики заявленного устройства.

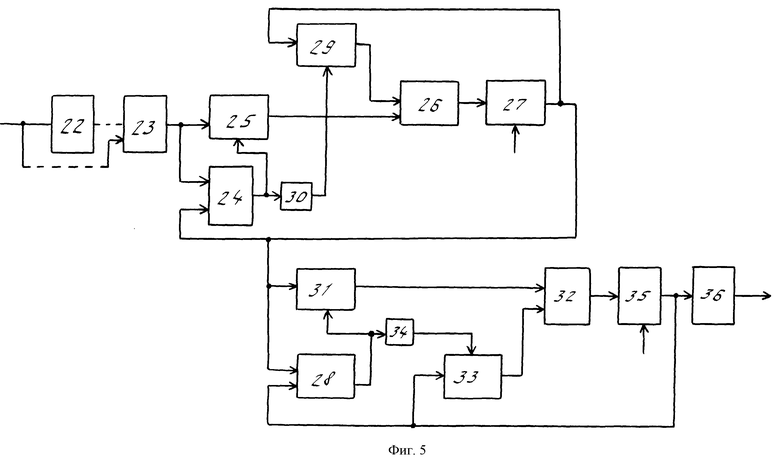

На фиг.5 приведена функциональная схема части заявленного устройства по п.2 формулы изобретения.

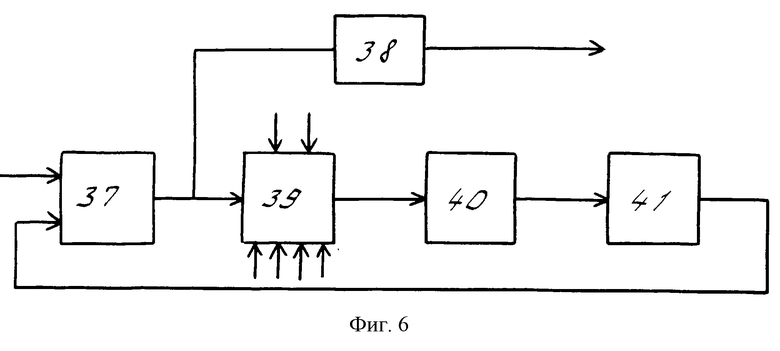

На фиг.6 приведена функциональная схема одного канала скоростного фильтра, заявленного устройства по п.3 формулы изобретения.

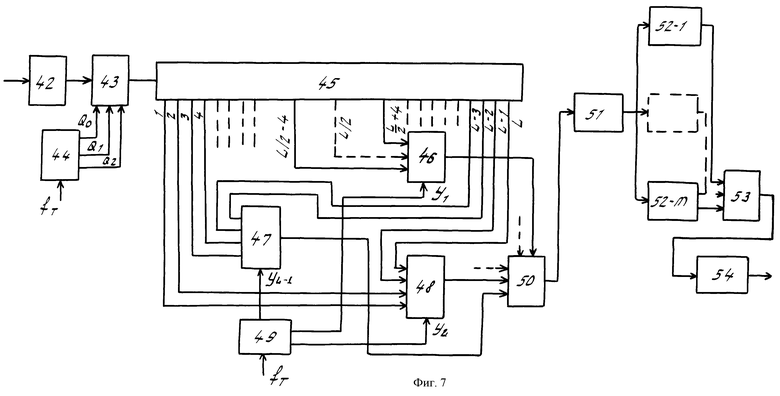

На фиг.7 приведена структурная схема устройства формирования азимутальных стробов по п.4 формулы изобретения.

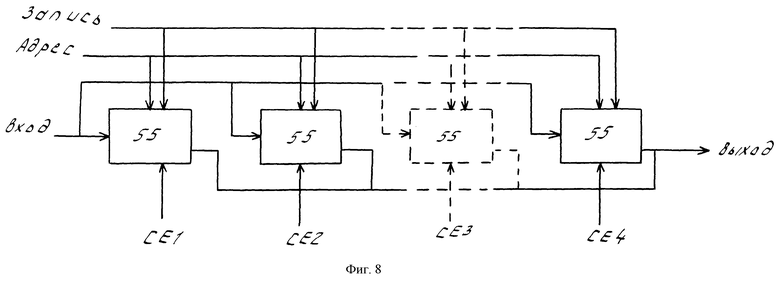

На фиг.8 приведена функциональная схема одного из вариантов межобзорной памяти заявленного устройства.

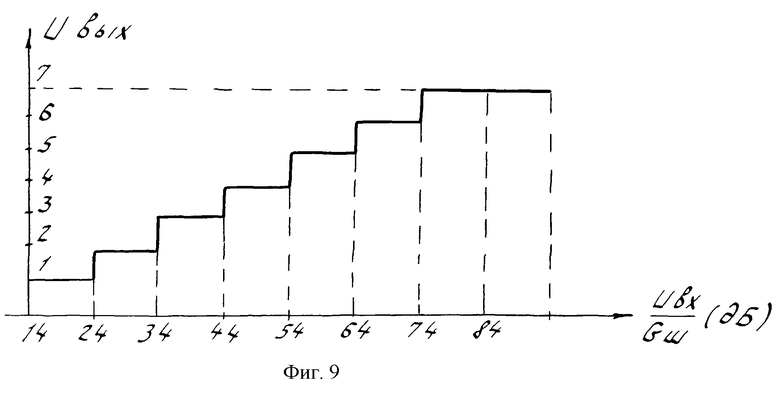

На фиг.9 представлена амплитудная характеристика.

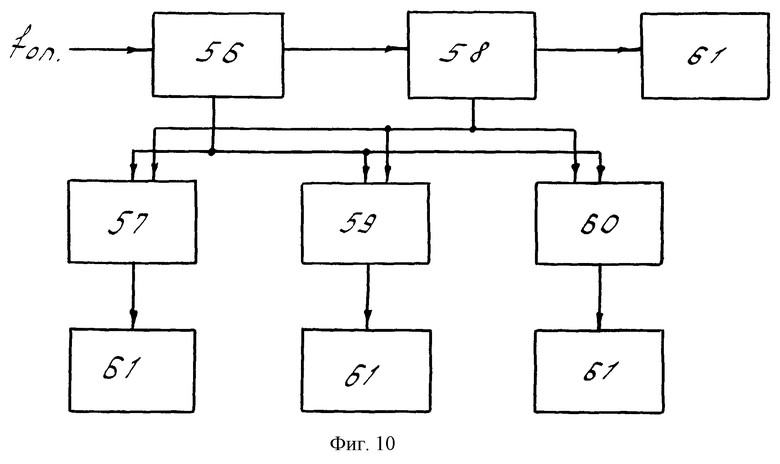

На фиг.10 приведена структурная схема хронизатора устройства.

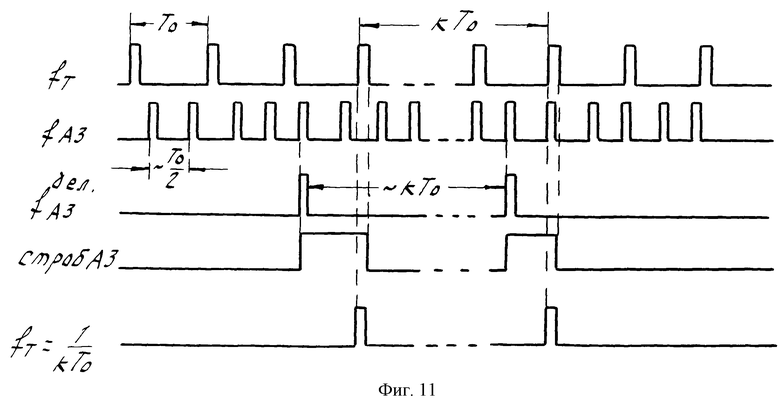

На фиг.11 изображена диаграмма, поясняющая синхронизацию время-азимут.

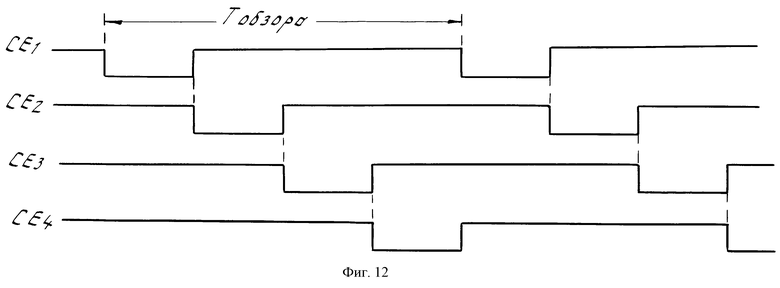

На фиг.12 приведена диаграмма напряжения для управления работой с одним из видов памяти, изображенной на фиг.8.

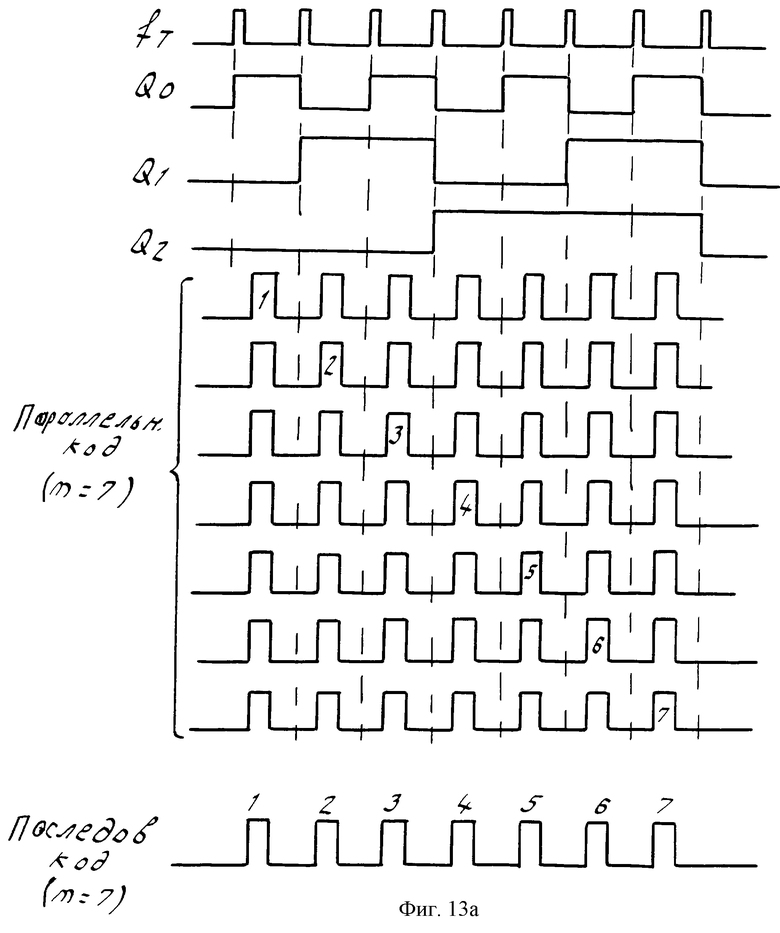

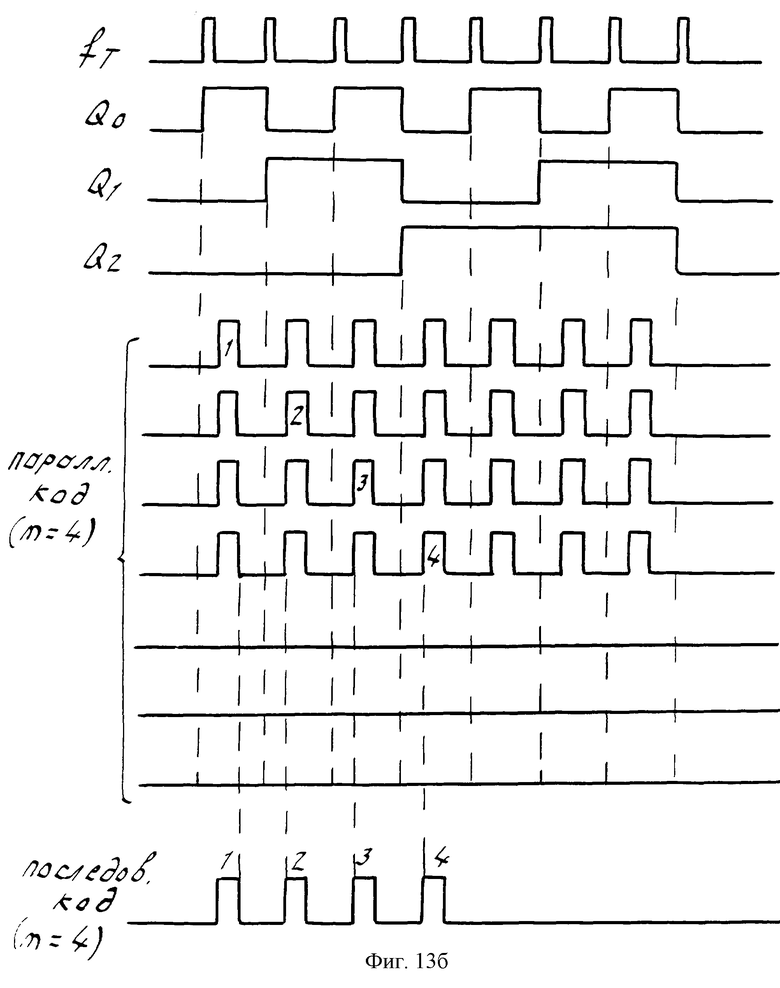

На фиг.13 изображены диаграммы преобразования входного параллельного кода в последовательный.

На фиг.14 приведены диаграммы, поясняющие принцип формирования сложного управляющего напряжения заявленного устройства.

На графических материалах и в тексте описания приняты следующие обозначения:

1 - ограничитель;

2 - оптимальный фильтр;

3 - детектор;

4 - некогерентный накопитель;

5 - устройство ВПС;

6 - ключ;

7 - блок подавления приема по БД ДН;

8 - блок формирования управляющего напряжения;

9 - нелинейный элемент;

10 - оптимальный фильтр;.

11 - детектор;

12 - некогерентный накопитель;

13 - азимуталъно-дальностный интегратор;

14 - устройство межобзорной обработки сигналов;

15 - скоростной фильтр;

16 - схема отбора максимального значения;

17 - устройство формирования азимутальных стробов;

18 - линия задержки 1(ЛЗ1);

19 - ЛЗ2;

20 - буферное устройство;

21 - хронизатор;

22 - ЛЗ2;

23 - сумматор;

24 - схема сравнения;

25 - ключ;

26 - схема объединения;

27 - регистр с обнуляющим входом;

28 - схема сравнения;

29 - ключ;

30 - инвертор;

31 - ключ;

32 - схема объединения;

33 - ключ;

34 - инвертор;

35 - ЛЗ3;

36 - регистр;

37 - сумматор;

38 - регистр;

39 - ЛЗ4;

40 - регистр;

41 - умножитель;

42 - преобразователь кода;

43 - коммутатор;

44 - хронизатор;

45 - ЛЗ5;

46, 47, 48 - ключи;

49 - хронизатор;

50 - схема объединения;

51 – ЛЗ1;

52 - ЛЗ6;

53 - регистр;

54 - преобразовтель кода;

55 - ЛЗ4;

56 - делители частоты;

57 - схема формирования адресных сигналов;

58 - формирователь временных меток;

59 - схема формирования последовательностей управляющих импульсов;

60 - схема "привязки" азимутальных сигналов к тактовым;

61 - выходные каскады.

В схеме по а.с. 266965, содержащей последовательно соединенные ограничитель 1, оптимальный фильтр 2, детектор 3, некогерентный накопитель 4, устройство ВПС 5, ключ 6, управляемый вход которого соединен с управляющим выходом ВПС, а выход ключа является выходом всего устройства, ко входу ограничителя 1 подключен выход блока ПБЛ ДНА 7, управляемый вход которого соединен с выходом блока формирования управляющего напряжения 8, а вход последнего подключен к основному входу блока ПБЛ ДНА 7 и является входом всего устройства.

Один из вариантов выполнения блока формирования управляющего напряжения 8 (фиг.3) содержит последовательно соединенные нелинейное устройство 9, оптимальный фильтр 10, детектор 11, некогерентный накопитель 12, азимутально-дальностный интегратор 13, устройство межобзорной обработки сигналов 14, представляющее набор параллельно включенных F-скоростных фильтров 15, выходы которых соединены с соответствующими входами схемы отбора максимального сигнала 16, выход которой является выходом устройства межобзорной обработки сигналов 14, формирователь азимутальных стробов 17, две линии задержки 18, 19, буферное устройство 20, выход которого соединен с управляемым входом блока 7, и хронизатор 21, управляющие выходы которого соединены с управляемыми входами: азимутально-дальностного интегратора 13, устройства межобзорной обработки сигналов 14, формирователя азимутальных стробов 17, хронизаторов 44, 49, линий задержки 18, 19, и имеющий вход для подключения опорной частоты РЛС (fоп). На фиг.10 приведена типовая структурная схема хронизаторов 21, 44, 49, которая отображает функции хронизации и управления устройством.

Из опорной частоты (fоп) путем деления ее счетчиком 56 и дешифрирования в устройстве 58 формируются все временные метки, необходимые для работы регистров и ОЗУ с любыми заданными временными интервалами.

Адресные сигналы для обращения к ячейкам памяти формируются делением определенных временных меток счетными устройствами 57. Путем деления на большие коэффициенты и дешифрирования ранее поделенных сигналов формируются последовательности управляющих импульсов для межобзорной (медленной) работы каналов межобзорных накопителей сигналов 59. Все сигналы хронизатора подаются к потребителям через выходные буферные каскады 61.

В хронизаторе осуществляется синхронизация двумерных сигналов - времени-азимута схемой привязки азимутальных и тактовых импульсов 60. Азимутальные метки формируются путем механического вращения антенны и являются нестабильными, вследствие чего и требуется вышеуказанная схема.

Сущность изобретения не изменится, если отдельные устройства блока 8 будут выполнены иначе, например, с применением микропроцессорной техники.

Азимутально-дальностный интегратор 13 (фиг.5) выполнен в виде последовательно соединенных первой линии задержки 22, сумматора 23, второй вход которого соединен со входом линии задержки 22 и является входом устройства, а выход - с одним из входов первой схемы сравнения 24 и с входом первого ключа 25; первой схемы объединения 26, один из входов которой соединен с выходом первого ключа 25, управляемого выходом первой схемы сравнения 24; регистра с обнуляющим входом 27, выход которого подключен к одному из входов первой (24) и второй (28) схем сравнения и ко входу второго ключа - 29, управляемый вход которого соединен с выходом первой схемы сравнения 24 через инвертор 30, а выход ключа 29 подключен ко второму входу схемы объединения 26; третьего ключа 31, управляемого выходом второй схемы сравнения 28; второй схемы объединения 32, второй вход которой соединен с выходом четвертого ключа 33, управляемый вход которого через инвертор 34 соединен с выходом второй схемы сравнения 28; второй линии задержки 35, выход которой подключен к входу четвертого ключа 33 и к второму входу второй схемы сравнения 28; и регистра 36, выход которого является выходом устройства 13 и подключен ко входу устройства межобзорной обработки сигналов 14.

Устройство межобзорной обработки 14 выполнено в виде набора F-параллельных каналов, входы которых объединены (фиг.3) и являются входом устройства 14, при этом каждый из каналов устройства межобзорной обработки сигналов (фиг.6) содержит последовательно соединенные сумматор 37, выход которого через первый регистр 38 является выходом одного из каналов, линию задержки 39, регистр 40, умножитель 41, выход которого подключен к одному из входов. сумматора 37, другой вход которого является входом канала, а выходы всех F-каналов объединяются схемой отбора максимального сигнала 16 (фиг.3), причем выход последней является выходом устройства 14 и подключен ко входу формирователя азимутальных стробов 17.

Формирователь азимутальных стробов 17 (фиг.7) содержит первый преобразователь кода 42, выход которого подключен к входу коммутатора 43, причем управляемый вход последнего подсоединен к выходу хронизатора 44, управляемым хронизатором 21, а выход - к входу первой линии задержки с L-отводами 45, подключенными соответствующим образом к ключам 46, 47, 48 (все ключи не показаны, всего ключей L/4-1), управляемые входы которых подсоединены к выходу хронизатора 49, являющегося частью хронизатора 21, так что выходы всех ключей подключены к входам схемы объединения 50, выход которой через вторую линию задержки 51 соединен со всеми входами третьей линии задержки 52, раздельные выходы которой через регистр 53 подключены к входу второго преобразователя кода 54, выход которого является выходом устройства 17, который через последовательно соединенные линии задержки (18, 19) и буферное устройство 20 (фиг.3) подключен к управляющему входу блока подавления приема по БЛ ДНА (7), выход которого является выходом блока 7.

Блок подавления приема по БЛ ДНА 7 представляет собой схему сравнения и может быть выполнен на базе арифметическо-логических устройств (АЛУ), например, 530ИП3, I33ИП3.

Принцип подавления приема по БЛ ДНА в одноканальном помехозащищенном приемнике заключается в следующем. В блоке формирования управляющего напряжения 8 осуществляется выделение "сильных" сигналов. Область "сильных" сигналов определяется соотношением между уровнем боковых лепестков и главным лучом ДНА (на прием-передачу), который определяет динамический диапазон сигналов (Δ В, дБ), допускающий однозначное измерение азимутальной координаты.

Сигналы, превышающие этот диапазон, являются "сильными", и, если не принять дополнительных мер, произойдет неоднозначное определение направления на цель. Для ослабления сигналов, принимаемых по БЛ, сигналы попадают в блок 8, где они запоминаются на время Т обзора и накапливаются в течение N обзоров. По этим сигналам вырабатывается управляющее напряжение в форме симметричной прямоугольно-ступенчатой пирамиды (см. фиг.4), совмещаемое по времени и длительности с приходящим эхосигналом. Это напряжение пропорционально уровню "сильных" сигналов и предназначено для изменения порога чувствительности в блоке 7, при этом порог остается равным нулю для "слабых" сигналов, т.е. сигналов, не превышающих динамический диапазон Δ В, дБ, по отношению к уровню собственных шумов. "Слабые" сигналы проходят на оптимальный фильтр (ОФ) 2 канала обнаружения без изменения, т.е. чувствительность приема по ним не изменяется.

Достоинством данного метода подавления приема эхосигналов по БЛ является использование амплитудной информации эхосигналов, принимаемых в области главного луча ДНА приемного канала обнаружения.

Данная информация наиболее устойчива к эффектам многопутного распространения радиоволн, обусловленных влиянием рельефа местности, где расположена РЛС (наиболее сильно из-за эффектов многопутного распространения радиоволн искажаются БЛ ДН антенной системы, при этом главный луч практически не искажается); при обнаружении на фоне активных шумовых помех, когда из-за наличия адаптивных схем компенсации активных помех происходит искажение ДН БЛ в направлении на постановщик помех. Благодаря данному достоинству предлагаемое устройство будет устойчиво работать при обнаружении целей на фоне активных помех и не искажать (вносить потери в отношение сигнал/шум) прием по относительно слабым эхосигналам (принимаемым без азимутальных БЛ).

Структурная схема предлагаемого устройства показана на фиг.3. Сигналы в данном приемном устройстве проходят следующим образом. Сигналы с выхода антенной системы через типовое приемное устройство, выходом которого при цифровой реализации предлагаемого устройства будет являться выход последовательно соединенных фазового детектора и АЦП [7], поступают на вход параллельно включенных блока формирования управляющего напряжения 8 и блока подавления приема по БЛ ДНА 7.

Блок формирования управляющего напряжения 8 включает в себя канал оптимальной временной обработки, содержащий последовательно соединенные нелинейное устройство 9, оптимальный фильтр 10, детектор 11 и некогерентный накопитель 12. Данная схема структурно совпадает с типовой схемой обработки сигналов, состоящей из последовательно соединенных нелинейного элемента 9 - оптимального фильтра 10 [6]. Отличительной особенностью от традиционного обнаружителя является то, что нелинейный элемент 9 на входе оптимального фильтра 10 имеет специфическую амплитудную характеристику, которая пропускает для последующей обработки "сильные" сигналы, амплитуда которых достаточна для приема по БЛ ДНА. При этом число дискретных уровней по амплитуде, которое соответствует числу уровней изменения чувствительности, в нелинейном элементе 9 выбирается таким образом, чтобы на выходе канала оптимальной временной обработки уровень несинхронных помех был незначительным и не приводил к нарушению работоспособности всего устройства вследствие ложных срабатываний. Уровень уменьшения несинхронных помех на выходе блока определяется базой сложного зондирующего сигнала М, используемого в РЛС, и числом эффективно накапливаемых q-импульсов в некогерентном накопителе 12. Коэффициент уменьшения уровня несинхронной помехи равен α =1/M· q.

Величина данного коэффициента ограничивает сверху максимальный динамический диапазон подавления боковых лепестков, в противном случае схема не будет обладать помехоустойчивостью. Для обзорных РЛС величина коэффициента α лежит в пределах 30... 45 дБ, что с учетом уровня БЛ на прием-передачу - 30 дБ (наиболее характерное значение для обзорных РЛС) означает, что предлагаемое устройство обработки позволяет уменьшить уровень приема по БЛ до 60... 75 дБ. Данная величина подавления приема по БЛ позволяет осуществлять однозначное определение азимутального направления на цели, имеющие достаточно большие эффективные площади рассеивания (ЭПР), таких как самолеты типа АНТ-22. Таким образом, в предложенном устройстве осуществляется достаточно эффективное подавление приема эхосигналов по БЛ и при приеме эхосигналов на фоне несинхронных помех.

Импульсная характеристика некогерентного накопителя 12 может быть произвольная, в зависимости от конкретной реализации, например, он может быть выполнен в виде трансверсального фильтра, весовые коэффициенты в котором соответствуют ДН главного луча, либо более простым квазиоптимальным экспоненциальным накопителем [5]. На практике наиболее рационально применить квазиоптимальный экспоненциальный накопитель, допускающий наиболее простую техническую реализацию, поскольку в данном канале осуществляется обработка сигналов, для которых отношение сигнал/шум существенно больше единице и потери по слабым сигналам (т.е. точность оценки амплитуды сигнала) существенного значения не имеет.

С выхода некогерентного накопителя 12 сигналы поступают на вход азимутально-дальностного интегратора 13, который по функциональному значению эквивалентен ФНЧ (фильтру низкой частоты), поскольку он предназначен для сужения спектра принимаемых колебаний до ширины спектра элемента разрешения РЛС, определяемый как произведение ширины ДН главного луча на длительность огибающей зондирующего сигнала. В результате принимаемые эхосигналы на выходе экспоненциального накопителя 12 с помощью азимутально-дальностного интегратора 13 можно преобразовать в последовательность амплитудных выборок, частота дискретизации которых по азимуту равна 1/К· То, а по дальности 1/τ , где

К - число элементов разрешения РЛС по дальности и азимуту;

То - период тактов зондирования;

τ - длительность элемента разрешения по дальности основного канала обнаружения.

При этом в пределах элемента разрешения ФН4 запоминается максимальное значение амплитуды эхосигналов. Далее эти выборки накапливаются в F-межобзорных скоростных фильтрах 15 в течение N обзоров для формирования более устойчивого, независимого от флюктуации ЭПР целей от обзора к обзору, управляющего напряжения. Число межобзорных скоростных фильтров 15 выбирается исходя из величины максимальной радиальной составляющей скорости цели и элемента разрешения по дальности.

Для уменьшения объема вычислений целесообразно элемент разрешения по дальности в фильтрах несколько увеличивать. Предельная величина увеличения равна длительности огибающей зондирующих сигналов, поскольку этой длительностью определяется элемент разрешения по дальности в типовом канале обнаружения, содержащем оптимальный фильтр 2. Выходы всех скоростных фильтров 15 объединяются схемой отбора по максимуму 16.

В схеме отбора максимального значения сигнала 16 осуществляется операция интегрирования скоростной информации путем выбора максимального значения напряжения на выходе фильтров 15, которое поступает на схему формирования азимутальных стробов 17.

Схема формирования азимутальных стробов 17 представляет собой линейный фильтр, имеющий относительно центра симметричную импульсную характеристику, длительность которой равна протяженности азимутальных боковых лепестков, пропорциональных числу амплитудных градаций в соответствии с амплитудой сигналов на входе приемного устройства. Сигналы в азимутальном фильтре 17 задерживаются по азимуту. Для совмещения управляющего напряжения с эхосигналами в следующем обзоре на выходе схемы формирования азимутальных стробов 17 включены линии задержки (18, 19). С выхода линий задержек 18, 19 сигналы поступают в выходное буферное устройство 20, которое преобразует дискретные выборки, обрабатываемые в устройстве формирования управляющего напряжения 8, в более плавные, шаг дискретизации которых по азимуту совпадает с тактовой частотой РЛС (То), а по дальности - с частотой дискретизации АЦП.

Схема азимутально-дальностного интегратора 13 приведена на фиг.5.

Для уменьшения потерь амплитудной информации при переходе к квантам большей длительности (α τ кв) в схеме интегрирования применено арифметическое суммирование прямых и задержанных на τ кв, 2τ кв и (α -1)· τ кв сигналов сумматором 23 (где 1<α <M). При этом для значительного сокращения объема аппаратуры на входе сумматора 23 предусмотрено устройство нормирования разрядности, на схеме не показано, т.к. при цифровой обработке оно может быть выполнено путем отбрасывания младших разрядов (смещения разрядной сетки) либо известным способом с помощью последовательно включенных схем сравнения и коммутаторов, управляемых знаками переноса схем сравнения, которые являются выходом схемы нормирования. На вторые входы схем сравнения поданы соответствующие преобразованным квантам амплитуды коды. Структурное построение этой схемы и преобразование в ней сигналов аналогично преобразованию сигналов в АЦП.

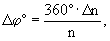

Сигнал нормированной разрядности параллельно подается на первый ключ 25 и на один из входов первой схемы сравнения 24, знак переноса которой управляет ключом 25, а через первый инвертор 30 - вторым ключом 29, на вход которого и на второй вход схемы сравнения 24 поступает сигнал с выхода первого регистра 27, который устанавливается в нулевое состояние через каждые α τ кв. Выходы обоих ключей 25 и 29 через буферную схему объединения 26 связаны со входом регистра 27. При этом в регистр 27 всегда записывается максимальный из α τ кв сигнал: прямого, задержанного на τ кв, 2τ кв и т.д. (α -1)· τ кв, т.к. схема сравнения 24 подключает на вход схемы объединения 26 всегда максимальный из сравниваемых сигнал. После установки регистра 27 в нулевое состояние процесс отбора максимального сигнала повторяется. С регистра 27 сигналы с τ дискрета=α τ кв поступают на устройство интегрирования по азимуту, состоящее из тех же элементов, что и описанное выше. Отличие состоит в том, что промежуточная память выполнена не на регистре на время τ кв, с обнуляющим входом (27), а на линии задержки 35, представляющее собой оперативное запоминающее устройство (ОЗУ) на время такта зондирования То. Установка в нулевое состояние линии задержки 35 происходит через К· То, что составляет по азимуту сектор в градусах, равный:

где К - целое число;

n - количество азимутальных меток за обзор;

Δ n - количество азимутальных меток за К· То тактов.

На выход линии задержки 35 проходят максимальные сигналы из КТо тактов, после чего ОЗУ 35 устанавливается в нулевое состояние и отбирается максимальная по амплитуде информация из следующего Δ j ° сектора. На втором регистре 36 после ОЗУ 35 амплитудная информация сохраняется в течение То тактов на каждом интегрированном (α τ кв) элементе дальности.

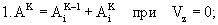

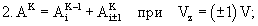

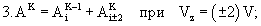

С азимутально-дальностного интегратора 13 двоичный код поступает параллельно на F-межобзорных скоростных фильтров 15, которые выделяют эхо сигналы от целей в зависимости от величины и направления радиальной составляющей скорости следующим образом:

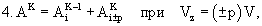

Vz=O; Vz=(± 1)V; Vz=(± 2)V; Vz=(± р)V; V=Δ D/To; p=1,2... и т.д.,

где Vz - радиальная составляющая скорости движения цели;

V - эффективная полоса пропускания скоростных фильтров по скорости;

Δ D - элемент разрешения по дальности на выходе азимутально-дальностного интегратора.

Структурная схема одного из фильтров 15 представлена на фиг.6.

Каждый скоростной фильтр 15 представляет собой экспоненциально-весовой межобзорный накопитель, состоящий из сумматора 37, цепи обратной связи с задержкой на время одного обзора Тоб в линии задержки 39 и первом регистре 40 и умножителя 41 с  Задержка на Тоб выполнена на ОЗУ 39 с объемом памяти, который определяется по формуле:

Задержка на Тоб выполнена на ОЗУ 39 с объемом памяти, который определяется по формуле:

где D - величина зоны действия БЛ, км;

Δ j - величина дискрета по азимуту, град;

П - объем памяти, килобайт.

Рабочие такты межобзорной памяти (запись - считывание информации) происходят с частотой 1/К· То. За время обзора количество таких тактов составит Тобз/К· То.

Эти рабочие такты задаются азимутальными метками, чтобы не было пропусков по азимуту в работе межобзорной памяти. Обеспечение синхронности работы фильтра обеспечивается специальной схемой привязки ("прошивки") тактовой частоты зондирования к азимутальным меткам, выполненной в хронизаторе 21. [7] Временная диаграмма работы схемы привязки приведена на фиг.11. Частота азимутальных импульсов fАЗ делится на определенный коэффициент, задающий частоту рабочих тактов и равна 1/K· То межобзорной памяти.

Полученный азимутальный импульс с пониженной частотой  включает триггер, сигнал с которого (строб АЗ) вместе с тактовой частотой fT поступает на схему совпадения, на выходе которой получается синхронный с азимутом тактовый сигнал частоты повторения

включает триггер, сигнал с которого (строб АЗ) вместе с тактовой частотой fT поступает на схему совпадения, на выходе которой получается синхронный с азимутом тактовый сигнал частоты повторения  Последний также обнуляет триггер, подготовив его для приема следующего импульса. [9].

Последний также обнуляет триггер, подготовив его для приема следующего импульса. [9].

Межобзорная память - основной элемент межобзорного экспоненциального накопителя скоростных фильтров устройства, накапливающих эхосигналы по всем элементам дальности (γ τ кв) за N обзоров. Максимальный эхосигнал накопится в том скоростном фильтре, который является оптимальным для эхосигналов, обладающих заданной радиальной скоростью.

Память для скоростных межобзорных фильтров 39 может быть выполнена на ОЗУ серии 132РУI. Управление памятью осуществляется с хронизатора 21, формирующего необходимые стандартные сигналы для ОЗУ, "запись-считывание", адресные, "выбор кристалла". Алгоритм работы межобзорной памяти фильтров следующий:

где  - амплитудная информация с i-й ячейки дальности в предыдущем обзоре;

- амплитудная информация с i-й ячейки дальности в предыдущем обзоре;

- амплитудная информация с (i±2)-й ячейки дальности в текущем обзоре;

- амплитудная информация с (i±2)-й ячейки дальности в текущем обзоре;

AK - результат сложения в текущем обзоре;

K - целое число, изменяющееся от 1 до N.

Схемы скоростных фильтров 15 идентичны, различие состоит в организации и управлении межобзорной памятью 39. Одна из них выполнена на фиг 8 и представляет собой группы ОЗУ 55, объединенных по входам и по выходам. Каждая группа управляется отдельным сигналом "выбор кристалла" (СЕ), поступающим с хронизатора 21. Временные диаграммы сигналов, управляющих работой одного из видов межобзорной памяти, состоящей из четырех массивов, и поступающих с хронизатора 21 (устройства 59), изображены на фиг.12. Отрицательный импульс (СЕ1-СЕ4) включает поочередно каждый из четырех массивов памяти, причем каждый импульс - синхронный со своим азимутальным сектором величиной l· Δ j ~90° , другие элементы памяти в этом момент находятся в 3-м состоянии. За обзор память всех азимутальных секторов заполняется текущей информацией. Обнуление формирователя 59 происходит один раз за обзор азимутальной меткой "Север". Информация за обзор записывается последовательно в каждую группу ОЗУ, занимая азимутальный сектор ~l· Δ j ° , где l=1,2... .

Накопленная в межобзорных скоростных фильтрах информация через выходные регистры 38 поступает на схему отбора максимального значения 16, которая может быть выполнена последовательными ступенями, каждая из которых состоит из схемы сравнения и коммутатора, управляемого знаком переноса схемы сравнения. В первой ступени сравниваются сигналы первых двух фильтров - Ф1 (А) и Ф2 (В). В случае А≥ В знак переноса схемы сравнения открывает коммутатор канала Ф1, а если А<В, открыт коммутатор канала Ф2. Таким образом, на выход всегда проходит максимальный сигнал. Результат первого сравнения и код сигнала канала Ф3 поступают на вторую ступень схемы отбора максимума. Этот результат и результат сравнения третьей ступени (каналов Ф4 и Ф5) поступают на четвертую ступень отбора максимума сигнала и т.д. После отбора максимального значения информация через промежуточный регистр, выполненный на ОЗУ, необходимого для воспроизведения информации в каждом такте для каждого элемента разрешения по дальности, поступает на вход формирователя азимутальных стробов 17. В устройстве 17 формируется напряжение в виде пирамидального строба протяженностью по азимуту до максимально возможной протяженности боковых лепестков с дискретностью в зависимости от мощности боковых лепестков через C· Δ j ° (C=1,2... ). При этом амплитудная характеристика устройства формирования управляющего напряжения выбрана таким образом, чтобы исключить в азимутальной окрестности сильной цели прием эхосигналов по боковым лепесткам.

На фиг.4 приведены импульсные характеристики устройства для двух уровней входных сигналов: а) 75 дБ и б) 50 дБ.

Импульсная характеристика имеет вид многоступенчатой симметричной пирамиды, на которой указаны по оси абсцисс протяженности стробов по азимуту в градусах, по оси ординат - градации управляющего напряжения. График построен для двух уровней входного сигнала.

На фиг.9 представлена амплитудная характеристика устройства, где по оси ординат указаны уровни напряжений, соответствующие выходным сигналам, а по оси абсцисс - дискретности изменения амплитуд сигналов на входе ОФ 2 основного канала в дБ. График построен для случая m=7.

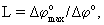

Для уменьшения объема аппаратуры, обусловленного сужением спектра обрабатываемых сигналов, можно применить процедуру временного уплотнения, для чего на входе устройства 17 в блоке 42 входная информация преобразуется в m-разрядный код, совпадающий с числом градаций изменения уровня чувствительности приема по БЛ. Коммутатором 43, управляемым хронизатором 44, амплитудная информация в виде m-значного числа мультиплексируется в нереальном времени (уплотняется) по тактам зондирования последовательным кодом в один канал. Временные диаграммы преобразования кодов - входного трехразрядного сначала в семиразрядный параллельный, а затем параллельного семиразрядного в последовательный код показаны на фиг.13а, б.

Параллельный семиразрядный код образуется сравнением входной трехразрядной амплитудной информации с пороговыми значениями от 1 до 7 в случае m=7 в устройстве 42 по временным тактам fт задаваемым хронизатором 21,в каждом элементе дальности внутри каждого такта. Распределенная по тактам информация затем в мультиплексоре 43, управляемом хронизатором 44, упаковывается в последовательный код, длина которого определяет амплитуду сигнала. На фиг.13а приведен случай величины сигнала: m=7, а на фиг.13б - m=4. Пример такого преобразования для числа m=7 приведен в таблице 1 приложения. В результате такого преобразования максимальный сигнал будет присутствовать на выходе коммутатора 43 m-тактов, минимальный - один такт.

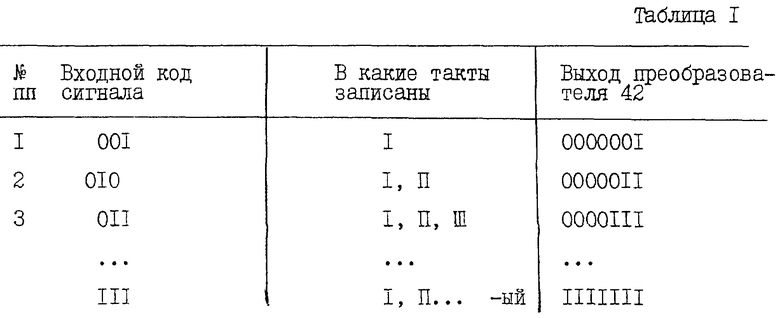

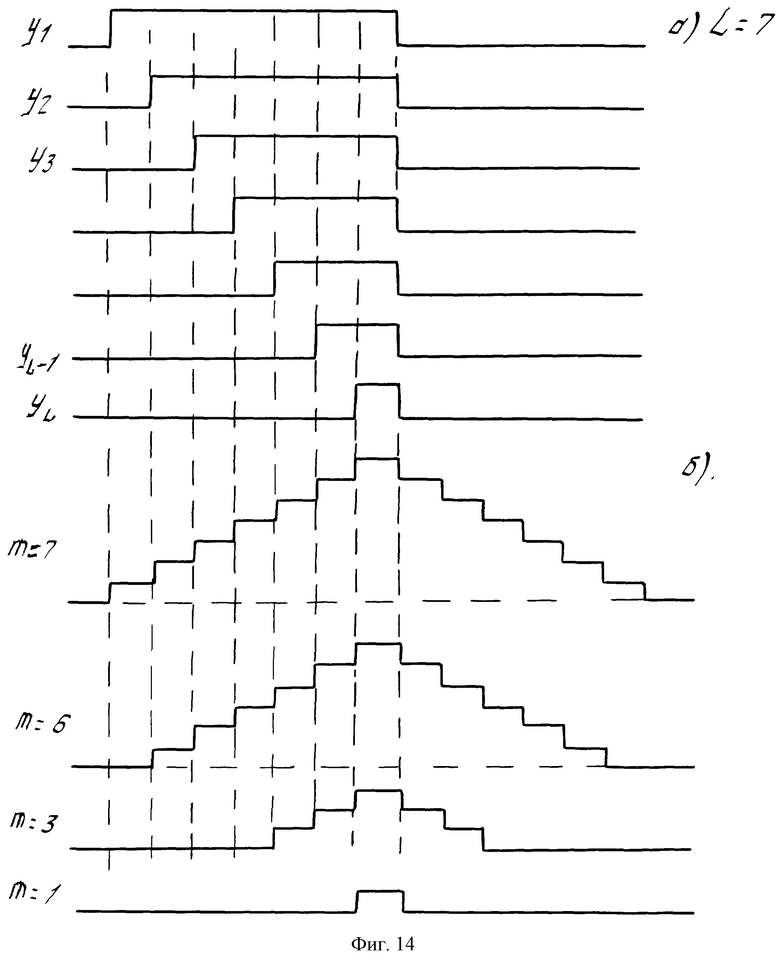

С выхода коммутатора 43 "упакованный" в один канал сигнал поступает на вход ЛЗ5(45), состоящую из L последовательно включенных ОЗУ с регистрами и отводами от каждого ОЗУ.  где Δ ϕmax° - максимальная протяженность боковых лепестков по азимуту сильных целей (до 60... 100 дБ). В каждое ОЗУ первые m-тактов (в случае максимального сигнала) внутри азимутального сектора (Δj° ) записывается информация с каждого кванта дальности в зоне действия боковых лепестков. В следующем азимутальном секторе Δ j ° информация из первого ОЗУ переписывается во второе ОЗУ и т.д. Через К· L тактов, т.е. через L азимутальных секторов, информация в случае максимального сигнала пишется во все L линии задержки (ОЗУ). Объем памяти каждого такого ОЗУ составляет: m· D/Δ D. Все L выходов ЛЗ5(45) с помощью хронизирующего устройства 49, ключей 46, 47, 48 (остальные на чертеже не показаны) и схемы объединения 50 объединены в один канал согласно табл.2 (приложение). Временные диаграммы управляющих ключами (46, 47, 48 и т.д.) сигналов и эпюр, показывающих принцип формирования выходных пирамидально-ступенчатых напряжений для разных случаев величины входного сигнала, изображены на фиг.14. На диаграмме показаны стробы, включающие различные участки, длинной линии задержки 45, через ключи 46, 47, 48, длительность которых определяется величиной сигнала и сопутствующих ему боковых лепестков. Указанные стробы сформированы на счетчике тактовых импульсов 56 и дешифраторах на логических элементах И, ИЛИ, НЕ, в устройстве 49, являющемся частью хронизатора. Логическое суммирование сигналов с ключей в элементе 50 изображено для четырех случаев разрядности "m" входного сигнала на фиг.14. Величины ступеней пирамидального управляющего напряжения по азимуту в градусах в зависимости от динамического диапазона входного воздействия и соответственно от разрядности "m", полученного в элементе 42 кода, показано на фиг.4.

где Δ ϕmax° - максимальная протяженность боковых лепестков по азимуту сильных целей (до 60... 100 дБ). В каждое ОЗУ первые m-тактов (в случае максимального сигнала) внутри азимутального сектора (Δj° ) записывается информация с каждого кванта дальности в зоне действия боковых лепестков. В следующем азимутальном секторе Δ j ° информация из первого ОЗУ переписывается во второе ОЗУ и т.д. Через К· L тактов, т.е. через L азимутальных секторов, информация в случае максимального сигнала пишется во все L линии задержки (ОЗУ). Объем памяти каждого такого ОЗУ составляет: m· D/Δ D. Все L выходов ЛЗ5(45) с помощью хронизирующего устройства 49, ключей 46, 47, 48 (остальные на чертеже не показаны) и схемы объединения 50 объединены в один канал согласно табл.2 (приложение). Временные диаграммы управляющих ключами (46, 47, 48 и т.д.) сигналов и эпюр, показывающих принцип формирования выходных пирамидально-ступенчатых напряжений для разных случаев величины входного сигнала, изображены на фиг.14. На диаграмме показаны стробы, включающие различные участки, длинной линии задержки 45, через ключи 46, 47, 48, длительность которых определяется величиной сигнала и сопутствующих ему боковых лепестков. Указанные стробы сформированы на счетчике тактовых импульсов 56 и дешифраторах на логических элементах И, ИЛИ, НЕ, в устройстве 49, являющемся частью хронизатора. Логическое суммирование сигналов с ключей в элементе 50 изображено для четырех случаев разрядности "m" входного сигнала на фиг.14. Величины ступеней пирамидального управляющего напряжения по азимуту в градусах в зависимости от динамического диапазона входного воздействия и соответственно от разрядности "m", полученного в элементе 42 кода, показано на фиг.4.

Если сигнал на входе Л35(45) максимальный (код - III), то на выход схемы объединения 50 пройдут сигналы со всех L ОЗУ. Причем информация с восьми центральных ОЗУ ( ) считывается в течение семи тактов, с двух ОЗУ соседних слева (L/2 –5, -4) и двух ОЗУ справа от восьми центральных (L/2 5, +6) в течение шести тактов и т.д. В крайних двух ОЗУ слева (1, 2) и справа (L-1, L) информация считывается в одном (первом) такте внутри каждого рабочего азимутального сектора Δ j ° , в котором присутствуют сигналы. Если входной код имеет вид 001 (минимальный сигнал), то к выходу подключены восемь центральных ОЗУ (

) считывается в течение семи тактов, с двух ОЗУ соседних слева (L/2 –5, -4) и двух ОЗУ справа от восьми центральных (L/2 5, +6) в течение шести тактов и т.д. В крайних двух ОЗУ слева (1, 2) и справа (L-1, L) информация считывается в одном (первом) такте внутри каждого рабочего азимутального сектора Δ j ° , в котором присутствуют сигналы. Если входной код имеет вид 001 (минимальный сигнал), то к выходу подключены восемь центральных ОЗУ ( ), что составляет минимальную область, занятую боковыми лепестками и равную 8· Δ j ° по азимуту. Если входной код имеет вид 010, то к выходам восьми центральных ОЗУ подключаются два соседних справа ОЗУ и два соседних слева, увеличивая область подавления боковых лепестков еще на 4· Δ j ° . Еще четыре значения кода добавляют каждый раз по четыре ОЗУ.

), что составляет минимальную область, занятую боковыми лепестками и равную 8· Δ j ° по азимуту. Если входной код имеет вид 010, то к выходам восьми центральных ОЗУ подключаются два соседних справа ОЗУ и два соседних слева, увеличивая область подавления боковых лепестков еще на 4· Δ j ° . Еще четыре значения кода добавляют каждый раз по четыре ОЗУ.

Таким образом, формируется одноразрядный азимутальный ступенчато-пирамидальный строб, в котором количество ступеней (длительность импульсной характеристики) определяется величиной входного напряжения.

Для восстановления амплитудной информации применены две ступени: в первой происходит преобразование одноразрядного последовательного кода в m-разрядный параллельный, во второй - восстановление входной амплитудной информации из m-разрядного кода в нереальном времени в реальное время. Преобразование одноразрядного кода, поступающего со схемы объединения 50 через линию задержки 51, служащую для компенсации задержки по дальности, на вход линии задержки 52, состоящей из m параллельно-включенных ОЗУ, происходит следующим образом:

в первом такте - запись информации в первое ОЗУ;

во втором - запись во второе ОЗУ;

в m-м такте - запись в m-е ОЗУ.

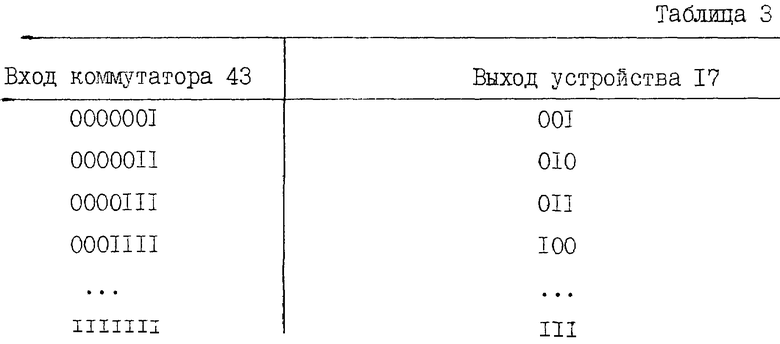

Считывание информации с раздельных выходов m-ОЗУ происходит одномоментно в рабочем такте по команде выбора кристалла СЕ, подаваемой одновременно на все ОЗУ ЛЗ6 (52.) Информация в двоичном коде из m-полученных каналов поступает на вход регистра 53, отключающего выход ЛЗ6 52 во время записи, и с выхода регистра поступает на вход устройства 54, восстанавливающего входной код из m-разрядного кода, согласно приложению, табл.3. Благодаря преобразованию информации на входе и выходе устройства 17 осуществляется экономия ОЗУ устройства 17 в log2(m+1) раз по сравнению с параллельной обработкой всех разрядов в устройстве 17.

В восстановленной амплитудной информации выбираются все задержки по дальности и по азимуту, а также расширение по дальности для точного и надежного совмещения управляющего напряжения блока 8 с приходящим эхосигналом.

Для этих целей между выходом формирователя азимутальных стробов 17 и входом блока подавления приема по БЛ ДН 7 включены последовательно линии задержки ЛЗ1 18, ЛЗ2 19 и буферное устройство 20.

В ЛЗ1 (18) осуществляется задержка по азимуту "грубо" на ОЗУ четырьмя последовательными ступенями. Это устройство компенсирует задержку сигнала, приобретенную в формирователе пирамидально-ступенчатого азимутального строба.

В ЛЗ2 (19) осуществляется задержка по азимуту "точно" с дискретностью Δ j ° и увеличение до длительности "несжатого" эхосигнала управляющего напряжения. Эта задержка может быть выполнена на ОЗУ, управляемом адресными счетчиками, и на регистрах, увеличивающих длительность управляющего напряжения. Задержка по дальности в целях сокращения объема аппаратуры осуществляется в одноканальном устройстве ЛЗ3 (51), находящемся в формирователе азимутальных стробов между выходом схемы объединения 50 и входом ЛЗ6 (52). Эта задержка может быть выполнена на ОЗУ и регистре и осуществляется сдвигом адресных кодов ОЗУ, формируемых счетчиком хронизатора 21, сумматором, мультиплексором через регистр. Величина сдвига задается кодом числа, поступающего на сложение с адресным кодом счетчика (схемы формирования 57). Выходное буферное устройство 20 позволяет считывать информацию, увеличенную до длительности несжатого эхосигнала каждый такт с частотой 1/To. Управляющее напряжение подается на блок 7 подавления приема по БЛ ДН антенны, где оно сравнивается с входным напряжением. В случае превышения управляющего напряжения над входным сигналом происходит отключение основного канала приемника и таким образом происходит подавление приема по боковым лепесткам диаграммы направленности. В заключение следует отметить, что, поскольку предлагаемое устройство вырабатывает управляющее напряжение для регулировки последующих элементов приемного такта для более устойчивой его работы, необходимо обеспечить некоторое вполне определенное превышение над ожидаемым уровнем эхосигналов в следующем обзоре. Практически это превышение должно соответствовать величине амплитудной градации принимаемых колебании в нелинейном элементе 9 на входе оптимального фильтра 10 дополнительного блока 8, формирующего управляющее напряжение. При меньшей величине этого превышения возможно появление приема эхосигналов по боковым лепесткам диаграммы направленности антенны.

Управление всеми устройствами, входящими в блок формирования управляющего напряжения 8 и в блок подавления приема по БЛ ДН 7, осуществляется хронизирующим устройством 21, которое синхронно с работой РЛС.

Таким образом, предлагаемое устройство позволяет практически исключить прием эхосигналов по боковым лепесткам диаграммы направленности для целей, обладающих произвольными ЭПР. Достигается это выбором базы сложного сигнала, величиной тактовой частоты зондирования и скоростью сканирования по азимутальной координате. При этом также одновременно достигается помехозащищенность устройства и при приеме эхосигналов на фоне произвольного вида несинхронных помех. Учитывая, что, в предлагаемом устройстве происходит обработка ограниченного объема информации (разрядность блока формирования управляющего напряжения для большинства практических применений не должна превышать 3-4 разрядов) и существенное сужение спектра принимаемых колебаний в процессе обработки (огрубление информации по дальности и азимуту) возможно применить при практической реализации, временное уплотнение обрабатываемой информации и все рассмотренные выше алгоритмы можно реализовать программными методами аналогично применяемым в современных ЭВМ. Т.е. практическая реализация предложенных алгоритмов затруднений не вызывает и может быть реализована на современной элементной цифровой базе. Практически за счет введения данных алгоритмов в состав приемника увеличения аппаратуры не происходит. Кроме того, предложенное устройство более эффективно функционирует при приеме на фоне импульсных несинхронных помех, чем известные многоканальные устройства ПБЛ, использующие амплитудные соотношения между каналами для подавления приема эхосигналов по боковым лепесткам. В таких устройствах требуется сохранение полной амплитудной информации, т.е. нельзя применять нелинейные схемы подавления несинхронных помех, которые широко используются в современных обзорных РЛС. Предлагаемое устройство указанным недостатком не обладает.

Источники информации

1. Вопросы судостроения. Сер. Общетехническая, вып.60, 1981 (с.54-59).

2. Авторское свидетельство №266965 (прототип).

3. Ю.С.Лезин. Оптимальные фильтры и накопители импульсных сигналов. - М.: Советское радио, 1969 (с.182-186).

4. Пахомов Ю.И., Зачепицкий А.А. К вопросу о защищенности радиолокационых приемников с ограничением от импульсных помех // Радиоэлектроника, 1969, 2.

5. Справочник по радиолокации. - М.: Сколник, т.3 (с.135-137, 170-174).

6. М.Г.Гарб. Синхронизация в телевидении. - М.: Радио и связь, 1982, с.52-55.

7. Расчет элементов импульсных и цифровых схем радиотехнических устройств/Под ред. Ю.М.Казаринова. - М.: Высшая школа, 1976 (с.94).

Изобретение относится к радиолокации и может быть использовано в импульсных радиолокационных станциях для устранения приема эхосигналов, приходящих по боковым лепесткам (БЛ) диаграммы направленности антенны (ДНА). Техническим результатом является улучшение подавления приема эхосигналов по боковым лепесткам диаграммы направленности антенны за счет снижения чувствительности приема эхосигналов по боковым лепесткам. Технический результат достигается за счет того, что к входу ограничителя подключен выход блока подавления приема по боковым лепесткам диаграммы направленности антенны, управляемый вход которого соединен с выходом блока формирования управляющего напряжения, который содержит последовательно соединенные нелинейное устройство, оптимальный фильтр, детектор, некогерентный накопитель, азимутально-дальностный интегратор, устройство межобзорной обработки сигналов, формирователь азимутальных стробов, две линии задержки, буферное устройство, выход которого соединен с управляемым входом блока подавления приема по боковым лепесткам диаграммы направленности антенны, и хронизатор, управляющие выходы которого соединены с управляемыми входами азимутально-дальностного интегратора, устройства межобзорной обработки сигналов, формирователя азимутальных стробов и линий задержки, и имеющий вход для подключения синхронизатора работы РЛС, при этом основной вход блока подавления приема по боковым лепесткам диаграммы направленности антенны соединен с входом блока формирования управляющего напряжения и является входом всего устройства. 3 з.п. ф-лы, 14 ил.

| ПРИЕМНОЕ УСТРОЙСТВО | 1985 |

|

RU2212041C2 |

Авторы

Даты

2004-04-10—Публикация

1990-05-07—Подача