Изобретение относится к радиотехнике и может найти применение в приемных устройствах.

Известны устройства компенсации узкополосных помех, описанные в а.с. №1688416, Н 04 В 1/10, а также в патенте №2034402, Н 04 В 1/10 от 30.04.95 г. и других, недостатком которых является малая степень подавления узкополосных помех.

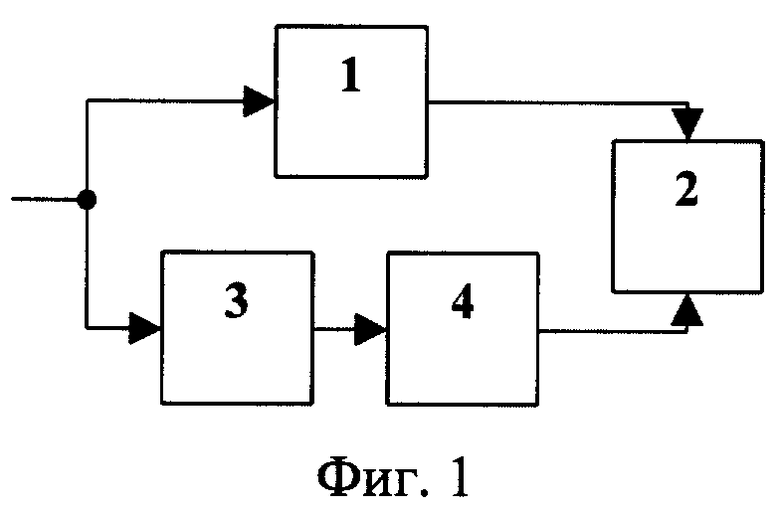

Наиболее близким по технической сущности к заявляемому устройству является устройство компенсации помех, описанное в статье Ефимова В.П. “Оценка влияния нелинейного преобразователя на помехоустойчивость приёма в спутниковых сетях”, опубликованное в журнале “Электромагнитные волны и электромагнитные системы”, №1, т.3, 1998, стр.95, принятое за прототип, структурная схема которого приведена на фиг.1, где обозначено: 1 - усилитель; 2 - вычитатель; 3 - ограничитель; 4 - полосовой фильтр.

Устройство-прототип содержит последовательно соединенные усилитель 1 и вычитатель 2, выход которого является выходом устройства, а также последовательно соединенные ограничитель 3 и полосовой фильтр 4, выход которого соединен со вторым входом вычитателя 2, при этом входы усилителя 1 и ограничителя 3 объединены и являются входом устройства.

Устройство-прототип работает следующим образом.

Входная смесь, содержащая сигнал и N-узкополосных помех, с входа устройства поступает в блок 1, где осуществляется её усиление, после чего смесь поступает на первый вход блока 3, на второй вход которого поступает оценка узкополосных помех, которая формируется за счёт ограничения входной смеси в блоке 3 с последующей фильтрацией результата ограничения в блоке 4. За счет вычитания в блоке 2 из входной смеси оценки узкополосных помех на его выходе выделяется сигнал и некомпенсированные остатки узкополосных помех.

Недостатком прототипа является малая степень подавления узкополосных помех.

Для устранения указанного недостатка в устройство компенсации узкополосных помех, содержащее усилитель и вычитатель, выход которого является выходом устройства, указанные усилитель и вычитатель введены в состав блоков N-го канала, в который также введены последовательно соединенные третий перемножитель, второй фильтр нижних частот, амплитудный детектор и блок сравнения с порогом; последовательно соединенные первый перемножитель, первый фильтр нижних частот, блок фильтрации и формирования управляющих напряжений и управляемый генератор; последовательно соединенные второй перемножитель и ключ, управляющий вход которого соединен с выходом блока сравнения с порогом и с управляющим входом блока фильтрации и формирования управляющих напряжений; при этом выход второго фильтра нижних частот через усилитель соединен с первым сигнальным входом второго перемножителя, второй опорный вход которого соединен с вторым опорным входом третьего перемножителя и с первым выходом управляемого генератора, второй выход которого соединен с вторым опорным входом первого перемножителя; кроме того, выход ключа соединен с вторым входом вычитателя, первый вход которого соединен с первыми сигнальными входами первого и третьего перемножителей и с входом N-ого канала, а также введены (N-1) каналов, аналогичных N-ому каналу по составу блоков и связей между ними, при этом вход первого канала является входом устройства, выход первого канала соединен с входом второго канала, вход i-ого канала, i=3,...,N, соединен с входом (N-1)-го канала.

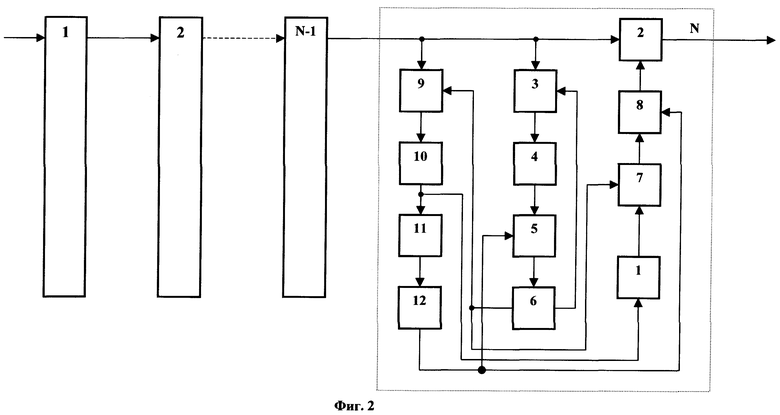

Структурная схема предлагаемого устройства приведена на фиг.2, где обозначено: 1 - усилитель; 2 - вычитатель; 3, 7, 9 - первый, второй и третий перемножители; 4, 10 - первый и второй фильтры нижних частот; 5 - блок фильтрации и формирования управляющих напряжений; 6 - управляемый генератор; 8 - ключ; 11 - амплитудный детектор; 12 - блок сравнения в порогом.

Предлагаемое устройство содержит N последовательно соединенных каналов, имеющих одинаковый состав блоков и связей. Вход первого канала является входом устройства, выход первого канала соединен с входом второго канала, выход второго канала соединен с входом третьего канала и так далее, выход (N-1)-гo канала соединен с входом N-го канала, выход которого является выходом устройства.

В каждом канале осуществляется формирование оценки одной из М узкополосных помех (М⇐N) и ее компенсация. Если входной сигнал первого канала содержит М узкополосных помех, то входной сигнал второго канала будет содержать М-1 узкополосных помех, третьего канала М-2 узкополосных помех и т.д.

Каждый из N каналов содержит вычитатель 2, первый вход которого является входом канала, а выход - выходом канала, содержит последовательно соединенные первый перемножитель 3, первый сигнальный вход которого соединен с входом устройства, первый фильтр нижних частот 4, блок фильтрации и формирования управляющих напряжений 5, управляемый генератор 6, первый выход которого соединен с вторым опорным входом перемножителя 3; содержит последовательно соединенные второй перемножитель 7 и ключ 8, выход которого соединен с вторым входом вычитателя 2, при этом второй опорный вход перемножителя 7 соединён с первым выходом управляемого генератора 6 и вторым опорным входом третьего перемножителя 9, первый сигнальный вход которого соединен с первым входом вычитателя 2, а выход перемножителя 9 через фильтр нижних частот 10 соединен с входом амплитудного детектора 11 и с входом усилителя 1, выход которого соединён с первым сигнальным входом второго перемножителя 7, а выход амплитудного детектора 11 через блок сравнения с порогом 12 соединен с управляющим входом ключа 8 и управляющим входом блока фильтрации и формирования управляющих напряжений 5.

Заявляемое устройство работает следующим образом. Входная смесь, содержащая полезный сигнал и узкополосные помехи, поступает на вход первого канала, где осуществляется поиск по частоте узкополосных помех в заданном диапазоне частот, захват одной (первой) узкополосной помехи, формирование ее оценки с последующей ее компенсацией. Выходной сигнал первого канала поступает на вход второго канала, где осуществляется процедура, аналогичная той, которая выполнялась в первом канале, при этом во втором канале осуществляется захват по частоте второй помехи, формирование её оценки и компенсация ее во входной смеси, поступающей на вход второго канала с выхода первого канала. Аналогичные процедуры осуществляются в 3-ем, 4-ом,...,(N-1), N-ом каналах. С выхода N-го канала сигнал подаётся на выход устройства.

Учитывая, что все каналы компенсации узкополосных помех имеют одинаковое построение, рассмотрим работу одного, первого канала.

Входная смесь, содержащая полезный сигнал и узкополосные помехи, поступает на первый сигнальный вход блока 9, на второй опорный его вход подается напряжение с первого выхода блока 6. В блоке 9 после перемножения узкополосных помех с напряжением, поступающим с первого выхода блока 6, на выходе блока 9 будет присутствовать напряжение с суммарной и разностной частотами, которое подается на блок 10. В блоке 10 осуществляется фильтрация нижних частот напряжения, снимаемого с выхода блока 9. Сигнал на выходе блока 10 появляется в том случае, когда разность между частотой захваченной узкополосной помехи и частотой управляемого генератора попадает в его полосу пропускания. С выхода блока 10 напряжение подается на блок 11, где за счет амплитудного детектирования выделяется его огибающая, поступающая на блок 12, где она сравнивается с порогом.

Одновременно входная смесь с входа устройства подается на первый сигнальный вход блока 3, на второй опорный вход которого подается напряжение с второго выхода блока 6.

После перемножения узкополосных помех с напряжением блока 6 на выходе блока 3 также выделяется напряжение с суммарной и разностной частотами, которое подается на блок 4, где осуществляется фильтрация нижних частот. На выходе блока 4 появляется напряжение в том случае, когда напряжение разностной частоты попадёт в его полосу пропускания. Напряжение с выхода блока 4 поступает на первый сигнальный вход блока 5, на второй управляющий вход которого подается напряжение с выхода блока 12.

При отсутствии превышения порога в блоке 12 на его выходе формируется управляющий сигнал логический ноль (“ЛОГ 0”). В этом случае блок 5 формирует на своём выходе пилообразное напряжение, которое поступает на управляющий вход блока 6 и обеспечивает режим сканирования его по частоте в заданном диапазоне частот, соответствующем полосе спектра полезного сигнала. В случае превышения порога в блоке 12 на его выходе формируется управляющий сигнал логическая единица (“ЛОГ 1”), соответствующая захвату одной (первой) помехи. Эта команда, поступая на управляющий вход блока 5, изменяет режим его работы. В этом случае блок 5 формирует напряжение, которое, поступая на блок 6, обеспечивает режим слежения за фазой и частотой захваченной первой узкополосной помехи.

Изменением частоты управляемого генератора 6 происходит подстройка фазы его выходного сигнала под фазу узкополосной помехи, которую необходимо скомпенсировать. В режиме синхронизма, когда фазовое рассогласование выходного сигнала блока 6 и узкополосной помехи имеет минимальную величину, с выхода блока 10 будет сниматься постоянная составляющая, определяющая амплитуду узкополосной помехи. Сигнал блока 10 через блок 1 поступает на первый вход блока 7, на второй вход которого поступает сигнал с первого выхода блока 6. За счет перемножения указанных сигналов на выходе блока 7 формируется оценка узкополосной помехи. Коэффициент передачи блока 1 выбирается таким образом, чтобы обеспечивалось равенство амплитуды оценки узкополосной помехи амплитуде первой узкополосной помехи во входной смеси. Одновременно команда (“ЛОГ 1”) с выхода блока 12 поступает на управляющий вход блока 8, отпирая его и обеспечивая прохождение оценки первой узкополосной помехи на второй вход блока 2, где она компенсирует соответствующую узкополосную помеху во входной смеси, поступающую с входа устройства на первый вход блока 2, с выхода которого входная смесь, из которой исключена первая помеха, поступает на выход канала.

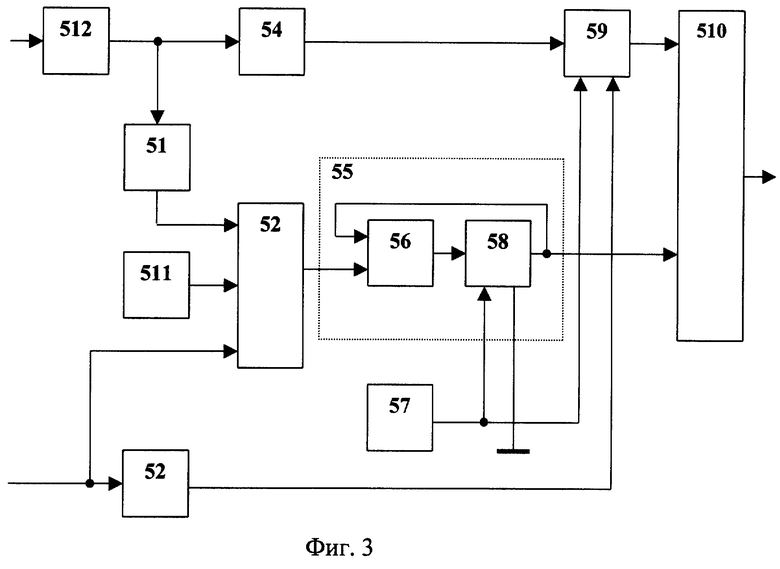

На фиг.3 показана функциональная схема одного из вариантов реализации блока 5, где обозначено: 51, 54 - первый и второй умножители на постоянные коэффициенты α1 и α2; 52 - инвертор; 53 - коммутатор; 55 - накопитель; 56, 59 - первый и второй регистры; 57 - генератор импульсов; 58, 510 - первый и второй сумматоры; 511 - блок памяти; 512 - аналого-цифровой преобразователь.

Блок 5 содержит последовательно соединенные блок памяти 511, коммутатор 53, первый сумматор 56, первый регистр 58, второй сумматор 510, выход которого является выходом блока 5, последовательно соединенные аналого-цифровой преобразователь 512, вход которого является сигнальным входом блока 5, второй умножитель на постоянный коэффициент α2 54, второй регистр 59, выход которого соединен с вторым входом второго сумматора 510, содержит первый умножитель на постоянный коэффициент α1 51, вход которого соединен с выходом аналого-цифрового преобразователя 512, а выход - с вторым сигнальным входом коммутатора 53, а также генератор тактовых импульсов 57, выходом соединенный с первым тактовым входом первого регистра 58 и с первым тактовым входом второго регистра 59, инвертор 52, вход которого соединен с первым управляющим входом коммутатора 53 и является управляющим входом блока 5, а выход соединен с вторым управляющим входом второго регистра 59, при этом второй управляющий вход первого регистра 58 заземлен, а выход первого регистра 58 соединен с вторым входом первого сумматора 56.

Блок 5 работает следующим образом.

Пока порог не превышен, с выхода блока 12 (фиг.2) на входы блоков 52 и 53 (фиг.3) поступает логический ноль. В этом случае на выходе блока 52 формируется логическая единица, которая обнуляет блок 59, а блок 53 подключает на вход блока 55 выход блока 511, который формирует постоянное число А, определяющее шаг перестройки устройства по частоте при поиске узкополосной помехи. При поступлении с выхода блока 57 на тактовый вход блока 58 тактовых импульсов в блок 58 записывается результат сложения в блоке 56 постоянного числа А, определяющего шаг перестройки по частоте, поступающего от блока 511 через блоки 53 и 56 с числовым значением, хранящимся в блоке 58. Поэтому код Uрег. на выходе блока 58 для момента времени t=(n+1)•T (где Т период тактовых импульсов на выходе блока 57, n - их число) определяется равенствами Uрег.((n+1)•Т) = Uрег.(n•Т)+Δ, если Uрег.((n+1)•Т)<2m и Uрег.((n+1)*T)=Uрег.(n*T)+Δ-2m, если Uрег.((n+1)*T)≥2m (где m число разрядов блока 56).

После достижения максимального значения Umax в блок 58 запишется остаток, величина которого не превышает А. Выбирая разрядность m блока 58, частоту Fген. = 1/Т тактовых импульсов и значение Δ, можно обеспечить перестройку частоты блока 6 с необходимой скоростью в заданном диапазоне частот. Выходной код блока 58 поступает на первый вход блока 510, на второй вход которого (пока не произошло превышение порога в блоке 12), с выхода блока 59 (фиг.3) подаются нули. При изменении выходного кода блока 58 выходной код блока 510 будет изменяться и перестраивать частоту блока 6 (см. фиг.2).

Когда разность частот между частотой сигнала блока 6 и частотой помехи станет меньше частоты среза блока 10, на выходе блока 11 появится постоянная составляющая, превышающая порог в блоке 12. На выходе блока 12 логический ноль измениться на логическую единицу. Логическая единица с выхода блока 12 поступает на блок 53, который по этой команде отключает от входа блока 55 выход блока 511 и подключает к нему выход блока 51. Одновременно логическая единица через блок 52, осуществляющий ее инверсию, подается на второй вход блока 59, разрешая запись в него кода, поступающего от блока 54. В результате выполненных переключений блок 6 (фиг.2) переходит в режим слежения за захваченной узкополосной помехой. В этом режиме сигнал фазовой ошибки, снимаемый с выхода блока 4 (фиг.2) через блок 512, переводящий его в цифровую форму, поступает на вход блока 54 (фиг.3), осуществляющий умножение его на постоянный коэффициент α2.

С выхода блока 54 цифровой код подается на сигнальный вход блока 59. Запись цифрового кода в блок 59 осуществляется по тактам, поступающим от блока 57 на его первый, тактовый вход. Сигнал фазовой ошибки, снимаемый с выхода блока 4 (фиг.2), через блок 512, переводящий сигнал в цифровую форму, и блок 51, обеспечивающий умножение на постоянный коэффициент α1, поступает на вход накопителя 55, состоящего из последовательно соединённых сумматора 56 и регистра 58. Накопитель 55, выполняющий функцию цифрового интегрирующего устройства, повышает порядок астатизма и точность работы устройства фазовой автоподстройки частоты. В сумматоре 510 код регистра 59 складывается с кодом регистра 58 и подаётся на вход блока 6.

Блок 511 может быть выполнен в виде регистра с обратными связями, в котором записано кодовое число А, и генератора тактовых импульсов, с выхода которого тактовые импульсы подаются на тактовый вход регистра, за счет чего обеспечивается запись кодового числа А на вход коммутатора 53.

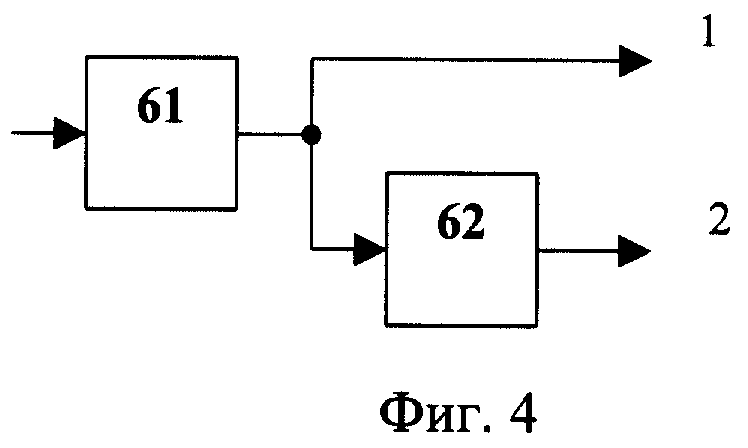

Структурная схема блока 6 приведена на фиг.4, где обозначено: 61 - перестраиваемый генератор; 62 - фазовращатель на 90°.

Блок 6 содержит перестраиваемый генератор 61 и фазовращатель на 90°, при этом управляющий вход блока 61 является управляющим входом блока 6, а выход блока 61 соединен с первым выходом блока 6 непосредственно, а с вторым входом - через блок 62.

Блок 6 работает следующим образом.

На управляющий вход блока 61 поступает управляющее напряжение с выхода блока 5, в соответствии с которым изменяется частота гармонического колебания, генерируемого блоком 61. С выхода блока 61 гармоническое колебание подается на первый выход блока 6 непосредственно, а на второй его выход - через блок 62.

Блок 61 является известным устройством, используемым в системах фазовой подстройки частоты (см. Диксон Р.К. Широкополосные системы. - М.: Связь, 1979, стр.144, рис.5.15).

Прототип обеспечивает наибольшую степень компенсации при наличии на его входе одиночной узкополосной помехи известной амплитуды, равной уровню ограничения ограничителя. При одновременном воздействии N узкополосных помех разного уровня в прототипе за счет ограничения входной смеси узкополосные помехи большого уровня подавляют более слабые узкополосные помехи. Поэтому амплитуды оценок узкополосных помех отличаются от амплитуд соответствующих им узкополосных помех во входной смеси, за счет чего снижается степень их подавления.

В заявляемом устройстве формирование оценки каждой из N узкополосных помех происходит в отдельном канале, при этом исключается возможность перераспределения амплитуд оценок узкополосных помех за счет их взаимного влияния. В результате чего в заявляемом устройстве степень подавления узкополосных помех выше, чем в прототипе.

Изобретение относится к радиотехнике. Технический результат заключается в повышении степени подавления узкополосных помех. Сущность изобретения заключается в том, что в известное устройство компенсации, содержащее усилитель и вычитатель, входящие в состав N-го канала, введены первый, второй и третий перемножители, первый и второй фильтры нижних частот, блок фильтрации и формирования управляющих напряжений, управляемый генератор, ключ, амплитудный детектор и блок сравнения с порогом, а также введены (N-1) каналов, аналогичных N-му каналу по составу блоков и связей между ними. 2 ил.

Устройство компенсации узкополосных помех, содержащее усилитель и вычитатель, выход которого является выходом устройства, отличающееся тем, что указанные усилитель и вычитатель введены в состав блоков N-го канала, в который также введены последовательно соединенные третий перемножитель, второй фильтр нижних частот, амплитудный детектор и блок сравнения с порогом; последовательно соединенные первый перемножитель, первый фильтр нижних частот, блок фильтрации и формирования управляющих напряжений и управляемый генератор; последовательно соединенные второй перемножитель и ключ, управляющий вход которого соединен с выходом блока фильтрации и формирования управляющих напряжений; при этом выход второго фильтра нижних частот через усилитель соединен с первым, сигнальным входом второго перемножителя, второй, опорный вход которого соединен с вторым, опорным входом третьего перемножителя и с первым выходом управляемого генератора, второй выход которого соединен с вторым, опорным входом первого перемножителя; кроме того, выход ключа соединен с вторым выходом вычитателя, первый вход которого соединен с первыми, сигнальным входами первого и третьего перемножителей и с входом N-го канала; а также введены N-1 каналов, аналогичных N-му каналу по составу блоков и связей между ними, при этом вход первого канала является входом устройства, выход первого канала соединен с входом второго канала, выход второго канала соединен со входом третьего канала и так далее, выход (N-1)-го канала соединен с входом N-го канала, выход которого является выходом устройства.

| УСТРОЙСТВО ПОДАВЛЕНИЯ УЗКОПОЛОСНЫХ ПОМЕХ | 1996 |

|

RU2126589C1 |

| RU 98122353 A, 27.09.2000 | |||

| ГСГЕСОЮаНАЯ [ | 0 |

|

SU372369A1 |

| Устройство компенсации узкополосной помехи | 1989 |

|

SU1732474A2 |

Авторы

Даты

2004-04-20—Публикация

2002-04-22—Подача