Изобретение относится к цифровой вычислительной технике и может быть использовано в автоматизированных системах для контроля микроЭВМ, содержащих цифровые входы - выходы.

Известно устройство для функционального контроля микроконтроллера (см. А.С. СССР №1578716 от 22.07.88, МКИ G 06 F 11/26, "Устройство для контроля микроЭВМ", Ткаченко А.М., Варго В.Л., Тютюнников Н.В., опубл. 15.07.90., Бюл. №26), содержащее блок ввода - вывода информации, два счетчика, два регистра, индикатор, два блока памяти, блок ключей, элемент И, три регистра, блок цифроаналоговых преобразователей, блок аналого-цифровых преобразователей, два аналоговых коммутатора, блок аналоговых ключей, блок регистров, цифровой коммутатор, схему сравнения, элемент ИЛИ и два блока элементов И. Вход "Пуск" устройства соединен с входами "Сброс" счетчиков и блока ввода-вывода информации первого регистра и является выходом устройства для подключения микроЭВМ (микроконтроллера). Первый выход блока ввода-вывода соединен с входом установки второго счетчика и информационным входом первого блока памяти. Второй выход блока ввода-вывода соединен с входом ввода информации второго блока памяти. Первый информационный выход второго блока памяти через блок ключей подключен к входам - выходам устройства для подключения микроЭВМ и информационному входу второго регистра. Адресный вход первого блока памяти соединен с выходом второго счетчика. Счетный вход второго счетчика подключен к тактовому входу устройства для подключения микроЭВМ. Вход "Чтение" первого блока памяти соединен с входом "Запрос ввода - вывода" устройства для подключения микроЭВМ. Вход признака "Ввод" устройства для подключения микроЭВМ подключен к первому входу элемента И и управляющему входу блока ключей. Вход признака "Вывод" устройства для подключения микроЭВМ соединен со вторым входом элемента И и синхровходом второго регистра. Информационный выход первого блока памяти и второй информационный выход второго блока памяти подключены к соответствующим информационным входам первого регистра. Выходы первого счетчика и второго регистра подключены к соответствующим адресным входам второго блока памяти. Вход "Чтение" второго блока памяти соединен с входом запроса ввода-вывода устройства для подключения микроЭВМ. Выход элемента И соединен с входом управления записью первого регистра. Выход первого регистра соединен с входом индикатора. Вход "Пуск" устройства соединен с входами "Сброс" третьего, четвертого и пятого регистров. Выход третьего регистра подключен к третьему адресному входу второго блока памяти. Третий информационный вход второго блока памяти подключен к управляющим входам цифрового коммутатора, первого и второго аналоговых коммутаторов, к информационным входам четвертого и пятого регистров, к входу "Пуск" блока регистров, к первым входам первого и второго блоков элементов И.

Информационный вход третьего регистра соединен с выходом цифрового коммутатора. Выходы второго регистра и блока аналого-цифровых преобразователей соединены с соответствующими информационными входами цифрового коммутатора. Первый и второй входы схемы сравнения подключены соответственно к выходам третьего и четвертого регистров. Выход схемы сравнения подключен к входу данных блока регистров. Цифровой выход блока регистров соединен с первым информационным входом блока цифроаналоговых преобразователей. Выход "Завершение преобразования" блока регистров соединен с первым входом элемента ИЛИ. Выход пятого регистра соединен со вторым информационным входом блока цифроаналоговых преобразователей. Аналоговый выход блока цифроаналоговых преобразователей через первый аналоговый коммутатор и блок аналоговых ключей подключен к входам-выходам устройства для подключения микроЭВМ. Входы-выходы устройства для подключения микроЭВМ через второй аналоговый коммутатор подключены также к аналоговому входу блока аналого-цифровых преобразователей. Вторые входы первого и второго блоков элементов И и элемента ИЛИ соединены соответственно с выходами "Вывод", "Ввод" и "Запрос ввода-вывода" устройства для подключения микроЭВМ. Выходы первого и второго блоков элементов И и элемента ИЛИ соединены соответственно с входом "Пуск" блока аналого-цифровых преобразователей, управляющим входом блока аналоговых ключей и счетным входом первого счетчика.

Недостатком известного устройства является невозможность определения конкретных тестовых команд, выполненных неправильно из-за отсутствия возможности детального сравнения и отображения для пользователя указанных команд.

Известно устройство для функционального контроля однокристального микроконтроллера (см. ЩЦМ 1.142.025 ТО утв. 1986 г., ОАО “НИИПМ”, г.Воронеж), взятое за прототип и содержащее измерительную головку (контролируемый однокристальный микроконтроллер), блок цифрового суммирования, блок тестовых последовательностей (блок постоянных запоминающих устройств тестовых последовательностей), блок памяти ошибок (блок оперативных запоминающих устройств), программируемый генератор импульсов, генератор произвольных последовательностей, блок управления (блок начальной установки контролируемого однокристального микроконтроллера), блок измерителей-источников, блок аналого-цифрового преобразователя, коммутационную матрицу (блок коммутации), блок задания уровней, персональную электронно-вычислительную машину (ПЭВМ). Выход коммутационной матрицы соединен с первым входом измерительной головки, первый выход которой соединен с первым входом блока цифрового суммирования, первым входом блока управления, первым входом блока тестовых последовательностей, вторым выходом программируемого генератора импульсов, входом-выходом генератора произвольных последовательностей, выходом блока аналого-цифрового преобразователя, первым входом коммутационной матрицы и входом блока задания уровней, выход которого соединен со вторым входом измерительной головки. Первый выход блока цифрового суммирования соединен с третьим входом измерительной головки, второй выход которой соединен со вторым входом блока цифрового суммирования, второй выход которого соединен с четвертым входом измерительной головки. Первый выход блока тестовых последовательностей соединен с первым входом блока памяти ошибок. Второй выход блока тестовых последовательностей соединен с третьим входом блока цифрового суммирования, третий выход которого соединен со вторым входом блока управления, третьим входом блока памяти ошибок и первым входом программируемого генератора импульсов, первый выход которого соединен со вторым входом блока тестовых последовательностей и пятым входом блока памяти ошибок. Первый, второй и третий выходы генератора произвольных последовательностей соответственно соединены с четвертым, пятым и восьмым входами блока цифрового суммирования. Четвертый выход генератора произвольных последовательностей соединен со вторым входом блока памяти ошибок. Группа выходов программируемого генератора импульсов соединена с соответствующей группой входов блока цифрового суммирования. Первый выход блока управления соединен со вторым входом программируемого генератора импульсов, второй выход блока управления соединен с входом блока измерителей источников, первый выход которого соединен со вторым входом блока коммутации. Второй выход блока измерителей-источников соединен с первым входом блока аналого-цифрового преобразователя, вход-выход блока управления соединен с выходом-входом ПЭВМ.

Недостатками известного устройства являются сложность управления для пользователя, поскольку пользователю необходимо приобретение специальных навыков, и невозможность обслуживания (ремонт) пользователем, поскольку известное устройство имеет очень сложную электрическую схему.

Задачей, решаемой предлагаемым изобретением, является создание устройства для функционального контроля однокристального микроконтроллера, обладающего простотой управления для пользователя и возможностью обслуживания.

Технический результат, заключающийся в простоте управления для пользователя и возможности обслуживания, достигается тем, что в устройство для функционального контроля однокристального микроконтроллера, содержащее блок коммутации, первый выход которого соединен с первым входом контролируемого однокристального микроконтроллера, блок постоянных запоминающих устройств тестовых последовательностей, первый выход которого соединен с первым входом блока оперативных запоминающих устройств, персональную электронно-вычислительную машину, блок начальной установки контролируемого однокристального микроконтроллера и шины питания, введены управляющий однокристальный микроконтроллер, постоянное запоминающее устройство управляющего однокристального микроконтроллера, блок начальной установки управляющего однокристального микроконтроллера, блок последовательного интерфейса, блок дешифрации управляющих сигналов, блок формирования адресов для постоянных запоминающих устройств тестовых последовательностей, блок записи в блок оперативных запоминающих устройств, блок чтения из блока оперативных запоминающих устройств, блок формирования адресов для блока оперативных запоминающих устройств и блок индикации, блок постоянных запоминающих устройств тестовых последовательностей снабжен дополнительной группой входов, блок коммутации снабжен двумя дополнительными входами, первый из которых соединен с первой шиной питания, второй дополнительный вход соединен с первым выходом управляющего однокристального микроконтроллера и с первым входом постоянного запоминающего устройства управляющего однокристального микроконтроллера, второй вход и группа входов-выходов постоянного запоминающего устройства управляющего однокристального микроконтроллера соединены соответственно со вторым выходом и группой выходов-входов управляющего однокристального микроконтроллера, первый вход которого соединен с выходом блока начальной установки управляющего однокристального микроконтроллера, вход блока начальной установки управляющего однокристального микроконтроллера соединен со второй шиной питания, второй вход и третий выход управляющего однокристального микроконтроллера соединены с первыми выходом и входом соответственно блока последовательного интерфейса, второй, третий и четвертый входы которого соединены соответственно со второй, третьей и четвертой шинами питания, а пятый вход и второй выход соединены соответственно с выходом и входом персональной электронно-вычислительной машины, первая группа выходов управляющего однокристального микроконтроллера соединена с группой входов блока дешифрации управляющих сигналов, группа выходов которого соединена с группой входов блока коммутации, вход и второй выход которого соединены с первыми выходом и входом соответственно контролируемого однокристального микроконтроллера, третий выход соединен с первым входом блока формирования адресов для постоянных запоминающих устройств тестовых последовательностей, группа выходов которого соединена с группой входов блока постоянных запоминающих устройств тестовых последовательностей, второй вход соединен со вторым входом контролируемого однокристального микроконтроллера и выходом блока начальной установки контролируемого однокристального микроконтроллера, вход блока начальной установки контролируемого однокристального микроконтроллера соединен с первым выходом блока коммутации и первым входом блока индикации, второй вход которого соединен со второй шиной питания, третий вход и вторая группа выходов управляющего однокристального микроконтроллера соединены соответственно со вторым выходом и дополнительной группой входов блока постоянных запоминающих устройств тестовых последовательностей, вход и группа выходов которого соединены соответственно со вторым выходом и группой входов контролируемого однокристального микроконтроллера, третий выход и группа выходов которого соединены соответственно с входом и группой входов блока записи в блок оперативных запоминающих устройств, группа выходов блока записи в блок оперативных запоминающих устройств соединена с первой группой входов блока оперативных запоминающих устройств, второй вход которого соединен с четвертым выходом управляющего однокристального микроконтроллера, первым входом блока формирования адресов для блока оперативных запоминающих устройств и входом блока чтения из блока оперативных запоминающих устройств, группа выходов блока чтения из блока оперативных запоминающих устройств соединена с группой входов управляющего однокристального микроконтроллера, пятый выход и третья группа выходов которого соединены соответственно со вторым входом блока формирования адресов для блока оперативных запоминающих устройств и первой группой входов блока чтения из блока оперативных запоминающих устройств, вторая группа входов блока чтения из блока оперативных запоминающих устройств соединена с группой выходов блока оперативных запоминающих устройств, вторая группа входов которого соединена с группой выходов блока формирования адресов для блока оперативных запоминающих устройств, третий вход блока формирования адресов для блока оперативных запоминающих устройств соединен с первым входом блока оперативных запоминающих устройств.

Указанная совокупность признаков позволяет достичь простоты управления для пользователя за счет возможности сравнения, обработки и отображения полученной информации и возможности обслуживания за счет простоты схемы.

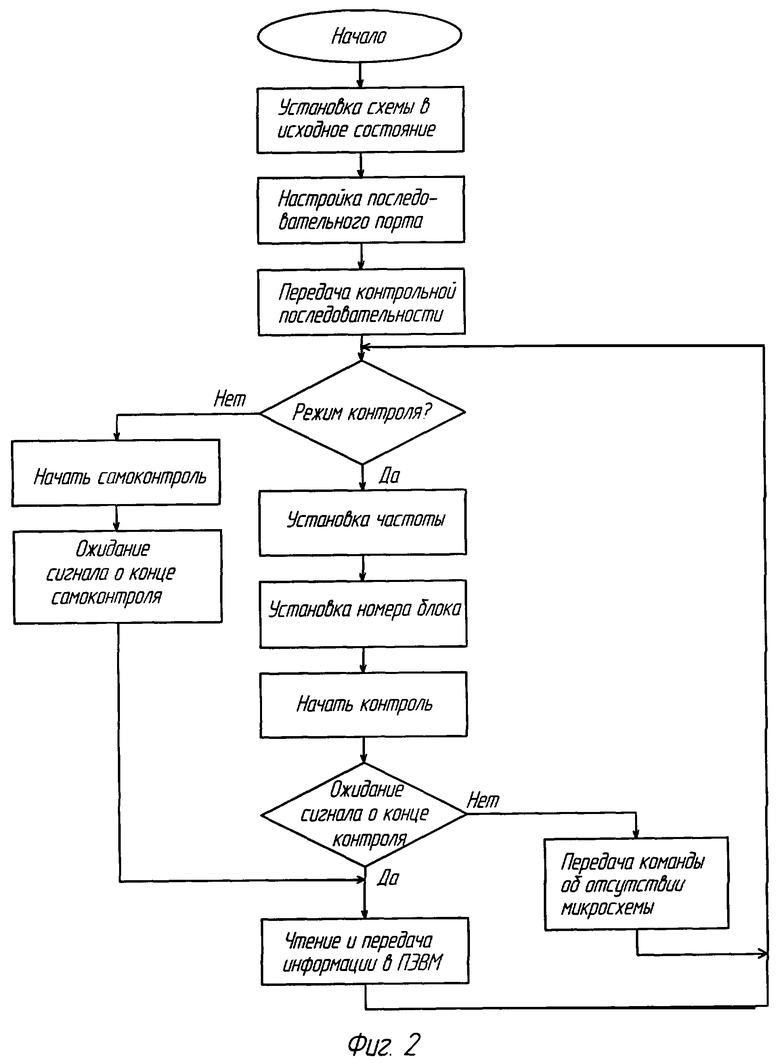

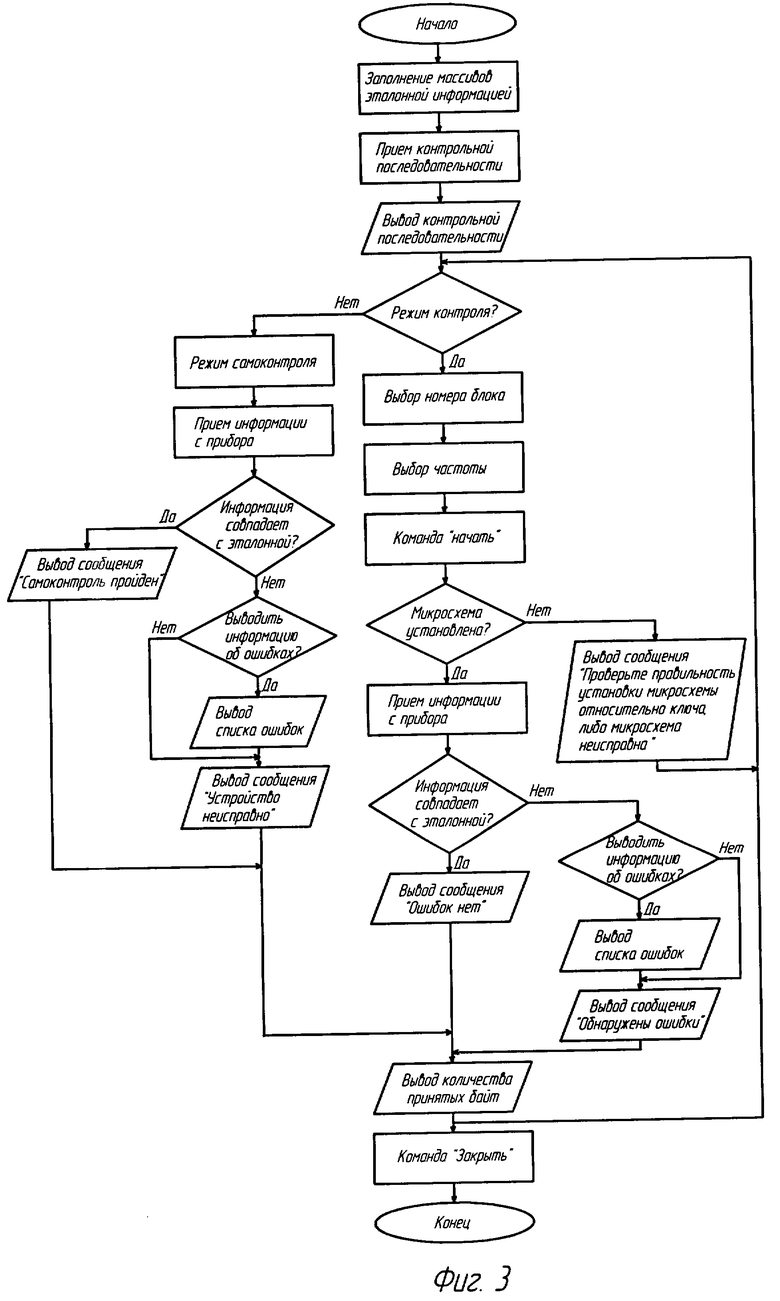

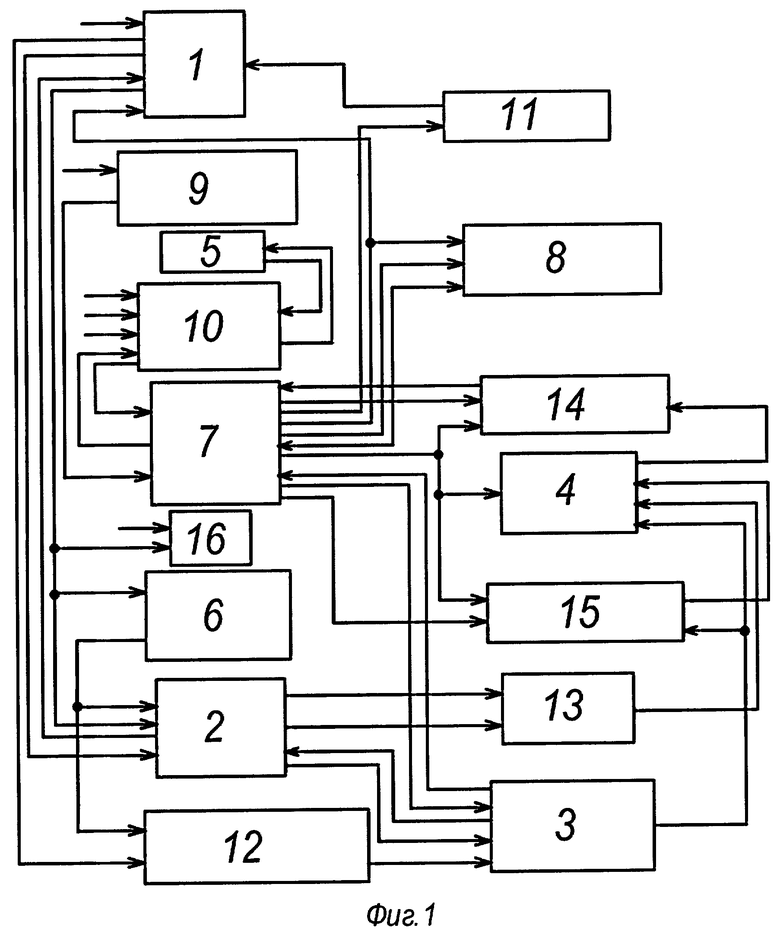

На фиг.1 приведена функциональная схема устройства для функционального контроля однокристального микроконтроллера; на фиг.2 и 3 приведены блок-схемы алгоритма работы соответственно управляющего однокристального микроконтроллера и ПЭВМ.

Устройство для функционального контроля однокристального микроконтроллера содержит (фиг.1) блок 1 коммутации (БК), контролируемый однокристальный микроконтроллер 2 (КОМ), блок 3 постоянных запоминающих устройств тестовых последовательностей (БПЗУТП), блок 4 оперативных запоминающих устройств (БОЗУ), ПЭВМ 5, блок 6 начальной установки контролируемого однокристального микроконтроллера (БНУКОМ), управляющий однокристальный микроконтроллер 7 (УОМ), постоянное запоминающие устройство 8 управляющего однокристального микроконтроллера (ПЗУУОМ), блок 9 начальной установки управляющего однокристального микроконтроллера (БНУУОМ), блок 10 последовательного интерфейса (БПИ), блок 11 дешифрации управляющих сигналов (БДУС), блок 12 формирования адресов для постоянных запоминающих устройств тестовых последовательностей (БФАДПЗУТП), блок 13 записи в блок оперативных запоминающих устройств (БЗВБОЗУ), блок 14 чтения из блока оперативных запоминающих устройств (БЧИБОЗУ), блок 15 формирования адресов для блока оперативных запоминающих устройств (БФАДБОЗУ) и блок 16 индикации (БИ).

Первый выход БК 1 соединен с первым входом КОМ 2. Первый выход БПЗУТП 3 соединен с первым входом БОЗУ 4. Первый вход БК 1 соединен с первой шиной 17 питания. Второй вход БК 1 соединен с первым выходом УОМ 7 и с первым входом ПЗУУОМ 8. Второй вход и группа входов-выходов ПЗУУОМ 8 соединены соответственно со вторым выходом и группой выходов-входов УОМ 7. Первый вход УОМ 7 соединен с выходом БНУУОМ 9. Вход БНУУОМ 9 соединен со второй шиной 18 питания. Второй вход и третий выход УОМ 7 соединены соответственно с первыми выходом и входом БПИ 10. Второй, третий и четвертый входы БПИ 10 соединены соответственно с шиной 18 питания, третьей шиной 19 питания и четвертой шиной 20 питания, а пятый вход и второй выход соединены соответственно с выходом и входом ПЭВМ 5. Первая группа выходов УОМ 7 соединена с группой входов БДУС 11. Группа выходов БДУС 11 соединена с группой входов БК 1. Вход и второй выход БК 1 соединены с первыми выходом и входом соответственно КОМ 2. Третий выход БК 1 соединен с первым входом БФАДПЗУТП 12. Группа выходов БФАДПЗУТП 12 соединена с группой входов БПЗУТП 3. Второй вход БФАДПЗУТП 12 соединен со вторым входом КОМ 2 и выходом БНУКОМ 6. Вход БНУКОМ 6 соединен с первым выходом БК 1 и первым входом БИ 16. Второй вход БИ 16 соединен с шиной 18 питания. Третий вход и вторая группа выходов УОМ 7 соединены соответственно со вторым выходом и дополнительной группой входов БПЗУТП 3. Вход и группа выходов БПЗУТП 3 соединены соответственно со вторым выходом и группой входов КОМ 2. Третий выход и группа выходов КОМ 2 соединены соответственно с входом и группой входов БЗВБОЗУ 13. Группа выходов БЗВБОЗУ 13 соединена с первой группой входов БОЗУ 4. Второй вход БОЗУ 4 соединен с четвертым выходом УОМ 7, первым входом БФАДБОЗУ15 и входом БЧИБОЗУ 14. Группа выходов БЧИБОЗУ 14 соединена с группой входов УОМ 7. Пятый выход и третья группа выходов УОМ 7 соединены соответственно со вторым входом БФАДБОЗУ 15 и первой группой входов БЧИБОЗУ 14. Вторая группа входов БЧИБОЗУ 14 соединена с группой выходов БОЗУ 4. Вторая группа входов БОЗУ 4 соединена с группой выходов БФАДБОЗУ 15. Третий вход БФАДБОЗУ 15 соединен с первым входом БОЗУ 4.

БК 1 может быть выполнен на трех реле РПС45, двух микросхемах 1109КТ4Б и шести диодах 2Д510А, при этом выходы микросхемы 1109КТ4Б подключены к отрицательным полюсам обмоток реле, диоды подключены параллельно обмоткам реле, причем катоды диодов подключены к положительному полюсу обмотки соответствующего реле. КОМ 2 может быть выполнен на микросхеме Н1830ВЕ31, кварцевом резонаторе и двух конденсаторах, при этом к выводам кварцевого резонатора подключаются два конденсатора, вторые выводы которых подключаются к шине "земля", в свою очередь выводы кварцевого резонатора подключаются на входы микросхемы Н1830ВЕ31 XI и Х2. БПЗУТП 3 может быть выполнен на двух микросхемах 27С512 и регистре 555ИР22, при этом шина данных первой микросхемы 27С512 подключается к информационным входам регистра 555ИР22. БОЗУ 4 может быть выполнен на четырех микросхемах КР537РУ10. ПЭВМ 5 может быть выполнена на ЭВМ типа IBM PC с операционной системой Windows 95/98, Windows NT 4.0 или Windows 2000. БНУКОМ 6 может быть выполнен на микросхемах 564ТЛ1, 564ЛА10 и интегрирующей цепочки из резистора и конденсатора, при этом выход интегрирующей цепочки подключается к первому входу микросхемы 564ТЛ1, первый выход микросхемы 564ТЛ1 подключается ко второму входу микросхемы 564ТЛ1, второй выход микросхемы 564ТЛ1 подключается к входу микросхемы 564ЛА10. УОМ 7 может быть выполнен на микросхеме Н1830ВЕ31, кварцевом резонаторе и двух конденсаторах, при этом к выводам кварцевого резонатора подключаются два конденсатора, вторые выводы которых подключаются к шине "земля", в свою очередь выводы кварцевого резонатора подключаются на входы микросхемы Н1830ВЕ31 XI и Х2. ПЗУУОМ 8 может быть выполнен на микросхемах К573РФ2 и регистре 555ИР22, при этом шина адресов микросхемы К573РФ2 подключается к выходам регистра 555ИР22. БНУУОМ 9 может быть выполнен на микросхемах 564ТЛ1, 564ЛА10 и интегрирующей цепочке из резистора и конденсатора, при этом выход интегрирующей цепочки подключается к первому входу микросхемы 564ТЛ1, первый выход микросхемы 564ТЛ1 подключается ко второму входу микросхемы 564ТЛ1, второй выход микросхемы 564ТЛ1 подключается к входу микросхемы 564ЛА10. БПИ 10 может быть выполнен по схеме, представленной в книге "Искусство схемотехники" Хоровица п.и Хилла У., издательство "МИР", 1998 г. стр.630, 631 рис.9.31. БДУС 11 может быть выполнен на микросхемах 555ИД7 и 555ЛН1, при этом выходы дешифратора 555ИД7 инвертируются через элементы ИЛИ-НЕ микросхем 555ЛН1. БФАПЗУТП 12 может быть выполнен на трех двоичных счетчиках 555ИЕ5, включенных между собой последовательно. БЗВБОЗУ 13 может быть выполнен на трех микросхемах 555ИР22 и на микросхеме 555ИР23. БЧИБОЗУ 14 может быть выполнен на микросхемах ИЛИ-НЕ 555ЛН1, 2 И-НЕ 555ЛАЗ и четырех регистрах 555ИР22, при этом выход ИЛИ-НЕ подключается к входу каждого из четырех вентилей 2И-НЕ, а четыре выхода микросхемы 2И-НЕ подключаются соответственно к выводу "Разрешение выхода" каждого из четырех регистров 555ИР22. БФАДБОЗУ 15 может быть выполнен на микросхемах 2 И-НЕ 555ЛАЗ и трех двоичных счетчиках 555ИЕ5, при этом выход элемента 2 И-НЕ подключен к счетному входу первого счетчика, все счетчики 555ИЕ5 включены между собой последовательно. БИ 16 может быть выполнен на двух светодиодах 3Л341Г и двух резисторах, при этом катоды светодиодов подключены к резисторам, вторые выводы обоих резисторов подключаются к шине "земля". Выполнение блоков на фиг.1 не показано.

Устройство для функционального контроля однокристального микроконтроллера работает следующим образом.

Запускается на выполнение программа на ПЭВМ 5, блок-схема программы представлена на фиг.3. Программа обеспечивает выбор режимов работы, выдачу на устройство соответствующих управляющих команд, прием информации от устройства и сравнение ее с эталонной. Режимы работы включают самоконтроль устройства и контроль при выбранной частоте и номере блока тестовых данных.

Включается питание устройства. БИ 16 показывает, что питание включено, а БНУУОМ 9 формирует сбросной сигнал для УОМ 7. Далее УОМ 7 постоянно обращается к ПЗУУОМ 8 для чтения программы, которая представлена в виде блок-схемы на фиг.2. Программа обеспечивает работу устройства в зависимости от выбранного режима, передачу на ПЭВМ 5 информации от устройства для сравнения ее с эталонной. Режимы работы включают самоконтроль устройства и контроль при выбранной частоте и номере блока тестовых данных. Режимы работы выбираются по команде от ПЭВМ 5.

УОМ 7 выдает контрольную последовательность в БПИ 10, которая сигнализирует о готовности прибора. БПИ 10, в свою очередь, транслирует эту последовательность в ПЭВМ 5. В режиме контроля (самоконтроля) ПЭВМ 5 дает команду на контроль (самоконтроль) УОМ 7 через БПИ 10. УОМ 7 формирует сигналы для БФАДБОЗУ 15 (приводя тем самым его в исходное состояние), БДУС 11, который, в свою очередь, дешифрирует их для БК 1. БК 1 подает сигналы для БИ 16 (который выдает индикацию о режиме контроль), КОМ 2, БФАДПЗУТП 12 и БНУКОМ 6. БНУКОМ 6 формирует сигнал сброса для КОМ 2. КОМ 2 начинает выполнять тестовую программу, которая находится в БПЗУТП 3. Адреса для БПЗУТП 3 приходят с БФАДПЗУТП 12. Состояния всех четырех портов КОМ 2 защелкиваются в БЗВБОЗУ 13, а далее происходит их запись в БОЗУ 4 по сигналу записи из БПЗУТП 3. Адреса для БОЗУ 4 приходят с БФАДБОЗУ 15. УОМ 7 ждет сигнала о конце контроля от БПЗУТП 3. Как только УОМ 7 получает этот сигнал, он формирует сигналы для БФАДБОЗУ 15 (приводя тем самым его в исходное состояние), БДУС 11, который, в свою очередь, дешифрирует их для БК 1. БК 1 снимает питание с КОМ 2 и подает сигнал для БИ 16 (который снимает индикацию о контроле). На следующем этапе УОМ 7 читает сохраненные данные в БОЗУ 4. Обращение УОМ 7 к БОЗУ 4 происходит через БЧИБОЗУ 4. При этом УОМ 7 подает сигнал и на БФАДБОЗУ 15. БФАДБОЗУ 15 формирует адреса для БОЗУ 4. УОМ 7 после чтения каждого байта сохраненных данных в БОЗУ 4 транслирует его в ПЭВМ 5 через БПИ 10. После получения всей информации программа на ПЭВМ 5 обрабатывает ее и выдает визуальный результат о проверенном микроконтроллере. Далее можно провести контроль для другого микроконтроллера.

Таким образом, описание работы подтверждает работоспособность заявляемого устройства. Простота управления для пользователя достигается за счет возможности сравнения, обработки и отображения полученной информации. Возможность обслуживания достигается за счет простоты схемы. Кроме того, устройство имеет малые ГМХ за счет замены морально-устаревшей элементной базы на новую.

Изготовлен опытный образец, испытания которого подтвердили осуществимость и практическую ценность заявляемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОНТРОЛЯ ОДНОКРИСТАЛЬНОГО МИКРОКОНТРОЛЛЕРА | 2003 |

|

RU2248606C1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Способ компенсации фазовых искажений в многоканальных системах аналого-цифрового преобразования сигналов и устройство для его реализации | 2019 |

|

RU2723566C1 |

| Внутрисхемный эмулятор | 1988 |

|

SU1615715A1 |

| УПРАВЛЯЮЩАЯ ЭВМ | 2005 |

|

RU2316807C2 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ИНФОРМАЦИИ | 1996 |

|

RU2097703C1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| ЦИФРОВОЙ РЕГУЛЯТОР ДЛЯ МНОГОДВИГАТЕЛЬНОГО ЭЛЕКТРОПРИВОДА | 1992 |

|

RU2071635C1 |

| МНОГОМАШИННАЯ СИСТЕМА УПРАВЛЕНИЯ | 2006 |

|

RU2320003C2 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в автоматизированных системах для контроля микроЭВМ, содержащих цифровые входы-выходы. Его использование позволяет получить технический результат в виде упрощения управления для пользователя и обслуживания. Технический результат достигается за счет того, что в устройство для функционального контроля однокристального микроконтроллера, содержащее блок коммутации, блок постоянных запоминающих устройств тестовых последовательностей, блок оперативных запоминающих устройств, ПЭВМ и блок начальной установки контролируемого однокристального микроконтроллера, дополнительно введены управляющий однокристальный микроконтроллер, постоянное запоминающее устройство управляющего однокристального микроконтроллера, блок начальной установки управляющего однокристального микроконтроллера, блок последовательного интерфейса, блок дешифрации управляющих сигналов, блок формирования адресов для постоянных запоминающих устройств тестовых последовательностей, блок записи в блок оперативных запоминающих устройств, блок чтения из блока оперативных запоминающих устройств, блок формирования адресов для блока оперативных запоминающих устройств и блок индикации. 3 ил.

Устройство для функционального контроля однокристального микроконтроллера, содержащее блок коммутации, первый выход которого соединен с первым входом контролируемого однокристального микроконтроллера, блок постоянных запоминающих устройств тестовых последовательностей, первый выход которого соединен с первым входом блока оперативных запоминающих устройств, персональную электронно-вычислительную машину, блок начальной установки контролируемого однокристального микроконтроллера и шины питания, отличающееся тем, что в него введены управляющий однокристальный микроконтроллер, постоянное запоминающее устройство управляющего однокристального микроконтроллера, блок начальной установки управляющего однокристального микроконтроллера, блок последовательного интерфейса, блок дешифрации управляющих сигналов, блок формирования адресов для постоянных запоминающих устройств тестовых последовательностей, блок записи в блок оперативных запоминающих устройств, блок чтения из блока оперативных запоминающих устройств, блок формирования адресов для блока оперативных запоминающих устройств и блок индикации, блок постоянных запоминающих устройств тестовых последовательностей снабжен дополнительной группой входов, блок коммутации снабжен двумя дополнительными входами, первый из которых соединен с первой шиной питания, второй дополнительный вход соединен с первым выходом управляющего однокристального микроконтроллера и с первым входом постоянного запоминающего устройства управляющего однокристального микроконтроллера, второй вход и группа входов-выходов постоянного запоминающего устройства управляющего однокристального микроконтроллера соединены, соответственно, со вторым выходом и группой выходов-входов управляющего однокристального микроконтроллера, первый вход которого соединен с выходом блока начальной установки управляющего однокристального микроконтроллера, вход блока начальной установки управляющего однокристального микроконтроллера соединен со второй шиной питания, второй вход и третий выход управляющего однокристального микроконтроллера соединены с первыми выходом и входом, соответственно, блока последовательного интерфейса, второй, третий и четвертый входы которого соединены, соответственно, со второй, третьей и четвертой шинами питания, а пятый вход и второй выход соединены, соответственно, с выходом и входом персональной электронно-вычислительной машины, первая группа выходов управляющего однокристального микроконтроллера соединена с группой входов блока дешифрации управляющих сигналов, группа выходов которого соединена с группой входов блока коммутации, вход и второй выход которого соединены с первыми выходом и входом, соответственно, контролируемого однокристального микроконтроллера, третий выход соединен с первым входом блока формирования адресов для постоянных запоминающих устройств тестовых последовательностей, группа выходов которого соединена с группой входов блока постоянных запоминающих устройств тестовых последовательностей, второй вход соединен со вторым входом контролируемого однокристального микроконтроллера и выходом блока начальной установки контролируемого однокристального микроконтроллера, вход блока начальной установки контролируемого однокристального микроконтроллера соединен с первым выходом блока коммутации и первым входом блока индикации, второй вход которого соединен со второй шиной питания, третий вход и вторая группа выходов управляющего однокристального микроконтроллера соединены, соответственно, со вторым выходом и дополнительной группой входов блока постоянных запоминающих устройств тестовых последовательностей, вход и группа выходов которого соединены, соответственно, со вторым выходом и группой входов контролируемого однокристального микроконтроллера, третий выход и группа выходов которого соединены, соответственно, с входом и группой входов блока записи в блок оперативных запоминающих устройств, группа выходов блока записи в блок оперативных запоминающих устройств соединена с первой группой входов блока оперативных запоминающих устройств, второй вход которого соединен с четвертым выходом управляющего однокристального микроконтроллера, первым входом блока формирования адресов для блока оперативных запоминающих устройств и входом блока чтения из блока оперативных запоминающих устройств, группа выходов блока чтения из блока оперативных запоминающих устройств соединена с группой входов управляющего однокристального микроконтроллера, пятый выход и третья группа выходов которого соединены, соответственно, со вторым входом блока формирования адресов для блока оперативных запоминающих устройств и первой группой входов блока чтения из блока оперативных запоминающих устройств, вторая группа входов блока чтения из блока оперативных запоминающих устройств соединена с группой выходов блока оперативных запоминающих устройств, вторая группа входов которого соединена с группой выходов блока формирования адресов для блока оперативных запоминающих устройств, третий вход блока формирования адресов для блока оперативных запоминающих устройств соединен с первым входом блока оперативных запоминающих устройств.

| Устройство для контроля микроЭВМ | 1988 |

|

SU1578716A1 |

Авторы

Даты

2004-07-10—Публикация

2002-05-27—Подача