Изобретение относится к информационно-вычислительной технике и технической кибернетике и может быть использовано в цифровых информационно-вычислительных системах, предназначенных для обработки двумерных массивов информации, в частности для цифровой обработки изображений.

Известны запоминающие устройства изображений (ЗУИ), содержащие шинный формирователь, блок местного управления, блок оперативной памяти, формирователь сигналов управления, мультиплексор адреса, формирователь импульсов и задающий генератор. Это ЗУИ обеспечивает автоматическую регенерацию информации, обмен информацией с ЭВМ в режимах с фиксированной ячейкой памяти автоинкрементированием и автодекрементированием адреса ячейки памяти, защиту хранящихся в ОЗУ данных по периметру (1 контрольный бит на шестнадцатиразрядное слово), возможность работы в режиме прерывания программы при возникновении ошибки паритета в режиме чтения данных, исправление однобитовой ошибки и выработку сигнала многобитовой ошибки программным путем. Программное обеспечение эксплуатируется в среде операицонной системы ОС ДВК и включает драйвер и тест-программу проверки ОЗУ.

Однако ЗУИ имеет низкую эффективность (25 50) использование памяти из-за преимущественного применения в устройствах обработки изображений четырехразрядного формата слова, невозможность ("неестественность") представления видеоинформации в удобном виде ("строками", "столбцами", "кадрами"), необходимость программного обеспечения на гибких магнитных дисках (ГМД) в среде операционной системе (ОС) ДВК, наличие нестандартных размеров, требующих отдельного корпуса и выносного кабеля с разъемом.

Наиболее близким к изобретению является контроллер динамического ОЗУ, содержащий три элемента И-НЕ, три элемента ИЛИ, три элемента НЕ, элемент И, счетчик адресов регенерации, коммутатор адреса, одновибратор, дешифратор, триггер обращения регенерации. Это устройство способно работать в ждущем режиме. Контроллер реализует обращения к ОЗУ в режимах чтения и записи и периодической регенерации информации ОЗУ. При этом регенерация обеспечивается в обычном режиме выполнения программы, состояниях ОЖИДАНИЕ, ОСТАНОВ и блокировки обращений к ОЗУ. Период регенерации, в котором количество циклов регенерации равно количеству обращений к ОЗУ, зависит от конкретной программы. Устройство работает следующим образом.

При отсутствии сигналов "Ожидание" и "Блокировка" на выходы разрядов адреса АО.А6 ОЗУ устрйоства поступают адреса строк, формируемые счетчиком адресов регенерации. Сигналы  и

и  не вырабатываются. Регенерация осуществляется по сигналу

не вырабатываются. Регенерация осуществляется по сигналу  , который вырабатывается одновибратором.

, который вырабатывается одновибратором.

С поступлением сигнала "4m" или "3n" регенерация приостанавливается. Адрес следующей строки, подлежащей регенерации, запоминается в счетчике адресов регенерации. На выходы разрядов адреса АО. А6 ОЗУ поступают младшие (А0 А6), а затем старшие (А7 А13) разряды адреса. Младшие разряды сопровождаются сигналом  , а старшие одним из сигналов

, а старшие одним из сигналов  0.CAS3 в зависимости от значения разрядов адреса А14 и А15. Если обращение к ОЗУ происходит в режиме записи (присутствует сигнал "3n"), то одновременно с одним из сигналов

0.CAS3 в зависимости от значения разрядов адреса А14 и А15. Если обращение к ОЗУ происходит в режиме записи (присутствует сигнал "3n"), то одновременно с одним из сигналов  0.

0. 3 вырабатывается соответствующий ему сигнал

3 вырабатывается соответствующий ему сигнал  0.

0. 3. На этом цикл обращения к ОЗУ завершается и устрйоство переходит в режим регенерации со строки ранее запомненной в счетчике адресов регенерации.

3. На этом цикл обращения к ОЗУ завершается и устрйоство переходит в режим регенерации со строки ранее запомненной в счетчике адресов регенерации.

В состояниях "Ожидание" и "Останов", характерных наличием сигнала "Ожидание", регенерация ОЗУ осуществляется с тактовой частотой МПУ.

Недостатки известного устрйоства заключаются в следующем:

ограниченность адресного пространства (4 блока по 16 К или 4 кадра размерностью 128х128);

отсутствие возможности автономной регенерации (регенерация осуществляется микропроцессором);

отсутствие возможности запоминания информации (нет блока оперативной памяти);

работа в асинхронном режиме; требование строгого соблюдения временных соотношений между сигналами обращения к памяти и тактовым сигналом (в основном устройство рассчитано на применение в МПУ, построенных с использованием системного контроллера К580ВК38 и тактового генератора К580ГФ24).

Целью изобретения является расширение функциональных возможностей за счет совместимости с единым каналом семейства микроЭВМ "Электроника-60", обеспечения запоминания изображений, использования синхронного режима работы и расширения адресного пространства.

Поставленная цель достигается тем, что в устройство, содержащее мультиплексор адреса, информационные входы первой группы которого соединены с информационными входом и выходом счетчика адресов строк регенерации, вход записи которого соединен с одним из выходов триггера регенерации и со входом формирователя сигнала  , один из выходов которого соединен с управляющим входом мультиплексора адреса, отдельный вход счетчика адресов строк регенерации соединен с другим входом формирователя сигналов

, один из выходов которого соединен с управляющим входом мультиплексора адреса, отдельный вход счетчика адресов строк регенерации соединен с другим входом формирователя сигналов  , дополнительно введены шинный формирователь, регистр адреса строк, регистр адреса столбцов, регистр адреса кадра, блок местного управления, генератор тактовых импульсов, формирователь сигналов разрешения

, дополнительно введены шинный формирователь, регистр адреса строк, регистр адреса столбцов, регистр адреса кадра, блок местного управления, генератор тактовых импульсов, формирователь сигналов разрешения  и

и  , формирователь сигналов

, формирователь сигналов  , блок оперативной памяти и формирователь сигналов

, блок оперативной памяти и формирователь сигналов  , при этом выходы шинного формирователя соединены с входами регистров адреса строк, столбцов, кадра, а также блока местного управления и блока оперативной памяти, выходы местного блока управления соединены с другими входами регистров адреса строк, столбцов, кадра, выходы регистров адреса строк и столбцов соединены соответственно с второй и третьей группами информационных входов мультиплексора адреса, отдельный выход блока местного управления соединен с одним из входов триггера регенерации, одним из входов формирователя сигналов разрешения

, при этом выходы шинного формирователя соединены с входами регистров адреса строк, столбцов, кадра, а также блока местного управления и блока оперативной памяти, выходы местного блока управления соединены с другими входами регистров адреса строк, столбцов, кадра, выходы регистров адреса строк и столбцов соединены соответственно с второй и третьей группами информационных входов мультиплексора адреса, отдельный выход блока местного управления соединен с одним из входов триггера регенерации, одним из входов формирователя сигналов разрешения  и

и  и одним из входов формирователя сигналов

и одним из входов формирователя сигналов  , два отдельных выхода блока местного управления соединены с входами шинного формирователя, отдельный вход блока местного управления соединен с другими входами формирователя сигналов

, два отдельных выхода блока местного управления соединены с входами шинного формирователя, отдельный вход блока местного управления соединен с другими входами формирователя сигналов  , формирователя сигналов

, формирователя сигналов  и с выходом формирователя сигналов разрешения

и с выходом формирователя сигналов разрешения  и

и  , а отдельный выход блока местного управления подключен к одному из входов формирователя

, а отдельный выход блока местного управления подключен к одному из входов формирователя  , отдельный вход которого соединен с выходом регистра адреса кадра и одним из входов формирователя сигналов

, отдельный вход которого соединен с выходом регистра адреса кадра и одним из входов формирователя сигналов  , а выход формирователя сигналов

, а выход формирователя сигналов  соединен с одним из входов блока оперативной памяти, два других входа которого соединены с выходами формирователей сигналов RAS и

соединен с одним из входов блока оперативной памяти, два других входа которого соединены с выходами формирователей сигналов RAS и  , отдельный вход блока оперативной памяти соединен с выходом мультиплексора адреса, а выход блока оперативной памяти соединен с входом шинного формирователя, при этом генератор тактовых импульсов соединен с одним из входов формирователя сигналов

, отдельный вход блока оперативной памяти соединен с выходом мультиплексора адреса, а выход блока оперативной памяти соединен с входом шинного формирователя, при этом генератор тактовых импульсов соединен с одним из входов формирователя сигналов  , с одним из входов формирователя сигналов разрешения

, с одним из входов формирователя сигналов разрешения  и

и  и одним из входов триггера регенерации, другой выход которого соединен с отдельным входом формирователя сигналов разрешения

и одним из входов триггера регенерации, другой выход которого соединен с отдельным входом формирователя сигналов разрешения  и

и  и информационным входом четвертой группы мультиплексора адреса.

и информационным входом четвертой группы мультиплексора адреса.

Сопоставительный анализ прототипа и предлагаемого технического решения позволяет заключить, что техническое решение соответствует критерию "новизны".

В известных устройствах, решающих задачу считывания и запоминания изображения (видеоинформации), либо запоминается информация с большим форматом слова (шестнадцатиразрядные), либо запоминается малый объем информации, либо эти устройства не могут работать в составе любой микроЭВМ семейства "Электроника-60" независимо от быстродействия применяемого процессора (ЭВМ), либо они (устройства) требуют доукомплектации (дооснащения) оперативными запоминающими устройствами.

Введение шинного формирователя и блока местного управления обеспечивают совместимость с единым каналом семейства микроЭВМ "Электроника-60", введение блока оперативной памяти запоминание изображения, введение формирователя сигналов разрешения  и

и  и генератора тактовых импульсов синхронный режим работы, и регистры адресов строк, столбцов и кара, формирователи сигналов

и генератора тактовых импульсов синхронный режим работы, и регистры адресов строк, столбцов и кара, формирователи сигналов  и

и  позволяют расширить адресное пространство. Каждый из вновь введенных блоков выполняют присущие им функции, но в заявляемой совокупности проявляют и новые свойства. Достижение такого эффекта позволяет считать предлагаемое техническое решение соответствующим критерию "существенные отличия".

позволяют расширить адресное пространство. Каждый из вновь введенных блоков выполняют присущие им функции, но в заявляемой совокупности проявляют и новые свойства. Достижение такого эффекта позволяет считать предлагаемое техническое решение соответствующим критерию "существенные отличия".

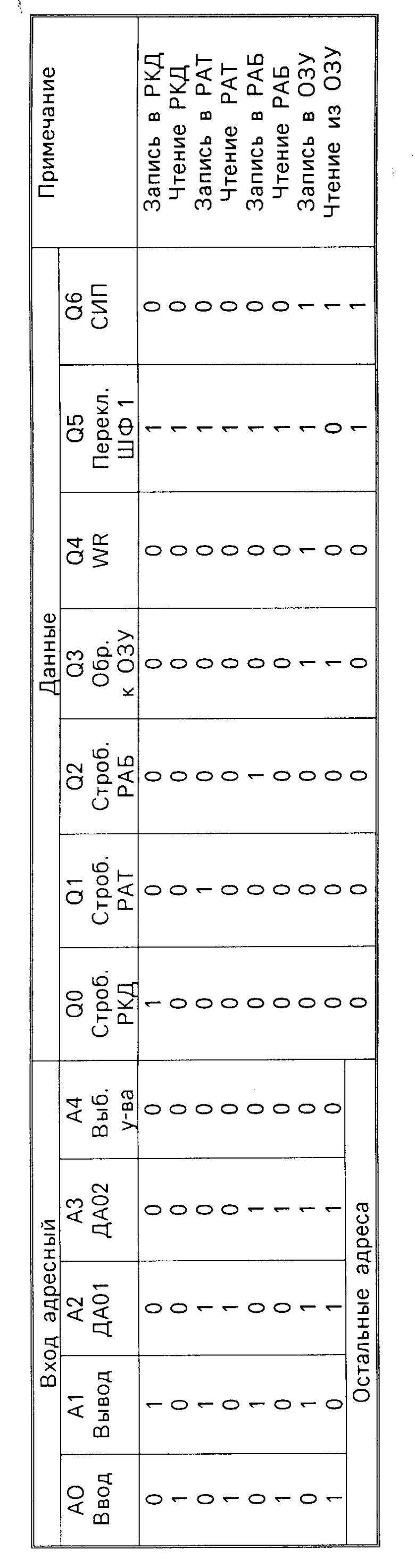

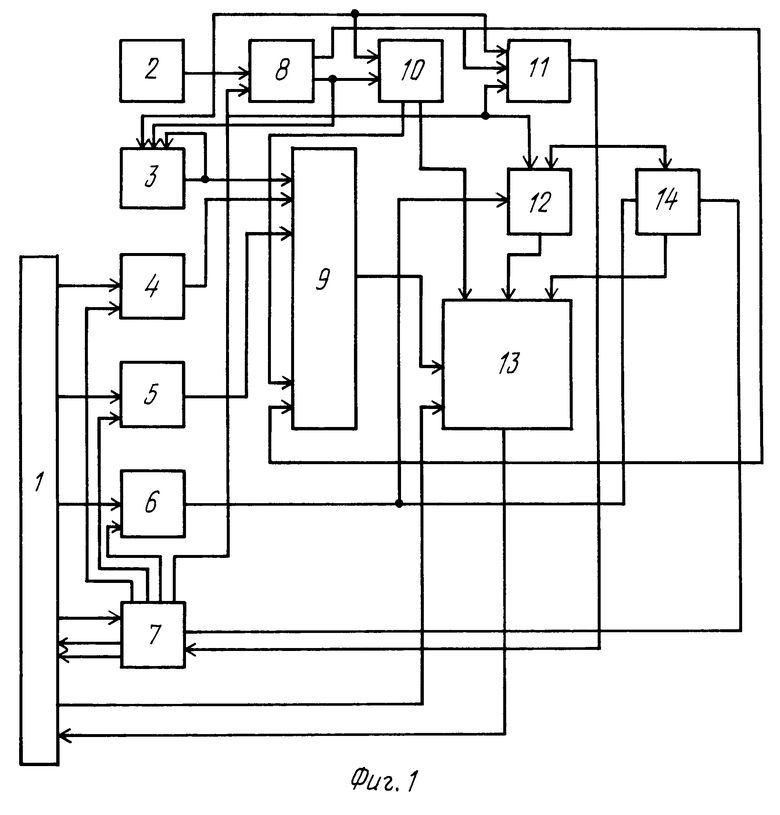

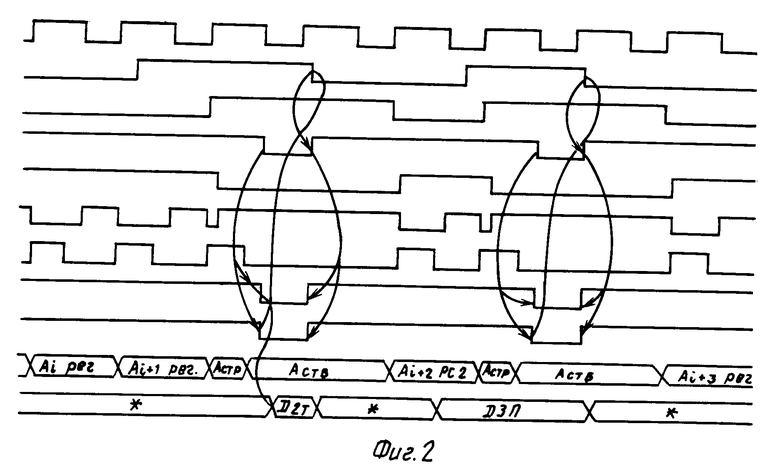

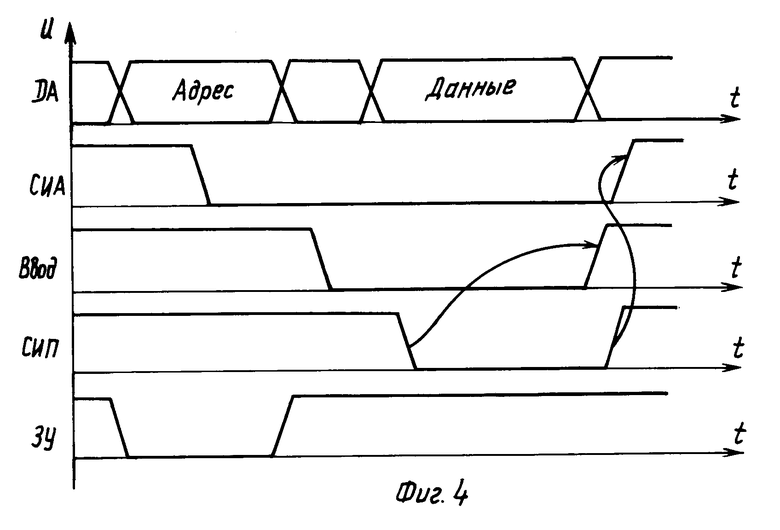

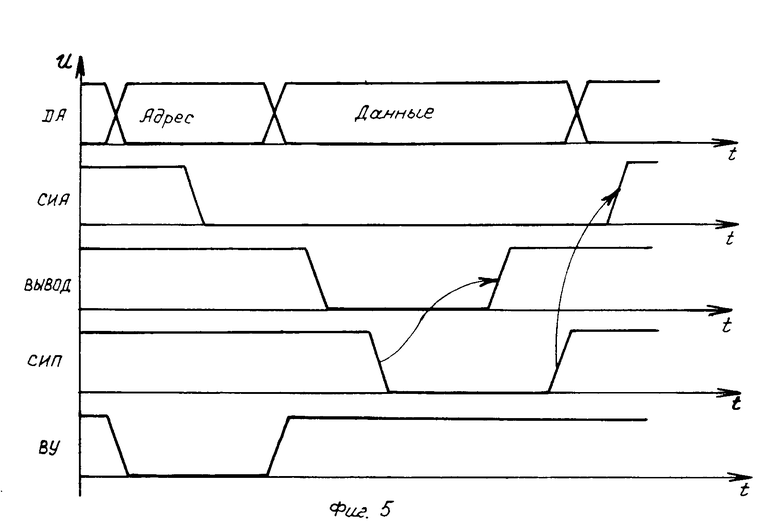

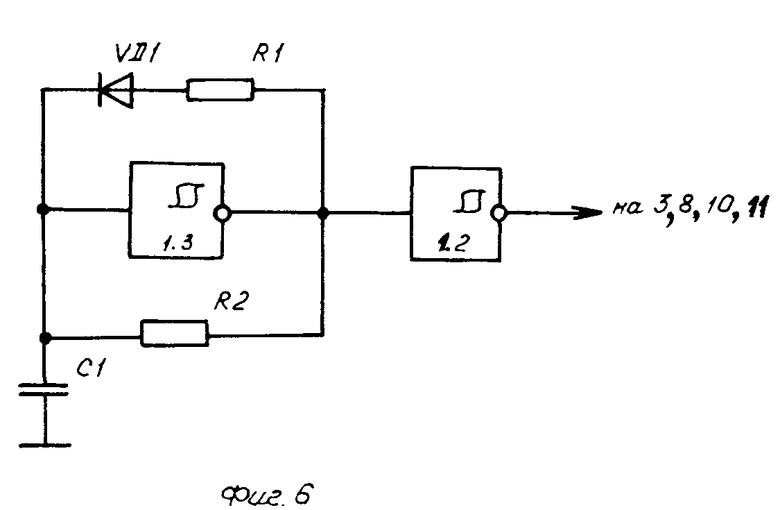

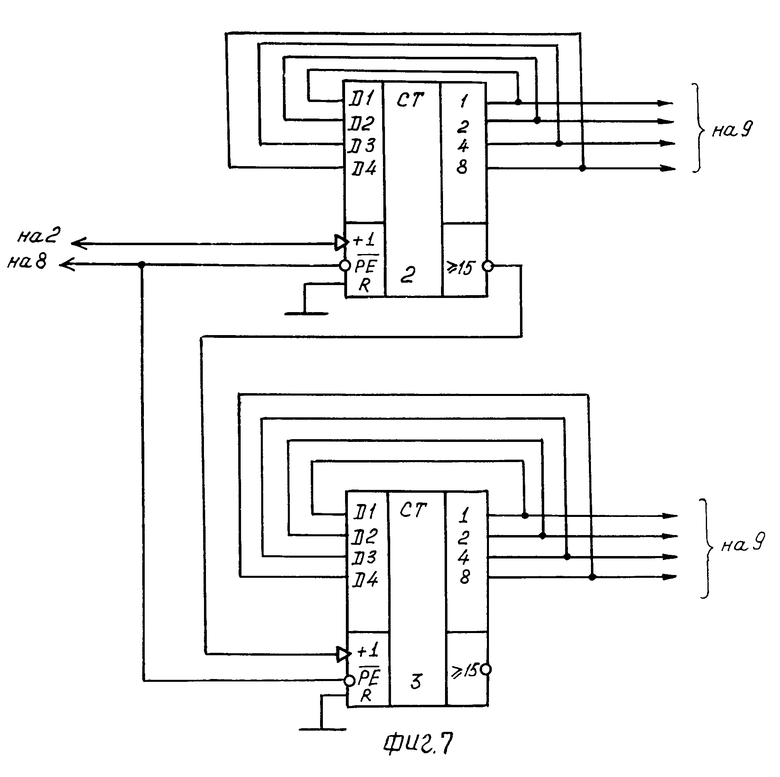

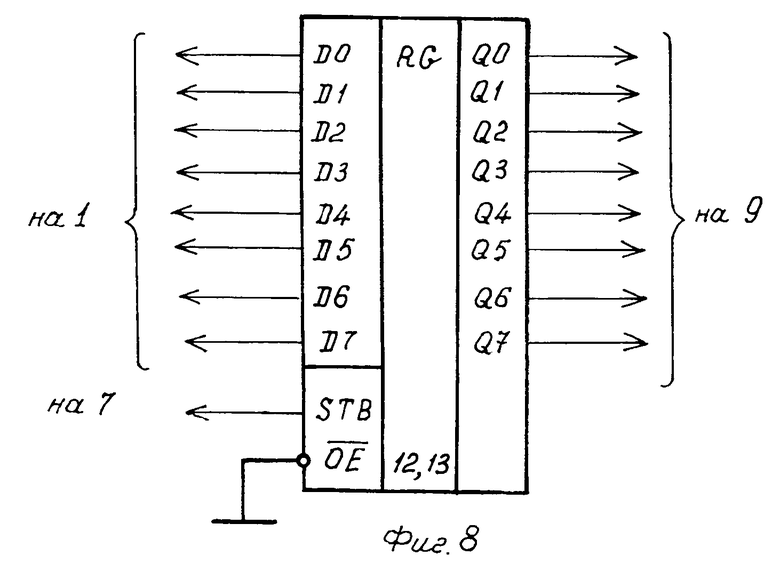

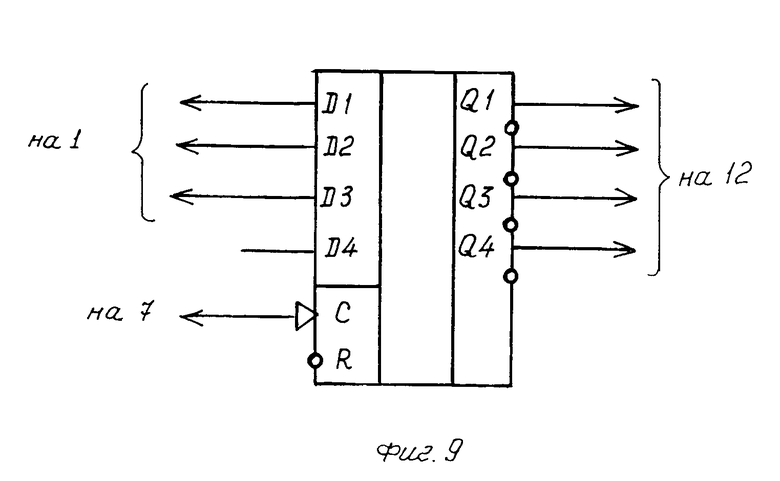

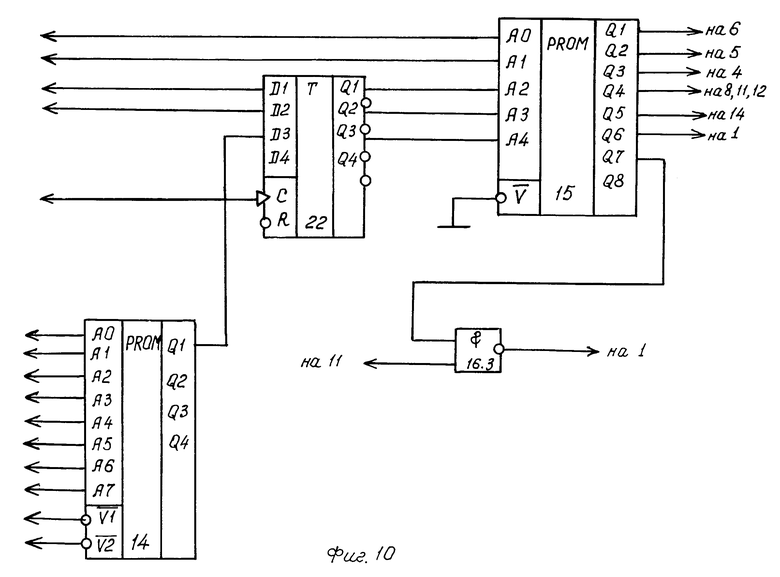

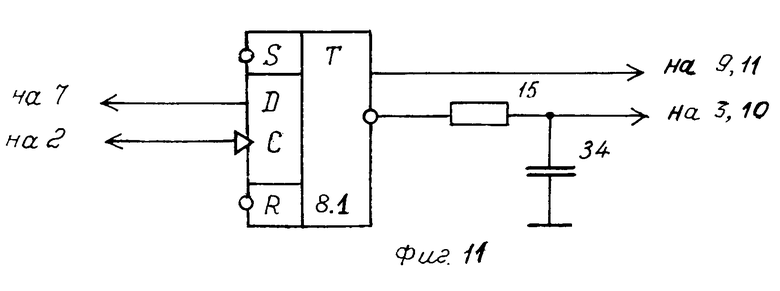

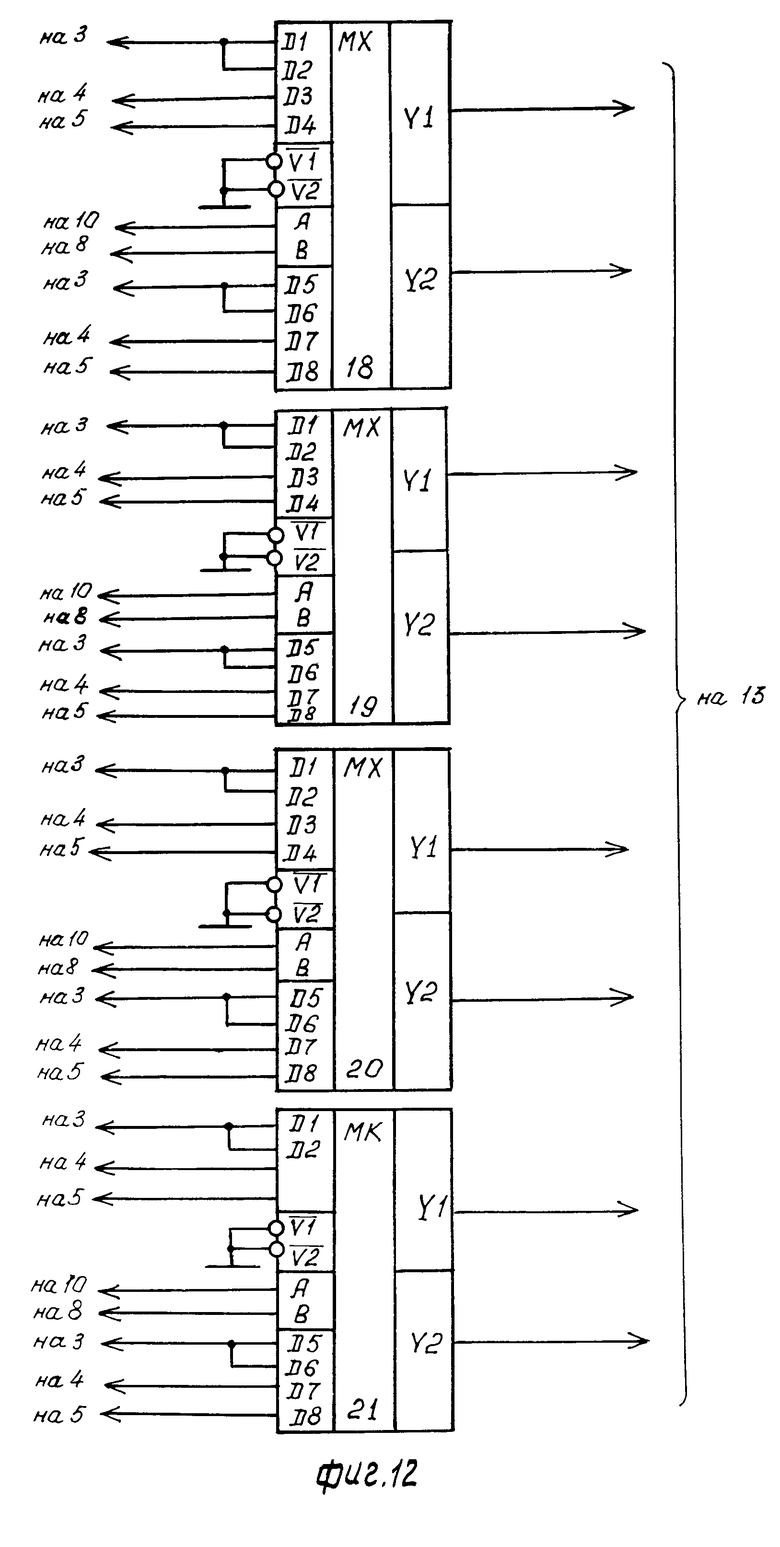

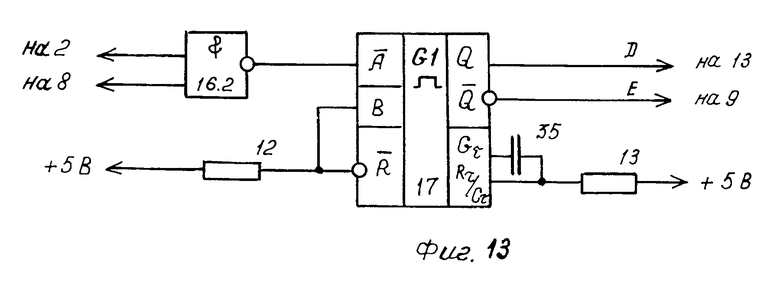

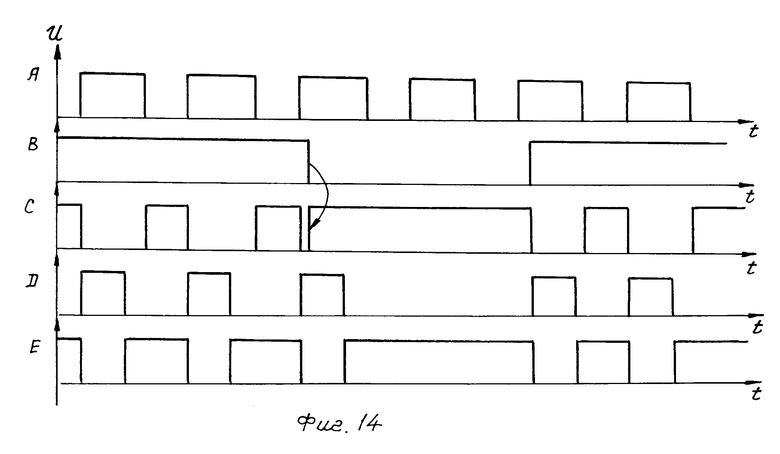

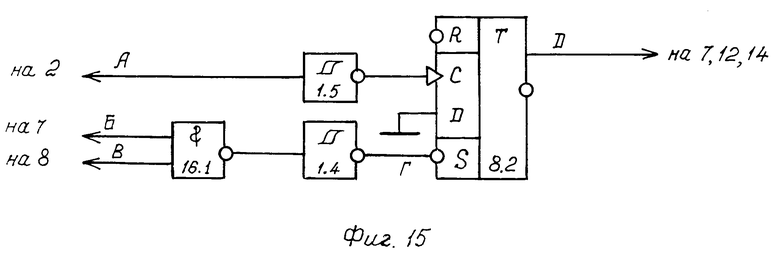

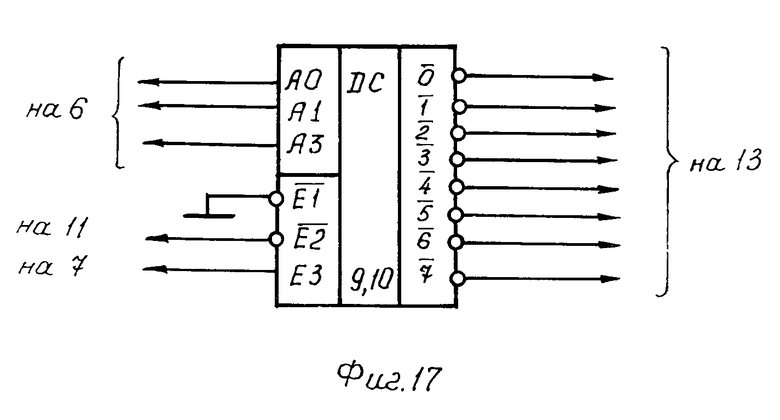

На фиг.1 показана структурная схема устройства; на фиг.2 временная диаграмма работы устройства; на фиг.3 вариант исполнения (принципиальная электрическая схема) шинного формирователя; на фиг.4 временная диаграмма цикла ВВОД; на фиг.5 временная диаграмма цикла ВЫВОД; на фиг.6 вариант исполнения (принципиальная электрическая схема) генератора тактовых импульсов; на фиг.7 вариант исполнения (принципиальная электрическая схема) счетчика адресов строк регенерации; на фиг.8 вариант исполнения регистра адреса строк и регистра адреса столбцов; на фиг.9 вариант исполнения регистра адреса кадра; на фиг.10 вариант исполнения (принципиальная электрическая схема) блока местного управления; на фиг.11 вариант исполнения (принципиальная электрическая схема) триггера регенерации; на фиг. 12 приведен вариант исполнения (принципиальная электрическая схема) мультиплексора адреса; на фиг.13 вариант исполнения (принципиальная электрическая схема) формирователя сигналов  ; на фиг.14 диаграммы работы формирователя сигналов

; на фиг.14 диаграммы работы формирователя сигналов  ; на фиг.15 вариант исполнения (принципиальная электрическая схема) формирователя сигналов разрешения

; на фиг.15 вариант исполнения (принципиальная электрическая схема) формирователя сигналов разрешения  и

и  ; на фиг.16 диаграммы работы формирователя сигналов разрешения

; на фиг.16 диаграммы работы формирователя сигналов разрешения  и

и  ; на фиг.17 вариант исполнения формирователя сигналов

; на фиг.17 вариант исполнения формирователя сигналов  и формирователя сигналов

и формирователя сигналов  .

.

Устройство содержит шинный формирователь (ШФ) 1, генератор тактовых импульсов (ГТИ) 2, счетчик адресов строк регенерации (САР) 3, регистр адреса строк (РАТ) 4, регистр адреса столбцов (РАБ) 5, регистр адреса кадра (РКД) 6, блок местного управления (БМУ) 7, триггер регенерации (ТРГ) 8, мультиплексор адреса (МА) 9, формирователь сигналов  (ФСР) 10, формирователь сигналов разрешения

(ФСР) 10, формирователь сигналов разрешения  и

и  (ФР) 11, формирователь сигналов

(ФР) 11, формирователь сигналов  (ФСК) 12, блок оперативной памяти (БОП) 13, формирователь сигналов

(ФСК) 12, блок оперативной памяти (БОП) 13, формирователь сигналов  (ФСЗ) 14.

(ФСЗ) 14.

Из структурной схемы, приведенной на фиг.1, следует, что отдельные выходы ШФ 1 подключены к отдельным входам РАТ 4, РАБ 5, РКД 6, БМУ 7 и БОП 13, выход которого соединен с отдельным входом ШФ 1, выход ГТИ 2 подключен к отдельным входам САР 3, ТРГ 8, ФСР 10 и ФР 11, отдельные выходы БМУ 7 подключены к отдельным входам РАТ 4, РАБ 5, РКД 6, ТРГ 8, ФР 11, ФСК 12 и ТРГ 8, другие отдельные выходы БМУ 7 подключены к отдельным входам ШФ 1, выход САР 3 подключен к отдельным входам САР 3 и МА 9, второй выход ТРГ 8 подключен к отдельным входам СА 3 и ФСР 10, первый выход ТРГ 8 соединен с отдельными входами ФР 11 и МА 9, выход РСТ 4 подключен к отдельному входу МА 9, выход РАБ 5 подключен к отдельному входу МА 9, выход РКД 6 подключен к отдельным входам ФСК 12 и ФСЗ 14, отдельный выход ФСР 10 подключен к отдельному входу МА 9, другой отдельный выход ФСР 10 подключен к отдельному входу БОП 13, выход МА 9 соединен с отдельным входом БОП 13, отдельный выход БМУ 7 подключен через ФС 3 к отдельному входу БОП 13; выход ФР 11 подключен к отдельным входам ФСК 12, ФСЗ 14 и БМУ 7, выход ФСК 12 соединен с отдельным входом БОП 13, ШФ 1 имеет вход, выход и двунаправленную связь с каналом ЭВМ.

На фиг.1 цифрами на связях обозначено количество проводов в шинах.

Устройство имеет три режима работы: а) режим регенерации записанной в БОП 13 информации; б) режим записи информации из ЭВМ в БОП 13; в) режим выборки (чтения) информации из БОП 13 в ЭВМ.

Устройство в исходном состоянии находится в режиме регенерации (а). В режимы б) или в) устройство может перейти в любое время по команде из ЭВМ. По окончании обмена информацией с ЭВМ устройство автоматически переходит в режим регенерации. Со стороны ЭВМ устройство представлено четырьмя регистрами: регистр адреса кадра (РКД 6), регистр адреса строки (РАТ 4), регистр адреса столбца (РАБ 5), регистр данных (БОП 13).

Работа устройства в режиме регенерации характеризуется отсутствием сигнала "Обращение к ОЗУ", вследствие чего триггер регенерации ТРГ 2 запрещает формирование сигналов  и

и  , разрешает тактирование счетчика адресов строк регенерации САР 3 при поступлении на его синхровход тактовых импульсов с ГТИ 2, переключает мультиплексор адреса МА 9 на выдачу адреса сформированного САР 3, и разрешает прохождение тактовых импульсов с ГТИ 2 на вход запуска одновибратора, входящего в состав ФСР 10. Одновибратор формирует минимальный интеграл между сигналами

, разрешает тактирование счетчика адресов строк регенерации САР 3 при поступлении на его синхровход тактовых импульсов с ГТИ 2, переключает мультиплексор адреса МА 9 на выдачу адреса сформированного САР 3, и разрешает прохождение тактовых импульсов с ГТИ 2 на вход запуска одновибратора, входящего в состав ФСР 10. Одновибратор формирует минимальный интеграл между сигналами  , поступающими на одноименные входы всех микросхем БОП 13. С формированием сигнала

, поступающими на одноименные входы всех микросхем БОП 13. С формированием сигнала  завершается цикл регенерации строки, адрес которой поступает на входы разрядов адреса А0 А7 БОП 13 через МА 9 из САР 3.

завершается цикл регенерации строки, адрес которой поступает на входы разрядов адреса А0 А7 БОП 13 через МА 9 из САР 3.

При обмене устройства с ЭВМ (режимы б и в) адрес кадра, строки и столбца, к которым происходит обращение, предварительно заносятся ЭВМ в РКД 6, РАТ 4 и РАБ 5 соответственно. При этом устройство находится в режиме регенерации. Для записи или чтения информации из БОП 13 ЭВМ должна обратиться к регистру данных.

В режиме записи информации из ЭВМ в БОП 13 БМУ 7 вырабатывает сигнал "Обращение к ОЗУ", который поступает на ТРГ 8, ФСР 10 и ФСК 12, в сигнал  , поступающий на ФСЗ 14. По переднему фронту тактовых импульсов с ГТИ 2 этот сигнал запоминается в ТРГ 8, вследствие чего приостанавливается регенерация на период обращения к БОП 13 и сохраняется текущее состояние САР 3;

, поступающий на ФСЗ 14. По переднему фронту тактовых импульсов с ГТИ 2 этот сигнал запоминается в ТРГ 8, вследствие чего приостанавливается регенерация на период обращения к БОП 13 и сохраняется текущее состояние САР 3;

МА 9 переключается на выдачу адреса строки, к которой происходит обращение (адрес строки предварительно заносится ЭВМ в РАТ 4). Сигналом  этот адрес запоминается во внутренних регистрах БИС БОП 13, после чего МА 9 переключается на выдачу адреса столбца.

этот адрес запоминается во внутренних регистрах БИС БОП 13, после чего МА 9 переключается на выдачу адреса столбца.

По заднему фронту тактовых импульсов ФР 11 вырабатывает сигнал "Разрешение  и

и  ", который поступает на ФСК 12, ФСК 12, ФСЗ 14 и БМУ 7, в результате чего

", который поступает на ФСК 12, ФСК 12, ФСЗ 14 и БМУ 7, в результате чего

ФСК 12 в соответствии с адресом кадра, поступающим с РКД 6, формирует один из сигналов  0.

0. 7, по которому во внутренних регистрах одной из восьми групп БИС БОП 13 запоминается адрес столбца, поступающего с РАБ 6 через МА 9;

7, по которому во внутренних регистрах одной из восьми групп БИС БОП 13 запоминается адрес столбца, поступающего с РАБ 6 через МА 9;

ФСЗ 14 в соответствии с адресом кадра, поступающим с РКД 6, формирует один из сигналов  0.

0. 7, по которому информация, поступающая из канала ЭВМ через шинный формирователь ШФ 1, запоминается в выбранной группе БИС БОП 13;

7, по которому информация, поступающая из канала ЭВМ через шинный формирователь ШФ 1, запоминается в выбранной группе БИС БОП 13;

БМУ 7 вырабатывает канальный сигнал к СИП, сигнализирующий о том, что данные от ЭВМ приняты, вследствие чего снимается сигнал "Обращение к ОЗУ" и завершается цикл записи, а устройство переходит в режим регенерации до прихода следующего сигнала "Обращение к ОЗУ".

Режим чтения информации из БОП 13 в ЭВМ аналогичен режиму записи. Отличие состоит в том, что сигнал  не вырабатывается, на ШФ 1 поступает с БМУ 7 сигнал, разрешающий передачу данных из ФЗУ в канал ЭВМ.

не вырабатывается, на ШФ 1 поступает с БМУ 7 сигнал, разрешающий передачу данных из ФЗУ в канал ЭВМ.

Диаграммы, поясняющие работу устройства, приведены на фиг.2.

На фиг.3 дан вариант исполнения шинного формирователя (ШФ 1), выполненный согласно известным рекомендациям и собранный на микросхемах 4, 5, 6, 7 и 16.4. Устройство принимает от ЭВМ следующие сигналы: 13 разрядов адреса, 8 разрядов данных, сигнал синхронизации активного устройства СИА, ВВОД, ВЫВОД, сигнал обращения к внешним устройствам ВУ. В ЭВМ передается следующая информация: 4 разряда данных из ОЗУ 13 и сигнал синхронизации пассивного устройства СИА. Данные и адрес передаются по одной шине последовательно. Двунаправленный обмен осуществляется только по 4 разрядам. Для связи с ЭВМ используются два приемника для разрядов ДА04 ДА07 и ДА09 ДА12 (микросхемы 4, 5); один приемо-передатчик для ДА00 ДА03 (микросхема 6); один приемник для сигналов СИА, ВВОД, ВЫВОД, ВУ и ДА08 (микросхема 7) и один передатчик сигнала СИП (микросхема 16.4).

На фиг.4 и 5 представлены временные диаграммы работы устройства при обмене информацией с ЭВМ. Обмен включает два цикла: цикл ВВОД (ввод данных в ЭВМ, фиг. 4) и цикла ВЫВОД (ввод данных в предлагаемое устройство, фиг.5). Последовательно выполнения операций цикла следующая. МикроЭВМ передает по шине данных адреса (ДА) адрес, а также вырабатывает сигнал ВУ, если адрес находится в требуемом диапазоне (например, 160000 177777). Через 150 нс после установления адреса микроЭВМ вырабатывает сигнал СИА, предназначенный для запоминания адреса во входной логике выбранного устройства. Устройство дешифрирует адрес и запоминает его; ЭВМ снимает адрес с шины ДА, снимает сигнал ВУ и вырабатывает сигнал ВВОД, сигнализируя о том, что она готова принять данные от устройства, и ожидает поступления сигнала СИП. Устройство помещает данные на линии ДА и вырабатывает сигнал СИА, сигнализирующий о том, что данные находятся в канале микроЭВМ. Если сигнал СИП не вырабатывается в течение 10 мкс после выдачи сигнала ВВОД, то микроЭВМ переходит к обслуживанию внутреннего прерывания по ошибке обращения к каналу. Если СИП вырабатывается, то микроЭВМ принимает данные и снимает сигнал ВВОД. Устройство снимает сигнал СИП, завершая операцию передачи данных. МикроЭВМ снимает сигнал СИА по заднему фронту сигнала СИП, завершая тем самым канальный цикл ВВОД.

В цикле ВЫВОД последовательность операций остается такой же, как в цикле ВВОД, за исключением того, что вместо команды ВВОД подается команда ВЫВОД, причем перед началом этой операции устанавливаются на входе устройства данные. В этом цикле источником данных является микроЭВМ.

На фиг. 6 дан вариант исполнения генератора тактовых импульсов (ГТИ) 2, выполненного на двух инвертирующих усилителях с порогом Шмитта 1.2 3 (микросхема 555ТЛ2). ГТИ 2 также включает резисторы 1 и 2, конденсатор 1 и диод 1. ГТИ 2 вырабатывает импульсы длительностью 280 нс с периодом следования 450 нс. Длительность генерируемых импульсов влияет на время установления сигнала  относительно сигнала

относительно сигнала  , а период следования тактирующих импульсов определяет длительность сигнала

, а период следования тактирующих импульсов определяет длительность сигнала  . Изменением длительности и частоты следования генерируемых импульсов формируются временные соотношения, соответствующие паспортным данным на применяемый тип БИС ОЗУ.

. Изменением длительности и частоты следования генерируемых импульсов формируются временные соотношения, соответствующие паспортным данным на применяемый тип БИС ОЗУ.

Счетчик адресов строк регенерации САР 3 (фиг.7) выполнен на микросхемах 2,3 (555ИЕ7). При отсутствии обращений к БОП 13 происходит процесс его регенерации. Тактирующие импульсы с ГТИ 2 поступают на счетный вход двоичного счетчика 2. По переднему фронту этих импульсов адрес регенерируемой строки увеличивается на 1 и через МА 9 поступает на адресные входы БИС ОЗУ 13.

При появлении команды "Обращение к ОЗУ" сигнал, поступающий с триггера регенерации ТРГ 8 на выходы  счетчиков 2,3 приостанавливает регенерацию на период обращения к памяти и сохраняет текущее состояние САР 3.

счетчиков 2,3 приостанавливает регенерацию на период обращения к памяти и сохраняет текущее состояние САР 3.

РАТ 4, РАБ 5 и РКД 6 служат для записи и хранения адреса строк, адреса столбцов и номера кадра соответственно (фиг.8 и 9). РАТ 4 и РАБ 5 представляют собой восьмиразрядные регистры 12 и 13 (микросхемы 580ИР82) и трехразрядный регистр 11 (микросхема КМ55ТМ8).

Работа РАТ 4, РАБ 5 и РКД 6 аналогична. Информационные входы регистров 12 и 13 через ШФ 1 связаны с восемью младшими разрядами шины ДА (ДА00 07), а регистр 11 с тремя (ДА00 02). Информация в регистрах запоминается по командам "запись адреса строк", "запись адреса столбцов" и "запись адреса кадра", которые поступают из ППЗУ 15 блока местного управления 7 на синхровход соответствующего регистра.

На фиг.10 дан вариант исполнения БМУ 7, выполненного на микросхемах 14, 15, 16.3-4,22. БМУ 7 в процессе обмена выполняет функции дешифратора адреса устройства, регистра и дешифратора команд. Адрес устройства и команды передаются от ЭВМ одним адресным словом. При этом разряды адреса А04 А12 и сигнал ВУ служат кодом устройства, а разряды А01 А02 и сигналы ВВОД и ВЫВОД несут в себе информацию о командах. БМУ 7 дешифрирует и выдает следующие команды:

запись адреса кадра (на РКД 6);

запись адреса строк (на РАТ 4);

запись адреса столбцов (на РАБ 5);

обращение ЭВМ к ОЗУ 13 (на ТРГ 8, ФР 11 и ФСК 12); запись в ОЗУ 13 (на ФСЗ 14);

СИП при обращении ЭВМ к устройству (на ШФ 1).

Для дешифрации и выдачи команд используются два ППЗУ 14, 15 и один регистр 22. ППЗУ 14, выполненное на микросхеме 556РТ4, предназначено для дешифрации адреса устройства. Если адрес, выставленный на шине ДА, совпадает с адресом данного устройства, то на выходе микросхемы 14 появляется логичексий "0". По команде СИА сигнал с дешифратора адрес, а также младшие разряды адреса А01 А02 запоминаются в регистре 22 (155ТМ8). Этот код команды хранится в регистре до прихода следующего сигнала СИА. С регистра информация поступает на второе ППЗУ 15 (155РЕЗ), куда поступают также сигналы ВВОД и ВЫВОД. В зависимости от комбинации этих сигналов на выходе ППЗУ 15 появляется соответствующая команда (см. таблицу).

Для формирования сигнала СИП, поступающего на ШФ 1, служит элемент 16.3. Причем при обращении ЭВМ к регистрам адреса кадров, строк и столбцов сигнал СИП формируется из сигнала, поступающего из ПЗУ 15 (выход 07), а при обращении к ОЗУ из сигнала, поступающего от ФР 11.

Триггер регенерации ТРГ 8 (фиг.11) включает триггер 8.1 (555ТМ2) и элементы задержки (резистор 15 и конденсатор 34). ТРГ 8 предназначен для обеспечения регенерации всех строк ОЗУ без пропуска и формирования сигналов: приостановки регенерации на период обращения к памяти на САР 3 и ФСР 10, переключения МА 9 на выдачу адерса ячейки, к которой происходит обращение и разрешения работы ФР 11.

Мультиплексор адреса МА 9 (фиг.12) содержит четыре микросхемы 155КП2. На информационные входы МА 9 соответствующим образом подаются адреса строк регенерации с САР 3, адреса строк с РАТ 4 и адреса столбцов с РАБ 5. На управляющие входы подаются проинвертированный сигнал  с ФСР 10 и сигнал с ТР 8, сигнализирующий о том, что регенерация запрещена.

с ФСР 10 и сигнал с ТР 8, сигнализирующий о том, что регенерация запрещена.

При наличии сигнала с ТРГ 8 на выход МА 9 передаются сначала адреса строк, а затем после прихода проинвертированного сигнала  адреса столбцов. В противном случае в БОП 13 поступают адреса строк регенерации (режим регенерации).

адреса столбцов. В противном случае в БОП 13 поступают адреса строк регенерации (режим регенерации).

На фиг. 13 дан вариант исполнения формирователя сигналов  (ФСР 10), выполненного на микросхемах 16,2, 17, резисторах 12, 13 и конденсаторе 35. Микросхема 16.2 выполняет роль ключа, на один вход которого поступают тактовые импульсы с ГТИ 2, а на другой сигнал с ТРГ 8. В режиме регенерации ключ открыт и тактовые импульсы походят на вход запуска микросхемы 17, которая представляет собой одновибратор, выполненный на 155АГ3. По переднему фронту тактовых импульсов одновибратор формирует временной интервал между сигналами

(ФСР 10), выполненного на микросхемах 16,2, 17, резисторах 12, 13 и конденсаторе 35. Микросхема 16.2 выполняет роль ключа, на один вход которого поступают тактовые импульсы с ГТИ 2, а на другой сигнал с ТРГ 8. В режиме регенерации ключ открыт и тактовые импульсы походят на вход запуска микросхемы 17, которая представляет собой одновибратор, выполненный на 155АГ3. По переднему фронту тактовых импульсов одновибратор формирует временной интервал между сигналами  , соответствующий паспортным данным на применяемый тип БИС ОЗУ.

, соответствующий паспортным данным на применяемый тип БИС ОЗУ.

При обращении к ОЗУ ФСР 10 формирует только один сигнал  для запоминания адреса строки ячейки, к которой происходит обращение. После этого ключ на микросхеме 16.2 закрывается сигналом, приходящим с ТРГ 8 на все время обращения к памяти.

для запоминания адреса строки ячейки, к которой происходит обращение. После этого ключ на микросхеме 16.2 закрывается сигналом, приходящим с ТРГ 8 на все время обращения к памяти.

Сигналы  , сформированные одновибратором, через буферные усилители поступают в БОП 13. А инвертированный сигнал

, сформированные одновибратором, через буферные усилители поступают в БОП 13. А инвертированный сигнал  с инверсного выхода одновибратора поступает на МА 9.

с инверсного выхода одновибратора поступает на МА 9.

Диаграммы работы ФСР 10 приведены на фиг.14.

На фиг.15 дан вариант исполнения формирователя сигналов разрешения  и

и  (ФР) 11, выполненного на микросхемах 1.4 5, 8.2, 16.1.

(ФР) 11, выполненного на микросхемах 1.4 5, 8.2, 16.1.

При отсутствии сигнала "Обращение к ОЗУ" из БМУ 7 и сигнала "прекращение регенерации" из ТРГ 8 триггер 8.2 находится в заблокированном состоянии. Вследствие этого на ФСК 12, ФСЗ 13 и БМУ 7 выдается сигнал логической "1", запрещающий выработку сигналов  ,

,  и разрешающий формирование сигнала к СИП БМУ 7.

и разрешающий формирование сигнала к СИП БМУ 7.

В режиме обращения к модулю ОЗУ триггер 8.2 разблокируется и по заднему фронту тактовых импульсов с ГТИ 2 на выходе триггера появляется логический "0", в результате чего формируются сигналы  и

и  и разрешается формирование сигнала

и разрешается формирование сигнала  .

.

Диаграммы, поясняющие работу ФР 11, приведены на фиг.16.

Формирователь сигналов  (ФСК) 12 и формирователь сигналов

(ФСК) 12 и формирователь сигналов  (ФСЗ) 14 фиг.17 вырабатывают один из сигналов

(ФСЗ) 14 фиг.17 вырабатывают один из сигналов  0.

0. 7 и

7 и  0.

0. 7, которыми выбирается один из восьми "кадров" модуля ОЗУ.

7, которыми выбирается один из восьми "кадров" модуля ОЗУ.

Блок оперативной памяти (БОП) 13, выполненный на 32 микросхемах 565РУБД. БОП 13, содержит 8 блоков ("кадров") емкостью 256х256х4 бит и позволяет непосредственно обращаться к любой ячейке любого из 8 блоков.

ФСК 12 и ФСЗ 14 представляют собой дешифраторы (микросхемы 9, 10), преобразующие трехразрядный код адреса кадра А0 А2, поступающий из РКД 6 в напряжение низкого логического уровня, появляющееся на одном из восьми выходов 0,0 0,7. Сформированные таким образом сигналы поступают на БИС ОЗУ 13 в качестве сигналов  и

и  .

.

На управляющие входы  дешифраторов подается сигнал разрешения с ФР 11. На вход

дешифраторов подается сигнал разрешения с ФР 11. На вход  поступают сигналы из БМУ 7: сигнал "обращение к ОЗУ" на ФСК 12 и "запись в ОЗУ" на ФСВ 14. Входы

поступают сигналы из БМУ 7: сигнал "обращение к ОЗУ" на ФСК 12 и "запись в ОЗУ" на ФСВ 14. Входы  обоих дешифраторов заземлены.

обоих дешифраторов заземлены.

По сравнению с известным предлагаемое устройство обладает более широкими возможностями за счет совместимости с единым каналом семейства микроЭВМ "Электроника-60" использования синхронного режима работы, возможности запоминания изображения и расширения адресного пространства.

Во-первых, известное устройство требует строгого соблюдения временных соотношений между сигналами обращения к памяти и тактовыми сигналами [4, с. 76-77] Это объясняется тем, что известное устройство ориентировано на применение микропроцессорных устройств, построенных с использованием системного контроллера К580ВК38 и тактового генератора 801Ф24.

Предлагаемое устройство может работать в составе любой микроЭВМ семейства "Электроника-60" независимо от быстродействия применяемого процессора. Это объясняется использованием синхронного режима работы.

Во-вторых, предлагаемое устройство обладает возможностью автономной регенерации за счет использования собственного генератора тактовых импульсов (т.е. синхрогенератора). Известное устрйоство не обладает автономной регенерацией из-за отсутствия собственного синхрогенератора (в прототипе синхронизация осуществляется внешним процессором).

В-третьих, предлагаемое устройство обладает возможностью запоминать изображения (видеоинформацию) за счет введения блока памяти (как уже указывалось в прототипе блок памяти отсутствует).

В-четвертых, предлагаемое устройство, обладает большим адресным пространством по сравнению с предлагаемым устройством. Например, предлагаемое устройство имеет адресное пространство А1n 8 блоков по 64 К (8х64 К), т.е. 512 К 512000, а известное А2n 4 блока по 16 К (4х16 К), т.е. 64 К 64000. Таким образом, предлагаемое устройство имеет адресное пространство в А1n/A2n 512К/64К 8 раз больше, чем известное. Больший размер адресного пространства обеспечивает больший объем запоминаемой видеоинформации.

Таким образом, предлагаемое устройство обладает более широкими функциональными возможностями.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| ТЕЛЕВИЗИОННОЕ СЛЕДЯЩЕЕ УСТРОЙСТВО | 1988 |

|

SU1574152A1 |

| ТЕЛЕВИЗИОННЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ ПОДВИЖНЫХ ТОЧЕЧНЫХ ОБЪЕКТОВ | 1989 |

|

SU1623537A1 |

| ТЕЛЕВИЗИОННЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1985 |

|

SU1454225A1 |

| ТЕЛЕВИЗИОННЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1986 |

|

SU1517737A1 |

| Устройство для ввода изображения в ЭВМ | 1988 |

|

SU1672491A1 |

| СПОСОБ ИЗМЕРЕНИЯ КООРДИНАТ ТОЧЕЧНОГО ОБЪЕКТА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1985 |

|

SU1493074A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1994 |

|

RU2108623C1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТОР | 1986 |

|

SU1412577A1 |

| ТЕЛЕВИЗИОННОЕ СЛЕДЯЩЕЕ УСТРОЙСТВО | 1985 |

|

SU1286089A1 |

Изобретение относится к информационно-вычислительной технике и предназначено для цифровой обработки изображений. В устройство, содержащее счетчик адресов строки регенерации, триггер регенерации, формирователь сигналов  , мультиплексор адреса, введены шинный формирователь, регистр адреса строк, регистр адреса столбцов, регистр адреса кадра, блок местного управления, генератор тактовых импульсов, блок оперативной памяти и три формирования сигналов. 17 ил.

, мультиплексор адреса, введены шинный формирователь, регистр адреса строк, регистр адреса столбцов, регистр адреса кадра, блок местного управления, генератор тактовых импульсов, блок оперативной памяти и три формирования сигналов. 17 ил.

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ, содержащее мультиплексор адреса, информационные входы первой группы которого соединены с информационными входом и выходами счетчика адресов строк регенерации, вход записи которого соединен с инверсным выходом триггера регенерации и первым входом первого формирователя сигналов, первый выход которого соединен с управляющим входом мультиплексора адреса, счетный вход счетчика адресов строк регенерации соединен с вторым входом первого формирователя, отличающееся тем, что в него введены шинный формирователь, регистр адреса строк, регистр адреса столбцов, регистр адреса кадра, блок местного управления, генератор тактовых импульсов, три формирователя сигналов, блок оперативной памяти, выходы шинного формирователя соединены с информационными входами регистров адреса строк, столбцов, кадра, блока местного управления и блока оперативной памяти, выходы первой группы блока местного управления подключены к соответствующим управляющим входам регистров адреса строк, столбцов, кадра, выходы регистров адреса строк и столбцов соединены соответственно с информационными входами второй и третьей групп мультиплексора адреса, первый выход блока местного управления соединен с нулевым входом триггера регенерации, третьими входами второго и третьего формирователей сигналов, выходы второй группы блока местного управления соединены с входами группы шинного формирователя, управляющий вход блока местного управления соединен с выходом второго формирователя сигналов, первый и второй входы которого соединены соответственно с выходом генератора тактовых импульсов, первым входом первого формирователя сигналов, единичным входом триггера регенерации, единичным выходом триггера регенерации, прямой выход которого соединен с вторым входом первого формирователя сигналов, второй выход которого и выходы третьего и четвертого формирователей сигналов соединены с информационными входами группы блока оперативной памяти, адресный вход которого соединен с выходом мультиплексора адреса, первый информационный вход которого соединен с выходом и входом обнуления счетчика адреса строк регенерации, первый вход третьего формирователя сигнала и второй вход четвертого формирователя сигналов объединены и подключены к выходу второго формирователя сигналов, второй выход блока местного управления соединен с третьим входом четвертого формирователя сигналов, первый вход которого соединен с вторым входом третьего формирователя и подключен к выходу регистра адреса кадра, выход блока оперативной памяти соединен с входом шинного формирователя, прямой выход триггера регенерации соединен с входом разрешения мультиплексора адреса.

| Контроллер динамического оперативного запоминающего устройства | 1987 |

|

SU1442995A1 |

Авторы

Даты

1995-11-10—Публикация

1990-06-18—Подача