сл С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство межмодульного обмена по магистрали LVDS-M с канальным резервированием и прямым доступом в память | 2016 |

|

RU2648574C2 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА | 2012 |

|

RU2524852C2 |

| Устройство для сопряжения ЭВМ с периферийным устройством | 1987 |

|

SU1439613A1 |

| Устройство для обмена информацией | 1989 |

|

SU1784103A3 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с периферийными устройствами | 1985 |

|

SU1285484A1 |

| АДАПТЕР МУЛЬТИПЛЕКСНЫХ КАНАЛОВ ИНФОРМАЦИОННОГО ОБМЕНА | 2000 |

|

RU2163728C1 |

| Адаптер магистрального последовательного интерфейса мультиплексного канала информационного обмена | 2016 |

|

RU2639959C2 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛОВОЙ ИНФОРМАЦИИ | 2016 |

|

RU2652467C1 |

| Устройство ввода-вывода | 2020 |

|

RU2753980C1 |

Изобретение относится к автоматике и вычислительной технике, в частности к системам управления технологическими процессами, станками, роботами, автоматическими линиями и комплексами, в состав которых входят вышеперечисленные объекты. Целью изобретения является повышение быстродействия системы за счет уменьшения времени реакции на входные воздействия. Эта цель достигается путе организации дополнительного уровня конвейерной обработки информации в контроллере главного абонента и периферийных контроллерах, позволяющего распараллелить во времени процессы подготовки и передачи информации по последовательной магистрали и предварительной обработке входных воздействий. Для этого в контроллер главного абонента и периферийные контроллеры введены блок управления и двунаправленный шинный формирователь, кроме того, в контроллер главного абонента введено запоминающее устройство обмена. 9 ил., 5табл

Изобретение относится к автоматике и вычислительной технике, в частности к системам управления технологическими процессами, станками, роботами, автоматическими линиями и комплексами, в состав которых входят вышеперечисленные объекты.

Цель изобретения -уменьшение времени реакции на входное воздействие за счет организации дополнительного уровня конвейерной обработки информации.

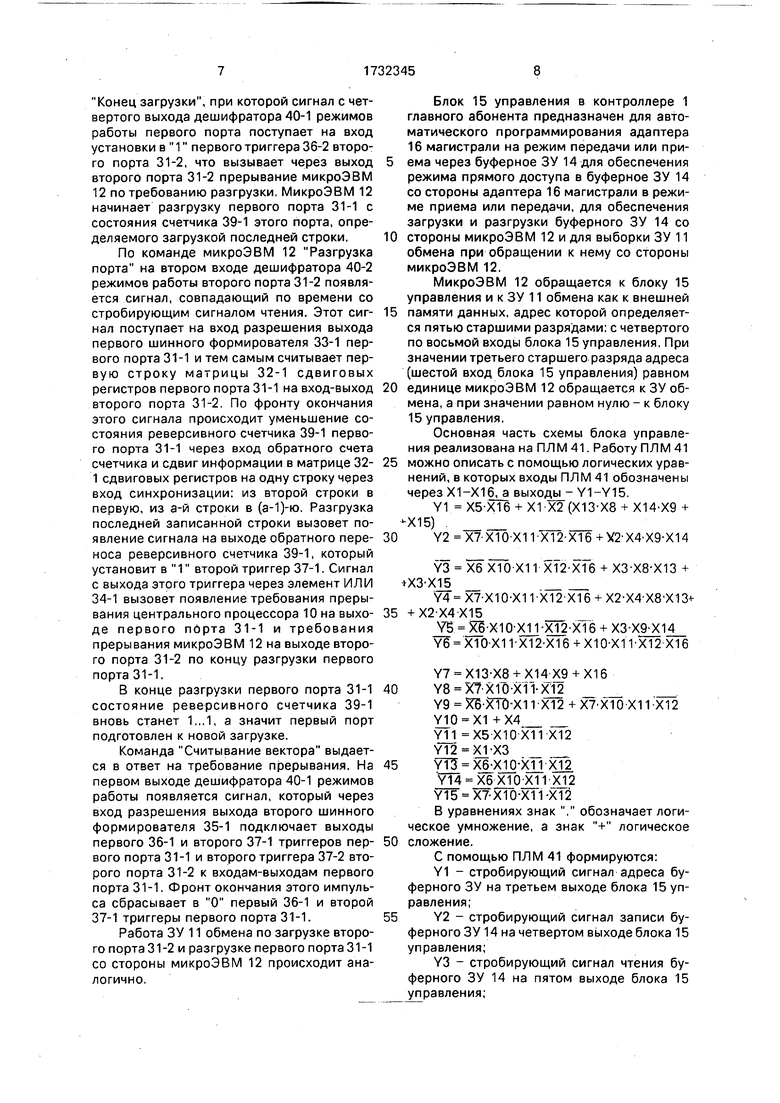

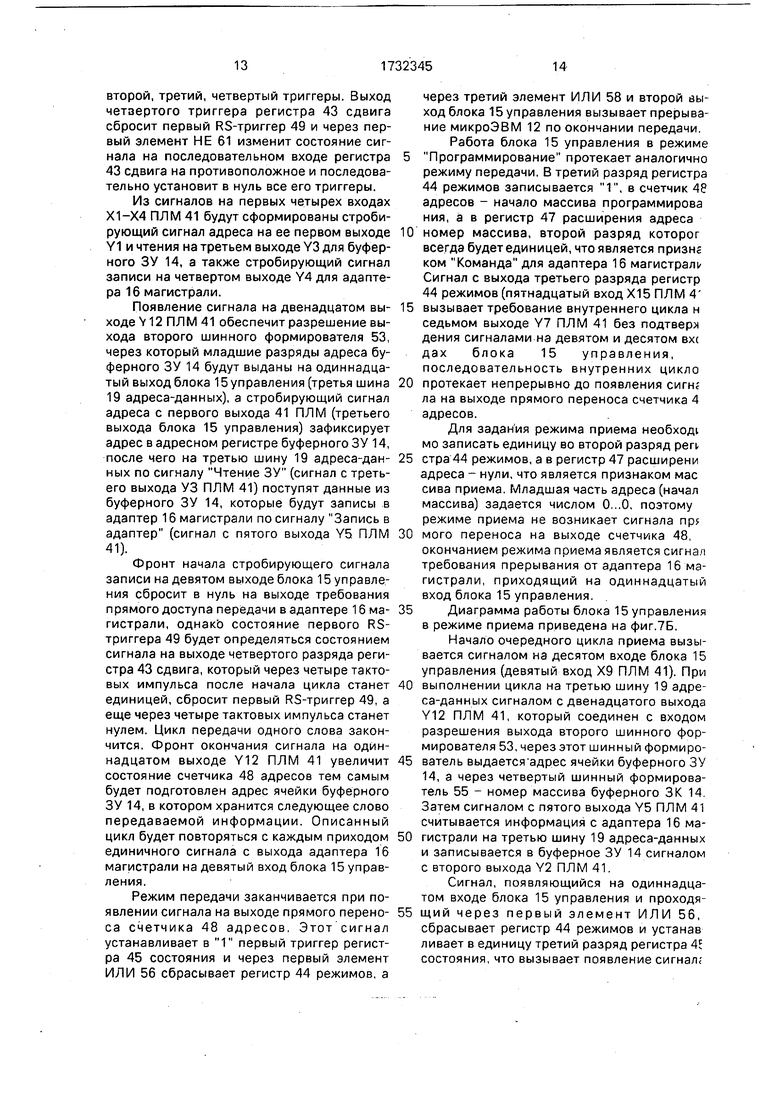

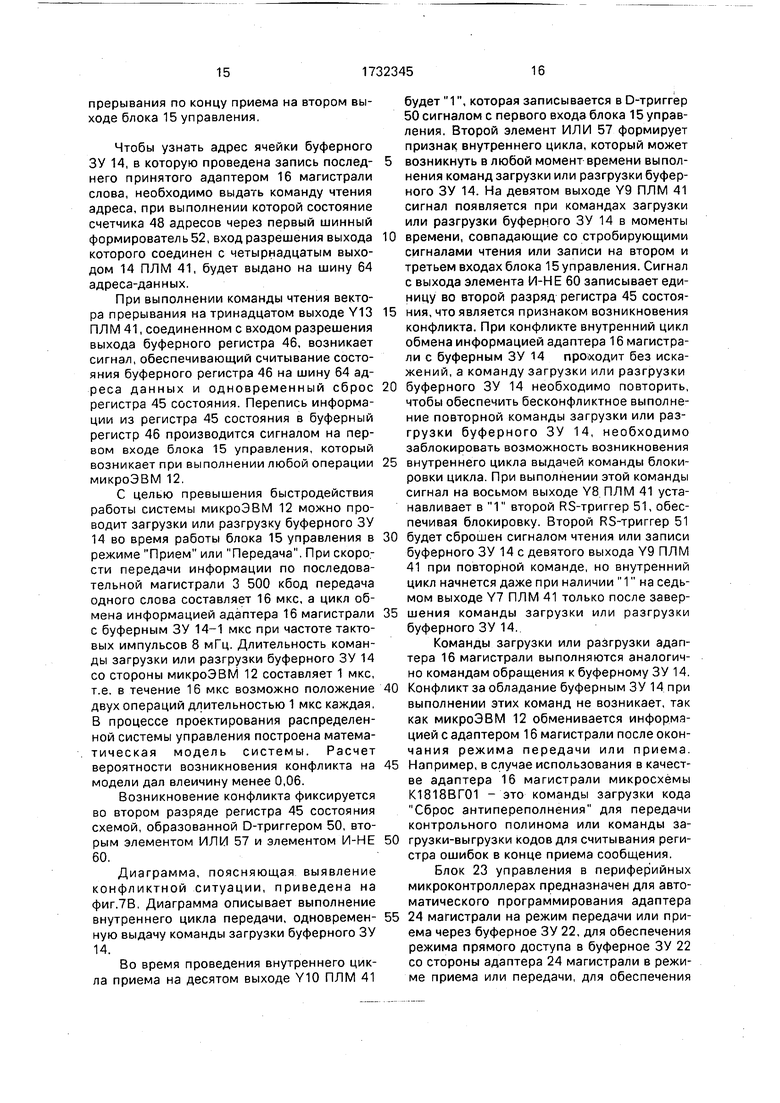

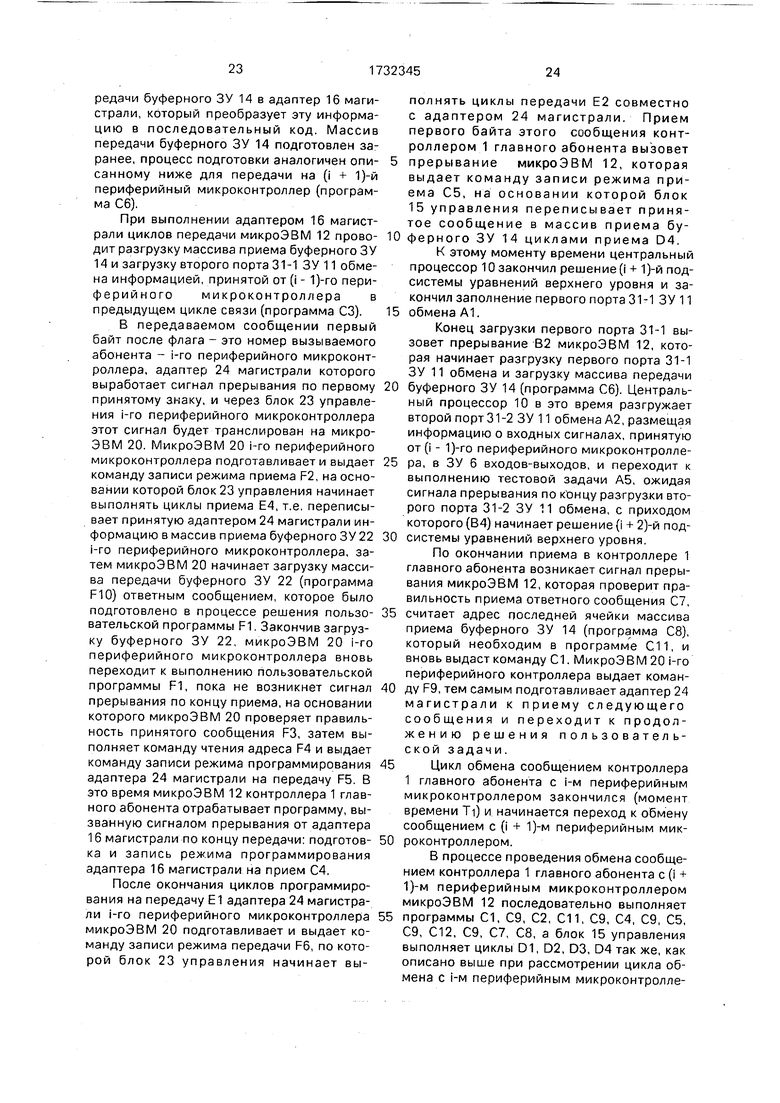

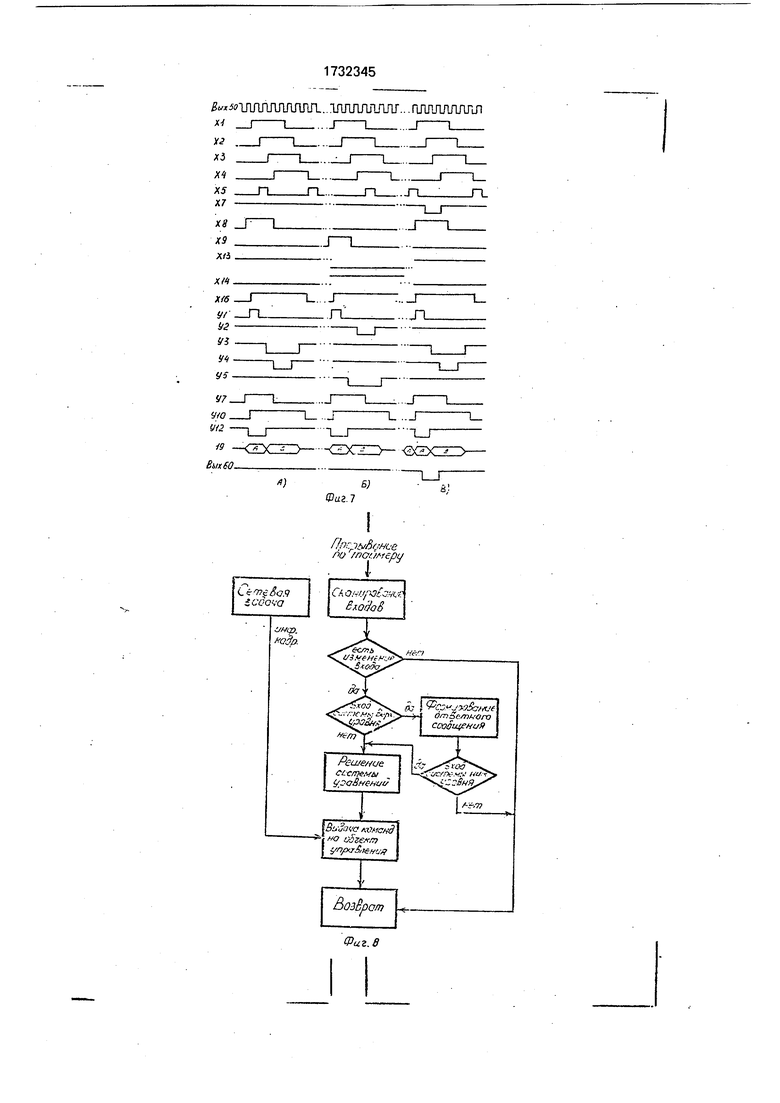

На фиг.1 и 2 представлена структурная схема распределенной системы управления; на фиг.З - функциональная схема запоминающего устройства обмена; на фиг,4 и 5 - функциональная схема блока управления; на фиг.6 - пример выполнения матрицы сдвиговых регистров; на фиг.7 - диаграмма

работы блока управления в режиме передачи (А), приема (Б) и работы блока управления в режиме передачи (А), приема (Б) и работы блока управления в режиме передачи с одновременной записью со стороны микро- ЭВМ в ЗУ обмена (В); на фиг.8 - блок-схема алгоритма работы периферийного микроконтроллера; на фиг.9 - временная диаграмма работы распределенной системы управления.

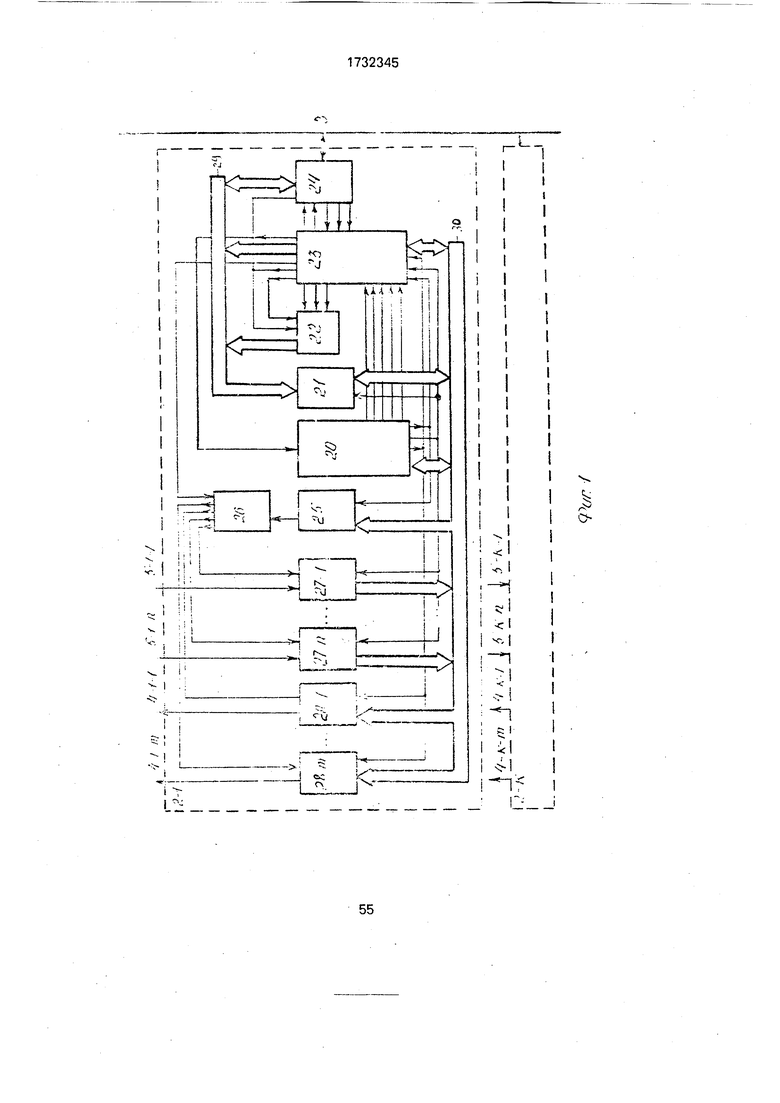

Распределенная система управления (фиг.1 и 2) содержит контроллер 1 главного абонента и К периферийных микроконтроллеров 2-1-2-К (где К - количество объектов управления), соединенных между собой и контроллером 1 главного абонента последовательной магистралью 3, а с объектами управления (на фиг.1 не показаны) - через

выходы 4-1-1 - 4-К-М и входы 5-1-1 - 5-К-Р, где М и Р - соответственно количество выходов и входов каждого объекта управления, связанного с одним периферийным микроконтроллером.

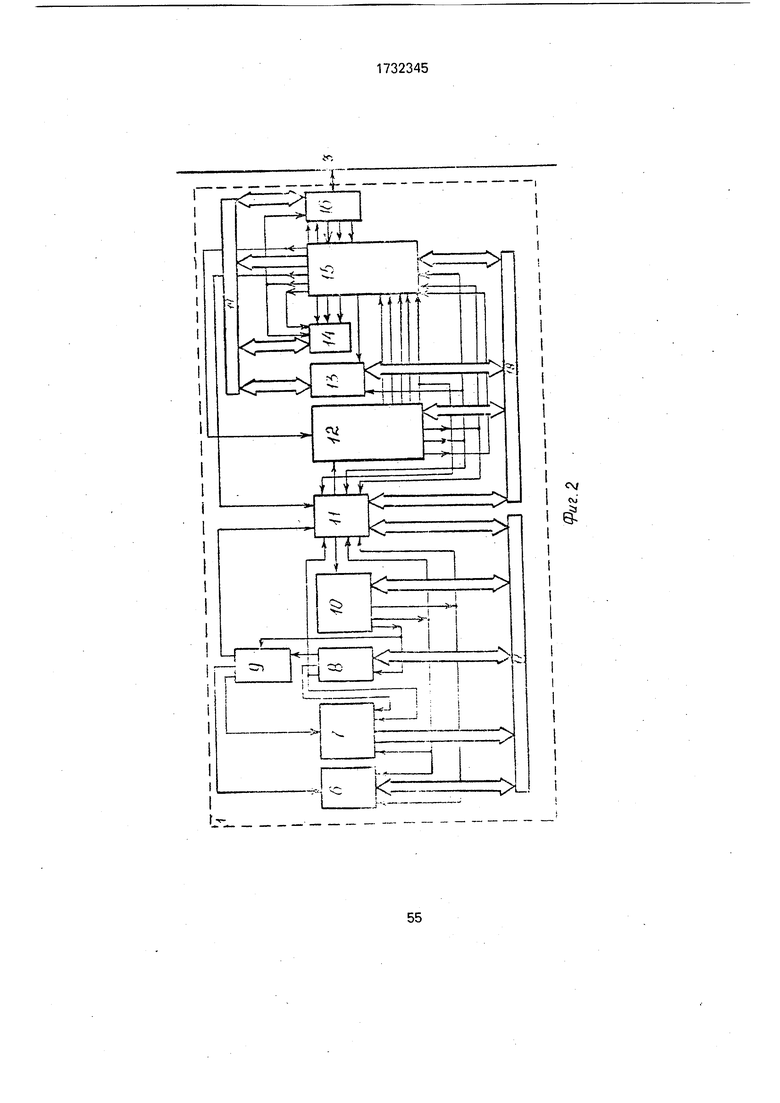

Контроллер 1 главного абонента содержит запоминающее устройство (ЗУ) 6 входов-выходов, ЗУ 7 команд, регистр 8 адреса, дешифратор 9, центральный процессор 10, ЗУ 11 обмена, микроЭВМ 12, двунаправленный шинный формирователь 13, буферное ЗУ 14, блок 15 управления и адаптер 16 магистрали, шины адреса-данных 17-19.

Каждый из периферийных микроконтроллеров 2-1 - 2-К содержит микроЭВМ 20, двунаправленный шинный формирователь 21, буферное ЗУ 22, блок 23 управления, адаптер 24 магистрали, регистр 25 адреса, дешифратор 26, Р объективных адаптеров 27-1 - 27-Р входов, М объективных адаптеров 28-1 - 28-М выходов.

ЗУ 6 входов-выходов предназначено для хранения оперативной информации о состоянии входов-выходов; ЗУ 7 команд содержит системные и пользовательские про- граммы, а также таблицы констант. Дешифратор 9 осуществляет выборку ЗУ 6 входов-выходов, ЗУ 7 команд и первого порта ЗУ 11 обмена. Первая 17, вторая 18 и третья 19 шины адреса-данных контроллера 1 главного абонента, а также первая 29 и вторая 30 шины адреса-данных периферийных микроконтроллеров 2-1 - 2-К содержат мультиплексированные информационные и адресные шины.

МикроЭВМ 12, двунаправленный шинный формирователь 13, буферное ЗУ 14, блок 15 управления и адаптер 16 магистрали, входящие в состав контроллера 1 главного абонента, по выполняемым функциям и форме исполнения идентичны одноименным блокам 20-24, входящим в состав каждого периферийного микроконтроллера. Однако содержимое постоянного запоминающего устройства (ПЗУ), входящего в состав микроЭВМ 12 контроллера 1 главного абонента, и содержимое ПЗУ, входящего в состав микроЭВМ 20 периферийных микроконтроллеров 2-1 - 2-К различаются: в первом помещены программы сетевой задачи, во втором - сетевой задачи и пользовательской.

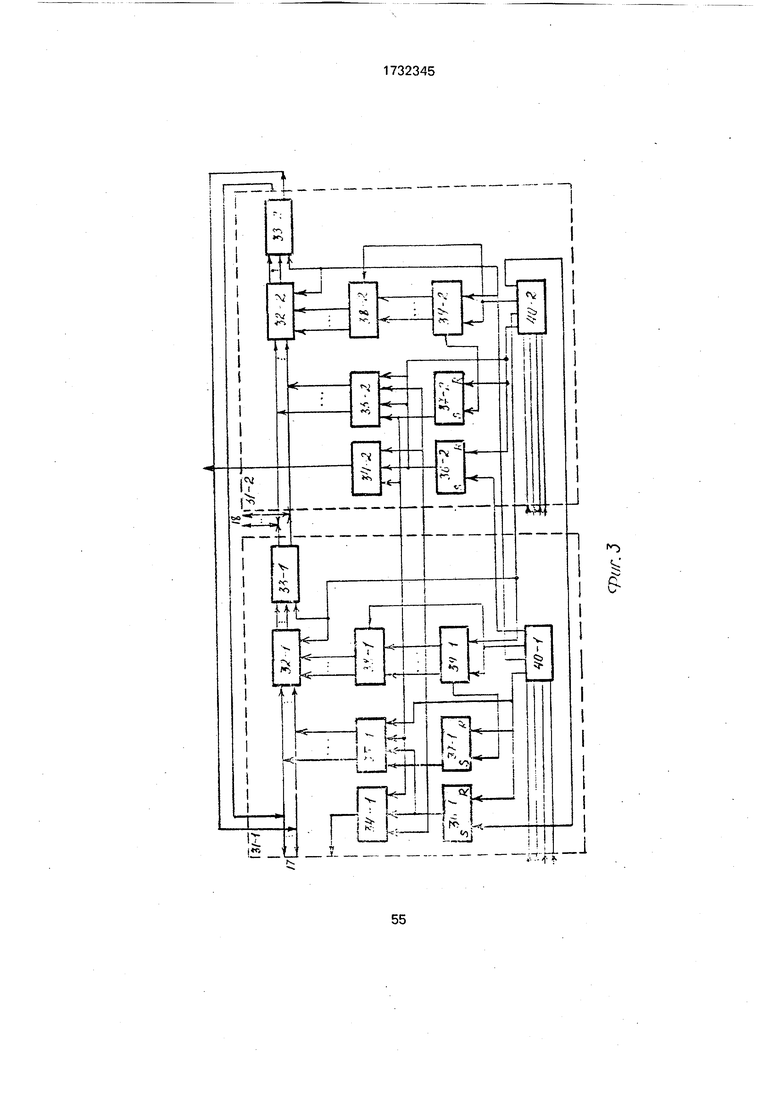

ЗУ 11 обмена (фиг.З) состоит из первого 31-1 и второй 31-2 портов. Каждый порт содержит соответственно матрицу 32-1 и 32-2 сдвиговых регистров, первый шинный формирователь 33-1 и 33-2, элемент ИЛИ 34-1 и 34-2, второй шинный формирователь 35-1 и 35-2, первый 36-1 и 36-2 и вторые 37-1 и 37-2 триггеры, дешифратор 38-1 и 38-2 записи,

реверсивный счетчик 39-1 и 39-2 и дешифратор 40-1 и 40-2 режимов работы.

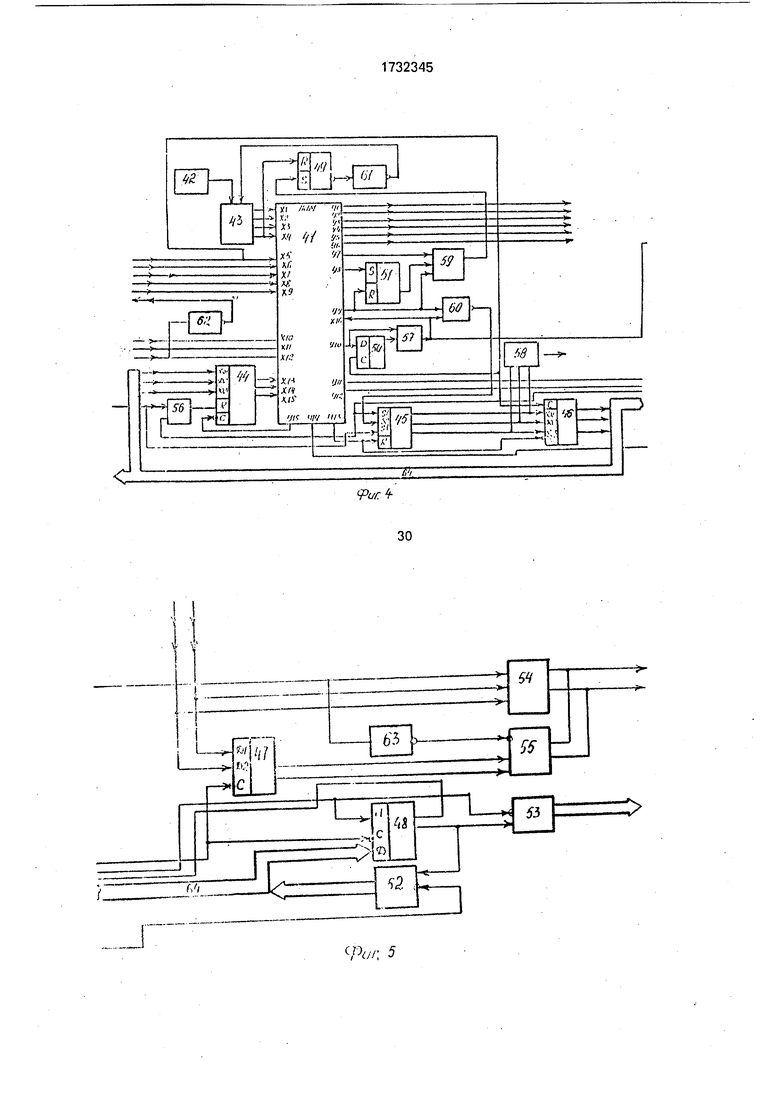

Блок управления (в контроллере 1 главного абонента - блок 15, в периферийных

микроконтроллерах - блок 23) (фиг.4 и 5) содержит программируемую логическую матрицу (ПЛМ) 41, генератор 42 тактовых импульсов, регистр 43 сдига, регистр 44 режимов, регистр 45 состояния, буферный ре0 гистр 46, регистр 47 расширения адреса, счетчик 48 адресов, первый RS-триггер 49, D-триггер 50, второй RS-триггер 51, первый 52, второй 53, третий 54 и четвертый 55 шинные формирователи, первый 56, второй

5 57 и третий 58 элементы ИЛИ, элемент И 59, элемент И-НЕ 60, первый 61, второй 62 и третий 63 элементы НЕ и шину 64 адреса- данных. Первый, второй и третий входы ПЛМ 41 соединены с выходами первого,

0 второго и третьего разрядов регистра 43 сдвига соответственно, четвертый вход ПЛМ 41 подключен к выходу четвертого разряда регистра 43 сдвига и к входу сброса первого RS-триггера 49, вход установки в

5 1 которого подключен к выходу элемента И 59, а инверсный выход подключен к входу первого элемента НЕ 61. Выход первого элемента НЕ 61 соединен с последовательным входом регистра 43 сдвига, вход синх0 ронизации которого соединен с выходом генератора 42 тактовых импульсов.

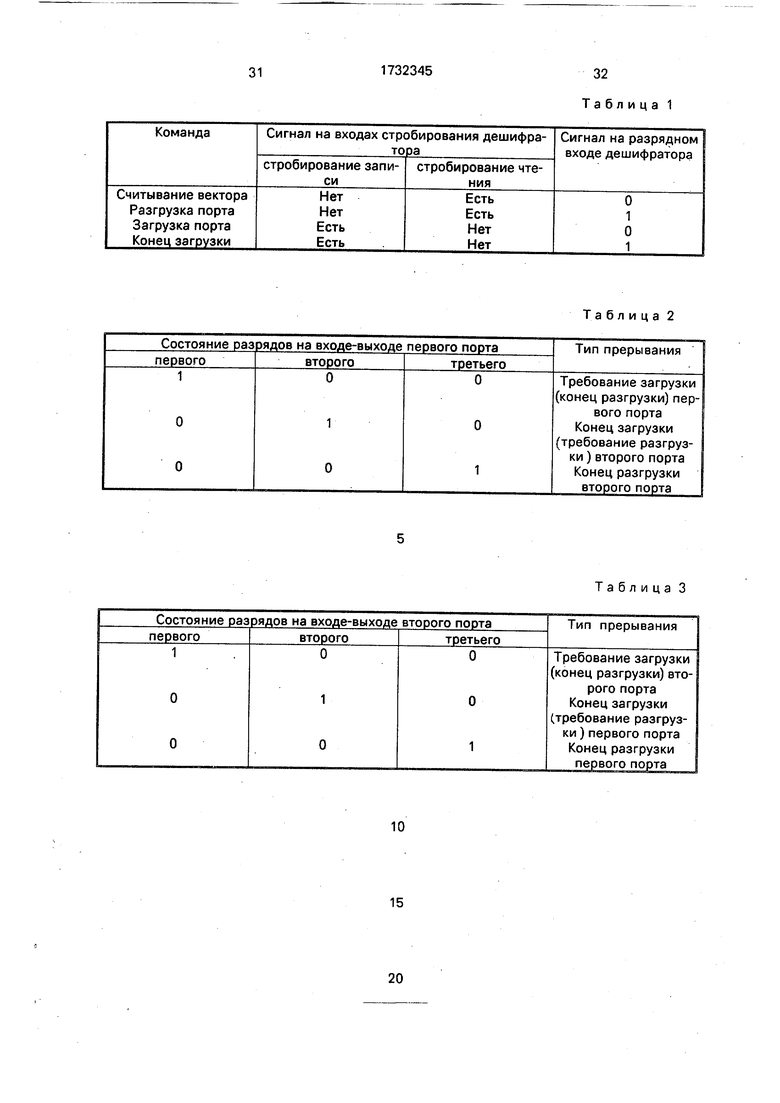

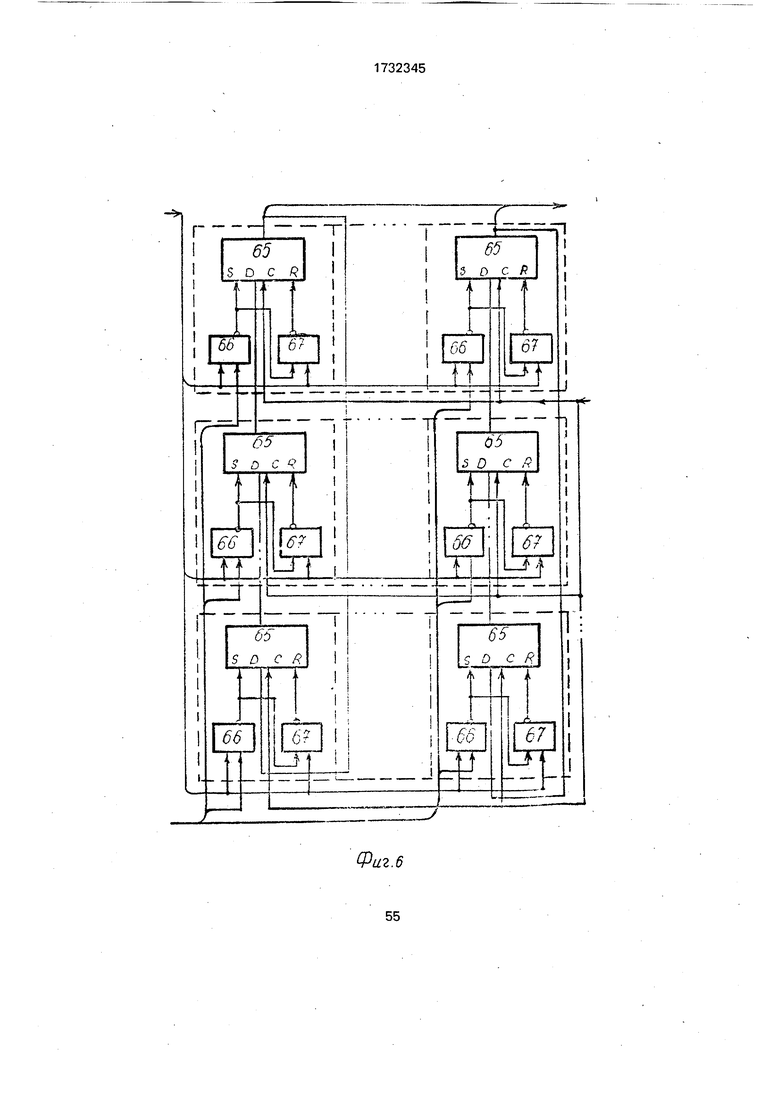

Каждая матрица 32-1 и 32-2 сдвиговых регистров (фиг.6) представляет собой матрицу ячеек размером а х Ь, где а - количест5 во разрядов, определяемое разрядностью микропроцессора (для однокристальной микроЭВМ а 8); b - количество строк в матрице, определяемое максимальным количеством байт информационного кадра.

0 Каждая ячейка матрицы состоит из синхронного триггера 65 и двух элементов И- НЕ 66 и 67, причем вход установки в 1 синхронного триггера 65 соединен с выходом первого элемента И-НЕ 66 и вторым

5 входом второго элемента И-НЕ 67, а вход сброса подключен к выходу второго элемента И-НЕ 67. Первые входы элементов И-НЕ ячеек каждой строки соединены между собой и являются входами записи строк мат0 рицы сдвиговых регистров. Вторые входы первых элементов И-НЕ 66 ячеек каждого столбца соединены между собой и являются информационными входами матрицы сдвиговых регистров. Входы синхронизации

5 синхронных триггеров 65 всех ячеек матрицы соединены между собой и образуют вход синхронизации матрицы сдвиговых регистров. Прямые выходы триггеров 65 с первого по а-й разряд первой строки соединены соответственно с D-входами синхронных триггеров 65 с первого по а-й разряд последней строки и являются информационными выходами матрицы сдвиговых регистров. D-вхо- ды синхронных триггеров 65 с первого по а-й разряд первой, второй, ... (Ь - 1)-й строк соединены соответственно с прямыми выходами триггеров с первого по а-й разряд второго, третьейb-й строк.

Распределенная система управления может быть реализована на следующих микросхемах: ЗУ 6 входов-выходов, буферные ЗУ 14 и 22 могут быть выполнены на микросхемах К 537 РУ 8, ЗУ 7 команд - на микросхеме К 573 РФ4, регистры 8 и 25 адреса - на микросхемах К 155 ТМ 5. В качестве центрального процессора 10 может быть использован стандартный микропроцессор КМ 1810 ВМ86, а в качестве микроЭВМ 12 и 20 - однокритальная микроЭВМ КР 1816 ВЕ751, причем на шину адреса-данных подключен портО, а кстаршим разрядам адреса - порт 2.

Двунаправленные шинные формирователи 13 и 21, входящие в состав контроллера 1 главного абонента и периферийных микроконтроллеров 2-1-2-К, а также шинные формирователи 33-1, 33-2, 35-1 и 35-2, входящие в состав ЗУ 11 обмена, и шинные формирователи 52-55, входящие в состав блоков 15 и 23 управления, могут быть реализованы на микросхеме КР 580 ВА86, причем в случае использования однонаправленных шинных формирователей вход направления соединен с общим. Адаптеры магистрали 16 и 24 могут быть выполнены на микросхеме КР 1818 ВГ01, причем в данном изобретении используется только один канал, вход выборки и вход А/В соединен с общим.

Реверсивные счетчики 39-1 и 39-2 ЗУ 11 обмена и счетчик 48 адресов блоков 15 и 23 управления могут быть реализованы на микросхемах К 155 ИЕ7, а ПЛМ 41 - на микросхеме К 556 РТ1, запрограммированной согласно приводимым ниже логическим уравнениям, вход выборки соединен с общим.

Буферный регистр 46 может быть выполнен на микросхеме К580 ИР 82. Объектные адаптеры 27-1 - 27-Р входов и объектные адаптеры 28-1 - 28-М выходов могут быть любыми, как аналоговыми, так и дискретными,

ЗУ 11 обмена предназначено для независимой передачи информации от центрального процессора 10 к микроЭВМ 12 через первый порт 31-1 и от микроЭВМ 12 к центральному процессору 10 через второй порт 31-2 и для синхронизации работы центрального процессора 10 и микроЭВМ 12 с

целью организации конвейерной обработки.

Центральный процессор 10 проводит загрузку первого порта 31-1 и разгрузки второго порта 31-2, а микроЭВМ 12 - загрузку второго порта 31-2 и разгрузку первого порта 31-1.

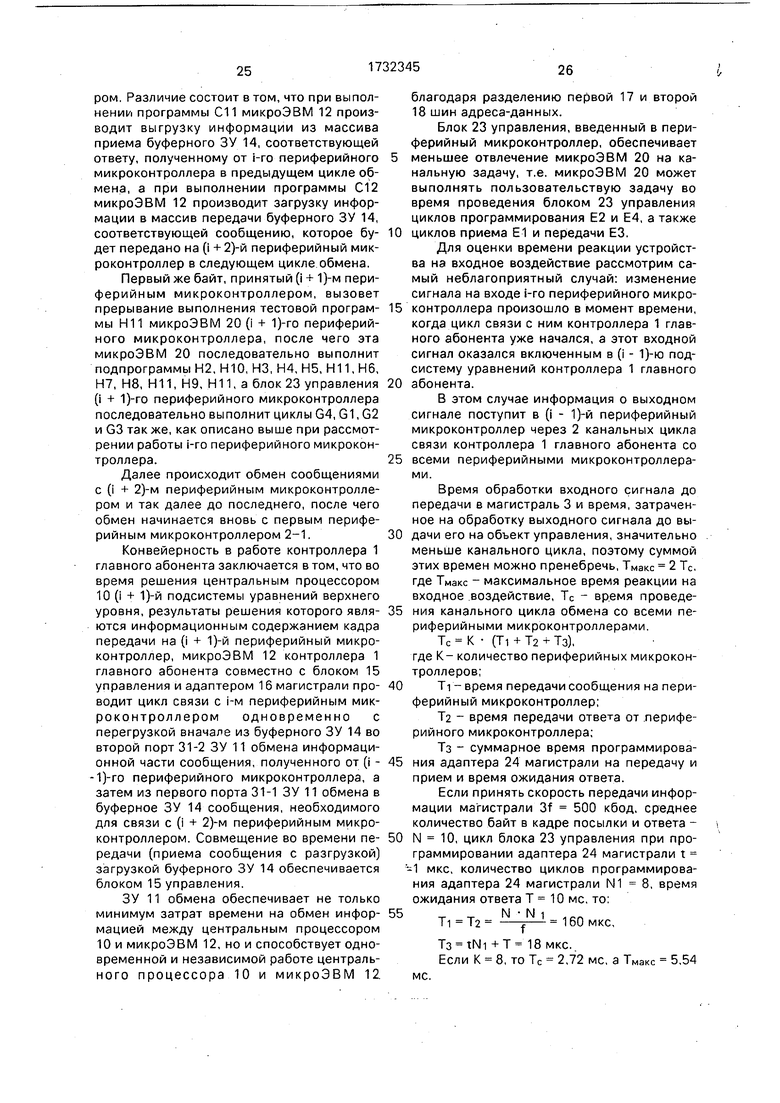

Команды обращения к ЗУ 11 обмена определяются состоянием входов дешифрато0 ров 40-1 и 40-2 режимов работы и приведены в табл.1,

Синхронизация обмена данными между процессором 10 и микроЭВМ 12 производится с помощью прерываний, осуществля5 емых через выходы первого 31-1 и второго 31-2 портов. Тип прерываний идентифицируется с помощью вектора, формат которого определяют три младшие разряда данных на входе-выходе первого или второго пор0 тов. В табл.2 приведены типы прерываний для процессора 10, а в табл.3 - для микро- ЭВМ 12.

Сигнал начальной установки (на фиг.З не показан) загружает все единицы в ревер5 сивные счетчики 39-1 и 39-2, устанавливает в 1 вторые триггеры 37-1 и 37-2 и сбрасывает в О первые триггеры 36-1 и 36-2 обоих портов. Это вызывает требование загрузки первого порта 31-1 со стороны центрзльно0 го процессора 10 и требование загрузки второго порта 31-2 со стороны микроЭВМ 12.

Загрузка первого порта 31-1 начинается с состояния реверсивного счетчика 39-1 11...1, и по мере загрузки его состояние уве5 личивается на единицу: 0000.,О, 0...01 и т.д. Выходы дешифраторов 38-1 и 38-2 записи каждого порта связаны с входами записи строк матрицы 40-1 и 40-2 дешифраторов следующим образом: первая строка - выход

0 дешифратора: 111...1; вторая строка-выход дешифратора: 00...0; третья строка - выход дешифратора: 00...01 и т.д.

По команде центрального процессора 10 Загрузка порта сигнал с третьего выхо5 да дешифратора 40-1 режимов работы, совпадающий по времени со стробирующим сигналом записи, поступает на входстроби- рования дешифратора 38-1 записи и увеличивает на единицу состояние реверсивного

0 счетчика 39-1 через вход прямого счета. Импульс с выхода дешифратора 38-1 первого порта производит запись информации с информационных входов матрицы 32-1 сдвиговых регистров в строку матрицы,

5 определяемую выходом дешифратора 38-1 записи. Увеличение состояния реверсивного счетчика 39-1 происходит по фронту окончания импульса.

В конце загрузки первого порта 31-1 центральный процессор 10 выдает команду

Конец загрузки, при которой сигнал с четвертого выхода дешифратора 40-1 режимов работы первого порта поступает на вход установки в 1 первого триггера 36-2 второго порта 31-2, что вызывает через выход второго порта 31-2 прерывание микроЭВМ 12 по требованию разгрузки, МикроЭВМ 12 начинает разгрузку первого порта 31-1 с состояния счетчика 39-1 этого порта, определяемого загрузкой последней строки.

По команде микроЭВМ 12 Разгрузка порта на втором входе дешифратора 40-2 режимов работы второго порта 31-2 появляется сигнал, совпадающий по времени со стробирующим сигналом чтения. Этот сиг- нал поступает на вход разрешения выхода первого шинного формирователя 33-1 первого порта 31-1 и тем самым считывает первую строку матрицы 32-1 сдвиговых регистров первого порта 31-1 на вход-выход второго порта 31-2 По фронту окончания этого сигнала происходит уменьшение состояния реверсивного счетчика 39-1 первого порта 31-1 через вход обратного счета счетчика и сдвиг информации в матрице 32- 1 сдвиговых регистров на одну строку через вход синхронизации: из второй строки в первую, из а-й строки в (а-1)-ю. Разгрузка последней записанной строки вызовет появление сигнала на выходе обратного пере- носа реверсивного счетчика 39-1, который установит в 1 второй триггер 37-1. Сигнал с выхода этого триггера через элемент ИЛИ 34-1 вызовет появление требования прерывания центрального процессора 10 на выходе первого порта 31-1 и требования прерывания микроЭВМ 12 на выходе второго порта 31-2 по концу разгрузки первого порта 31-1.

В конце разгрузки первого порта 31-1 состояние реверсивного счетчика 39-1 вновь станет 1...1, а значит первый порт подготовлен к новой загрузке.

Команда Считывание вектора выдается в ответ на требование прерывания. На первом выходе дешифратора 40-1 режимов работы появляется сигнал, который через вход разрешения выхода второго шинного формирователя 35-1 подключает выходы первого 36-1 и второго 37-1 триггеров пер- вого порта 31-1 и второго триггера 37-2 второго порта 31-2 к входам-выходам первого порта 31-1. Фронт окончания этого импульса сбрасывает в О первый 36-1 и второй 37-1 триггеры первого порта 31-1.

Работа ЗУ 11 обмена по загрузке второго порта 31-2 и разгрузке первого порта 31-1 со стороны микроЭВМ 12 происходит аналогично.

Блок 15 управления в контроллере 1 главного абонента предназначен для автоматического программирования адаптера 16 магистрали на режим передачи или приема через буферное ЗУ 14 для обеспечения режима прямого доступа в буферное ЗУ 14 со стороны адаптера 16 магистрали в режиме приема или передачи, для обеспечения загрузки и разгрузки буферного ЗУ 14 со стороны микроЭВМ 12 и для выборки ЗУ 11 обмена при обращении к нему со стороны микроЭВМ 12.

МикроЭВМ 12 обращается к блоку 15 управления и к ЗУ 11 обмена как к внешней памяти данных, адрес которой определяется пятью старшими разрядами: с четвертого по восьмой входы блока 15 управления. При значении третьего старшего разряда адреса (шестой вход блока 15 управления) равном единице микроЭВМ 12 обращается к ЗУ обмена, а при значении равном нулю - к блоку 15 управления.

Основная часть схемы блока управления реализована на ПЛМ 41. Работу ПЛМ 41 можно описать с помощью логических уравнений, в которых входы ПЛМ 41 обозначены через Х1-Х16,а выходы - Y1-Y15.

Y1 Х5-Х16 + Х1 Х2 (Х13-Х8 + Х14-Х9 + 0(15)

Y2 X7X10X11 X12 Х16- -У2 Х4 Х9-Х14

Y3 Х6 Х10 Х11 Х12-Х16 + ХЗ-Х8-Х13 +

X3-X1j5

Y4 Х7-Х10-Х11 Х12 Х16 + Х2-Х4 Х8 Х13

+Х2Х4Х15

J75 J§-X10-XTI-X12-X16 + X3-X9-X14 Y6 X10X11 X12-X16 + X10-X11 Х12Х16

Y7 Х13-Х8 + Х14 Х9 + Х16

Y8 X7X10-X11-X12

Y9 X15-XTO-X11 X12 + Х7 Х10Х11 Х12

Y10 - Х1 + Х4

X5X10X11 X12

Y12 X1;X3

YT3 Х6 :Х10-ХГ1 Х12

Y14 xi 1 xi 2

Y15 X7-X10-X11-X12

В уравнениях знак . обозначает логическое умножение, а знак + логическое сложение.

С помощью ПЛМ 41 формируются:

Y1 - стробирующий сигнал адреса буферного ЗУ на третьем выходе блока 15 управления;

Y2 - стробирующий сигнал записи буферного ЗУ 14 на четвертом выходе блока 15 управления;

Y3 - стробирующий сигнал чтения буферного ЗУ 14 на пятом выходе блока 15 управления;

Y4 - стробирующий сигнал записи адаптера 16 магистрали на девятом выходе блока 15 управления;

Y5 - стробирующий сигнал чтения адаптера 16 магистрали на десятом выходе блока 15 управления;

Y6-сигнал разрешения выхода двунаправленного шинного формирователя 13 на восьмом выходе блока 15 управления;

Y7 - сигнал требования внутреннего цикла;

Y8-сигнал записи блокировки внутреннего цикла;

Y9 - сигнал загрузки или разгрузки буферного ЗУ 14;

Y1U - признак проведения внутреннего цикла;

Y11 - сигнал загрузки номера массива и номера начальной ячейки буферного ЗУ 14 при выполнении команды записи режима;

Y12 - сигнал разрешения выхода для второго шинного формирователя 53, через который выдается номер ячейки буферного ЗУ 14 при выполнении внутреннего цикла;

Y13 - сигнал разрешения выхода для буферного регистра 46 при выполнении операции чтения вектора;

Y14 - сигнал разрешения выхода для первого шинного формирователя 52 при выполнении операции чтения адреса;

Y15 - сигнал загрузки режима при выполнении команды записи режима работы.

Тактовый генератор 42 и регистр 43 сдвига предназначены для обеспечения временной привязки сигналов на выходах ПЛМ 41 при выполнении запрограммированных в регистре 44 режимов работы блока 15 управления, рассчитанных на 8 тактов.

Регистр 45 состояния служит для хранения признаков окончания режима передачи, конфликта за обладание буферным ЗУ 14 и прерывания от адаптера 16 магистрали. Появление любого признака вызывает сигнал прерывания на втором выходе блока 15 управления и формирует вектор этого прерывания в буферном регистре 46.

Регистр 47 расширения адреса совместно с четвертым шинным формирователем 55 служит для формирования старших разрядов адреса буферного ЗУ 14 при выполнении режимов передачи, приема и программирования адаптера 16 магистрали, а третий шинный формирователь 54 служит для формирования старших разрядов адреса при обращении к буферному ЗУ 14 со стороны микроЭВМ 12.

Счетчик 48 адресов служит для формирования и хранения младших разрядов адреса буферного ЗУ 14. Первый шинный формирователь 52 обеспечивает считывание состояния счетчика 48 адресов на входы-выходы блока 15 управления, а второй шинный формирователь 53 - на одиннадцатый выход блока 15 управления.

D-триггер 50 совместно с элементом

ИЛИ 57 формирует признак выполнения очередного цикла режима работы блока 15 управления, а совместно с элементом И-НЕ 60 - признак конфликта. RS-триггер 49, ре0 гистр 49, регистр 43 сдвига, элемент И 59 и элемент НЕ 61 обеспечивают длительность выполнения циклов режима работы блока 15 управления в количестве 8 тактов тактового генератора 42.

5 RS-триггер 51 блокирует выполнение циклов режима работы блока 15 управления при повторном после конфликта выполнении операций загрузки или разгрузки буферного ЗУ 14 со стороны микроЭВМ 12.

0 Сигнал с седьмого выхода Y7 ПЛМ 41 является требованием проведения очередного внутреннего цикла обмена информацией адаптера 16 магистрали с буферным ЗУ 14. Этот сигнал можно заблокировать

5 через элемент И 59 командой Блокировка цикла, при которой через выход У8 ПЛМ 41 второй RS-триггер 51 будет установлен в 1. Сбрасывается в ноль второй RS-триггер 51 через выход Y9 ПЛМ 41 при проведении

0 повторного после конфликта обмена информацией микроЭВМ 12 с буферным ЗУ 14. Сигнал с выхода Y10 ПЛМ 41 является признаком проведения внутреннего цикла. С помощью D-триггера 50, на вход синхрони5 зации которого поступает с первого входа блока 15 управления стробирующий сигнал адреса от микроЭВМ 12, и второго элемента ИЛИ 57 осуществляется привязка внутреннего цикла к проводимойЪперации загрузки

0 и разгрузки .буферного ЗУ 14 со стороны микроЭВМ 12, а элемент И-НЕ 60 служит для выявления конфликта и записи во второй триггер регистра 45 состояния требования прерывания, которое через третий

5 элемент ИЛИ 58 поступает на второй выход блока 15 управления.

Кроме того, сигнал с выхода второго элемента ИЛИ 57 управляет входом разрешения выхода третьего шинного формиро0 вателя 54 при проведении операции разгрузки или загрузки буферного ЗУ 14 со стороны микроЭВМ 12 или входом разрешения выхода четвертого шинного формирователя 55 через третий элемент НЕ 63 при

5 проведении внутреннего цикла.

Запись старших разрядов адреса с седьмого и восьмого входов блока управления в регистр 47 расширения адреса производится при операции Запись режима сигналом, поступающим с одинадцатого выхода Y11 матрицы ПЛМ 41 и совпадающим по времени со стробирующим сигналом адреса на первом входе блока 15 управления. Стробирующий сигнал с двенадцатого выхода Y12 ПЛМ 41 разрешает выдачу адреса ячейки буферного ЗУ 14 сообщений со счетчика 48 адресов через второй шинный формирователь 53 на одиннадцатый выход блока управления при внутреннем цикле. По фронту окончания этого сигнала происходит увеличение информации в счетчике 48 адресо. Сигнал с выхода прямого переноса счетчика 48 адресов сбрасывает регистр 44 режимов и устанавливает в 1 первый триггер регистра 45 состояния.

На тринадцатом выходе Y13 ПЛМ 41 сигнал появляется при операции Чтение вектора прерывания. Этот сигнал разрешает считывание информации с буферного регистра 46 на шину 64 адреса-данных, одновременного производится сброс регистра 45 состояния.

Сигнал с четырнадцатого выхода Y14 ПЛМ 41 поступает на вход разрешения выхода первого шинного формирователя 52, через который производится считывание состояния счетчика 48 адресов на шину 64 адреса-данных при операции Чтение адреса.

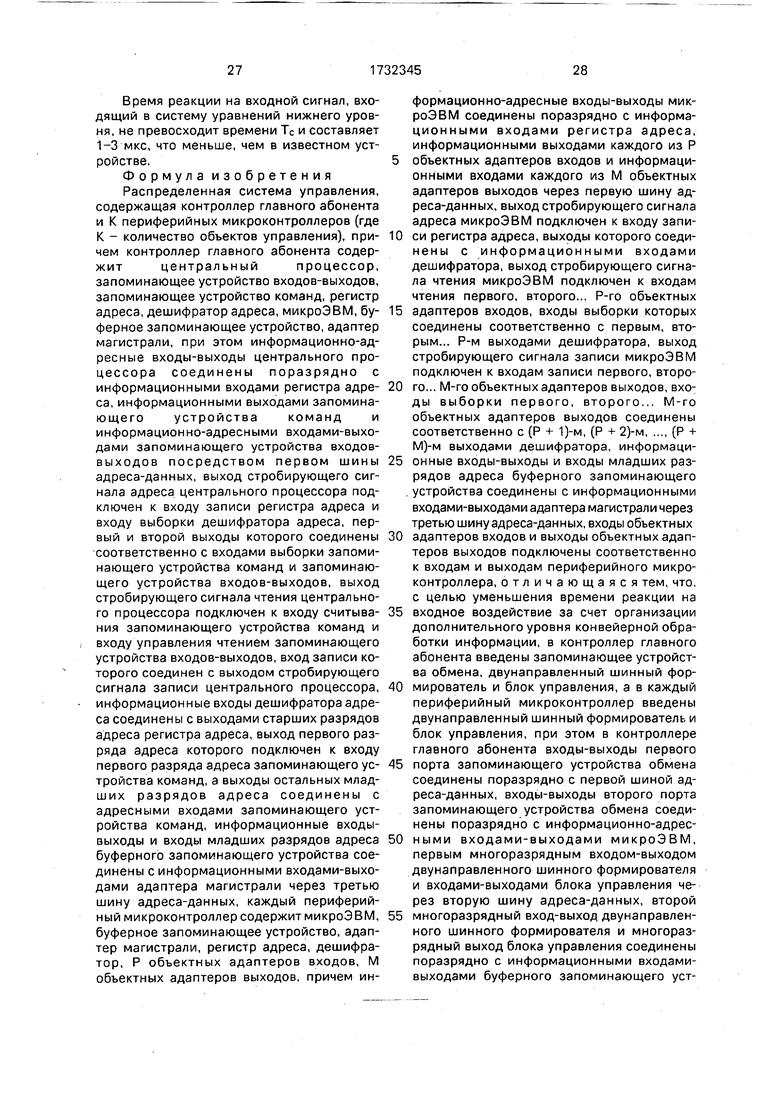

В табл.4 приведены команды обращения микроЭВМ 12 к блоку 15 управления.

По команде Запись режима происходит загрузка регистра 47 расширения адреса номером массива буферного ЗУ 14 сообщений и счетчика 48 адресов номером начальной ячейки массива. Номера массивов буферного ЗУ 14 сообщений определяются четвертым и пятым старшими разрядами микроЭВМ 12 и соответствуют: массив программирования на передачу -11; массив программирования на прием - 01; массив передаваемых данных - 10; массив принимаемых данных - 00.

Информация о выполняемом режиме определяется тремя младшими разрядами шины 64 адреса-данных и запоминается в регистре 44 режимов. Загрузка производится сигналом с пятнадцатого выхода Y15 ПЛМ 41, совпадающим по времени со стробирующим сигналом записи на третьем входе блока 15 управления. Разряды регистра 44 режимов определяют: первый разряд - режим передачи; второй разряд - режим приема; третий разряд - режим программирования.

Сигнал начальной установки (на фиг.4 и 5 не показан) загружает нули (сбрасывает) в регистр 45 состояния, в регистр 44 режимов и регистр 43 сдвига, после чего микроЭВМ

12 посредством команд загрузки буферного ЗУ 14 перегружает из внутреннего постоянного запоминающего устройства микроЭВМ 12 в массив программирования буферного ЗУ 14 информацию, предназначенную для

программирования адаптера 16 магистрали на прием и передачу, и выдает команду записи режима программирования на передачу.

Выдача команды Загрузка режима программирования инициирует выполнение непрерывной последовательности внутренних циклов переписи информации из буферного ЗУ 14 в адаптер 16 магистрали, что обеспечивает настройку адаптера на прием

или передачу информации по последовательной магистрали 3.

После получения информации для передачи от центрального процессора 10 через ЗУ 11 обмена микроЭВМ 12 перегружает ее

в массив передачи буферного ЗУ 14 и выдает команду Запись режима передачи. При выдаче команды записи режима передачи в регистр 47 расширения адреса загружается номер массива передаваемых данных, в

счетчик 48 адресов загружается адрес начала массива, а в регистр 44 режимов - признак режима передачи. Сигнал с седьмого выхода блока 15 управления поступает одновременно на вход второго старшего разряда буферного ЗУ 14 и вход признака Команда - данные адаптера 16 магистрали. Так как значение этого разряда буферного ЗУ 14 при режимах Прием и Передача равно нулю, то записываемая в адаптер 16

магистрали информация будет восприниматься как передаваемые данные. Диаграмма работы блока 15 управления в режиме Передача приведена на фиг.7а. Появление на восьмом входе Х8 ПЛМ 41

(девятый вход блока 15 управления) сигнала требования прямого доступа в буферное ЗУ 14 при передаче вызывает появление сигнала на седьмом выходе Y7 ПЛМ 41, Второй RS-триггер 51 находится в сброшенном состоянии. Следовательно, на выходе элемента И 59 будет единица, которая запишется в первый RS-триггер 49. Инверсный выход первого RS-триггера 49 через первый элемент НЕ 61 установит единицу на последовательном входе регистра 43 сдвига и первый же импульс с выхода генератора 42 тактовых импульсов запишет единицу в первый триггер регистра 43 сдвига, а последующие импульсы передвинут единицу во

второй, третий, четвертый триггеры. Выход четвертого триггера регистра 43 сдвига сбросит первый RS-триггер 49 и через первый элемент НЕ 61 изменит состояние сигнала на последовательном входе регистра 43 сдвига на противоположное и последовательно установит в нуль все его триггеры.

Из сигналов на первых четырех входах Х1-Х4 ПЛМ 41 будут сформированы строби- рующий сигнал адреса на ее первом выходе Y1 и чтения на третьем выходе Y3 для буферного ЗУ 14, а также стробирующий сигнал записи на четвертом выходе Y4 для адаптера 16 магистрали.

Появление сигнала на двенадцатом выходе V12 ПЛМ 41 обеспечит разрешение выхода второго шинного формирователя 53, через который младшие разряды адреса буферного ЗУ 14 будут выданы на одиннадцатый выход блока 15 управления (третья шина 19 адреса-данных), а стробирующий сигнал адреса с первого выхода 41 ПЛМ (третьего выхода блока 15 управления) зафиксирует адрес в адресном регистре буферного ЗУ 14, после чего на третью шину 19 адреса-данных по сигналу Чтение ЗУ (сигнал с третьего выхода УЗ ПЛМ 41) поступят данные из буферного ЗУ 14, которые будут записы в адаптер 16 магистрали по сигналу Запись в адаптер (сигнал с пятого выхода Y5 ПЛМ 41).

Фронт начала стробирующего сигнала записи на девятом выходе блока 15 управления сбросит в нуль на выходе требования прямого доступа передачи в адаптере 16 магистрали, однак о состояние первого RS- триггера 49 будет определяться состоянием сигнала на выходе четвертого разряда регистра 43 сдвига, который через четыре тактовых импульса после начала цикла станет единицей, сбросит первый RS-триггер 49, а еще через четыре тактовых импульса станет нулем. Цикл передачи одного слова закончится. Фронт окончания сигнала на одиннадцатом выходе Y12 ПЛМ 41 увеличит состояние счетчика 48 адресов тем самым будет подготовлен адрес ячейки буферного ЗУ 14, в котором хранится следующее слово передаваемой информации. Описанный цикл будет повторяться с каждым приходом единичного сигнала с выхода адаптера 16 магистрали на девятый вход блока 15 управления.

Режим передачи заканчивается при появлении сигнала на выходе прямого переноса счетчика 48 адресов, Этот сигнал устанавливает в 1 первый триггер регистра 45 состояния и через первый элемент ИЛИ 56 сбрасывает регистр 44 режимов, а

через третий элемент ИЛИ 58 и второй выход блока 15 управления вызывает прерывание микроЭВМ 12 по окончании передачи. Работа блока 15 управления в режиме

Программирование протекает аналогично режиму передачи, В третий разряд регистра 44 режимов записывается 1, в счетчик 48 адресов - начало массива программирова ния, а в регистр 47 расширения адреса

номер массива, второй разряд которог всегда будет единицей, что является признг ком Команда для адаптера 16 магистрал Сигнал с выхода третьего разряда регистр 44 режимов (пятнадцатый вход Х15 ПЛМ 4

вызывает требование внутреннего цикла н седьмом выходе Y7 ПЛМ 41 без подтвер дения сигналами на девятом и десятом вхс дах блока 15 управления, последовательность внутренних цикло

протекает непрерывно до появления сигн; ла на выходе прямого переноса счетчика 4 адресов.

Для задания режима приема необход1 мо записать единицу во второй разряд peri.

стра 44 режимов, а в регистр 47 расширени адреса - нули, что является признаком мае сива приема. Младшая часть адреса (начал массива) задается числом 0...0, поэтому режиме приема не возникает сигнала nps

мого переноса на выходе счетчика 48, окончанием режима приема является сигнап требования прерывания от адаптера 16 магистрали, приходящий на одиннадцатый вход блока 15 управления.

Диаграмма работы блока 15 управления в режиме приема приведена на фиг.7Б.

Начало очередного цикла приема вызывается сигналом на десятом входе блока 15 управления (девятый вход Х9 ПЛМ 41). При

выполнении цикла на третью шину 19 адреса-данных сигналом с двенадцатого выхода Y12 ПЛМ 41, который соединен с входом разрешения выхода второго шинного формирователя 53, через этот шинный формирователь выдается адрес ячейки буферного ЗУ 14, а через четвертый шинный формирователь 55 - номер массива буферного ЗК 14 Затем сигналом с пятого выхода Y5 ПЛМ 41 считывается информация с адаптера 16 магистрали на третью шину 19 адреса-данных и записывается в буферное ЗУ 14 сигналом с второго выхода Y2 ПЛМ 41.

Сигнал, появляющийся на одиннадцатом входе блока 15 управления и проходящий через первый элемент ИЛИ 56, сбрасывает регистр 44 режимов и устанав ливает в единицу третий разряд регистра 4Е состояния, что вызывает появление сигнале

прерывания по концу приема на втором выходе блока 15 управления,

Чтобы узнать адрес ячейки буферного ЗУ 14, в которую проведена запись послед- него принятого адаптером 16 магистрали слова, необходимо выдать команду чтения адреса, при выполнении которой состояние счетчика 48 адресов через первый шинный формирователь 52, вход разрешения выхода которого соединен с четырнадцатым выходом 14 ПЛМ 41, будет выдано на шину 64 адреса-данных.

При выполнении команды чтения вектора прерывания на тринадцатом выходе Y13 ПЛМ 41, соединенном с входом разрешения выхода буферного регистра 46, возникает сигнал, обеспечивающий считывание состояния буферного регистра 46 на шину 64 адреса данных и одновременный сброс регистра 45 состояния. Перепись информации из регистра 45 состояния в буферный регистр 46 производится сигналом на первом входе блока 15 управления, который возникает при выполнении любой операции микроЭВМ 12.

С целью превышения быстродействия работы системы микроЭВМ 12 можно проводит загрузки или разгрузку буферного ЗУ 14 во время работы блока 15 управления в режиме Прием или Передача. При скорости передачи информации по последовательной магистрали 3 500 кбод передача одного слова составляет 16 мкс, а цикл обмена информацией адаптера 16 магистрали с буферным ЗУ 14-1 мкс при частоте тактовых импульсов 8 мГц. Длительность команды загрузки или разгрузки буферного ЗУ 14 со стороны микроЭВМ 12 составляет 1 мкс, т.е. в течение 16 мкс возможно положение двух операций длительностью 1 мкс каждая, В процессе проектирования распределенной системы управления построена математическая модель системы. Расчет вероятности возникновения конфликта на модели дал влеичину менее 0,06.

Возникновение конфликта фиксируется во втором разряде регистра 45 состояния схемой, образованной D-триггером 50, вторым элементом ИЛИ 57 и элементом И-НЕ 60.

Диаграмма, поясняющая выявление конфликтной ситуации, приведена на фиг.7В, Диаграмма описывает выполнение внутреннего цикла передачи, одновремен- ную выдачу команды загрузки буферного ЗУ 14.

Во время проведения внутреннего цикла приема на десятом выходе Y10 ПЛМ 41

будет 1, которая записывается в D-триггер 50 сигналом с первого входа блока 15 управления. Второй элемент ИЛИ 57 формирует признак внутреннего цикла, который может возникнуть в любой момент времени выполнения команд загрузки или разгрузки буферного ЗУ 14. На девятом выходе Y9 ПЛМ 41 сигнал появляется при командах загрузки или разгрузки буферного ЗУ 14 в моменты времени, совпадающие со стробирующими сигналами чтения или записи на втором и третьем входах блока 15 управления. Сигнал с выхода элемента И-НЕ 60 записывает единицу во второй разряд регистра 45 состояния, что является признаком возникновения конфликта. При конфликте внутренний цикл обмена информацией адаптера 16 магистрали с буферным ЗУ 14 проходит без искажений, а команду загрузки или разгрузки буферного ЗУ 14 необходимо повторить, чтобы обеспечить бесконфликтное выполнение повторной команды загрузки или разгрузки буферного ЗУ 14, необходимо заблокировать возможность возникновения внутреннего цикла выдачей команды блокировки цикла. При выполнении этой команды сигнал на восьмом выходе Y8 ПЛМ 41 устанавливает в 1 второй RS-триггер 51, обеспечивая блокировку. Второй RS-триггер 51 будет сброшен сигналом чтения или записи буферного ЗУ 14 с девятого выхода Y9 ПЛМ 41 при повторной команде, но внутренний цикл начнется даже при наличии 1 на седьмом выходе Y7 ПЛМ 41 только после завершения команды загрузки или разгрузки буферного ЗУ 14.

Команды загрузки или разгрузки адаптера 16 магистрали выполняются аналогично командам обращения к буферному ЗУ 14. Конфликт за обладание буферным ЗУ 14 при выполнении этих команд не возникает, так как микроЭВМ 12 обменивается информацией с адаптером 16 магистрали после окон- чания режима передачи или приема. Например, в случае использования в качестве адаптера 16 магистрали микросхемы К1818ВГ01 - это команды загрузки кода Сброс антипереполнения для передачи контрольного полинома или команды загрузки-выгрузки кодов для считывания регистра ошибок в конце приема сообщения.

Блок 23 управления в периферийных микроконтроллерах предназначен для автоматического программирования адаптера 24 магистрали на режим передачи или приема через буферное ЗУ 22, для обеспечения режима прямого доступа в буферное ЗУ 22 со стороны адаптера 24 магистрали в режиме приема или передачи, для обеспечения

загрузки и разгрузки буферного ЗУ 22 со стороны микроЭВМ 20 и для выборки дешифратора 26 при обращении к объектным адаптерам 27-1-27-Р входов и объектным адаптерам 28-1-28-М выходов со стороны микроЭВМ 20.

В периферийных микроконтроллерах 2- 1-2-К в адресном пространстве микроЭВМ 20 место ЗУ обмена занимают объектные адаптеры входов и выходов. Поэтому при значении третьего старшего разряда адреса, равном нулю, микроЭВМ 20 обращается к блоку 23 управления, а при значении, равном единице - через дешифратор к объект- ным адаптерам входов и выходов. В остальном работа блока 23 управления в периферийных микроконтроллерах 2-1-2-К аналогична работе блока 15 управления в контроллере 1 главного абонента, описанной выше.

Управление распределенными объектами или частями сложного объекта осуществляется путем решения системы уравнений, в которых независимыми переменными являются состояния датчиков объекта управления (на фиг.1 не показаны), подключенных к входам 5-1-1-5-Р-К периферийных микроконтроллеров 2-1-2-К, а результатами решения - сигналы, выдаваемые на исполнительные электромеханизмы через выходы 4-1-1-4-М-К, Вся система уравнений реализована в двух уровнях: нижний уровень - системы уравнений, описывающие различные объекты управления или части сложного объекта; верхний уровень - системы уравнений, описывающие взаимные связи объектов управления или частей объекта управления.

Системы уравнений нижнего уровня решаются в периферийных микроконтроллерах 2-1-2-К, а системы уравнений верхнего уровня решает центральный процессор 10 в контроллере 1 главного абонента. Выходные сигналы уравнений, решаемых в данном периферийном микроконтроллере, формируются на основе только его входных сигналов. Выходные сигнали уравнений верхнего уровня, поступившие от контроллера 1 главного абонента на данный периферийный микроконтроллер, зависят от состояния входных сигналов других периферийных микроконтроллеров.

Обмен информацией между контроллером 1 главного абонента и периферийными микроконтроллерами 2-1-2-К осуществляется с помощью сетевой задачи, алгоритм которой помещен во внутреннее ПЗУ микроЭВМ 12 контроллера 1 главного абонента и микроЭВМ 20 периферийных микроконтроллеров 2-1-2-К.

Физическое сопряжение (протокол физического уровня) обеспечивают адаптеры

16 и 24 магистрали. Передаваемые и принимаемые сообщения, а также информация, необходимая для программирования адаптеров 16 и 24 магистрали, хранятся в буферных ЗУ сообщений 14 и 22.

Двунаправленный шинный формирователь 13 контроллера 1 главного абонента обеспечивает разделение первой 17 и третьей 19 шин адреса-данных при раздельной работе микроЭВМ 12 и адаптера 16 магистрали и

подсоединение микроЭВМ 12 к буферному ЗУ 14 сообщений при обмене с ним информацией. Аналогичным образом двунаправленный шинный формирователь 21 каждого периферийного микроконтроллера обеспечивает разделение первой 29 и второй 30 шин адреса-данных при раздельной работе микроЭВМ 20 и адаптера 24 магистрали и подсоединение микроЭВМ 20 к буферному ЗУ 22 сообщений при обмене с ним информацией.

В основу сетевой задачи положен принцип запрос - ответ. МикроЭВМ 12 контроллера 1 главного абонента обращается последовательно ко всем периферийным

микроконтроллерам 2-1-2-К, посылая на них информацию об изменившихся выходах, если эти изменения произошли. В ответном сообщении каждый периферийный микроконтроллер подтверждает прием сообщения и сопровождает ответ информацией об изменившихся входных сигналах, относящихся к уравнениям верхнего уровня.

Кадрами инициализации связи обмениваются после включения питания или невосстановимого нарушения связи.

С помощью супервизорных кадров производится запрос информационного кадра или ответ на принятый кадр.

Информационные кадры содержат индентификатор сообщения и его информационное содержание.

Состав кадров и их структуры приведены в табл.5.

Использование контролирующего полинома позволяет осуществить задачу передаваемой информации и при сбоях провести повторную передачу без инициализации системы. Команды логического уровня обеспечивают запись, чтение, тестирование

входов-выходов каждого периферийного микроконтроллера, запуск и останов задач периферийного микроконтроллера, обмен результатами тестирования и т.д.

МикроЭВМ 20 каждого периферийного микроконтроллера, помимо сетевой задачи, выполняет пользовательскую задачу, алгоритм которой приведен на фиг.8.

Вызов пользовательской задачи произ- водится таймером (входящим в состав мик- роЭВМ 20), время цикла работы которого больше суммы времен выполнения самых длинных ветвей сетевой программы и пользовательской.

Программный модуль сканирования включает в себя последовательный опрос всех входных сигналов объектных адаптеров входов, при необходимости их предварительную обработку, например цифровую фильтрацию, и сравнение полученных значений входных сигналов со значениями сиг- налов предыдущего цикла. В случае изменения сигналов из них выделяются сигналы, относящиеся к уравнениям верхнего уровня, и производится формирование ответного сообщения.

При появлении новых значений сигналов, относящихся к уравнениям нижнего уровня, проводится цикл решения этих уравнений. Результаты решения выдаются на объект управления в виде команд через объектные адаптеры выходов.

Некоторые входные сигналы могут одновременно входить в системы уравнений верхнего и нижнего уровней. В этом случае вначале формируется ответное сообщение, затем решается система уравнений нижнего уровня.

Если в сетевой задаче от главного або- нента принят информационный кадр, его содержание выдается на объектные адаптеру выходов в виде выходных команд.

Система уравнений верхнего уровня, которую решает центральный процессор, разбита на ряд подсистем. Каждая подсистема определяется принадлежностью выходных сигналов к определенному периферийному микроконтроллеру. Переход к решению (+2)-й подсистемы централь- ный процессор 10 осуществляет после окончания решения (1+1)-й подсистемы и прихода ответного сообщения от(И)-го периферийного микроконтроллера, которое микроЭВМ 12 контроллера 1 главного або- нента передает на центральный процессор 10 через второй порт 31-2 ЗУ 11 обмена. Вначале центральный процессор 10 контроллера 1 главного абонента разгружает второй порт 31-2 и размещает полученные новые значения входов в ЗУ 6 входов-выходов, а затем решает подсистему уравнений и результаты решения размещает в первом порте 31-1.

Если в результате решения получаются новые значения выходов, формируется информационный кадр; если значения выходов не изменились - супервизорный кадр. Аналогично в периферийных микроконтроллерах при появлении новых значений входных сигналов, относящихся к уравнениям верхнего уровня, формируется в ответном сообщении информационный кадр; если изменений нет - супервизррный кадр.

Распределенная система управления работает следующим образом.

После включения источника питания и установки системы в исходное состояние сигналом начальной установки (его действие описано выше) центральный процессор 10 и микроЭВМ 12 контроллера 1 главного абонента и микроЭВМ 20 в периферийных микроконтроллерах 2-1-2-К выполняют программы тестирования всех подключенных к ним блоков. Контроллер 1 главного абонента опрашивает последовательно все периферийные микроконтроллеры 2-1-2-К о результатах текстирования и посылает на них команду готовности, на основании которой периферийные микроконтроллеры 2-1- 2-К подключают питание к исполнительным механизмам объектов управления и переходят к выполнению пользовательской задачи согласно алгоритму, приведенному на фиг.8. Контроллер 1 главного абонента начинает решать подсистемы уравнений верхнего уровня. Решение каждой подсистемы уравнений заканчивается передачей результатов через первый порт 31-1 ЗУ 11 обмена на микроЭВМ 12, которая формирует сообщение на тот периферийный микроконтроллер, к которому относится данная подсистема. В ответном сообщении этот периферийный микроконтроллер посылает информацию об изменившихся входных сигналах, отнесенных к системе уравнений верхнего уровня.

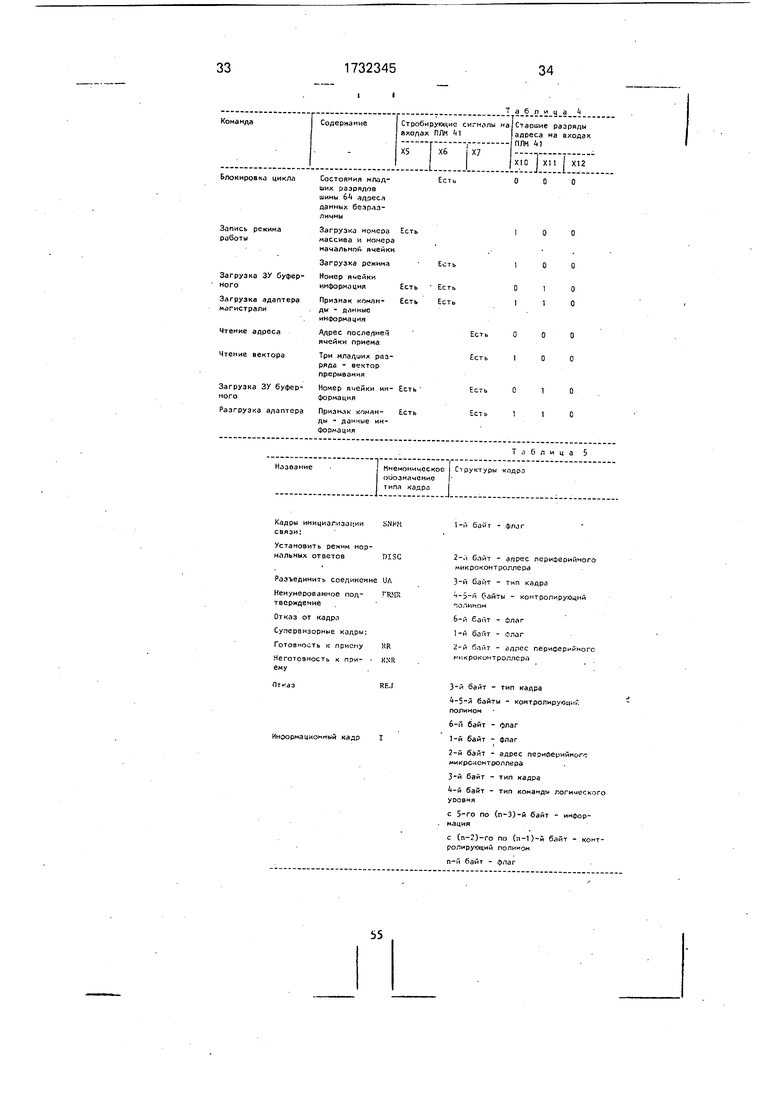

Взаимодействие всех блоков системы во время обмена сообщениями контроллера 1 главного абонента с i-м и (i + 1)-м периферийными микроконтроллерами показано на фиг.7, на которой приняты следующие обозначения:

А - программы работы центрального процессора 10;

А1 - программа решения (i + 1)-й подсистемы уравнения верхнего уровня и загрузки первого порта 31-1 ЗУ 11 обмена;

А2 - программа разгрузки второго порта 31-2 ЗУ 11 обмена и размещения в ЗУ 6 входов - выходов информации о входных сигналах, поступившей от (i - 1)-го периферийного микроконтроллера;

A3 - программа решения (i + 2)-й подсистемы уравнений верхнего уровня и загрузки первого порта 31-1 ЗУ 11 обмена;

А4 - программа разгрузки второго порта 31-2 ЗУ 11 обмена и размещение в ЗУ 6 входов-выходов информации о входных сигналах, поступившей от i-ro периферийного микроконтроллера;

А5 - выполнение тестов;

В - требования прерывания от ЗУ 11 обмена;

81- прерывание центрального процессора 10 по требованию разгрузки второго порта 31-1;

82- прерывание микроЭВМ 20 по требованию разгрузки первого порта 31-1;

83- прерывание микроЭВМ 12 по требованию загрузки второго порта 31-2;

84- прерывание центрального процессора 10 по требованию загрузки первого порта 31-1;

С - программы работы микроЭВМ 12;

С1 - подготовка и выдача команды записи режима программирования адаптера 16 магистрали на передачу;

С2 - подготовка и выдача команды записи режима передачи;

СЗ, СЮ - разгрузка массива приема буферного ЗУ 14 и загрузка второго порта ЗУ 11 обмена;

С4 - подготовка и выдача команды записи режима программирования адаптера 16 магистрали на прием;

С5 - выдача команды записи режима приема;

С6, С11 - разгрузка первого порта 31-1 ЗУ 11 обмена и загрузка массива передачи буферного ЗУ 14;

С7 - проверка правильности полученного ответа;

С8 - выполнение команды чтения адреса;

С9 - выполнение тестовой задачи;

D - циклы работы блока 15 управления;

D1 - циклы программирования адаптера 16 магистрали на передачу;

D2 - циклы передачи;

D3 - циклы программирования адаптера 16 магистрали;

D4 - циклы приема;

Е - циклы работы блока 23 управления i-ro периферийного микроконтроллера;

G - циклы работы блока 23 управления (i + 1)-го периферийного микроконтроллера;

Е1, G1 - циклы программирования адаптера 24 магистрали на передачу;

Е2, G2 - циклы передачи;

ЕЗ, G3 - циклы программирования адаптера 24 магистрали на прием;

Е4, G4 - циклы приема;

F - программы работы микроЭВМ 20

i-ro периферийного микроконтроллера;

Н - программы работы микроЭВМ 20 (г + 1)-го периферийного микроконтроллера;

F1, Н1 - программа пользовательской задачи;

F2, Н2 - подготовка и выдача команды записи режима приема;

F3, НЗ - проверка правильности полученного сообщения;

F4, Н4 - выполнение команды чтения

адреса;

F5, Н5 - подготовка и выдача командь записи режима программирования адапте ра 24 магистрали на передачу; F6, Н6 - подготовка и выдача командь

записи режима передачи;Р7, Н7 - разгрузка массива приема буферного ЗУ 22;

F8, Н8 - выдача полученной информа ции о выходных сигналах на объектныб адаптеры 28-1-28-М выходов;

F9, Н9 - подготовка и выдача командь записи режима программирования адаптера 24 магистрали на прием;

F10. НЮ - загрузка массива передача буферного ЗУ 22 передаваемым ответом;

F11. Н11 - тестовая задача.

Началом отсчета времени Т0 на фиг.9 является момент подготовки и выдачи команды записи режима программирования на передачу С1. Эту команду выдает микро- ЭВМ 12 контроллера 1 главного абонента на блок 15 управления и переходит к выполнению тестовой задачи С9. Блок 15 управления начинает выполнение внутренних циклов программирования адаптера 16 магистрали на передачу D1, т.е. обеспечивает перепись массива программирования из буферного ЗУ 14 в адаптер 16 магистрали. В это время центральный процессор 10 решает (i + 1)-ю подсистему уравнений верхнего уровня, постепенно заполняя результатами первый порт 31-1 ЗУ 11 обмена, а периферийные микроконтроллеры 2-1-К-2 либо выполняют пользовательскую программу, либо прово- дят тестирование. На фиг,9 j-й и (i + 1)-й периферийные микроконтроллеры выполняют пользовательские задачи F1 и Н1.По окончании программирования блок 15 управления вырабатывает сигнал прерывания микроЭВМ 12. В прерывающей программе микроЭВМ 12 подготавливает и выдает команду записи режима передачи С2, по которой блок 15 управления начинает выполнять циклы переписи информации из массива передачи буферного ЗУ 14 в адаптер 16 магистрали, который преобразует эту информацию в последовательный код. Массив передачи буферного ЗУ 14 подготовлен заранее, процесс подготовки аналогичен описанному ниже для передачи на (i + 1)-й периферийный микроконтроллер (программа С6).

При выполнении адаптером 16 магистрали циклов передачи микроЭВМ 12 проводит разгрузку массива приема буферного ЗУ 14 и загрузку второго порта 31-1 ЗУ 11 обмена информацией, принятой от (i - 1)-го пери- ферийного микроконтроллера в предыдущем цикле связи (программа СЗ).

В передаваемом сообщении первый байт после флага - это номер вызываемого абонента - i-ro периферийного микроконтроллера, адаптер 24 магистрали которого выработает сигнал прерывания по первому принятому знаку, и через блок 23 управления i-ro периферийного микроконтроллера этот сигнап будет транслирован на микро- ЭВМ 20. МикроЭВМ 20 i-ro периферийного микроконтроллера подготавливает и выдает команду записи режима приема F2, на основании которой блок 23 управления начинает выполнять циклы приема Е4, т.е. переписывает принятую адаптером 24 магистрали информацию в массив приема буферного ЗУ 22 i-ro периферийного микроконтроллера, затем микроЭВМ 20 начинает загрузку массива передачи буферного ЗУ 22 (программа F10) ответным сообщением, которое было подготовлено в процессе решения пользовательской программы F1. Закончив загрузку буферного ЗУ 22, микроЭВМ 20 i-ro периферийного микроконтроллера вновь переходит к выполнению пользовательской программы F1, пока не возникнет сигнал прерывания по концу приема, на основании которого микроЭВМ 20 проверяет правильность принятого сообщения F3, затем выполняет команду чтения адреса F4 и выдает команду записи режима программирования адаптера 24 магистрали на передачу F5. В это время микроЭВМ 12 контроллера 1 главного абонента отрабатывает программу, вызванную сигналом прерывания от адаптера 16 магистрали по концу передачи: подготовка и запись режима программирования адаптера 16 магистрали на прием С4.

После окончания циклов программирования на передачу Е1 адаптера 24 магистрали 1-го периферийного микроконтроллера микроЭВМ 20 подготавливает и выдает команду записи режима передачи F6, по которой блок 23 управления начинает выполнять циклы передачи Е2 совместно с адаптером 24 магистрали. Прием первого байта этого сообщения контроллером 1 главного абонента вызовет

прерывание микроЭВМ 12, которая выдает команду записи режима приема С5, на основании которой блок 15 управления переписывает принятое сообщение в массив приема буферного ЗУ 14 циклами приема D4.

К этому моменту времени центральный процессор 10 закончил решение (i + 1)-й подсистемы уравнений верхнего уровня и закончил заполнение первого порта 31-1 ЗУ 11

обменаА1.

Конец загрузки первого порта 31-1 вызовет прерывание В2 микроЭВМ 12, которая начинает разгрузку первого порта 31-1 ЗУ 11 обмена и загрузку массива передачи

буферного ЗУ 14 (программа С6). Центральный процессор 10 в это время разгружает второй порт 31-2 ЗУ 11 обмена А2, размещая информацию о входных сигналах, принятую от (i - 1)-го периферийного микроконтроллера, в ЗУ 6 входов-выходов, и переходит к выполнению тестовой задачи А5, ожидая сигнала прерывания по кЪнцу разгрузки второго порта 31-2 ЗУ 11 обмена, с приходом которого (В4) начинает решение (i + 2)-й подсистемы уравнений верхнего уровня.

По окончании приема в контроллере 1 главного абонента возникает сигнал прерывания микроЭВМ 12, которая проверит правильность приема ответного сообщения С7,

считает адрес последней ячейки массива приема буферного ЗУ 14 (программа С8), который необходим в программе С11, и вновь выдаст команду С1. МикроЭВМ 20 i-ro периферийного контроллера выдает команду F9, тем самым подготавливает адаптер 24 магистрали к приему следующего сообщения и переходит к продолжению решения пользовательской задач и.

Цикл обмена сообщением контроллера 1 главного абонента с i-м периферийным микроконтроллером закончился (момент времени Ti) и начинается переход к обмену сообщением с (i + 1)-м периферийным микроконтроллером.

В процессе проведения обмена сообщением контроллера 1 главного абонента с (i + 1)-м периферийным микроконтроллером микроЭВМ 12 последовательно выполняет

программы С1, С9, С2, С11, С9, С4, С9, С5, С9, С12, С9, С7, С8, а блок 15 управления выполняет циклы D1, D2, D3, D4 так же, как описано выше при рассмотрении цикла обмена с i-м периферийным микроконтроллером. Различие состоит в том, что при выполнении программы С11 микроЭВМ 12 производит выгрузку информации из массива приема буферного ЗУ 14, соответствующей ответу, полученному от i-ro периферийного микроконтроллера в предыдущем цикле обмена, а при выполнении программы С12 микроЭВМ 12 производит загрузку информации в массив передачи буферного ЗУ 14, соответствующей сообщению, которое будет передано на (i + 2)-й периферийный микроконтроллер в следующем цикле обмена.

Первый же байт, принятый (i + 1)-м периферийным микроконтроллером, вызовет прерывание выполнения тестовой программы Н11 микроЭВМ 20 (i + 1)-го периферийного микроконтроллера, после чего эта микроЭВМ 20 последовательно выполнит подпрограммы Н2, НЮ, НЗ, Н4, Н5, Н11, Н6, Н7, Н8, Н11, Н9, Н11, а блок 23 управления (i + 1)-го периферийного микроконтроллера последовательно выполнит циклы G4, G1,G2 и G3 так же, как описано выше при рассмотрении работы i-ro периферийного микроконтроллера.

Далее происходит обмен сообщениями с (i + 2)-м периферийным микроконтроллером и так далее до последнего, после чего обмен начинается вновь с первым периферийным микроконтроллером 2-1.

Конвейерность в работе контроллера 1 главного абонента заключается в том, что во время решения центральным процессором 10 (i + 1)-й подсистемы уравнений верхнего уровня, результаты решения которого являются информационным содержанием кадра передачи на (i + 1)-й периферийный микроконтроллер, микроЭВМ 12 контроллера 1 главного абонента совместно с блоком 15 управления и адаптером 16 магистрали проводит цикл связи с I-M периферийным микроконтроллером одновременно с перегрузкой вначале из буферного ЗУ 14 во второй порт 31-2 ЗУ 11 обмена информационной части сообщения, полученного от (i - -1)-го периферийного микроконтроллера, а затем из первого порта 31-1 ЗУ 11 обмена в буферное ЗУ 14 сообщения, необходимого для связи с (i + 2)-м периферийным микроконтроллером. Совмещение во времени передачи (приема сообщения с разгрузкой) загрузкой буферного ЗУ 14 обеспечивается блоком 15 управления.

ЗУ 11 обмена обеспечивает не только минимум затрат времени на обмен информацией между центральным процессором 10 и микроЭВМ 12, но и способствует одновременной и независимой работе центрального процессора 10 и микроЭВМ 12

благодаря разделению первой 17 и второй 18 шин адреса-данных.

Блок 23 управления, введенный в периферийный микроконтроллер, обеспечивает

меньшее отвлечение микроЭВМ 20 на канальную задачу, т.е. микроЭВМ 20 может выполнять пользовательствую задачу во время проведения блоком 23 управления циклов программирования Е2 и Е4, а также

циклов приема Е1 и передачи ЕЗ.

Для оценки времени реакции устройства на входное воздействие рассмотрим самый неблагоприятный случай: изменение сигнала на входе i-ro периферийного микроконтроллера произошло в момент времени, когда цикл связи с ним контроллера 1 главного абонента уже начался, а этот входной сигнал оказался включенным в (i - 1)-ю подсистему уравнений контроллера 1 главного

абонента.

В этом случае информация о выходном сигнале поступит в (i - 1)-й периферийный микроконтроллер через 2 канальных цикла связи контроллера 1 главного абонента со

всеми периферийными микроконтроллерами.

Время обработки входного сигнала до передачи в магистраль 3 и время, затраченное на обработку выходного сигнала до выдачи его на объект управления, значительно меньше канального цикла, поэтому суммой этих времен можно пренебречь, Тмакс 2 Тс, где Тмакс - максимальное время реакции на входное воздействие, Тс - время проведения канального цикла обмена со всеми периферийными микроконтроллерами.

Тс К (Ti + Т2 - Тз),

где К- количество периферийных микроконтроллеров;

Ti - время передачи сообщения на периферийный микроконтроллер;

Т2 - время передачи ответа от периферийного микроконтроллера;

Тз - суммарное время программирования адаптера 24 магистрали на передачу и прием и время ожидания ответа.

Если принять скорость передачи информации магистрали 3f 500 кбод, среднее количество байт в кадре посылки и ответа -

N 10, цикл блока 23 управления при программировании адаптера 24 магистрали t -1 мкс, количество циклов программирования адаптера 24 магистрали , время ожидания ответа Т 10 мс, то:

N N 1 , .

Ti Т2 ;-- 1 60 мкс,

Ts tNi +Т 18 мкс. Если К 8, то Тс 2,72 мс, а Тмакс 5,54 мс.

Время реакции на входной сигнал, входящий в систему уравнений нижнего уровня, не превосходит времени Тс и составляет 1-3 мкс, что меньше, чем в известном устройстве. Формула изобретения Распределенная система управления, содержащая контроллер главного абонента и К периферийных микроконтроллеров (где К - количество объектов управления), при- чем контроллер главного абонента содержит центральный процессор, запоминающее устройство входов-выходов, запоминающее устройство команд, регистр адреса, дешифратор адреса, микроЭВМ, бу- ферное запоминающее устройство, адаптер магистрали, при этом информационно-адресные входы-выходы центрального процессора соединены поразрядно с информационными входами регистра адре- са, информационными выходами запоминающего устройства команд и информационно-адресными входами-выходами запоминающего устройства входов- выходов посредством первом шины адреса-данных, выход стробирующего сигнала адреса центрального процессора подключен к входу записи регистра адреса и входу выборки дешифратора адреса, первый и второй выходы которого соединены соответственно с входами выборки запоминающего устройства команд и запоминающего устройства входов-выходов, выход стробирующего сигнала чтения центрального процессора подключен к входу считыва- ния запоминающего устройства команд и входу управления чтением запоминающего устройства входов-выходов, вход записи которого соединен с выходом стробирующего сигнала записи центрального процессора, информационные входы дешифратора адреса соединены с выходами старших разрядов адреса регистра адреса, выход первого разряда адреса которого подключен к входу первого разряда адреса запоминающего ус- тройства команд, а выходы остальных младших разрядов адреса соединены с адресными входами запоминающего устройства команд, информационные входы- выходы и входы младших разрядов адреса буферного запоминающего устройства соединены с информационными входами-выходами адаптера магистрали через третью шину адреса-данных, каждый периферийный микроконтроллер содержит микроЭВМ, буферное запоминающее устройство, адаптер магистрали, регистр адреса, дешифратор, Р объектных адаптеров входов, М объектных адаптеров выходов, причем информационно-адресные входы-выходы микроЭВМ соединены поразрядно с информационными входами регистра адреса, информационными выходами каждого из Р объектных адаптеров входов и информационными входами каждого из М объектных адаптеров выходов через первую шину адреса-данных, выход стробирующего сигнала адреса микроЭВМ подключен к входу записи регистра адреса, выходы которого соеди- нены с информационными входами дешифратора, выход стробирующего сигнала чтения микроЭВМ подключен к входам чтения первого, второго... Р-го объектных адаптеров входов, входы выборки которых соединены соответственно с первым, вторым... Р-м выходами дешифратора, выход стробирующего сигнала записи микроЭВМ подключен к входам записи первого, второго... М-го объектных адаптеров выходов, входы выборки первого, второго... М-го объектных адаптеров выходов соединены

соответственно с (Р + 1)-м, (Р + 2)-м(Р +

М)-м выходами дешифратора, информационные входы-выходы и входы младших разрядов адреса буферного запоминающего устройства соединены с информационными входами-выходами адаптера магистрали через третью шину адреса-данных, входы объектных адаптеров входов и выходы объектных адаптеров выходов подключены соответственно к входам и выходам периферийного микроконтроллера, отличающаяся тем, что, с целью уменьшения времени реакции на входное воздействие за счет организации дополнительного уровня конвейерной обработки информации, в контроллер главного абонента введены запоминающее устройства обмена, двунаправленный шинный формирователь и блок управления, а в каждый периферийный микроконтроллер введены двунаправленный шинный формирователь и блок управления, при этом в контроллере главного абонента входы-выходы первого порта запоминающего устройства обмена соединены поразрядно с первой шиной адреса-данных, входы-выходы второго порта запоминающего устройства обмена соединены поразрядно с информационно-адресными входами-выходами микроЭВМ, первым многоразрядным входом-выходом двунаправленного шинного формирователя и входами-выходами блока управления через вторую шину адреса-данных, второй многоразрядный вход-выход двунаправленного шинного формирователя и многоразрядный выход блока управления соединены поразрядно с информационными входами- выходами буферного запоминающего устройства, первый управляющий вход первого порта запоминающего устройства обмена подключен к выходу стробирующего сигнала чтения центрального процессора, а первый управляющий вход второго порта соединен с выходом стробирующего сигнала чтения микроЭВМ, входом направления передачи двунаправленного шинного формирователя и вторым входом блока управления, первый вход которого подключен к выходу строби- рующего сигнала адреса микроЭВМ, второй управляющий вход первого порта запоминающего устройства обмена подключен к выходу стробирующего сигнала записи центрального процессора, а второй управ- ляющий вход второго порта соединен с выходом стробирующего сигнала записи микроЭВМ и третьим входом блока управления, третьи входы первого и второго портов запоминающего устройства обмена подклю- чены соответственно к третьему выходу дешифратора адреса и первому выходу блока управления, четвертый вход первого порта соединен с выходом первого разряда адреса регистра адреса, а четвертый вход второго порта подключен к выходу первого старшего разряда адреса микроЭВМ и четвертому входу блока управления, выходы первого и второго портов соединены соответственно с входом прерывания центрального процес- сора и первым входом прерывания микро- ЭВМ, второй вход прерывания которой подключен к второму выходу блока управления, выходы второго, третьего, четвертого и пятого старших разрядов адреса микроЭВМ соединены соответственно с пятым, шестым, седьмым и восьмым входами блока управления, девятый, десятый и одиннадцатый входы которого подключены соответственно к выходу требования прямо- го доступа передачи, выходу требования прямого доступа приема и выходу прерывания адаптера магистрали,третий, четвертый и пятый выходы блока управления соединены соответственно с входами выборки, запи- си и чтения буферного запоминающего устройства, выходы первого и второго старших разрядов адреса которого подключены соответственно к шестому и седьмому выходам блока управления, восьмой выход блока управления соединен с входом разрешения выхода двунаправленного шинного формирователя, а девятый и десятый выходы блока управления соединены соответственно с входами записи и чтения адаптера магистра- ли, вход признака Команда-данные которого подключен к седьмому выходу блока управления, последовательный вход-выход

адаптера магистрали подключен к входу-выходу контроллера главного абонента, в каждом периферийном микроконтроллере первый многоразрядный вход-выход двунаправленного шинного формирователя соединенпоразрядносинформационно-адресными входами-выходами микроЭВМ и входами-выходами блока управления через первую шину адреса-дан- ных, второй многоразрядный вход-выход двунаправленного шинного формирователя и многоразрядный выход блока управления соединены поразрядно с информационными входами-выходами буферного запоминающего устройства, выход стробирующего сигнала адреса микроЭВМ соединен с первым входом блока управления, второй вход которого соединен с входом направления передачи двунаправленного шинного формирователя и выходом стробирующего сигнала чтения микроЭВМ, а третий вход подключен к выходу стробирующего сигнала записи микроЭВМ, выходы с первого по пятый старших разрядов адреса микроЭВМ соединены соответственно с входами с четвертого по восьмой блока управления, а девятый, десятый и одиннадцатый входы блока управления подключены соответственно к выходу требования прямого доступа передачи, выходу требования прямого доступа приема и выходу требования прерывания адаптера магистрали, первый и второй выходы блока управления соединены соответственно с входом выборки дешифратора и входом прерывания микроЭВМ, третий, четвертый и пятый выходы блока управления соединены соответственно с входами выборки, записи и чтения буферного запоминающего устройства, входы первого и второго старших разрядов адреса которого подключены соответственно к шестому и седьмому выходам блока управления, восьмой выход блока управления соединен с входом разрешения выхода двунаправленного шинного формирователя, а девятый и десятый выходы блока управления соединены соответственно с входами записи и чтения адаптера магистрали, вход признака Команда-данные которого подключен к седьмому выходу блока управления, последовательный вход-выход адаптера магистрали является входом-выходом периферийного микроконтроллера, входы- выходы всех периферийных микроконтроллеров соединены между собой и входом-выходом контроллера главного абонента через последовательную магистраль.

31

1732345

32 Таблица 1

Таблица 2

Таблица 3

а

ер

ера

фер

тера

Состояния младших рээрядоа шины 64 адреса данных беэрлз- личны

Загрузка номера Есть массива и номера начальной ячейки

Загрузка режима

Номер ячейки информация Есть

Признак комлн- Есть ды - данные информация

Адрес последней ячейки приема

Три младии разряда - вектор прерывания

Номер ячейки ин- Есть формация

Призкзк команды - данчые информация

Есть

Название

Кадры инициализации связи:

Установить режим нормальных ответов

Разъединить соединени

Ненумерованное под- твсрждение

Отказ от кадра Сучервизорные кадры Готовность к приему

Неготовность к приему

Информационней кадр

Есть

Есть

Есть

Есть Есть

Есть

Есть

1

О О О О

Таблица 5

Мнемоническое Структуры кадра оиозначение | типа кадра I

1-й байт - флаг

2-й бдит - адрес периферийного

микроконтроллера

3-й байт - тип кадра

байты - контролирующий

OIKHOM

6-и байт - Флаг 1-и ба IT - Слог

-й гпит - адрес периферийного гикроконтроллсрл

3-й байт - тип кадра

байты - контролируюц.н полином

6-П байт - флаг J-й байт - флаг

2-й байт - адрес периферийного микроконтроллера

3-й байт - тип кадра

-й байт - тип команды логимегк уоовня

с по (п-З)-й байт - информация

с (п-2)-го по (п-1)-й байт - ко ролируощий полином

n-й байт - флаг

о

-

; i i

1 x-.|

1

-n-

f

r°

K

d

оН

, ,

bi

TJ

St C2Cil

in

4CO CM CO

rI

H-ii

r-4

JUd

с

S9

#

зи:гш

&

JX.

-iX

ел а/ /U

J

Фиг.6

впнзЪпдооэ OJO 4U/}curo ),-V DЈCtrr,C3Ј i &f

ШЛЯП/ШЛЯ ЯПЯПЯПШ1 ТШШЛЯПЯПЯо

jwi//5 j Эгоч о ,«

&™9Ц

( Off L

ffv-awtv/ f/.7ff|

ллчэндосЪ

1Чл-ЭЪ/37Э ЗГ НЗ/ПЭ(У

age

ФН/7

)

fic/3,M,Du; oa э- н/уы„ щ

ыжш

ел

го

у

о

| Устройство для управления распределенными объектами | 1985 |

|

SU1290261A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Патент США №4413319, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-05-07—Публикация

1989-10-16—Подача