Изобретение относится к цифровой измерительной и управляющей технике и может быть использовано в многомашинных (многопроцессорных) системах управления, когда наряду с выполнением задач управления, таких как формирование сигналов управления технологическим оборудованием, сбор, преобразование и анализ технологических параметров, прием-передача данных и других, микроЭВМ (микропроцессоры) обмениваются данными с помощью общего оперативного запоминающего устройства (общего ОЗУ) с использованием общей шины (ОШ), в связи с чем в процессе обмена данными возникает необходимость упорядочения доступа при одновременном обращении к общему ОЗУ двух и более микроЭВМ.

Известна многомашинная система, состоящая из нескольких процессоров, регистров связи с общей шиной и общей памятью данных (авторское свидетельство СССР №833082). Недостатком системы является сложность устройства и недостаточная надежность при работе в промышленных условиях.

Известно многоканальное устройство для подключения источников информации к общей магистрали (авторское свидетельство №1735862), состоящее из общей шины, шины арбитража, шины сопровождения передачи и устройства для запроса, состоящего из нескольких регистров, счетчиков и других элементов. Недостатком устройства является сложность организации взаимодействия с общей шиной и большое количество осуществляющих подключение элементов.

Известен способ управления общей шиной совместно используемой памяти в мультипроцессорной системе с целью предотвращения конфликта на общей шине (патент США №5202973), заключающийся в поочередном захвате шины на определенный период времени по предварительной скрытой проверке шины. Недостаток способа заключается в сложности способа организации управления общей шиной.

Известна мультипроцессорная система с усовершенствованным соединением для локальных процессорных систем, работающих независимо (патент США №5423007). Недостаток системы состоит в двухступенчатом способе доступа и арбитража к глобальной памяти.

Известна система центральных процессоров, состоящая из множества центральных процессоров, общей памяти, адресной шины, в которой доступ к общей шине осуществляется с помощью одного процессора (заявка США №2002/0046297 А1).

Недостаток системы состоит в том, что организация доступа к общей шине возложена на один из процессоров, который не может быть выключен из системы.

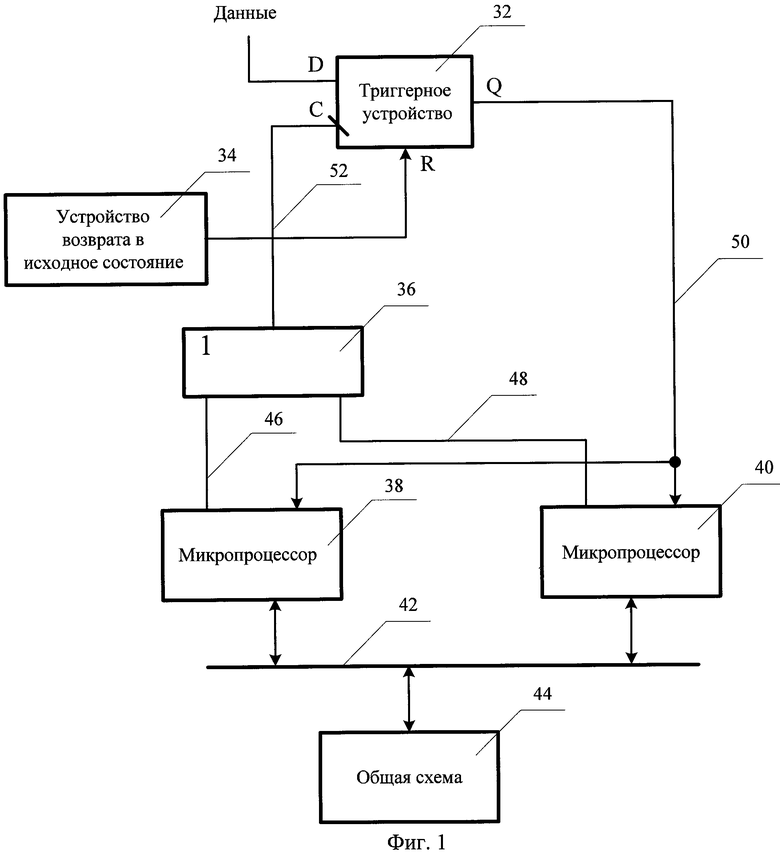

Наиболее близкой к предлагаемому изобретению по своей технической сущности является мультипроцессорная система с предварительной обработкой состояния общей схемы (патент США №5355500). Блок-схема системы представлена на фиг.1 (прототип). Система состоит из множества микропроцессоров 38-40, которые связаны общей шиной 42 с общей схемой 44, триггерного устройства 32 для формирования запускающего сигнала и сигнала разрешения/запрещения начальной обработки состояния микропроцессоров в ответ на сигналы считывания 46-48, выдаваемые любым микропроцессором из множества микропроцессоров 38-40, устройства 34 для возврата в исходное состояние триггерного устройства 32 после включения электропитания мультипроцессорной системы и схемы ИЛИ 36 для формирования сигнала считывания для триггерного устройства, в котором каждый из упомянутых микропроцессоров 38-40 может контролировать упомянутый сигнал разрешения начальной обработки 50 и формировать сигнал считывания 46-48 почти одновременно с контролем, посредством чего один микропроцессор из упомянутого множества микропроцессоров 38-40 выполняет операцию начальной обработки в упомянутой общей схеме 44, когда остальные упомянутые микропроцессоры контролируют сигнал разрешения обработки 50 в режиме запрета.

Упомянутое триггерное устройство 32 мультипроцессорной системы выполняет логическое суммирование сигналов считывания, сформированных множеством микропроцессоров.

Схема 32 для формирования сигнала разрешения начальной обработки 50 мультипроцессорной системы представляет собой схему D-триггера, причем сигнал от внешних устройств о передаче данных поступает на вход D-триггера, сигнал возврата в исходное состояние с выхода устройства поступает на вход R установки в первоначальное состояние триггера, запускающий сигнал поступает на синхронизирующий вход С триггерного устройства, сигнал разрешения начальной обработки формируется на выходе триггера.

Устройство 34 возврата в первоначальное состояние мультипроцессорной системы приводится в действие при первом включении мультипроцессорной системы.

Мультипроцессорная система (фиг.1) работает следующим образом.

После включения электропитания устройство 34 возврата в исходное состояние формирует сигнал возврата в исходное состояние, который поступает на вход R установки триггера. На выходе триггерного устройства 32 формируется сигнал разрешения начальной обработки 50, который поступает на множество микропроцессоров 38-40.

Один из микропроцессоров, контролирующий сигнал разрешения начальной обработки 50, может выставить на входе D триггерного устройства 32 сигнал данных (лог.1) и сформировать сигнал считывания 46-48, который поступает на логическую схему ИЛИ 36 и с выхода логической схемы ИЛИ 36 на вход синхронизации 52 триггерного устройства.

Триггерное устройство 32 по сигналу считывания переводит сигнал разрешения начальной обработки 50 в режим запрета, по которому все другие микропроцессоры из множества микропроцессоров 38-40 могут контролировать сигнал разрешения 50 в режиме запрета.

Микропроцессор, сформировавший сигнал считывания, через общую линию (шину) управления 42 соединяется с общей схемой 44. По окончании сеанса связи упомянутый микропроцессор устанавливает на входе D триггерного устройства сигнал данных (лог.0) и формирует сигнал считывания 46-48, по которому сигнал разрешения начальной обработки 50 переводится в режим разрешения. После чего другой микропроцессор из множества микропроцессоров при необходимости повторяет описанную процедуру доступа к общей схеме 44 через общую линию управления 42.

К недостаткам мультипроцессорной системы по патенту США №5355500 следует отнести возможность формирования сигнала считывания несколькими микропроцессорами одновременно и ненадежное функционирование многопроцессорной системы в условиях разнесенного конструктивного исполнения отдельных процессоров.

Использование триггерного устройства в составе арбитра в условиях применения многопроцессорной системы в промышленных установках снижает надежность формирования сигнала начальной обработки и исключает устойчивое состояние триггерного устройства из-за помех как по линиям связи между отдельными микропроцессорами, так и по шинам питающего микропроцессоры напряжения.

Задачей настоящего изобретения является повышение надежности обмена данными между микроЭВМ при использовании общего ОЗУ в качестве устройства обмена данными в многомашинной системе управления. При этом решается техническая задача создания устройства разрешения конфликтных ситуаций при столкновениях (коллизиях) двух и более сигналов на общей шине при одновременном обращении к общему ОЗУ двух и более микроЭВМ.

Сущность предлагаемого изобретения заключается в том, что в многомашинной системе управления, состоящей из N управляющих микроЭВМ, каждая из которых через локальные шины связана с внешними устройствами ввода-вывода, каждая из которых общей шиной связана с общим ОЗУ, общего ОЗУ, выполняющего функцию обмена данными между микроЭВМ, в систему дополнительно введен арбитр общей шины, выполненный из N логических элементов (N-1)И-HE, поставленных в соответствие каждой микроЭВМ, входы которых соединены с линиями запроса доступа всех микроЭВМ кроме соответствующей, выходы которых соединены с входами проверки сигналов разрешения/запрещения всех микроЭВМ, причем дополнительно в программное обеспечение каждой микроЭВМ введена программа анализа состояния выходных сигналов арбитра и запроса доступа к арбитру, включающая команды отключения запроса, временной задержки, проверки состояния общей шины, включения запроса доступа, повторной проверки состояния общей шины, записи/чтения данных и отключения запроса доступа.

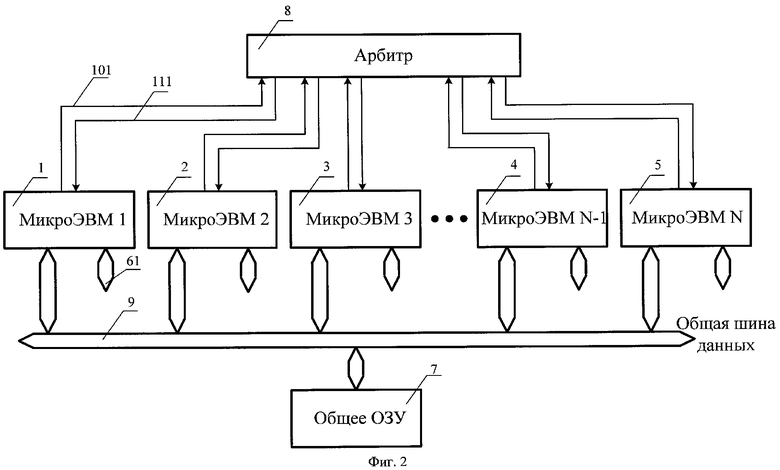

Блок-схема многомашинной системы управления изображена на фиг.2.

Система состоит из микроЭВМ 1...5, локальной шины первой микроЭВМ 61, общего ОЗУ 7, арбитра 8, общей шины данных 9, линии запроса доступа первой микроЭВМ 101 и линии разрешения/запрещения первой микроЭВМ 111.

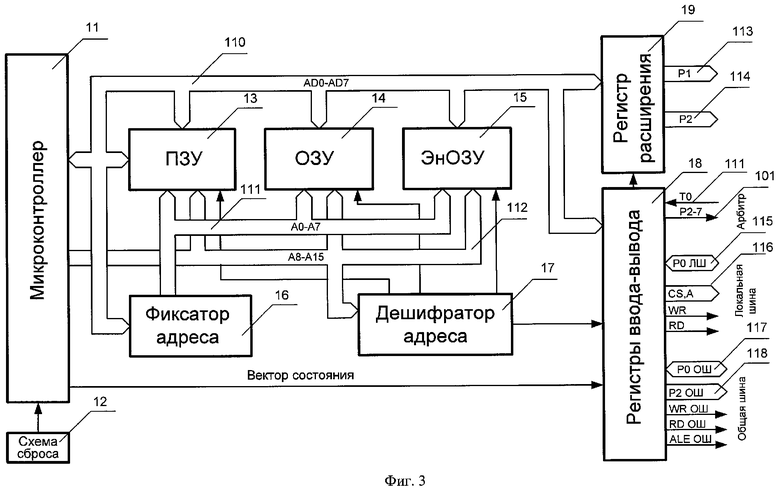

На фиг.3 изображена структурная схема первой микроЭВМ, входящей в состав многомашинной системы. МикроЭВМ состоит из микроконтроллера 11, схемы сброса 12, постоянного запоминающего устройства (ПЗУ) 13, оперативного запоминающего устройства (ОЗУ) 14, 15, фиксатора адреса 16, дешифратора адреса 17, регистров ввода-вывода 18, регистра расширения 19, внутренней шины адрес-данные 110, шины младших адресов 111, шины старших адресов 112, шины порта Р1 113, шины порта Р2 114, локальной шины порта Р0 115, локальной шины адреса 116, общей шины порта Р0 117, общей шины адреса 118, линии запроса доступа 101, линии разрешения/запрещения 111.

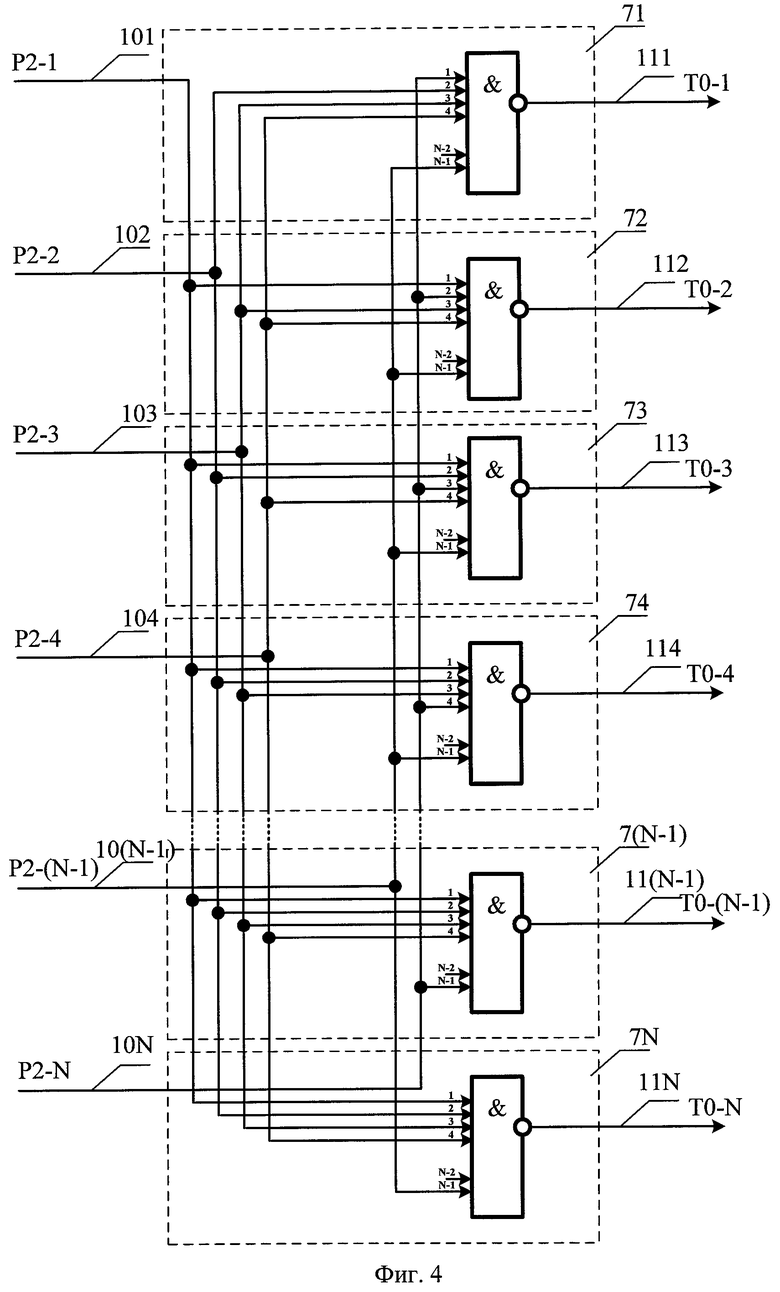

На фиг.4 показана схема арбитра общей шины многомашинной системы управления с N микроЭВМ. Арбитр состоит из логических элементов (N-1)И-НЕ 71...7N, линий запроса доступа 101...10N, линий разрешения/запрещения 111...11N.

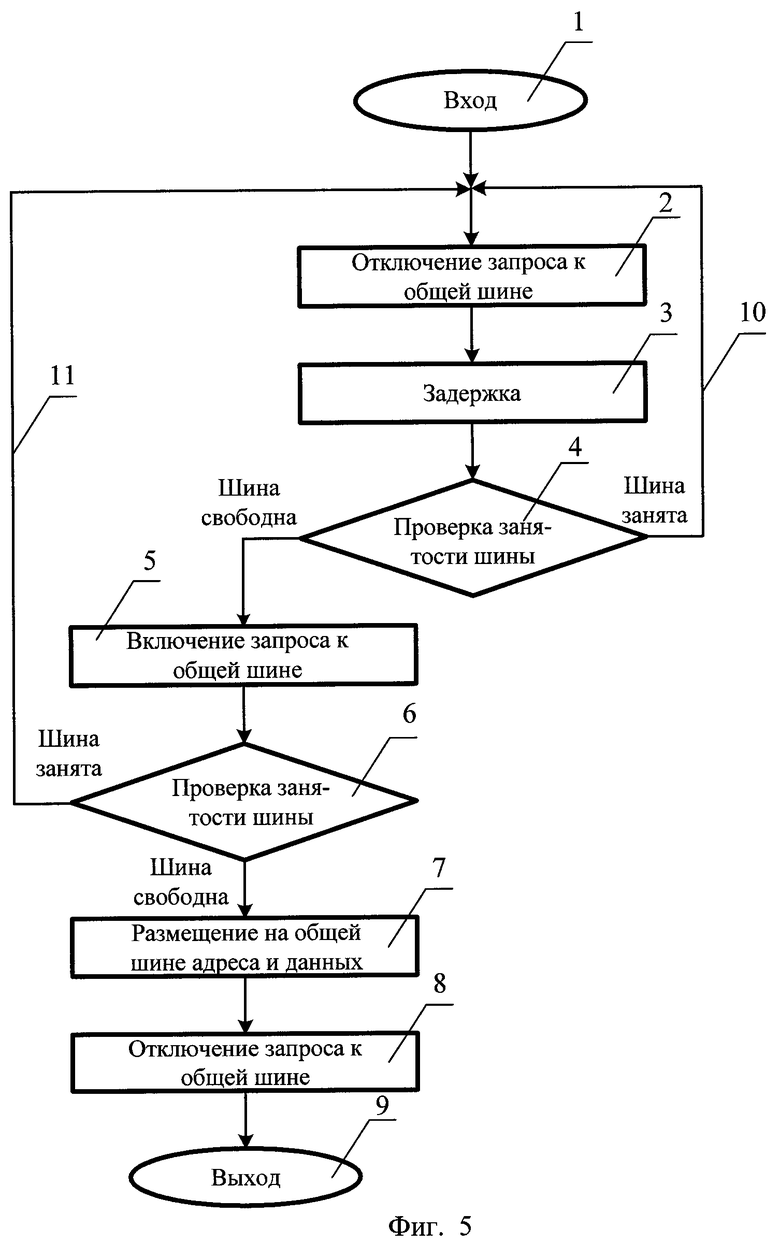

На фиг.5 показана блок-схема алгоритма запроса доступа микроЭВМ к общему ОЗУ многомашинной системы. Блок-схема включает блок входа 1 и блок выхода 9 из программы, блоки отключения запроса 2, 8, блок задержки 3, блоки проверки занятости шины 4, 6, блок включения запроса 5, блок размещения на шине адреса и данных 7 и переходы на начало цикла в случае занятой шины 10, 11.

В качестве микроконтроллера в микроЭВМ используются однокристальные микрокомпьютеры типа КР1816ВЕ31 (Р80с31ВН) и Р8044АН (Р8344АН).

Многомашинная система управления работает следующим образом. После одновременного или раздельного включения электропитания все включенные микроЭВМ 1...5, показанные на фиг.2, выполняют команду отключения запроса к общей шине и переходят к выполнению задач, алгоритмы которых записаны в ПЗУ 13 (фиг.3) каждой микроЭВМ. При этом, как следует из фиг.3, связь со своими внешними устройствами каждая микроЭВМ выполняет через регистры ввода-вывода 18 локальной шины 115, 116. К числу задач, решаемых микроЭВМ, относятся формирование циклов преобразования аналоговых сигналов в кодированную форму, анализ цифровых и позиционных сигналов состояния оборудования, формирование и передача команд управления оборудованием, обмен данными с диспетчерским пунктом, выполнение инструкций по управлению технологического оборудования и установок и др.

В конце цикла решаемых задач микроЭВМ выполняют программу обращения к общему ОЗУ с целью чтения и/или записи данных в общее ОЗУ. Связь с общим ОЗУ выполняется через регистры ввода-вывода 18 общей шины 117, 118.

В связи с тем, что к общему ОЗУ могут обращаться две и более микроЭВМ одновременно, в многомашинную систему введен программно-аппаратный арбитр, повышающий надежность обмена данными между микроЭВМ в многомашинной системе за счет разрешения конфликтных ситуаций при столкновениях двух и более сигналов на общей шине при одновременном обращении к общему ОЗУ двух и более микроЭВМ.

Арбитр доступа к общей шине и общему ОЗУ (фиг.4) состоит из N (по числу микроЭВМ) логических элементов (N-1)И-HE, первые входы 2, 3,...N элементов объединены и соединены с выходом запроса доступа первой микроЭВМ, вторые входы 1, 3,...N элементов объединены и соединены с выходом запроса доступа второй микроЭВМ, третьи входы 1, 2, 4,...N элементов объединены и соединены с выходом запроса доступа третьей микроЭВМ и т.д., N-1 входы 1, 2,...N-2, N элементов объединены и соединены с выходом запроса N-1 микроЭВМ, первый вход первого элемента, второй вход второго элемента, третий вход третьего элемента и т.д., N-2 вход N элемента объединены и соединены с выходом запроса доступа N микроЭВМ, выход разрешение/запрещение первого элемента соединен с входом проверки первой микроЭВМ, выход разрешение/запрещение второго элемента соединен с входом проверки второй микроЭВМ и т.д., выход разрешение/запрещение N элемента соединен с входом проверки N микроЭВМ.

Схема арбитра общей шины обеспечивает формирование разрешения ("лог.0") на всех выходах 111...11N при отсутствии запросов доступа ("лог.1") на всех входах 101...10N. При формировании запроса доступа ("лог.0") только на одном из входов 101...10N формируется разрешение на одном соответствующем выходе 111...11N. При формировании запроса ("лог.0") на двух и более входах 101...10N на всех выходах 111...11N формируются запрещения ("лог.1").

Блок-схема алгоритма программы доступа к общему ОЗУ для чтения и/или записи данных (фиг.5) начинается с выполнения команды отключения запроса к общей шине 2 (входы 101-10N арбитра), выполнения последующей переменной временной задержки 3 для организации очереди и проверки занятости общей шины 4 (выходы 111-11N арбитра).

Для выполнения программы доступа к общему ОЗУ каждая из микроЭВМ выходом 101 и входом 111 (фиг.3) соединена соответственно с входом и выходом арбитра. В случае занятой шины выполняется переход 10 на начало цикла, а в случае свободной шины включается запрос 5 путем установки входа арбитра 101...10N в состояние "лог.0". После чего повторно проверяется занятость общей шины 6.

В случае занятой шины выполняется переход 11 на начало цикла.

Переходы 10 и 11 двух и более микроЭВМ в случае занятой общей шины сопровождаются повторным выполнением программы доступа к общему ОЗУ. Временная задержка 3 в программе доступа к общему ОЗУ задается для каждой из микроЭВМ различной и достаточной для установки запроса на входе арбитра, в результате чего микроЭВМ при обращении к общему ОЗУ выстраиваются в очередь. Первой получает доступ к общему ОЗУ та из микроЭВМ, в которой временная задержка минимальная, затем получает доступ микроЭВМ с большей задержкой и т.д.

В случае свободной шины микроЭВМ размещает на общей шине адрес и данные записи и/или чтения из общего ОЗУ 7.

По окончании обмена данными микроЭВМ выполняет отключение запроса к общей шине 8 путем установки на входе арбитра 101...10N "лог.1" и выполняет выход из программы.

В связи с тем, что обмен данными микроЭВМ с общим ОЗУ выполняется в параллельном коде с тактовой частотой 12 МГц (в случае использования в качестве микроЭВМ микрокомпьютеров типа КР1816ВЕ31) запись или чтение данных из общего ОЗУ объемом 256 байт занимает время около 21 мс, что составляет меньшую часть цикла выполнения задач микроЭВМ многомашинной системы.

Практически было изготовлено и включено в постоянную эксплуатацию свыше 800 многомашинных систем управления. В каждой многомашинной системе управления использовалось пять микроЭВМ на основе микрокомпьютеров типа КР1816ВЕ31. Отказов по причине неразрешимых конфликтных ситуаций при столкновениях двух и более сигналов на общей шине при обращении к общему ОЗУ за время эксплуатации многомашинных систем в течение 45000 часов непрерывной работы зафиксировано не было.

Данное обстоятельство позволяет утверждать, что использование в многомашинной системе управления программно-аппаратного арбитра по предлагаемой схеме исключает возникновение неразрешимых конфликтных ситуаций при столкновениях двух и более сигналов на общей шине при обмене данными с общим ОЗУ и обеспечивает повышение надежности обмена данными между микроЭВМ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство доступа к общей памяти | 1987 |

|

SU1543410A1 |

| Резервированная система | 1990 |

|

SU1785087A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Многопроцессорная система | 1990 |

|

SU1709330A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

| Многопроцессорная система | 1988 |

|

SU1522228A1 |

| Многомашинная вычислительная система | 1990 |

|

SU1798798A1 |

| Многоканальное устройство для сопряжения вычислительных машин | 1986 |

|

SU1322302A1 |

| Многопроцессорная вычислительная система | 1985 |

|

SU1277129A1 |

Изобретение относится к цифровой измерительной и управляющей технике, в частности к многомашинным системам управления. Технический результат изобретения заключается в повышении надежности обмена данными между микроЭВМ при использовании общего ОЗУ в качестве устройства обмена данными. Технический результат достигается за счет того, что многомашинная система, состоящая из n управляющих микроЭВМ, содержит общее ОЗУ, программно-аппаратный арбитр общей шины, выполненный из N логических элементов (N-1)И-HE, а программное обеспечение микроЭВМ дополнено программой анализа и запроса доступа к арбитру, включающей команду временной задержки для постановки микроЭВМ в очередь после обнаружения столкновения. 5 ил.

Многомашинная система управления, содержащая N управляющих микроЭВМ, каждая из которых связана локальной шиной с внешними устройствами ввода-вывода для выполнения комплекса задач под управлением программного обеспечения, записанного в ПЗУ каждой управляющей микроЭВМ, общее оперативное запоминающее устройство (общее ОЗУ), которое используется в качестве устройства обмена данными между управляющими микроЭВМ, связанное общей шиной с каждой из N управляющих микроЭВМ, отличающаяся тем, что в систему введен программно-аппаратный арбитр общей шины, составленный из N логических элементов (N-1)И-HE, поставленных в соответствие каждой микроЭВМ, причем выход запроса доступа к общей шине каждой из N-1 микроЭВМ соединен с одноименными входами всех, кроме одноименного, логических элементов (N-1)И-HE, выход запроса доступа к общей шине N-й микроЭВМ соединен со свободными входами всех, кроме одноименного, логических элементов (N-1)И-HE, выход разрешение/запрещение каждого из N логических элементов (N-1)И-HE соединены с входом проверки одноименной микроЭВМ, а программное обеспечение каждой микроЭВМ дополнено программой анализа выходного сигнала одноименного логического элемента (N-1)И-HE и формирования сигнала запроса доступа к общей шине при обращении к общему ОЗУ для всех, кроме одноименного, логических элементов (N-1)И-HE, которая включает в себя команду отключения запроса к общей шине, команду временной задержки, которая предусматривает изменяемую величину задержки, обеспечивающую постановку микроЭВМ в очередь при их одновременном обращении к общему ОЗУ, команду проверки выходного сигнала логического элемента (N-1)И-HE, команду включения запроса доступа к общей шине, команду повторной проверки состояния выходного сигнала одноименного логического элемента(N-1)И-НЕ, команду записи/чтения данных из общего ОЗУ и команду отключения запроса доступа.

| US 5307466 А, 26.04.1994 | |||

| УСТРОЙСТВО ОБРАБОТКИ ИНФОРМАЦИИ | 1993 |

|

RU2080652C1 |

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| Устройство для сопряжения процессоров через общую память в многопроцессорной системе | 1984 |

|

SU1231508A1 |

| JP 60020271 A, 01.02.1985. | |||

Авторы

Даты

2008-03-20—Публикация

2006-03-06—Подача