Изобретение относится к технике связи и может использоваться в аппаратуре асинхронного ввода-вывода синхронной двоичной информации в цифровые каналы систем с импульсно-кодовой модуляцией и дельта-модуляцией.

Цель - расширение диапазона изменения тактовой частоты входного сигнала при сохранении точности восстановления его фазы.

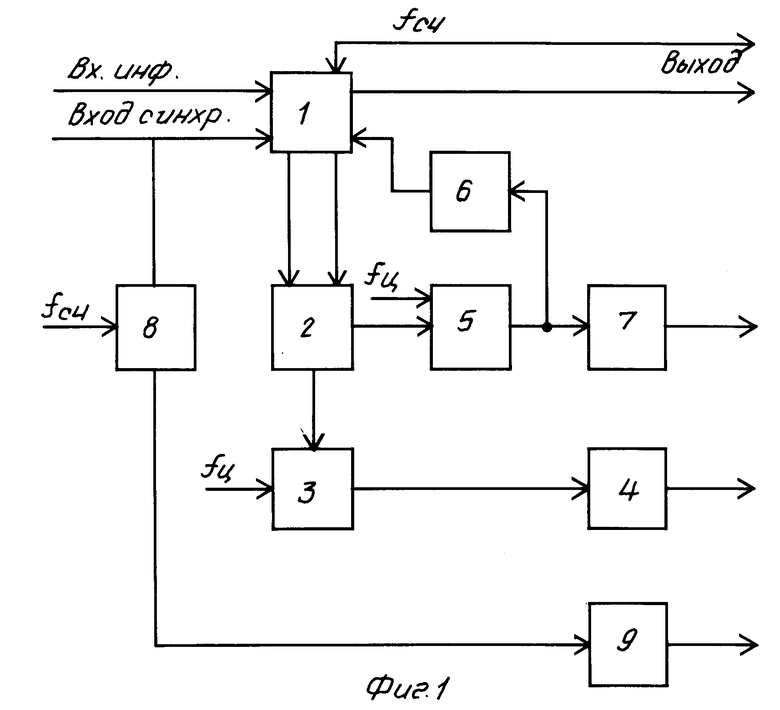

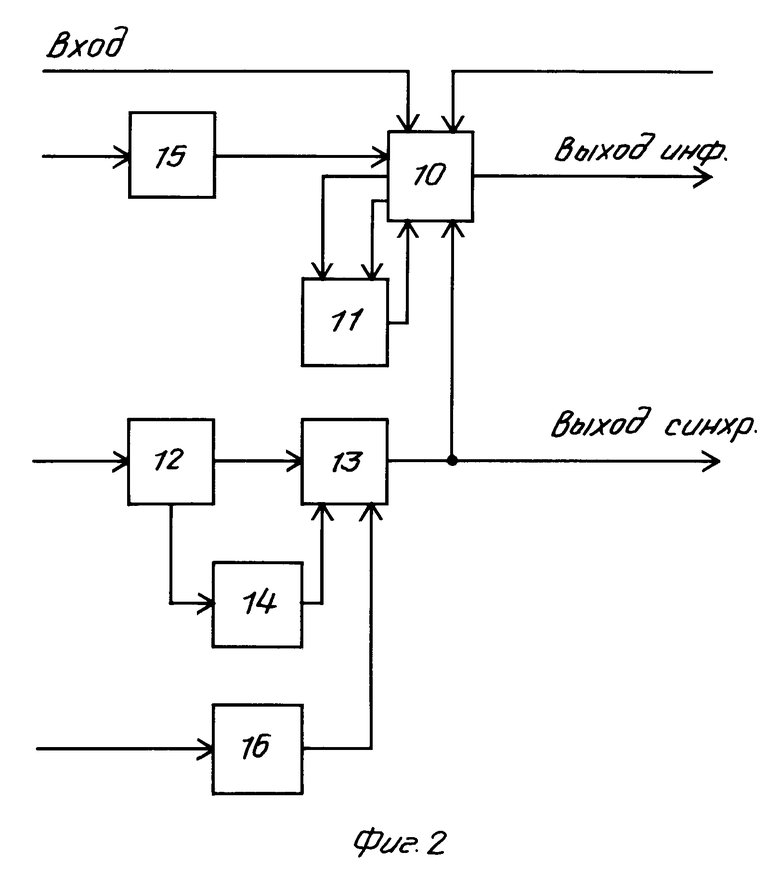

На фиг. 1 и 2 представлены схемы передающей и приемной сторон устройства асинхронного преобразования импульсных последовательностей.

Устройство асинхронного преобразования импульсных последовательностей содержит на передающей стороне блок 1 памяти, фазовый детектор 2, измеритель 3 фазы импульсов записи, первый блок 4 кодирования, счетчик 5 импульсов, блок 6 управления, второй блок 7 кодирования, измеритель 8 периода импульсов записи и третий блок 9 кодирования.

На приемной стороне устройство содержит блок 10 памяти, блок 11 грубой установки фазы, первый блок 12 декодирования, формирователь 13 импульсов считывания, блок 14 стирания, второй блок 15 декодирования и третий блок 16 декодирования.

Устройство асинхронного преобразования импульсных последовательностей работает следующим образом.

На передающей стороне синхронно с тактовыми импульсами производится запись информации в блок 1. Фазовый детектор 2 ведет слежение за фазовым рассогласованием между моментами записи и считывания, и при изменении его на величину, равную одному периоду импульсов считывания, вырабатывает команду о наличии неоднородности. Счетчик 5 производит подсчет количества неоднородностей, возникших в течение цикла передачи, и с помощью блока 6 корректирует процесс считывания информации из блока 1. Одновременно с этим полученные значения количества неоднородностей кодируются во втором блоке 7 для того, чтобы на приемной стороне с помощью второго блока 15 была осуществлена соответствующая коррекция записи синхронного сигнала в блок 10. На передающей стороне в измерителе 8 производится измерение периода следования фронтов входных тактирующих импульсов. Измерение производится с точностью до части тактового интервала синхронных считывающих импульсов (шага измерения), полученное значение кодируется в третьем блоке 9.

На приемной стороне третий блок 16 и формирователь 13 восстанавливают значение периода, которое с точностью до шага измерения на передающей стороне совпадает с периодом следования импульсов записи. Одновременно с этим на передающей стороне с помощью измерителя 3 один раз за цикл производится измерение фазы импульсов записи. Измеренные значения кодируются во втором блоке 4 кодом, позволяющим на приемной стороне обнаруживать ошибки. Значения фаз декодируются блоком 12 и с помощью блока 14 устанавливают фазу считывающих импульсов в формирователе 13. Блок 11 обеспечивает начальное фазирование импульсов записи и считывания в блоке 10 после включения устройства и после срывов синхронизма на приемной стороне.

Использование: в технике связи, а именно в аппаратуре асинхронного ввода-вывода синхронной двоичной информации в цифровые каналы систем с импульсно-кодовой модуляцией и дельта-модуляцией. Сущность изобретения: устройство содержит на передающей стороне блок памяти, фазовый детектор, измеритель фазы импульсов записи, три блока кодирования, счетчик импульсов, блок управления, измеритель периода импульсов записи. На приемной стороне - блок памяти, блок грубой установки фазы, три блока декодирования, формирователь импульсов считывания, блок стирания. Устройство позволяет на приемной стороне восстановить синхросигнал тактовой частоты с заданной точностью. Подсчет количества неоднородностей в цикле передачи счетчиком обеспечивает на передающей стороне ввод, а на приемной стороне восстановление входной информации из группового тракта. 2 ил.

УСТРОЙСТВО АСИНХРОННОГО ПРЕОБРАЗОВАНИЯ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ, содержащее на передающей стороне последовательно соединенные блок памяти, фазовый детектор, последовательно соединенные измеритель фазы импульсов записи и первый блок кодирования, выход которого является первым сигнальным выходом устройства, счетчик импульсов и блок управления, выход которого подключен к управляющему входу блока памяти, информационный, тактовый и счетный входы которого являются соответственно одноименными входами устройства, управляющий выход блока памяти является одноименным выходом устройства, на приемной стороне последовательно соединенные первый блок декодирования, блок стирания, формирователь импульсов считывания, блок памяти и блок грубой установки фазы, выход которого подключен к импульсному входу блока памяти, информационный и тактовый входы и первый информационный выход блока памяти являются соответственно одноименными входами и выходом устройства, второй информационный выход блока памяти подключен к одноименному входу блока грубой установки фазы, вход первого блока декодирования является первым сигнальным входом устройства, второй выход первого блока декодирования через формирователь импульсов считывания подключен к выходу синхронизации устройства, отличающееся тем, что на передающей стороне введены второй блок кодирования и последовательно соединенные измеритель периода импульсов записи и третий блок кодирования, выход которого является вторым сигнальным выходом устройства, первый вход измерителя периода импульсов записи подключен к тактовому входу устройства, второй вход измерителя периода импульсов записи является счетным входом, выход второго блока кодирования является третьим сигнальным выходом устройства, первый выход фазового детектора соединен с первым входом измерителя фазы импульсов записи, второй выход фазового детектора соединен через счетчик импульсов с входом блока управления и входом второго блока кодирования, при этом на вход обнуления счетчика импульсов записи и второй вход измерителя фазы импульсов подаются импульсы цикловой частоты, на приемной стороне введены второй и третий блоки декодирования, выход которого соединен с третьим входом формирователя импульсов считывания, а выход второго блока декодирования соединен с первым входом блока памяти, при этом вход второго блока декодирования является третьим сигнальным входом устройства, а вход третьего блока декодирования - вторым сигнальным входом устройства.

| Устройство для асинхронного сопряжения каналов | 1977 |

|

SU690638A1 |

Авторы

Даты

1994-11-30—Публикация

1991-07-01—Подача