Эта заявка заявляет приоритет на заявку, озаглавленную “Устройство и способ для выполнения кодирования и согласования скорости в системе мобильной связи МДКР”, зарегистрированную в офисе корейской промышленной собственности 30 октября 2001 г., и которой присвоен серийный № 2001-64967, содержание которой включено в настоящее описание в качестве ссылки.

Настоящее изобретение относится вообще к устройству и способу передачи/приема данных в системе мобильной связи МДКР (множественного доступа с кодовым разделением) и, в частности, к устройству и способу передачи/приема данных, использующих объединенное канальное кодирование и согласование скорости.

В системе мобильной связи фактически невозможно принимать сигнал, передаваемый из передатчика через проводную сеть, без искажений и шумов. Поэтому предложены различные способы для минимизации искажения и шума и способ кодирования с контролем ошибок является типичным способом. В самых последних системах мобильной связи МДКР турбо-коды и сверточные коды используются в способах кодирования с контролем ошибок. Устройство для осуществления кодирования с контролем ошибок обычно называется “канальным кодером”.

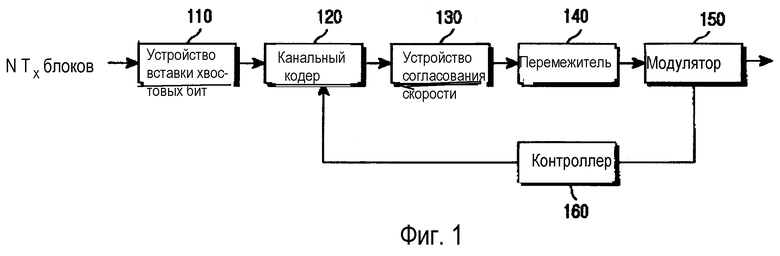

Фиг.1 иллюстрирует структуру обычного передатчика в системе мобильной связи МДКР. Ссылаясь на фиг.1, N блоков передачи данных (N Тх), передаваемых из верхнего уровня, подаются в качестве входных данных устройства 110 вставки хвостовых бит. Устройство 110 вставки хвостовых бит вставляет хвостовые биты в каждый из N блоков передачи данных. Устройство 110 вставки хвостовых бит, когда оно использует сверточные коды, расположено перед канальным кодером 120. Однако устройство 110 вставки хвостовых бит, когда оно использует турбокоды, может быть включено в канальный кодер 120. То есть для вставки хвостовых бит, память в канальном кодере 120 инициализируется в момент времени, когда кодирование блока входных данных закончено. Канальный кодер 120 включает в себя, по меньшей мере, одну кодовую скорость для того, чтобы кодировать N блоков передачи. Типичная кодовая скорость (k/n) равна 1/2 или 3/4. В кодовой скорости k (k=1,3,...) указывает число бит блока входных данных, поданного в канальный кодер 120, а n (n=2,4,...) указывает число бит, выведенных из канального кодера 120. Следовательно, при кодовой скорости 1/2 канальный кодер 120 принимает, например, 100 бит и выводит 200 бит, а при канальной скорости 3/4 канальный кодер 120 принимает, например, 300 бит и выводит 400 бит. То есть кодовая скорость представляет отношение числа бит блока входных данных к числу закодированных выходных бит. Кроме того, канальный кодер 120 поддерживает множество кодовых скоростей посредством прокалывания или повторения, обычно основанного на базовой кодовой скорости 1/3 или 1/5. В случае базовой кодовой скорости 1/3 для того, чтобы поддерживать кодовую скорость 1/2, канальный кодер генерирует 300 бит для 100 входных бит при базовой кодовой скорости 1/3, а затем прокалывает 100 бит из 300 бит. Канальный кодер 120, если он использует турбокоды, генерирует систематические биты в качестве выходных данных и биты контроля четности, имеющие способность коррекции ошибок для систематических бит. На фиг.1 канальный кодер 120 определяет кодовую скорость для использования под управлением контроллера 160. Недавно ПК3П (проект компании 3-го поколения) и ПК3П-2, который определил стандарт мобильной связи 3-го поколения, исследовал стандарты ВДПД (высокоскоростной доступ к пакетам данных) и 1×EV-DV для обслуживания высокоскоростных данных радиопакетов через совместно используемый канал. Способ адаптивного кодирования и модуляции является одним из базовых способов, определенных для этих стандартов. Этот способ адаптивно изменяет кодовую скорость и порядок модуляции в соответствии с состоянием линии радиосвязи. В способе контроллер определяет подходящую кодовую скорость в соответствии с состоянием канала так, что кодер канала может выполнять кодирование с требуемой кодовой скоростью. Такой способ адаптации линии связи может быть разделен на способ управления мощностью и способ САМК (схема адаптивной модуляции и кодирования). Способ управления мощностью обычно используется в существующей системе мобильной связи, но САМК используется только в системе мобильной связи ВДПД.

В стандарте УМТС (универсальной мобильной телекоммуникационной системы) (версия ’99), принятом ПК3П, закодированные биты, выведенные из канального кодера 120 подаются в устройство 130 согласования скорости. Устройство 130 согласования скорости выполняет согласование скорости относительно закодированных бит. Обычно число закодированных бит, выведенных из канального кодера 120, не равно общему числу бит блока передачи данных (БПД) в эфире. Согласование скорости является операцией согласования числа закодированных бит с общим числом бит, требуемых в эфире, посредством повторения и прокалывания относительно закодированных бит. Согласование скорости раскрыто подробно в стандарте, принятом ПК3П, таким образом, дополнительное описание не будет предоставлено. Предполагается, что согласование скорости будет использоваться даже в стандарте ВДВД.

Закодированные биты, число которых контролируется устройством 130 согласования скорости, подаются в перемежитель 140. Перемежитель 140 выполняет перемежение относительно закодированных бит. Перемежение выполняется для того, чтобы разделить соседние закодированные биты как можно дальше друг от друга, таким образом, максимизируя способность коррекции ошибок, даже, если происходит потеря в конкретных данных во время передачи данных через радиоканал. Например, как изложено выше, так как канальный кодер 120 генерирует систематические биты и биты контроля четности, соседние закодированные биты включают в себя систематические биты и связанные биты контроля четности. Следовательно, когда систематические биты и биты контроля четности одновременно теряются, способность коррекции ошибок канального кодера в приемнике резко уменьшается. Например, в обычной радиосреде, на которую действует замирание, ошибка пакета, указывающая, что биты данных в конкретной позиции одновременно потеряны, происходит часто. Перемежитель 140 выполняет функцию разделения соседних закодированных бит как можно дальше друг от друга для того, чтобы минимизировать потерю данных из-за ошибки пакета.

Перемежающиеся закодированные биты подаются в модулятор 150. В стандарте ВДПД перемежающиеся закодированные биты модулируются с помощью заранее определенного одного из различных способов модуляции, такого как КФМ (квадратурная фазовая манипуляция), 8ФМ (8-ричная фазовая манипуляция), 16КАМ (16-ричная амплитудная модуляция) и 64КАМ (квадратурная амплитудная модуляция), перед передачей. Из способов модуляции способ модуляции высокого порядка может передавать больше информации по сравнению со способом модуляции низкого порядка. Однако, если предполагается, что передатчик передает данные на одном и том же уровне мощности различных способов модуляции, вероятность потери данных является относительно высокой, когда используется способ модуляции высокого порядка, по сравнению с тем, когда используется способ модуляции низкого порядка. Следовательно, необходимо выбрать оптимальный способ модуляции в соответствии с окружением канала. Это контролируется контроллером 160 САКМ (системы автоматического контроля модуляции).

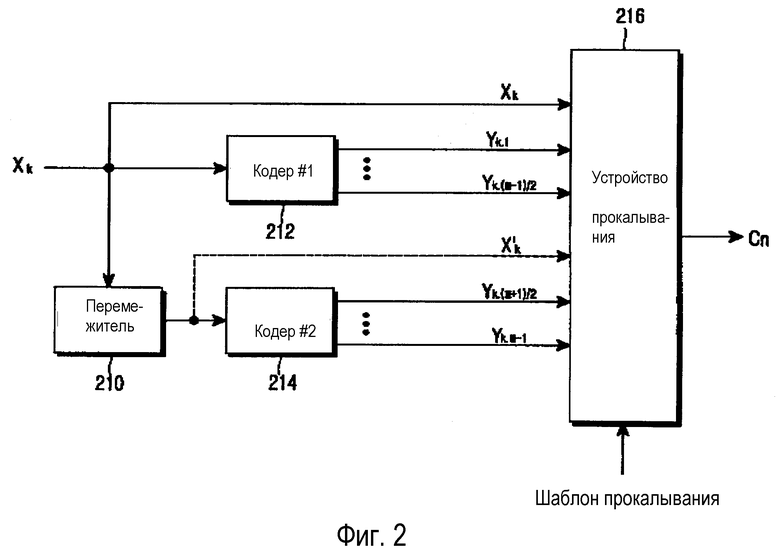

Фиг.2 иллюстрирует подробную структуру канального кодера 120, изображенного на фиг.1. Как проиллюстрировано на фиг.2, канальный кодер 120 включает в себя два составляющих кодера 212 и 214 с базовой кодовой скоростью 1/М, перемежитель 210 и устройство 216 прокалывания.

Ссылаясь на фиг.2, первый составляющий кодер 212 принимает заранее определенное число бит Хk входных данных и выводит закодированные биты в свой выходной порт Yk,L, если заранее определенная базовая скорость равна 1/3. Перемежитель 210 перемежает Хk бит входных данных. Второй составляющий кодер 214 кодирует перемежающиеся Хk биты данных, принятые из перемежителя 210. Если базовая кодовая скорость равна 1/3, второй составляющий кодер 214 выводит закодированные биты в свой выходной порт Yk,(M+1)/2. Систематические биты Хk, означающие фактические данные передачи, и биты Yk контроля четности складываются для того, чтобы скорректировать ошибку, сгенерированную во время декодирования в приемнике. На фиг.2 выходные данные первого кодера 212 представляются как Yk,1,...,Yk(M-1)/2, а выходные данные второго кодера 214 представляются как Yk,(M-1)/2,...,Yk,M-1. То есть, когда базовая кодовая скорость увеличивается до 1/3, 1/5 и 1/7, выходные порты первого и второго составляющих кодеров 212 и 214 увеличиваются в числе. Устройство 216 прокалывания контролируется в соответствии с кодовой скоростью, определенной контроллером 160. Конкретно устройство 216 прокалывания выборочно прокалывает систематические биты или биты контроля четности в соответствии с заранее определенным шаблоном прокалывания и выводит проколотые закодированные биты Сn, таким образом, удовлетворяя заранее определенной кодовой скорости и скорости модуляции. То есть устройство 216 прокалывания обеспечивается заранее определенным шаблоном прокалывания из контроллера 160 в соответствии с кодовой скоростью и прокалывает закодированные биты, выведенные из первого и второго кодеров 212 и 214.

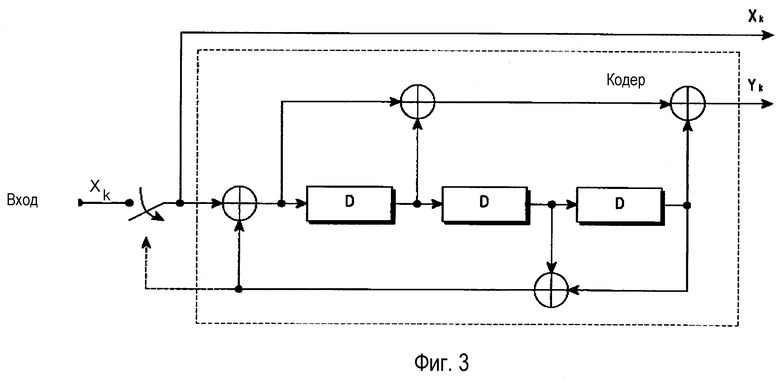

Фиг.3 иллюстрирует подробную структуру первого и второго кодеров 212 и 214, изображенных на фиг.2. Как проиллюстрировано на фиг.3, первый и второй кодеры 212 и 214, каждый обычно включает в себя множество сдвиговых регистров.

Ссылаясь на фиг.3, кодер кодирует входные биты Хk в систематические биты Хk и биты Yk контроля четности. Кодер может генерировать различные биты контроля четности для одного и того же входного бита в соответствии с тем, как соединены сдвиговые регистры. Начальные значения сдвиговых регистров все равны 0, а выходными данными кодера с базовой кодовой скоростью 1/М (М=3,5,7,...) являются X1,Y1,1,Y1,2,...,Y1,M-1,X2,Y2,1,Y2,2,...,Y2,M-1,...,Yk,1,Yk,2,...,Yk,M-1, где k представляет полное число входных бит. После кодирования всех входных бит переключатель на фиг.3 переключается так, что закодированные биты подаются обратно в сдвиговые регистры. Закодированные биты обратной связи используются как хвостовые биты. Следовательно, кодер, проиллюстрированный на фиг.3, может генерировать 3 хвостовые биты. Так как канальный кодер 120 состоит из двух кодеров 212 и 214, канальный кодер 120 генерирует всего 6 хвостовых бит. Число хвостовых бит, сгенерированных кодером, равно числу сдвиговых регистров, содержащих кодер. Если 3 хвостовые биты подаются в первый составляющий кодер 212, первый составляющий кодер 212 кодирует принятые хвостовые биты, а затем инициализирует сдвиговые региcтры в их начальные значения 0. 3 хвостовые биты, сгенерированные вторым составляющим кодером 214, подаются во второй составляющий кодер 214, и второй составляющий кодер 214 кодирует принятые хвостовые биты, а затем инициализирует сдвиговые регистры. Между тем, хвостовые биты, сгенерированные составляющими кодерами, и закодированные биты, сгенерированные с помощью кодирования хвостовых бит, называются РО (решетчатыми оконечными) битами. Если два кодера с базовой кодовой скоростью 1/М, каждый включает в себя L сдвиговых регистров, генерируются (М+1)хL РО битами. РО биты подвергаются прокалыванию или повторению с помощью устройства 130 согласования скорости вместе с закодированными битами.

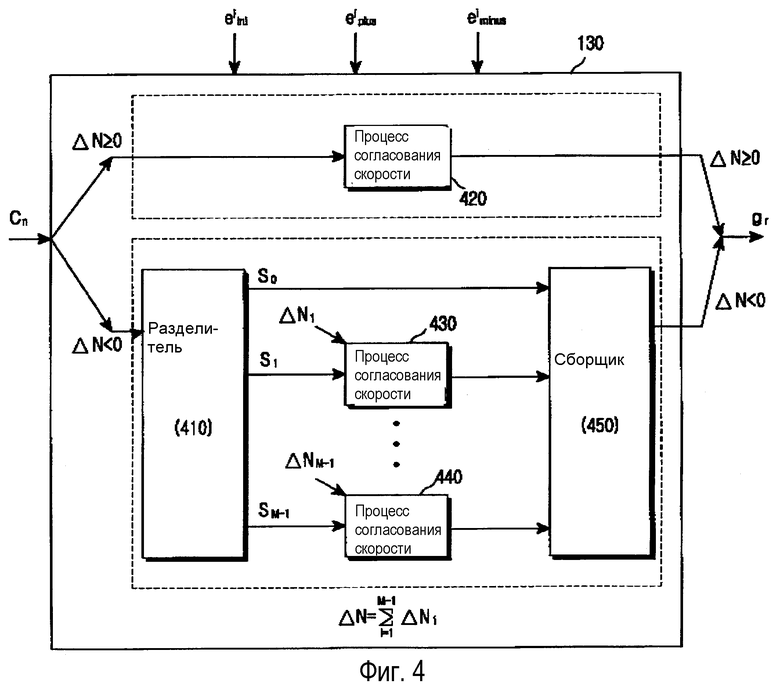

Фиг.4 иллюстрирует подробную структуру устройства 130 согласования скорости, изображенного на фиг.1. Как проиллюстрировано на фиг.4, устройство 130 согласования скорости разделяется на разделитель (или демультиплексор) 410 бит, сборщик (или мультиплексор) 450 бит и процессоры 420, 430 и 440 согласования скорости. Фиг.5 иллюстрирует общую процедуру для выполнения согласования скорости.

Ссылаясь на фиг.4 и фиг.5, входной сигнал Сn из канального кодера 120 подается в устройство 130 согласования скорости. Для входного сигнала Сn устройство 130 согласования скорости определяет, является ли число ΔN бит, прокалываемых и повторяемых, положительным числом или отрицательным числом, и определяет выполнить повторение или прокалывание в соответствии с определенными результатами (этап 512 фиг.5). То есть, если ΔN является отрицательным числом, устройство 130 согласования скорости прокалывает столько бит, чему равно ΔN из Сn. Иначе, если n является положительным числом, устройство 130 согласования скорости повторяет столько бит, чему равно ΔN из Сn.

Например, если ΔN является отрицательным числом, Сn подается в разделитель 410 бит. Разделитель 410 бит разделяет входные биты Сn на М бит от S0 до Sm-1. S0 представляет все систематические биты Хk среди входных бит Сn. Здесь S0 может включать в себя несколько РО бит. S1 до SM-1 представляет Yk,1 до Yk,M-1 соответственно. Каждый из S1 до SM-1 может также влючать в себя несколько РО бит. S1 до SM-1 подаются в свои связанные процессоры 430 и 440 согласования скорости, которые определяют биты, прокалываемые в соответствии с количеством прокалывания N (i=1~N 1). Процесс определения с помощью процессоров 430 и 440 согласования скорости, прокалывать ли каждый из S1 до SM-1, выполняется на этапах с 514 по 522 фиг.5. В большинстве случаев прокалывание выполняется относительно бит контроля четности, а не систематических бит. Следовательно, как проиллюстрировано на фиг.4, систематические биты S0 подаются непосредственно в сборщик 450 бит без отдельного согласования скорости. Сборщик 450 бит прокалывает биты, определенные, как прокалываемые, из закодированных бит, поданных из процессоров 430 и 440 согласования скорости, и выводит не проколотые закодированные биты вместе с систематическими битами S0, поданными из разделителя 410 бит.

Однако, если ΔN является положительным числом, должно быть выполнено повторение бит. Следовательно, входные биты Сn подаются в процессор 420 согласования скорости, где они подвергаются повторению бит. Процессор 420 согласования скорости для повторения бит применяется как для систематических бит, так и для бит контроля четности, и этот процесс выполняется на этапах с 524 по 534 фиг.5.

Закодированные биты gr, выведенные из процессора 420 согласования скорости и сборщика 450 бит, перемежаются перемежителем 140 и, наконец, модулируются с помощью модулятора 150 перед передачей в приемник.

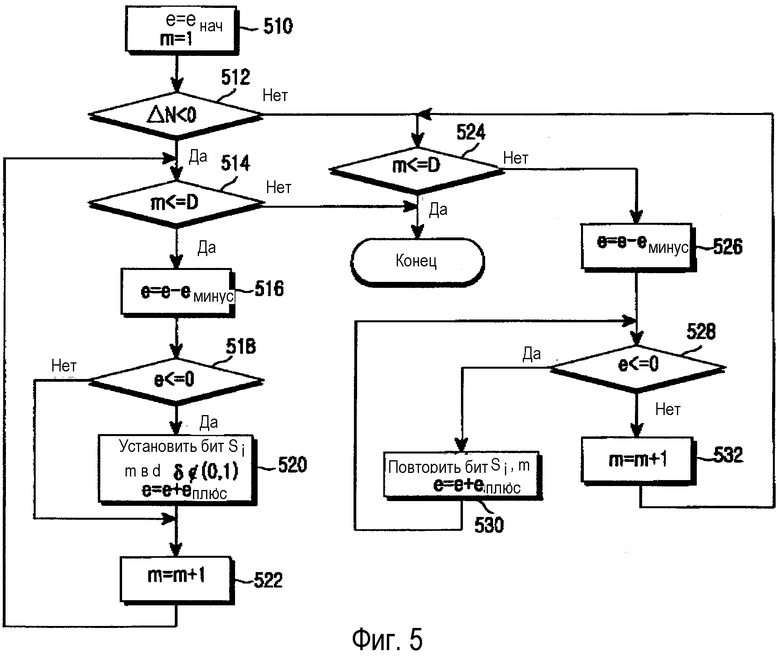

Фиг.5 иллюстрирует общую процедуру для выполнения согласования скорости. Параметры, используемые в описании операции согласования скорости со ссылкой на фиг.4 и фиг.5, включают:

е: начальная ошибка между текущей скоростью прокалывания и требуемой скоростью прокалывания;

енач: начальное значение е;

еминус: отрицательное приращение е;

еплюс: приращение е;

m: индекс текущего бита;

δ: значение, за исключением 0 и 1 (бит, за исключением

0 и 1 прокалывается сборщиком 450 бит) и

D: полное число бит, поданных в алгоритм согласования скорости.

Параметры енач, еминус и еплюс определяются из числа ΔN бит, прокалываемых или повторяемых, а способ определения основан на способе согласования скорости, определенном стандартом ПК3П. Начальная позиция прокалывания определяется параметром енач.

Ссылаясь на фиг.5, на этапе 510 устройство 130 согласования скорости устанавливает параметр енач в начальное значение е и устанавливает значение счетчика m в 1. На этапе 512 устройство 130 согласования скорости сравнивает число ΔN бит, прокалываемых или повторяемых, с “0” для того, чтобы определить, является ли ΔN положительным числом или отрицательным числом. Если определено на этапе 512, что ΔN является отрицательным числом, устройство 130 согласования скорости выполняет процесс прокалывания в течение этапов с 514 по 522. Иначе, если определено на этапе 512, что ΔN является положительным числом, устройство 130 согласования скорости выполняет процесс повторения в течение этапов с 524 по 530.

Сначала процесс прокалывания будет описан подробно. На этапе 514 устройство 130 согласования скорости сравнивает параметр m, указывающий порядок бит, обрабатываемых в текущий момент, с полным числом D входных бит (m≤D) для того, чтобы определить, полностью ли выполнено согласование скорости относительно всех входных бит. Если определено на этапе 514, что согласование скорости полностью выполнено относительно всех входных бит, устройство 130 согласования скорости заканчивает процесс прокалывания. Однако, если определено на этапе 514, что согласование скорости не полностью выполнено относительно всех входных бит, устройство 130 согласования скорости переходит к этапу 516. На этапе 516 устройство 130 согласования скорости обновляет значение е с помощью вычисления разности е-еминус между е и отрицательным приращением еминус, поданным из верхнего уровня. После обновления е устройство 130 согласования скорости определяет на этапе 518, является ли обновленное значение е меньшим или равным “0”. Если определено на этапе 518, что обновленное значение е меньше чем или равно “0”, устройство 130 согласования скорости переходит к этапу 520, так как соответствующий входной бит является прокалываемым битом. На этапе 520 устройство 130 согласования скорости устанавливает в некоторое значение, за исключением 0 и 1. Установка в значение, за исключением 0 и 1, эквивалентно обозначению битом, прокалываемым сборщиком 450 бит. Кроме того, на этапе 520 устройство 130 согласования скорости обновляет е с помощью вычисления суммы е+еплюс значения е и значения приращения еплюс, поданного из верхнего уровня. Если е больше чем “0” на этапе 518 или операция этапа 520 завершена, устройство 130 согласования скорости увеличивает на этапе 522 m на 1 для того, чтобы выбрать следующий бит, а затем возвращается на этап 514 для того, чтобы повторить процесс прокалывания.

Теперь процесс повторения будет описан подробно. На этапе 524 устройство 130 согласования скорости сравнивает m с D (m≤D) для того, чтобы определить, завершено ли согласование скорости. Если определено на этапе 524, что согласование скорости завершено, устройство 130 согласования скорости заканчивает процесс повторения. Однако, если определено на этапе 524, что согласование скорости еще не завершено, устройство 130 согласования скорости переходит к этапу 526. На этапе 526 устройство 130 согласования скорости обновляет е с помощью вычисления разности е-еминус между значением е и значением еминус. После обновления е устройство 130 согласования скорости определяет на этапе 528, является ли обновленное значение е меньше чем или равно “0”. Если определено на этапе 528, что обновленное значение е меньше чем или равно “0”, устройство 130 согласования скорости переходит к этапу 530, так как соответствующий входной бит является битом повторения. На этапе 520 устройство 130 согласования скорости повторяет соответствующий входной бит Si,m. Кроме того, на этапе 530 устройство 130 согласования скорости обновляет е с помощью вычисления суммы е+еплюс значений е и еплюс, а затем возвращается на этап 528 и сравнивает опять обновленное значение е с “0”, таким образом, чтобы определить, должно ли повторение быть выполнено опять. То есть, устройство 130 согласования скорости повторяет соответствующий входной бит заранее определенное число раз в течение этапов с 528 по 530. Однако, если е больше чем ”0” на этапе 528, устройство 130 согласования скорости увеличивает на этапе 532 m на 1 для того, чтобы выбрать следующий бит, а затем возвращается на этап 524 для того, чтобы повторить процесс повторения.

Как описано выше, в передатчике для традиционной системы мобильной связи МДКР канальный кодер и устройство согласования скорости сконструированы отдельно. В этом случае одно прокалывание выполняется с помощью устройства прокалывания в канальном кодере, а другое прокалывание выполняется опять с помощью устройства согласования скорости, таким образом, вызывая увеличение сложности технического обеспечения и времени обработки и уменьшение быстродействия канального кодера.

Следовательно, задачей настоящего изобретения является получить устройство и способ передачи/приема данных для улучшения эффективности всей системы с помощью объединения прокалывания/повторения для канального кодирования с прокалыванием/повторением для согласования скорости.

Другой задачей настоящего изобретения является получить устройство и способ передачи/приема данных для одновременного выполнения прокалывания/повторения для канального кодирования и прокалывания/повторения для согласования скорости с помощью выполнения одной операции прокалывания/повторения относительно закодированных бит.

Другой задачей настоящего изобретения является получить устройство и способ для объединения прокалывания/повторения для канального кодирования с прокалыванием/повторением для согласования скорости для того, чтобы увеличить эффективность канального кодера и упростить процедуру ГЗАПП (гибридного запроса автоматической повторной передачи).

В соответствии с первым аспектом настоящего изобретения предлагается передатчик для использования в системе мобильной связи, включающий в себя кодер для кодирования потока бит информации, принятых в течение данного периода передачи с базовой кодовой скоростью, и генерирования потока систематических бит и множества потоков бит контроля четности, и процессор для обеспечения множества параметров для согласования скорости в ноль (0) разности, определенной с помощью вычитания полного числа систематических бит и бит контроля четности, сгенерированных кодером, из полного числа бит, переданных через радиоканал в течение данного периода передачи. Передатчик содержит устройство согласования скорости, если разность равна отрицательной величине, для равномерного прокалывания одинакового числа бит, соответствующих разности в потоках бит контроля четности без прокалывания потока систематических бит, и, если разность равна положительной величине, для повторения одинакового числа бит, соответствующих разности в потоке систематических бит и потоках бит контроля четности, для того чтобы согласовать число передаваемых бит.

В соответствии со вторым аспектом настоящего изобретения предлагается способ передачи в системе мобильной связи, включающей в себя кодер для кодирования потока бит информации, принятых в течение данного периода передачи с базовой кодовой скоростью, и генерирования потока систематических бит и множества потоков бит контроля четности, и процессор для обеспечения множества параметров для согласования скорости в ноль (0) разности, определенной с помощью вычитания полного числа систематических бит и бит контроля четности, сгенерированных кодером, из полного числа бит, переданных через радиоканал в течение данного периода передачи. После приема запроса прокалывания на основании разности передатчик равномерно прокалывает потоки бит контроля четности одинаковым числом бит в каждых потоках бит контроля четности без прокалывания потока систематических бит, таким образом прокалывая столько бит, чему равна разность. После приема запроса повторения процессор изменяет параметры для того, чтобы предать другие биты для бит предыдущей передачи. Передатчик повторяет определенное число бит в потоке систематических бит и потоках бит контроля четности при почти одинаковом числе бит, таким образом повторяя столько бит, чему равна разность.

Вышеупомянутые и другие задачи, признаки и преимущества настоящего изобретения станут более понятными из следующего подробного описания, взятого совместно с сопровождающими чертежами, на которых:

фиг.1 иллюстрирует структуру обычного передатчика в системе мобильной связи МДКР;

фиг.2 иллюстрирует подробную структуру канального кодера, изображенного на фиг.1;

фиг.3 иллюстрирует подробную структуру кодеров, изображенных на фиг.2;

фиг.4 иллюстрирует подробную структуру устройства согласования скорости, изображенного на фиг.1;

фиг.5 иллюстрирует общую процедуру для выполнения согласования скорости;

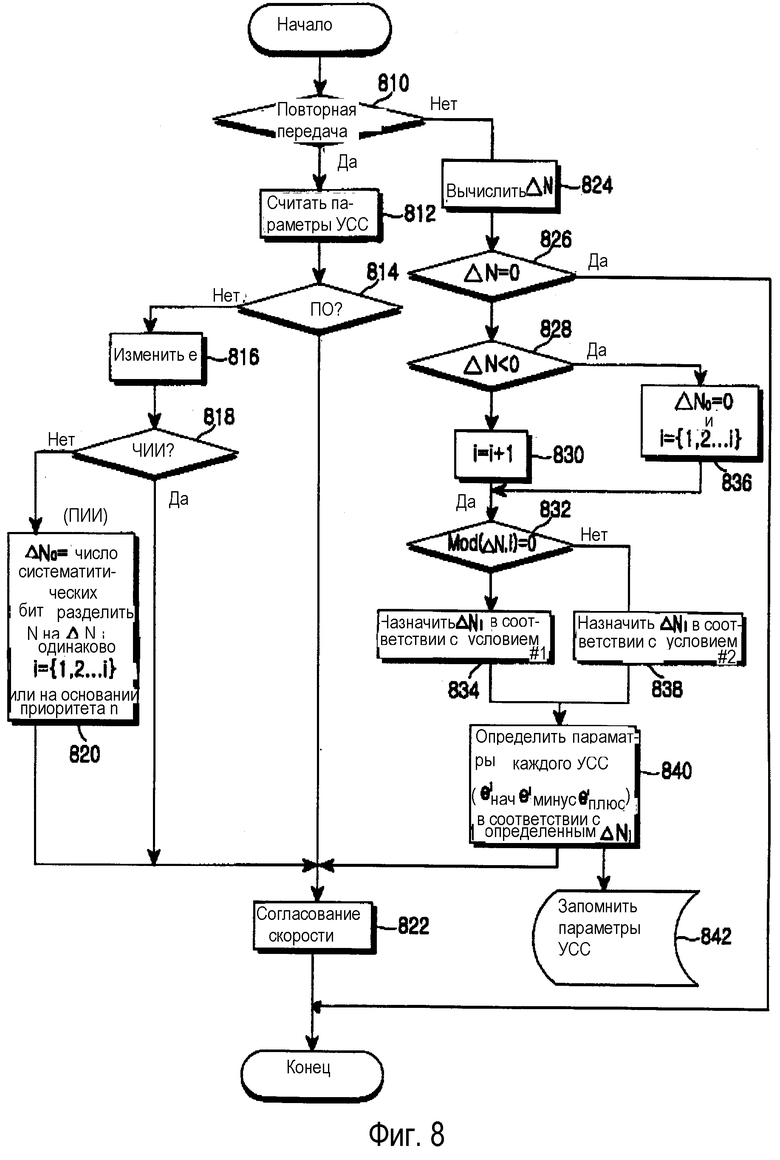

фиг.6 иллюстрирует структуру передатчика в системе мобильной связи МДКР в соответствии с осуществлением настоящего изобретения.

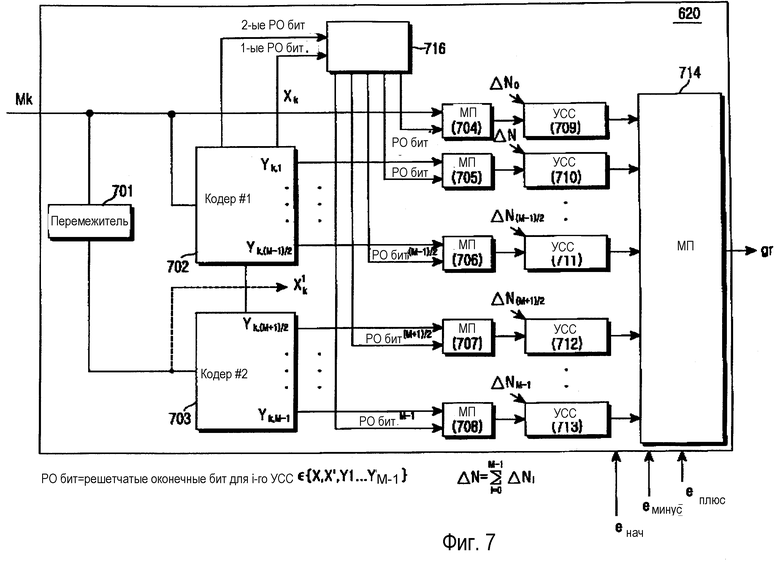

фиг.7 иллюстрирует объединенную структуру канального кодера и устройства согласования скорости в соответствии с осуществлением настоящего изобретения.

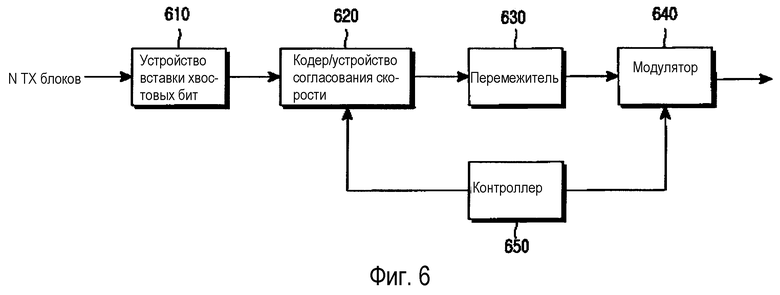

фиг.8 иллюстрирует процедуру для объединенного выполнения канального кодирования и согласования скорости в соответствии с осуществлением настоящего изобретения.

Предпочтительное осуществление настоящего изобретения будет описано здесь ниже со ссылкой на сопровождающие чертежи. В нижеследующем описании хорошо известные функции или конструкции не описаны подробно, так как они затеняли бы изобретение излишними деталями.

В передатчике для обычной системы мобильной связи МДКР назначение устройства прокалывания в канальном кодере отличается от назначения устройства согласования скорости. Однако, так как устройство прокалывания в канальном кодере также выполняет повторение, а также прокалывание, устройство прокалывания подобно по операции устройству согласования скорости. Следовательно, в осуществлении настоящего изобретения необходимо управлять устройством прокалывания в канальном кодере и устройством согласования скорости вместе, а не независимо. Кроме того, необходимо увеличить эффективность канального кодера с помощью предотвращения повторения, выполняемого устройством согласования скорости после того, как выполнено прокалывание канальным кодером.

Канальный кодер, применяемый в стандарте пакетной связи (например, ВДПД или 1×EV-DV) в самых последних системах мобильной связи МДКР, ввел способ адаптации линии связи, основанный на САКМ. Следовательно, канальный кодер генерирует бит контроля четности, число которых обычно больше (или меньше), чем число бит, которые могут передаваться. Это значит, что базовая кодовая скорость не равна кодовой скорости, которая фактически применяется. Следовательно, устройство прокалывания выполняет прокалывание или повторение. Кроме того, когда используется ГЗАПП (гибридный запрос автоматической повторной передачи), типичный способ высокоскоростной передачи пакетных данных, шаблон прокалывания может изменяться во время повторной передачи. ГЗАПП является способом управления линией связи, используемым, когда имеется ошибка в первоначально переданных пакетных данных. Следовательно, ГЗАПП является способом для повторной передачи пакетных данных, которые были дефектными при их первоначальной передаче, для того чтобы компенсировать дефектные пакетные данные. ГЗАПП может быть разделен на преследуемое объединение (ПО), полную инкрементную избыточность (ПИИ) и частичную инкрементную избыточность (ЧИИ). ПО является способом для передачи в течение передачи того же самого пакета, который передан как первоначальная передача, таким образом, шаблон прокалывания, используемый при повторной передаче, идентичен шаблону прокалывания, используемому при первоначальной передаче. ПИИ является способом для передачи систематических бит и бит контроля четности в конкретном соотношении при первоначальной передаче и передачи пакета, состоящего только из некоторых или всех бит контроля четности при повторной передаче для того, чтобы улучшить выигрыш кодирования декодера в приемнике. ЧИИ является способом для передачи в течение повторной передачи пакета данных, состоящего из систематических бит и ранее не переданных новых бит контроля четности. ЧИИ имеет аналогичное ПО действие при объединении во время декодирования систематических бит с первоначально переданными систематическими битами и имеет аналогичное ПИИ действие при декодировании бит контроля четности. В отличие от ПО инкрементная избыточность (ИИ), состоящая из ПИИ и ЧИИ, должна изменять шаблон прокалывания во время повторной передачи. Следовательно, должен также приниматься во внимание для того, чтобы управлять вместе устройством прокалывания в канальном кодере и устройством согласования скорости. Таким образом, осуществление настоящего изобретения предоставит способ для объединенного управления устройством прокалывания в канальном кодере и устройством согласования скорости, принимая во внимание ГЗАПП. Несмотря на то что настоящее изобретение будет описано со ссылкой на пример, где турбо-кодер используется в качестве канального кодера, изобретение может быть также применено к случаю, где сверточный кодер используется в качестве канального кодера. В этом случае систематические биты и биты контроля четности все служат в качестве бит контроля четности.

Перед описанием осуществления настоящего изобретения будет сделано описание примерных шаблонов прокалывания, основанных на кодовых скоростях, используемых в САКМ, и процессов канального кодирования и согласования скорости, выполняемых с помощью шаблонов прокалывания. В настоящем описании будет предполагаться базовая кодовая скорость 1/3, а кодовые скорости, используемые в САКМ, будут включать в себя 1/4 и 1/2 из 1/4, 1/2 и 3/4. Кодовые скорости 1/2 и 3/4 требуют прокалывания, так как они больше, чем базовая кодовая скорость 1/3. Однако кодовая скорость 1/4 требует повторения, так как она меньше, чем базовая скорость 1/3. В шаблонах прокалывания, данных ниже, “0” означает прокалывание соответствующего закодированного бита ”1”, означает не прокалывание соответствующего закодированного бита, а значение, большее чем ”1”, означает повторение соответствующего закодированного бита. Например, “2” в шаблоне прокалывания означает два повторения соответствующего закодированного бита.

Прежде всего будут описаны шаблоны прокалывания, основанные на кодовых скоростях, используемых в САКМ.

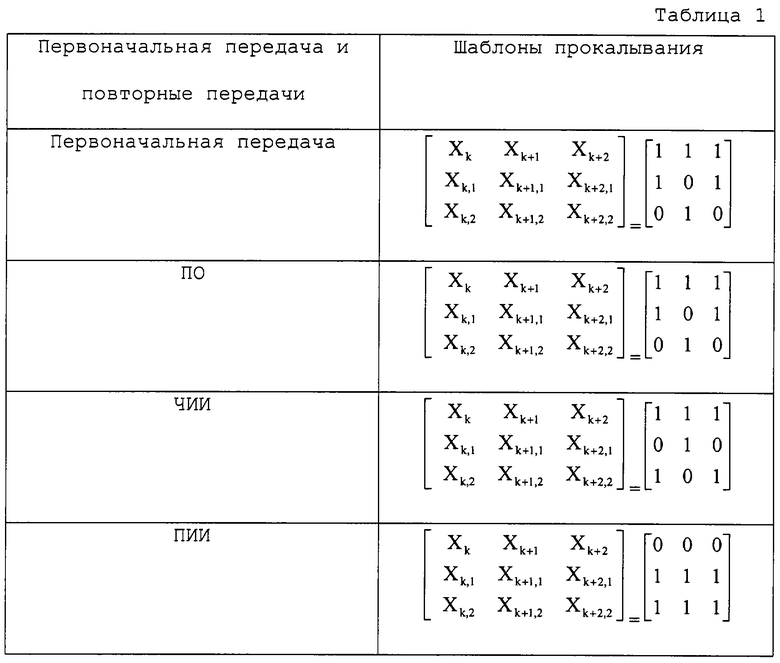

Во-первых, таблица 1 иллюстрирует примерные шаблоны прокалывания в соответствии с первоначальной передачей и повторными передачами для базовой кодовой скорости 1/3 и кодовой скорости 1/2.

Канальный кодер с базовой кодовой скоростью 1/3 кодирует 3 входных бита в 9 закодированных бит в соответствии с шаблоном прокалывания, проиллюстрированным в таблице 1, а затем прокалывает 3 бита из 9 закодированных бит, таким образом выводя 6 закодированных бит. Во время повторной передачи ПО использует тот же самый шаблон прокалывания, который использован при первоначальной передаче, но ЧИИ и ПИИ используют отличный шаблон прокалывания от шаблона прокалывания, использованного при первоначальной передаче.

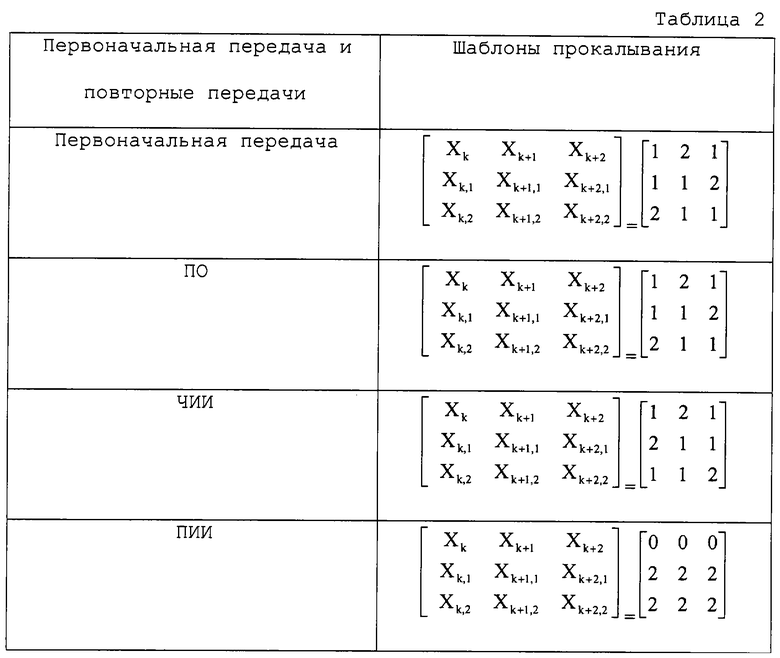

Во-вторых, таблица 2 иллюстрирует примерные шаблоны прокалывания в соответствии с первоначальной передачей и повторными передачами для базовой кодовой скорости 1/3 и кодовой скорости 1/4.

Канальный кодер с базовой кодовой скоростью 1/3 кодирует 3 входных бита в 9 закодированных бит в соответствии с шаблоном прокалывания, проиллюстрированным в таблице 2, а затем повторяет 3 бита из 9 закодированных бит, таким образом выводя 12 закодированных бит.

Далее будут описаны процессы канального кодирования и согласования скорости, выполняемые с помощью шаблонов прокалывания. Согласование скорости требуется, когда число закодированных бит, сгенерированных с помощью канального кодирования, не равно полному числу бит, которые могут быть переданы. То есть для того чтобы согласовать число закодированных бит с полным числом передаваемых бит, выполняется согласование скорости для прокалывания или повторения закодированных бит.

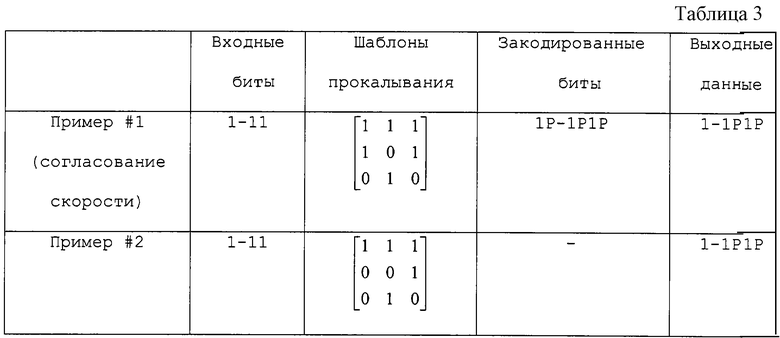

Во-первых, таблица 3 иллюстрирует примеры вывода полного числа бит закодированных бит, которые могут быть переданы посредством канального кодирования и согласования скорости, для базовой кодовой скорости 1/3 и кодовой скорости 1/2.

Из закодированных бит или выходных данных в таблице 3, 1 или –1 представляют систематические биты, а Р представляет бит контроля четности.

В примере #1 таблицы 3, если полное число передаваемых бит равно 5, канальный кодер с базовой кодовой скоростью 1/3 кодирует 3 входных бита в 9 закодированных бит, генерирует 6 закодированных бит с помощью прокалывания 3 бит из 9 закодированных бит в соответствии с шаблоном прокалывания, а затем прокалывает один из 6 закодированных бит для согласования скорости. Пример #1 таблицы 3 изображает традиционный способ, где канальное кодирование и согласование скорости разделены. Однако пример #2 таблицы 3 изображает новый способ, где канальное кодирование и согласование скорости объединены в соответствии с настоящим изобретением. Как проиллюстрировано в примере #1 таблицы 3, второй закодированный бит проколот из 6 закодированных бит с помощью согласования скорости так, что 5 закодированных бит выводятся как полное число передаваемых закодированных бит. В примере #2 таблицы 3, соответствующей примеру #1, возможно вывести 5 передаваемых закодированных бит посредством одного процесса прокалывания с помощью вставки “0” (прокалывания) в шаблон прокалывания в позиции закодированного бита, проколотого с помощью согласования скорости примера #1. Выходной результат примера #1 идентичен выходному результату примера #2.

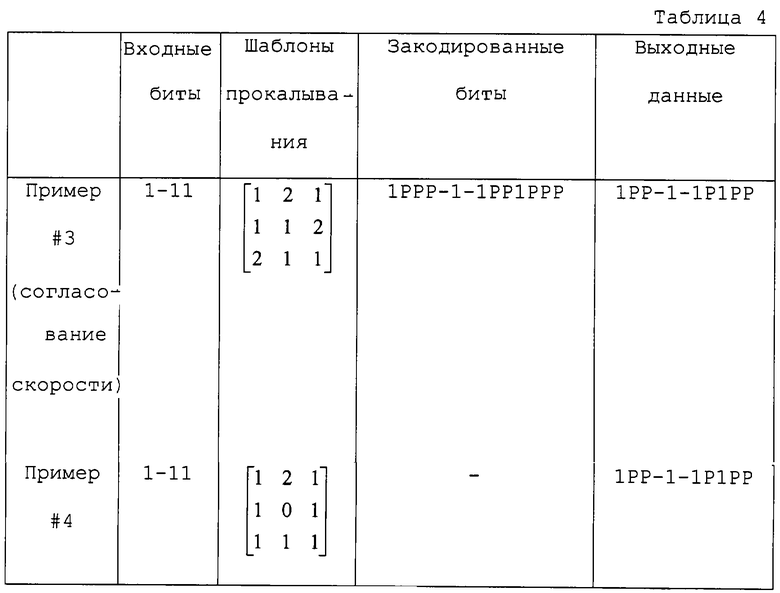

Во-вторых, таблица 4 иллюстрирует примеры вывода полного числа закодированных бит, передаваемых посредством канального кодирования и согласования скорости, для базовой кодовой скорости 1/3 и кодовой скорости 1/4.

Пример #3 таблицы 4 изображает традиционный способ, в котором, если полное число передаваемых бит равно 9, 3, биты проколоты из 12 закодированных бит для согласования скорости. Однако пример #4 таблицы 4 изображает новый способ, в котором канальное кодирование и согласование скорости объединены в соответствии с осуществлением настоящего изобретения. Конкретно пример #4 изображает шаблон прокалывания и закодированные биты, сгенерированные с помощью одновременного выполнения канального кодирования и согласования скорости в соответствии с шаблоном прокалывания. Как проиллюстрировано в примере #3 таблицы 4, четвертый, седьмой и одиннадцатый закодированные биты проколоты из 12 закодированных бит для согласования скорости так, что 9 закодированных бит выводятся как полное число передаваемых бит. В примере #4 таблицы 4, соответствующей примеру #3, возможно вывести 9 передаваемых закодированных бит посредством одного процесса прокалывания с помощью вставки “0” (прокалывания) в шаблон прокалывания в позиции закодированных бит, проколотых с помощью согласования скорости примера #3. Выходной результат примера #3 идентичен выходному результату примера #4.

Замечено из таблиц 3 и 4, что, когда заранее определенные закодированные биты прокалываются для согласования скорости, сначала прокалываются биты контроля четности вместо систематических бит.

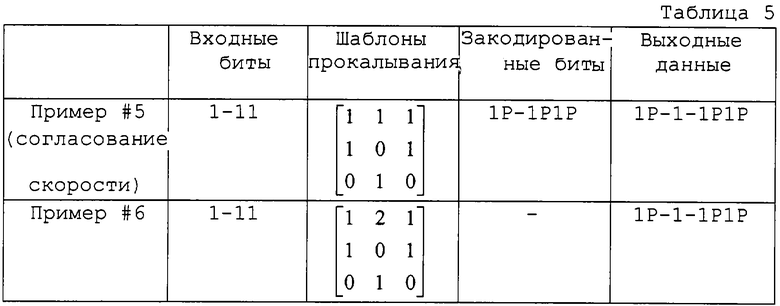

В-третьих, таблица 5 иллюстрирует примеры вывода полного числа закодированных бит, передаваемых посредством канального кодирования и согласования скорости, для базовой кодовой скорости 1/3 и кодовой скорости 1/2.

В примере #5 таблицы 5, если полное число передаваемых бит равно 7, 1 бит из 6 закодированных бит повторяется для согласования скорости. Пример #5 таблицы 5 изображает шаблон прокалывания для случая, где канальное кодирование и согласование скорости разделены в соответствии с предшествующим уровнем техники, закодированные биты основаны на шаблоне прокалывания и закодированные бит сгенерированы с помощью выполнения согласования скорости относительно закодированных бит. Пример #6 таблицы 5 изображает шаблон прокалывания для случая, где канальное кодирование и согласование скорости объединены в соответствии с настоящим изобретением, и закодированные биты сгенерированы с помощью выполнения канального кодирования и согласования скорости в соответствии с шаблоном прокалывания. Как проиллюстрировано в примере #5 таблицы 5, один закодированный бит из 6 закодированных бит повторяется для согласования скорости так, что 6 закодированных бит выводятся как полное число передаваемых бит. В примере #5 третий закодированный бит “-1” из 6 закодированных бит повторяется один раз (“2” в таблице 5 представляет повторение один раз). В примере #6 таблицы 5, соответствующей примеру #5, возможно вывести 7 передаваемых закодированных бит посредством одного процесса прокалывания с помощью вставки “1” (повторения) в шаблон прокалывания в позиции закодированного бита, повторенного с помощью согласования скорости примера #5. Выходной результат примера #5 идентичен выходному результату примера #6.

Как можно понять из предшествующего описания, независимое управление устройством прокалывания в канальном кодере и устройством согласования скорости требует дополнительного и излишнего процесса, и невозможно выполнить эффективное прокалывание с независимым управлением.

Между тем, результирующий шаблон прокалывания, данный с помощью примера 6 таблицы 5, представляется с помощью

Уравнение (1)

Из уравнения (1) следует отметить, что входной бит во втором столбце в первой строке повторяется. Для того чтобы получить более эффективный выигрыш кодирования по сравнению с шаблоном кодирования уравнения (1), предпочтительно передавать бит контроля четности без повторения систематического бита вместо прокалывания бита контроля четности, а затем повторить систематический бит. Шаблон прокалывания для этого изображен с помощью

Из уравнения (1) следует отметить, что входной бит во втором столбце в первой строке повторяется. Для того чтобы получить более эффективный выигрыш кодирования по сравнению с шаблоном кодирования уравнения (1), предпочтительно передавать бит контроля четности без повторения систематического бита вместо прокалывания бита контроля четности, а затем повторить систематический бит. Шаблон прокалывания для этого изображен с помощью

Уравнение (2)

Вышеприведенные примеры показали, что возможно реализовать объединенный шаблон прокалывания посредством примеров прокалывания или повторения заранее определенного числа бит на шаблон прокалывания в процессах канального кодирования и согласования скорости. Однако, когда все передаваемые закодированные биты генерируются с использованием шаблона прокалывания 9(3*3), шаблон прокалывания может быть использован несколько раз. Иначе должен быть использован очень большой шаблон прокалывания, указывающий все закодированные биты. Описание изобретения будет сделано для случая, где используется шаблон прокалывания примера #1, изображенного в таблице 3. Если число входных бит равно 30, канальный кодер с базовой кодовой скоростью 1/3 будет генерировать 90 закодированных бит. Так как шаблон прокалывания примера #1 представляет одну единицу прокалывания на 9 бит, если шаблон прокалывания применяется 10 раз, 3 бита прокалываются каждый раз, таким образом, прокалывая в целом 30 бит. В результате генерируются 60 закодированных бит. Если необходимо согласование скорости для прокалывания 4 бит, невозможно выполнить согласование скорости с помощью способа объединенного управления прокалыванием с помощью канального кодера и прокалывания с помощью устройства согласования скорости. Иначе должна использоваться единица шаблона прокалывания, равная 90. Оба этих случая требуют сложной обработки. По этой причине операционный принцип настоящего изобретения реализуется с помощью применения каждого закодированного бита в алгоритме согласования скорости вместо шаблона прокалывания, основанного на полном числе бит передачи.

Теперь предпочтительное осуществление настоящего изобретения будет описано подробно со ссылкой на сопровождающие чертежи.

Фиг.6 иллюстрирует структуру передатчика в системе мобильной связи МДКР в соответствии с осуществлением настоящего изобретения. Ссылаясь на фиг.6, N блоков передачи данных, передаваемых из верхнего уровня на физический уровень, подаются в устройство 610 вставки хвостовых бит. Устройство 610 вставки хвостовых бит вставляет хвостовые биты в каждом из блоков передачи данных. N блоков передачи со вставленными хвостовыми битами сначала кодируются с помощью кодера/устройства согласования скорости 620 с кодовой скоростью. Так как закодированные биты, закодированные с кодовой скоростью, не равны по числу битам данных, передаваемым через радиоканал, некоторые из закодированных бит подвергаются прокалыванию или повторению для согласования скорости для того, чтобы согласовать закодированные биты с числом бит, передаваемых через радиоканал.

Закодированные биты, сгенерированные с помощью согласования скорости, перемежаются с помощью перемежителя 630, и перемежающиеся закодированные биты модулируются с помощью модулятора 640 при заранее определенном способе модуляции перед передачей.

Как проиллюстрировано на фиг.6, в осуществлении настоящего изобретения структура для выполнения канального кодирования и структура для выполнения согласования скорости объединены в одну структуру. Процессор 650 генерирует множество параметров (еминус, еплюс, ΔN) для согласования скорости и управляющего сигнала модуляции для модулятора.

Фиг.7 иллюстрирует структуру для совместного выполнения канального кодирования и согласования скорости в передатчике системы мобильной связи МДКР в соответствии с осуществлением настоящего изобретения. Конкретно фиг.7 иллюстрирует объединенную структуру для выполнения канального кодирования с кодовой скоростью 1/М и выполнения прокалывания и повторения с использованием алгоритма согласования скорости.

Перед описанием структуры фиг.7 в соответствии с осуществлением настоящего изобретения понятия, используемые в настоящем описании, будут определены следующим образом.

Понятие “входные биты” относится к битам, принятым для канального кодирования, а понятие “поток входных бит” относится к потоку входных бит, последовательно подаваемых в кодер. Понятие “закодированные биты” означает биты, выведенные из кодера, а понятие “поток закодированных бит” означает поток закодированных бит, последовательно выведенных из кодера. Понятие “систематические биты” означает те же самые биты, как входные биты из закодированных бит, а понятие “поток систематических бит” означает поток систематических бит, последовательно выведенных из кодера. Понятие “биты контроля четности” означает биты контроля четности для коррекции ошибок систематических бит в приемнике из закодированных бит, а понятие “последовательность бит контроля четности” означает поток бит контроля четности, последовательно выведенных из кодера. Понятие “РО бит” означает биты, выведенные из кодера, только для согласования скорости, а понятие “поток РО бит” означает поток РО биты, последовательно выведенных из первого кодера. Понятие “первые РО биты” означает РО биты, выведенные из первого кодера, понятие “вторые РО биты” означает РО биты, выведенные из второго кодера. Понятие “поток первых РО бит” означает поток первых РО бит, последовательно выведенных из первого кодера, понятие “поток вторых РО бит” означает поток вторых РО бит, последовательно выведенных из второго кодера. Понятие “группа РО бит” означает каждую группу, полученную разделением РО бит на множество групп, связанных с множеством устройств согласования скорости для согласования скорости. В некоторых случаях систематические биты и биты контроля четности могут включать в себя хвостовые биты и РО биты. ΔN означает полное число бит, прокалываемых или повторяемых множеством устройств согласования скорости. То есть, ΔN указывает разность между полным числом закодированных бит, закодированных с базовой кодовой скоростью, и полным числом предаваемых бит. ΔN означает число бит, прокалываемых или повторяемых i-м устройством согласования скорости, где “i” используется для того, чтобы указать одно устройство согласования скорости из множества устройств согласования скорости или различать число бит, прокалываемых или повторяемых каждым устройством согласования скорости. ΔN означает число бит, повторяемых для потока систематических бит, а ΔN по ΔNi означают число бит, повторяемых для каждого потока бит контроля четности. Другие понятия имеют значения, определенные выше.

Ссылаясь на фиг.7, поток входных бит, состоящий из единичных входных бит Mk, подается совместно в первый составляющий кодер 702 и второй составляющий кодер 703 через перемежитель 701. Первый составляющий кодер 702 кодирует входные биты Мk с данной кодовой скоростью и выводит поток первых РО бит вместе с потоком закодированных бит. Например, если базовая кодовая скорость равна 1/М, поток закодированных бит, выеденных из первого составляющего кодера 702, включает в себя один поток систематических бит Хk и (М-1)/2 потоков бит контроля четности с Yk,1 по Yk,(M-1)/2.

Второй составляющий кодер 703 кодирует перемежающиеся входные биты Х’k, поданные из перемежителя 701, с данной кодовой скоростью и выводит поток вторых РО бит вместе с потоками закодированных бит. Например, если базовая скорость равна 1/М, поток закодированных бит, выведенных из второго составляющего кодера 703, включает в себя один поток систематических бит Х’k и (М-1)/2 потоков бит контроля четности с Yk,(M-1)/2 по Yk,M-1. Обычно не нужно выводить Х. Однако выводятся хвостовые биты для инициализации первого составляющего кодера 702 и хвостовые биты для инициализации второго составляющего кодера 703.

Если базовая скорость равна 1/3, в основном выводятся закодированные биты Хk, Yk,1 и Yk,2. Кроме того, существуют первые хвостовые биты для инициализации первого составляющего кодера 302, вторые хвостовые биты для инициализации второго составляющего кодера 703, первые РО биты, полученные с помощью кодирования первых хвостовых бит первым составляющим кодером 702, и вторые РО биты, полученные с помощью кодирования вторых хвостовых бит вторым составляющим кодером 703. Поток РО бит включает в себя первые и вторые хвостовые биты и первые и вторые РО биты. Поток первых РО бит включает в себя первые хвостовые биты и первые РО биты, а поток вторых РО бит включает в себя вторые хвостовые биты и вторые РО биты. Здесь k – индекс, указывающий порядок сигнала бит.

Между тем, полное число бит, составляющих поток первых РО бит и поток вторых РО бит, выведенных из первого составляющего кодера 702 и второго составляющего кодера 703, определяется как (М+1)хL, если определено число L хвостовых бит. Здесь L означает число хвостовых бит, сгенерированных первым составляющим кодером 702 и вторым составляющим кодером 703.

Поток первых РО бит и поток вторых РО бит подается в распределитель 716 РО бит. Первые и вторые РО биты во время согласования скорости относительно потоков закодированных бит используются для того, чтобы быть мультиплексированными с закодированными битами каждого потока закодированных бит. Определение и функция РО бит, составляющих поток первых РО бит и поток вторых РО бит, уже описаны. Распределитель 716 РО бит распределяет первые и вторые РО биты, составляющие потоки первых и вторых РО бит, из первого составляющего кодера 702 и второго составляющего кодера 703 в группы РО бит, число которых равно числу потоков закодированных бит из первого составляющего кодера 702 и второго составляющего кодера 703. Распределитель 716 РО бит распределяет РО биты так, что группы РО бит для каждого потока закодированных бит должны иметь одинаковое число РО бит. На фиг.7, так как базовая кодовая скорость первого и второго составляющих кодеров 702 и 703 определяется как 1/М, распределитель 716 РО бит распределяет РО биты, составляющие потоки РО бит, в М групп РО бит. М групп РО бит, каждая состоящая из заранее определенного числа РО бит, распределителем РО биты подаются в М связанных мультиплексоров (МП) 704 по 708. На фиг.7 М групп РО бит представляются с помощью РО бит1, РО бит2,..., РО бит(M-1)/2, РО бит(M+1)/2,..., и РО битM-1 соответственно.

Между тем, число мультиплексоров 704 по 708, принимающих выходные сигналы первого составляющего кодера 702 и второго составляющего кодера 703, и РО бит в единице группы РО бит из распределителя 716 РО бит равно числу потоков закодированных бит, сгенерированных при базовой кодовой скорости. Например, если базовая кодовая скорость равна 1/3, канальный кодер 620 должен включать в себя 3 мультиплексора, так как 3 потока закодированных бит, включающие поток систематических бит и выходные биты первого составляющего кодера 702 и второго составляющего кодера 703, генерируются при базовой кодовой скорости. То есть 3 мультиплексора соответствуют потоку систематических бит, выходным битам первого составляющего кодера 702 и выходным битам второго составляющего кодера 703 соответственно. На фиг.7, так как базовая кодовая скорость первого составляющего кодера 702 и второго составляющего кодера 703 равна 1/М, канальный кодер 620 включает в себя М мультиплексоров. Мультиплексоры 704 по 708 каждый мультиплексирует свои потоки входных закодированных бит с РО битами в единице группы РО бит. Среди мультиплексоров 704 по 708 мультиплексор 704, принимающий поток систематических бит, мультиплексирует поток систематических бит с РО бит в соответствующей группе РО бит.

Потоки закодированных бит, мультиплексированные с РО битами, выведенные из мультиплексоров 704 по 708, подаются в соответствующие устройства 709 по 713 согласования скорости (УСС). То есть поток систематических бит, мультиплексированный с РО битами1, выведенный из мультиплексора 704, подается в устройство 709 согласования скорости, а поток бит контроля четности, мультиплексированный с РО битами2, выведенный из мультиплексора 705, подается в устройство 710 согласования скорости. Поток бит контроля четности, мультиплексированный с РО(M-1)/2 битами, выведенный из мультиплексора 706, подается в устройство 711 согласования скорости. Поток бит контроля четности, мультиплексированный с

РО битами(M+1)/2, выведенный из мультиплексора 707, подается в устройство 712 согласования скорости. Наконец, поток бит контроля четности, мультиплексированный с РО битамиM-1, выведенный из мультиплексора 708, подается в устройство 713 согласования скорости.

Следовательно, число устройств 709 по 713 согласования скорости должно быть равно числу мультиплексоров 704 по 708. Кроме того, устройства 709 по 713 согласования скорости снабжаются номерами ΔN0 по ΔNM-1 прокалываемых или повторяемых бит, присвоенными им из верхнего уровня. Сумма номеров ΔN0 по NM-1, прокалываемых или повторяемых бит, предоставленных устройствам 709 по 713 согласования скорости, равна полному числу прокалываемых или повторяемых бит с помощью канального кодирования и согласования скорости. Это выражается с помощью

Уравнение (3)

Устройства 710 по 713 согласования скорости определяют повторяемые или прокалываемые биты в потоках закодированных бит из мультиплексоров 705 по 708 на основании номеров, присвоенных им, повторяемых или прокалываемых бит. Между тем, устройство 709 согласования скорости принимает поток систематических бит, мультиплексированный с РО битами в группе первых РО бит, выведенной из мультиплексора 704, и определяет повторяемые систематические биты среди систематических бит, составляющих поток систематических бит. То есть мультиплексор 709, управляющий систематическими битами, не активизируется во время прокалывания. Это может быть выражено с помощью ΔN0=0 для ΔN<0. ΔN<0 означает, что требуется прокалывание относительно закодированных бит. В этом случае устройство 709 согласования скорости не активизируется с помощью установки числа ΔN0 повторяемых систематических бит в “0”. Здесь биты, повторяемые или прокалываемые среди закодированных бит в одном потоке закодированных бит, могут быть определены с помощью процесса, описанного в связи с фиг.5. После определения повторяемых или прокалываемых закодированных бит устройства 709 по 713 согласования скорости подают свои потоки закодированных бит в сборщик бит или мультиплексор (МП) 714.

Сборщик бит (или МП) 714 прокалывает или повторяет биты, определенные прокалываемыми или повторяемыми устройствами 709 по 713 согласования скорости, и выводит столько бит, чему равно число требуемых бит передачи.

Устройство прокалывания в традиционном канальном кодере 120 и разделитель 410 бит в традиционном устройстве 130 согласования скорости могут быть исключены, так как кодер/устройство согласования скорости 620 фиг.7 включает в себя мультиплексоры 704 по 708, связанные с потоками закодированных бит из первого составляющего кодера 702 и второго составляющего кодера 703.

Фиг.8 иллюстрирует процедуру для совместно выполняемого канального кодирования и согласования скорости в передатчике для системы мобильной связи МДКР в соответствии с осуществлением настоящего изобретения. Процедура фиг.8 разделяется на операцию во время первоначальной передачи и операцию во время повторной передачи.

Параметры, используемые на фиг.8, будут определены следующим образом. Постоянная условия k обозначает число устройств согласования скорости для выполнения повторения или прокалывания среди устройств согласования скорости, i – величина, обозначающая устройство согласования скорости для выполнения повторения или прокалывания. Диапазон параметра i определяется в соответствии с тем, выполнять ли повторение или прокалывание. В следующем описании полное число устройств согласования скорости будет представляться с помощью М.

Ссылаясь на фиг.8, кодер/устройство согласования скорости 620 определяет на этапе 810, является ли текущая передача повторной передачей. Если определено на этапе 819, что текущая передача является повторной передачей, кодер/устройство согласования скорости 620 выполняет согласование скорости в течение этапов 812 по 820. Однако, если определено на этапе 810, что текущая передача является первоначальной передачей, кодер/устройство согласования скорости 620 выполняет согласование скорости в течение этапов 824 по 842. Согласование скорости происходит после каждого из вышеупомянутых процессов.

Во-первых, будет описана операция во время первоначальной передачи. На этапе 824 кодер/устройство согласования скорости 620 вычисляет полное число ΔN бит, прокалываемых или повторяемых во время первоначальной передачи, на основании полного числа передаваемых бит и полного числа бит, сгенерированных при кодировании заранее определенного числа К входных бит с базовой кодовой скоростью. После вычисления ΔN кодер/устройство согласования скорости 620 определяет на этапе 826, равно ли ΔN “0”. Если ΔN равно “0”, это значит, что число передаваемых бит равно числу закодированных бит, таким образом, прокалывание или повторение относительно закодированных бит не требуется. Следовательно, если определено на этапе 826, что ΔN равно “0”, кодер/устройство согласования скорости 620 подает поток закодированных бит в перемежитель 630 без выполнения согласования скорости. Однако, если определено на этапе 826, что ΔN не равно “0”, кодер/устройство согласования скорости 620 определяет на этапе 828, больше ли или равно ли ΔN “0”. То, что ΔN меньше чем “0” означает, что N бит должны быть проколоты среди закодированных бит. В противоположность, то, что ΔN больше чем “0”, означает, что ΔN бит среди закодированных бит должны быть повторены. Следовательно, если определено на этапе 828, что ΔN больше чем “0”, кодер/устройство согласования скорости 620 переходит к этапу 830 для того, чтобы повторить ΔN бит среди закодированных бит. Однако, если определено на этапе 828, что ΔN меньше чем “0”, кодер/устройство согласования скорости 620 переходит к этапу 836 для того, чтобы проколоть ΔN бит среди закодированных бит.

На этапе 830 кодер/устройство согласования скорости 620 устанавливает диапазоны k и i так, что число ΔN повторяемых бит назначается каждому из М устройств согласования скорости при выполнении согласования скорости относительно закодированных бит. Следовательно, на этапе 830 кодер/устройство согласования скорости 620 устанавливает k в полное число М устройств согласования скорости так, что число повторяемых бит может быть назначено всем устройствам согласования скорости, а также устанавливает диапазон i в 0≤i≤M-1, т.е. {0,1,2,...,М-1}. Однако на этапе 836, так как невозможно назначить число прокалываемых бит устройству согласования скорости для управления систематическими бит, кодер/устройство согласования скорости 620 должен установить диапазоны k и i так, что число прокалываемых бит должно быть назначено устройствам согласования скорости, за исключением устройства согласования скорости для управления систематическими бит. Следовательно, на этапе 836 кодер/устройство согласования скорости 620 устанавливает k в М-1 и устанавливает диапазон i в 1≤i≤M-1, т.е. {1,2,...,М-1}. Кроме того, кодер/устройство согласования скорости 620 устанавливает число ΔN прокалываемых бит, поданных в устройство согласования скорости для управления потоком систематических бит, в “0”. Следовательно, при выполнении этапа 830 кодер/устройство согласования скорости 620 устанавливает параметры так, что полное число N прокалываемых бит должно быть распределено в (М-1) групп бит. То есть во время повторения все устройства согласования скорости выполняют операцию повторения. Однако во время прокалывания все устройства согласования скорости, за исключением устройства согласования скорости для управления потоком систематических бит, выполняют операцию прокалывания.

После установки диапазонов k и i для повторения или прокалывания в течение этапов 830 по 836 кодер/устройство согласования скорости 620 выполняет операцию назначения ΔNi. ΔNi указывает число бит, прокалываемых или повторяемых соответствующим устройством согласования скорости. Имеются несколько способов распределения полного числа ΔN прокалываемых или повторяемых бит в устройства согласования скорости. В настоящем описании настоящее изобретение предоставит 4 возможных способа.

В первом способе ΔN является кратным k, и всем закодированным битами назначается одинаковый приоритет. Например, предполагается, что М=4, ΔN=6 и выполняется прокалывание. В этом случае k=3 и 1≤i≤3. Следовательно, Ni, т.е. ΔN1, ΔN2 и ΔN3, каждому назначается 2 так, что каждое из устройств согласования скорости, за исключением устройства согласования скорости для управления потоком систематических бит, прокалывает 2 бита. Однако, если предполагается, что М=3, N=6 и выполняется повторение, тогда k=3 и 1 i

i 2. Следовательно, ΔNi, т.е. ΔN1, ΔN2 и ΔN3, каждому назначается 2 так, что каждое из устройств согласования скорости повторяет 2 бита.

2. Следовательно, ΔNi, т.е. ΔN1, ΔN2 и ΔN3, каждому назначается 2 так, что каждое из устройств согласования скорости повторяет 2 бита.

Во втором способе ΔN является кратным k, и закодированным битам назначаются различные приоритеты. Например, предполагается, что М=4, ΔN=6 и выполняется прокалывание. В этом случае k=3 и 1≤i≤3. Следовательно, ΔNi назначается 3, ΔN2 назначается 2 и ΔN3 назначается 1. Кроме того, ΔN0, соответствующему устройству согласования скорости для управления потоком систематических бит, назначается 0. Однако, если предполагается, что М=3, ΔN=6 и выполняется повторение, тогда k=3 и 1≤i≤2. Следовательно, ΔN0 назначается 3, ΔN1 назначается 2 и ΔN2 назначается 1. То есть приоритет закодированных бит, управляемых соответствующими устройствами согласования скорости, назначается различному числу бит, прокалываемых или повторяемых соответствующими устройствами согласования скорости. Здесь при первоначальной передаче ранее не переданные биты контроля четности являются более высокими по приоритету, чем поток систематических бит.

В третьем способе ΔN не является кратным k, и всем закодированным битам назначается одинаковый приоритет. Например, предполагается, что М=4, ΔN=5 и выполняется прокалывание. В этом случае k=3 и 1≤i≤3. Следовательно, ΔN1 назначается 2, ΔN2 назначается 2 и ΔN3 назначается 1. Кроме того, ΔN0, соответствующему устройству согласования скорости для управления потоком систематических бит, назначается 0. Однако, если предполагается, что М=3, ΔN=5 и выполняется повторение, тогда k=3 и 1≤i≤2. Следовательно, N назначается 2, ΔN1 назначается 2 и ΔN2 назначается 1. В этом способе число бит, назначаемых устройствам согласования скорости, соответствующим случаю, где ΔN не является кратным k, поддерживается по возможности одинаковым.

В четвертом способе ΔN не является кратным k, и закодированным битам назначаются различные приоритеты. Например, предполагается, что М=4, ΔN=5 и выполняется прокалывание. В этом случае k=3 и 1≤i≤3. Следовательно, ΔN1 назначается 3, ΔN2 назначается 1 и ΔN3 назначается 1. Кроме того, ΔN0, соответствующему устройству согласования скорости для управления потоком систематических бит, назначается 0. Однако, если предполагается, что М=3, ΔN=5 и выполняется повторение, тогда k=3 и 1≤i≤2. Следовательно, ΔN0 назначается 3, ΔN1 назначается 1 и ΔN2 назначается 1. В этом способе систематические биты, имеющие более высокий приоритет, чем бит контроля четности, обрабатываются первыми.

Следовательно, для того, чтобы назначить ΔNi на основании ΔN и k, используется один из четырех способов. Несмотря на то, что в настоящем описании проиллюстрированы четыре способа, могут быть рассмотрены другие способы.

Процесс выполнения вышеупомянутых способов будет описан со ссылкой на фиг.8. На этапе 832 кодер/устройство согласования скорости 620 определяет, является ли ΔN кратным k. Для этого кодер/устройство согласования скорости 620 выполняет операцию относительно k по модулю N. Если результат операции по модулю равен “0”, кодер/устройство согласования скорости 620 определяет, что ΔN является кратным k. Иначе, если результат операции по модулю равен “1”, кодер/устройство согласования скорости 620 определяет, что ΔN не кратно k. Если определено на этапе 832, что ΔN является кратным k, кодер/устройство согласования скорости 620 переходит к этапу 834, где он назначает ΔNi по первому условию. Первым условием является условие для применения первого способа и второго способа. Следовательно, на этапе 834 кодер/устройство согласования скорости 620 может назначать ΔNi в первом способе и втором способе. Однако, если определено на этапе 832, что ΔN не является кратным k, кодер/устройство согласования скорости 620 переходит к этапу 838, где он назначает ΔNi по второму условию. Вторым условием является условие для применения третьего способа и четвертого способа. Следовательно, на этапе 838 кодер/устройство согласования скорости 620 может назначать ΔNi в третьем способе и четвертом способе.

После назначения ΔNi на этапах 843 и 838 кодер/устройство согласования скорости 620 определяет на этапе 840 параметры УСС в соответствии с определенными ΔNi. Параметры УСС включают в себя параметры устройств согласования скорости енач, еминус, е плюс и Di, требуемые для выполнения согласования скорости с помощью алгоритма, изображенного на фиг.5. Параметр Di указывает число закодированных бит, поданных в каждое устройство согласования скорости. Параметры УСС определяются в зависимости от заранее определенной кодовой скорости, канальной кодовой скорости и числа бит передачи. Параметр енач является параметром для определения первоначально прокалываемого или повторяемого бита, и на основании значения еплюс и значения еминус кодер/устройство согласования скорости 620 определяет период, в который он будет прокалывать или повторять закодированные биты, поданные в устройства согласования скорости. То есть, если число прокалываемых или повторяемых бит равно 4, кодер/устройство согласования скорости 620 определяет параметры так, что закодированные биты, поданные в устройства согласования скорости, прокалываются или повторяются с периодами 4 бит. Предпочтительно определять период как можно длительный.

После определения параметров УСС на этапе 840 кодер/устройство согласования скорости 620 запоминает определенные параметры в данном буфере на этапе 842. После этого кодер/устройство согласования скорости 620 переходит к этапу 822, где устройства согласования скорости каждое прокалывает или повторяет столько закодированных бит, чему равно определенное число на основании определенных параметров.

Затем будет описана операция во время повторной передачи. На этапе 812 кодер/устройство согласования скорости 620 считывает параметры УСС, запомненные в буфере на этапе 842. Параметры УСС указывают параметры, запомненные при первоначальной передаче на этапе 842. После считывания параметров УСС кодер/устройство согласования скорости 620 определяет на этапе 814, использовать ли ПО как ГЗАПП. Обычно ПО является ГЗАПП для передачи тех же самых закодированных бит, которые передавались при первоначальной передаче, даже во время повторной передачи. Следовательно, если определено на этапе 814, что ПО используется как ГЗАПП, кодер/устройство согласования скорости 620 переходит к этапу 822, где оно выполняет согласование скорости на основании считанных параметров УСС. Однако, если ПО не поддерживается, кодер/устройство согласования скорости 620 исключает операцию на этапе 814 и переходит к этапу 816.

Однако, если определено на этапе 814, что ПО не используется как ГЗАПП, это значит, что ИИ используется как ГЗАПП. Следовательно, кодер/устройство согласования скорости 620 переходит к этапу 816, где он изменяет параметр енач, определенный при первоначальной передаче. Например, в случае ИИ передаваемые закодированные биты изменяются при первоначальной передаче и каждой повторной передаче. Причиной для изменения енач является повторять или прокалывать различные закодированные биты при каждой передаче с помощью изменения первоначального значения для первоначального прокалывания или повторения. То есть, когда енач изменяется, хотя число прокалываемых или повторяемых бит является постоянным, позиции прокалываемых или повторяемых бит изменяются. Процессор 650 изменяет значение енач, когда повторная передача требуется с помощью гибридного запроса автоматической повторной передачи (ГЗАПП).

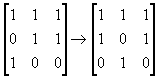

После изменения енач кодер/устройство согласования скорости 620 определяет на этапе 818, используется ли ЧИИ как ГЗАПП. Обычно ЧИИ является ГЗАПП для поддержания систематических бит среди первоначально переданных закодированных бит и изменения только бит контроля четности во время повторной передачи. С этой целью ΔN0 должно поддерживаться в 0. Следовательно, ΔNi не изменяется. По этой причине все биты контроля четности, сгенерированные при базовой кодовой скорости, биты контроля четности, отличные от бит контроля четности, переданных при первоначальной передаче, передаются, так как измененное енач отличается от енач, установленного во время первоначальной передачи. При описании вышеупомянутого способа с шаблоном прокалывания уравнение (4) изображает пример выполнения прокалывания в позиции, сдвинутой на один бит в соответствии с другим енач.

Уравнение (4)

В уравнении (4) левый шаблон прокалывания был использован в предыдущей передаче, а правый шаблон прокалывания будет использован в текущей повторной передаче. По сравнению с шаблоном прокалывания, использованным при предыдущей передаче, шаблон прокалывания, используемый при текущей повторной передаче, имеет вторую строку, сдвинутую вправо на единицу. Кроме того, последняя строка также сдвинута вправо на единицу. То есть изменение енач эквивалентно изменению шаблона прокалывания, как проиллюстрировано в уравнении (4).

Следовательно, если определено на этапе 818, что ЧИИ используется как ГЗАПП, кодер/устройство согласования скорости 620 переходит к этапу 822, где он выполняет согласование скорости на основании считанных параметров УСС и измененного енач. Однако, если определено на этапе 818, что ЧИИ не используется как ГЗАПП, кодер/устройство согласования скорости 620 переходит к этапу 820, так как это значит, что ПИИ используется как ГЗАПП. ПИИ является ГЗАПП для передачи не систематических бит, а передачи только измененных бит контроля четности во время повторной передачи. Следовательно, на этапе 820 для того, чтобы предотвратить систематические биты от того, чтобы они были переданы, кодер/устройство согласования скорости 620 устанавливает ΔN0 в число систематических бит. То есть все систематические биты прокалываются. Кроме того, так как возможно передавать больше бит контроля четности, кодер/устройство согласования скорости 620 назначает ΔNi, за исключением ΔN0, с использованием одного из четырех способов. После назначения ΔNi кодер/устройство согласования скорости 620 определяет параметры на основании назначенных ΔNi, а затем переходит к этапу 822 для того, чтобы выполнить согласования скорости.

Как описано выше, настоящее изобретение использует канальное кодирование с согласованием скорости для того, чтобы уменьшить сложность технического обеспечения передатчика для системы мобильной связи МДКР, и таким образом уменьшить стоимость. Кроме того, возможно быстро выполнять канальное кодирование и согласование скорости относительно данных передачи, таким образом сокращая время задержки обработки данных в передатчике.

Несмотря на то, что изобретение изображено и описано со ссылкой на его определенное осуществление, специалистам в данной области техники будет понятно, что различные изменения по форме и деталям могут быть сделаны в нем, не выходя за рамки объема и сущности изобретения, как определено прилагаемой формулой изобретения.

Изобретение относится к системам передачи данных в системе мобильной связи с множественным доступом с кодовым разделением (МДКР) каналов. Достигаемый технический результат - улучшение эффективности системы с помощью объединения прокалывания или повторения для канального кодирования с прокалыванием или повторением для согласования скорости. Передатчик для использования в системе мобильной связи включает кодер для кодирования потока бит информации и генерирования потока систематических бит и множества потоков бит контроля четности, процессоров для согласования скорости в ноль разности, устройство согласования скорости. 5 н. и 22 з.п. ф-лы, 8 ил, 5 табл.

| US 5870393 А, 09.02.1999 | |||

| СПОСОБ ОРТОГОНАЛЬНОЙ РАЗНЕСЕННОЙ ПЕРЕДАЧИ-ПРИЕМА СИГНАЛА В СОТОВОЙ СИСТЕМЕ РАДИОСВЯЗИ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 1998 |

|

RU2145152C1 |

| Прибор для очистки паром от сажи дымогарных трубок в паровозных котлах | 1913 |

|

SU95A1 |

| ЕР 0693830 А2, 24.01.1996 | |||

| Устройство для безопилочного резаниядРЕВЕСиНы пРОВОлОКОй | 1979 |

|

SU827293A1 |

Авторы

Даты

2004-07-27—Публикация

2002-10-18—Подача