Предлагаемое изобретение относится к области электронной техники и может быть использовано для преобразования тока в частоту в устройствах с высокими требованиями к надежности и точности преобразования.

Известен преобразователь напряжения в частоту, см., например, описанный в [1], содержащий последовательно соединенные интегратор, первый компаратор, первый одновибратор, охваченные отрицательной обратной связью на первый вход интегратора, второй вход интегратора соединен со входом интегрального преобразователя, а выход первого одновибратора с первым входом коммутатора.

Недостаток известного устройства состоит в том, что оно не позволяет проводить компенсации нулевого сигнала (сигнала смещения) как самого преобразователя, так и сигнала смещения датчика тока, что во многих случаях не позволяет получить требуемой точности преобразования.

Наиболее близким техническим решением к предлагаемому является интегральный преобразователь [2], содержащий интегратор, первый и второй компараторы, первый и второй одновибраторы, коммутатор, реверсивный счетчик, преобразователь код - напряжение.

Недостаток этого устройства состоит в том, что оно имеет большое время переходного процесса, в течение которого достигается требуемая точность компенсации (сигнала смещения) как самого преобразователя, так и сигнала смещения датчика тока.

Задача изобретения - снижение времени переходного процесса, в течение которого достигается требуемая точность компенсации (сигнала смещения) как самого преобразователя, так и сигнала смещения датчика тока.

Эта задача достигается тем, что в интегральный преобразователь, содержащий интегратор, первый и второй компараторы, первый и второй одновибраторы, коммутатор и реверсивный счетчик, суммирующий и вычитающий входы которого соединены с соответствующими выходами коммутатора, вход управления которого подключен к шине управляющего сигнала, а вход интегрального преобразователя соединен с входом интегратора, выход которого подключен к входам первого и второго компараторов, соединенных своими выходами соответственно с входами первого и второго одновибраторов, выходы которых подключены соответственно к инвертирующему и к неинвертирующему входам интегратора, дополнительно введены первый, второй и третий элементы ИЛИ, первый, второй, третий и четвертый элементы И, генератор импульсов, первый и второй счетчики импульсов, формирователь импульсов и n каналов управления, каждый из которых содержит первый, второй и третий элементы И канала управления и элемент ИЛИ, первый и второй входы которого соединены соответственно с выходом первого и второго элементов И канала управления, а выход элемента ИЛИ подключен к первому входу третьего элемента И канала управления, при этом выходы третьего элемента И первого, второго, ... и n-го каналов управления соединены соответственно с первым, вторым, ... и n-м входами третьего элемента ИЛИ, первые входы первого элемента И первого, второго, ... и n-го каналов управления соединены соответственно с неинверсным выходом первого, второго, ... и n-го разрядов реверсивного счетчика, инверсные выходы которого подключены соответственно к первым входам второго элемента И первого, второго, ... и n-го каналов управления, вторые входы которых соединены с неинверсным выходом (n+1)-го разряда реверсивного счетчика и первым входом первого элемента И, вторые входы первого элемента И первого, второго, ... и n-го каналов управления соединены с инверсным выходом (n + 1)-го разряда реверсивного счетчика и первым входом второго элемента И, вторые входы третьего элемента И первого, второго, ... и n-го каналов управления подключены соответственно к первому, второму, ... и n-му выходам формирователя импульсов, первый вход которого соединен с выходом третьего элемента И, а второй вход формирователя импульсов соединен с выходом генератора импульсов и с С-входом первого счетчика импульсов, выход которого подключен к второму входу третьего элемента И и первому входу четвертого элемента И, второй вход которого соединен с шиной управляющего сигнала, а третий вход подключен к инверсному выходу второго счетчика импульсов, С-вход которого соединен с выходом четвертого элемента И, а неинверсный выход второго счетчика импульсов подключен к первому входу третьего элемента И, выход третьего элемента ИЛИ соединен со вторыми входами первого и второго элементов И, выходы которых подключены соответственно к вторым входам первого и второго элементов ИЛИ, первые входы которых соединены соответственно с выходами первого и второго одновибраторов, а выходы первого и второго элементов ИЛИ подключены к соответствующим входам коммутатора и являются выходом интегрального преобразователя.

Формирователь импульсов содержит третий счетчик импульсов, первый, второй, ... и n-й частотные формирователи, каждый из которых включает в себя последовательно соединенные триггер и элемент И, и формирователь тактов, содержащий счетчик Джонсона и первый, второй, ... и (n+1)-й элементы И, первые входы которых соединены соответственно с первым, вторым, ... и (n+1)-м выходами счетчика Джонсона, С-вход которого подключен к второму входу формирователя импульсов и вторым входам первого, второго, и (n+1)-го элементов И, выходы которых являются первым, вторым, ... и (n+1)-м выходами формирователя тактов, при этом С-вход третьего счетчика импульсов соединен с первым входом формирователя тактов, а выходы первого, второго, ... и n-го разрядов третьего счетчика импульсов подключены к С-входам триггеров первого, второго, ... и n-го частотных формирователей, R-входы которых соединены соответственно с вторым, третьим, ... и (n+1)-м выходами формирователя тактов, вторые входы элемента И первого, второго, ... и n-го частотных формирователей подключены соответственно к первому, второму, ... и n-му выходам формирователя тактов, а выходы элементов И первого, второго, ... и n-го частотных формирователей являются первым, вторым, ... и n-м выходами формирователя импульсов.

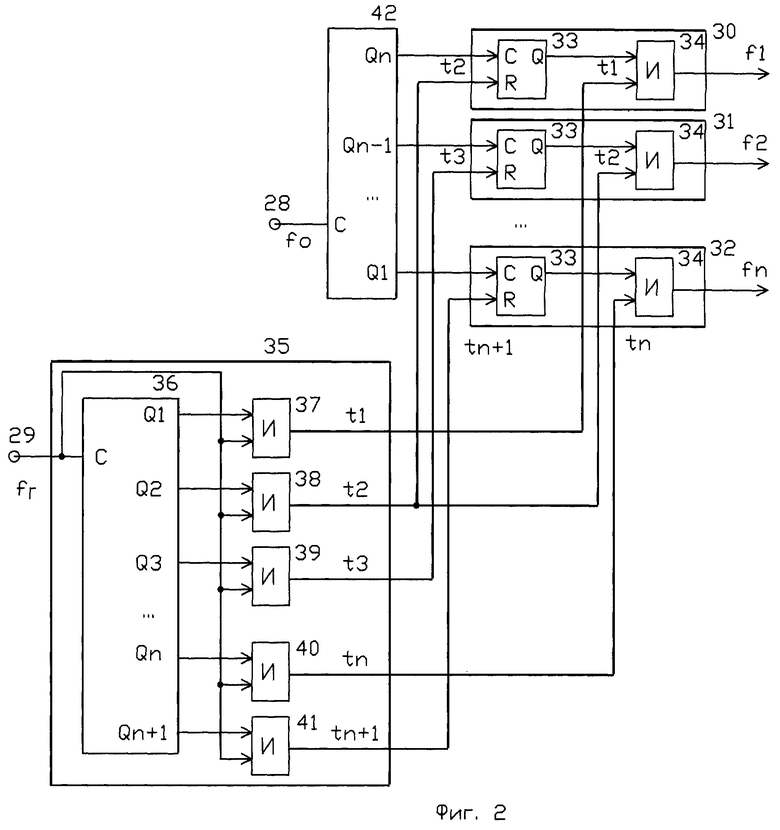

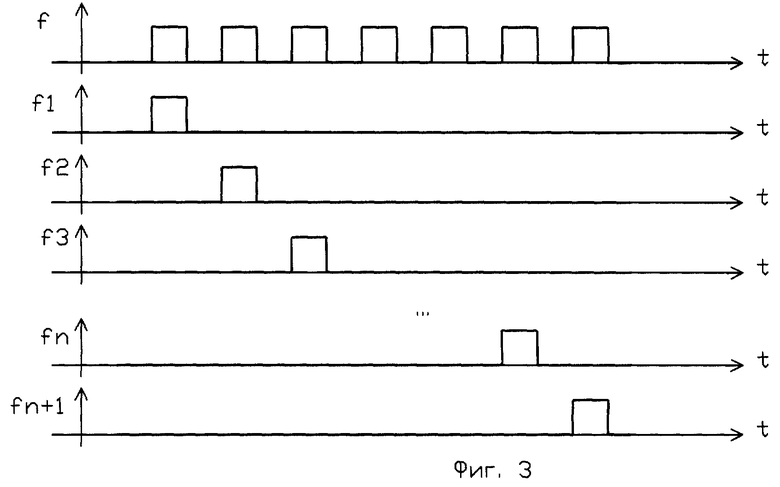

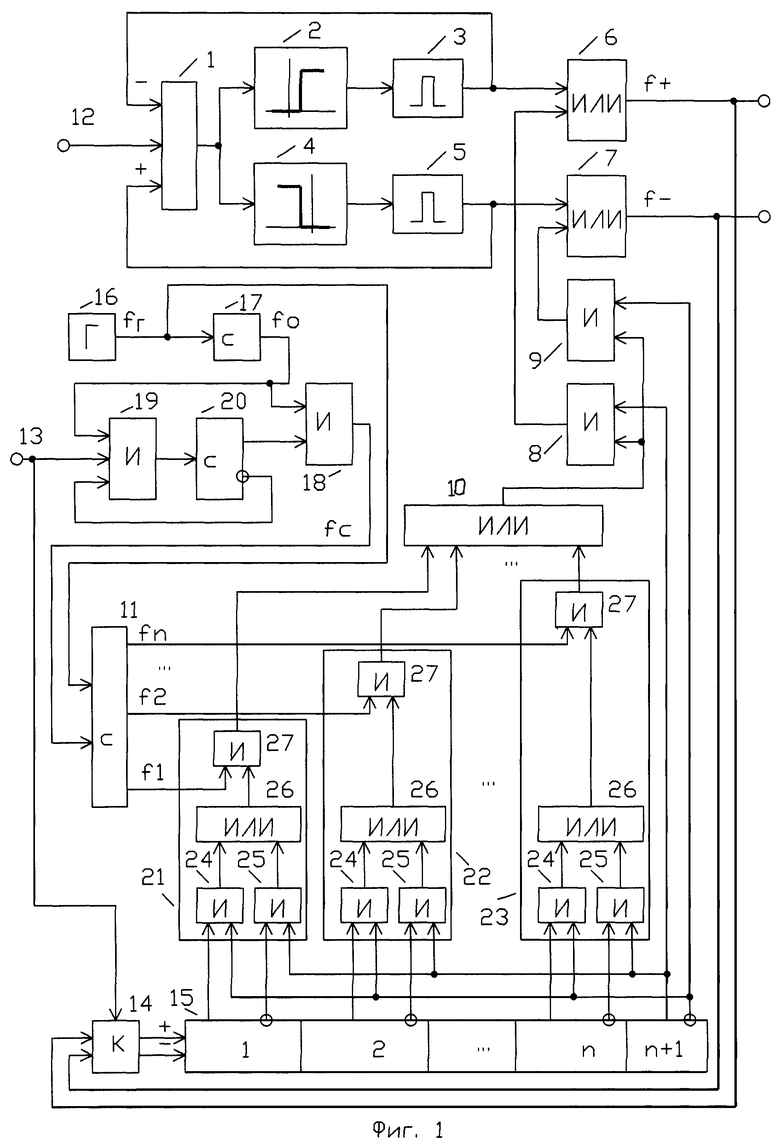

На фиг.1 приведена блок-схема интегрального преобразователя, на фиг.2 - схема формирователя импульсов, на фиг.3 - временная диаграмма формирования тактов.

На фиг.1: 1 - интегратор, 2 - первый компаратор, 3 - первый одновибратор, 4 - второй компаратор, 5 - второй одновибратор, 6 - первый элемент ИЛИ, 7 - второй элемент ИЛИ, 8 - первый элемент И, 9 - второй элемент И, 10 - третий элемент ИЛИ, 11 - формирователь импульсов, 12 - вход интегрального преобразователя, 13 - шина управляющего сигнала, 14 - коммутатор, 15 - реверсивный счетчик, 16 - генератор импульсов, 17 - первый счетчик импульсов, 18 - третий элемент И, 19 - четвертый элемент И, 20 - второй счетчик импульсов, 21 - первый канал управления, 22 - второй канал управления, 23 – n-й канал управления, 24 - первый элемент И канала управления, 25 - второй элемент И канала управления 26 - элемент ИЛИ канала управления, 27 - третий элемент И канала управления.

На фиг.2: 28 - первый вход формирователя импульсов, 29 - второй вход формирователя импульсов, 30 - первый частотный формирователь, 31 - второй частотный формирователь, 32 – n-й частотный формирователь, 33 - триггер, 34 - элемент И частотного формирователя, 35 - формирователь тактов, 36 - счетчик Джонсона, 37 - первый элемент И формирователя тактов, 38 - второй элемент И формирователя тактов, 39 - третий элемент И формирователя тактов, 40 – n-й элемент И формирователя тактов, 41 (n + 1)-й элемент И формирователя тактов, 42 - третий счетчик импульсов.

На фиг.3: fг - выходной сигнал генератора импульсов, t1, t2, t3, ... t(n=1) - выходные импульсы формирователя тактов.

В интегральном преобразователе (фиг.1) выход интегратора 1 соединен с входами первого 2 и второго 4 компараторов, выходы которых соединены соответственно с входами первого 3 и второго 5 одновибраторов. Выход первого одновибратора 3 соединен с инвертирующим входом интегратора 1 и первым входом первого элемента ИЛИ 6, второй вход которого подключен к выходу первого элемента И 8. Выход второго одновибратора 5 соединен с неинвертирующим входом интегратора 1 и первым входом второго элемента ИЛИ 7, второй вход которого подключен к выходу второго элемента И 9. Выход генератора импульсов 16 соединен с вторым входом формирователя импульсов 11 и С-входом первого счетчика импульсов 17, выход которого подключен ко второму входу третьего элемента И 18 и первому входу четвертого элемента И 19, второй вход которого соединен с шиной управляющего сигнала 13 и входом управления коммутатора 14. Третий вход четвертого элемента И 19 соединен с инверсным выходом второго счетчика 20, С-вход которого соединен с выходом четвертого элемента И 19. Неинверсный выход второго счетчика 20 подключен к первому входу третьего элемента И 18, выход которого соединен с первым входом формирователя импульсов 11, первый, второй, ... и n-й выходы которого соединены соответственно с вторыми входами третьего элемента И 27 первого 21, второго 22, ... и n-го 23 каналов управления, выходы которых подключены соответственно к первому, второму, ... и n-му входам третьего элемента ИЛИ 10, выход которого соединен со вторыми входами первого 8 и второго 9 элементов И. Первый вход первого элемента И 8 соединен с неинверсным выходом (n+1)-го разряда реверсивного счетчика 15 и вторыми входами первого элемента И 24 первого 21, второго 22, ... и (n+1)-го 23 каналов управления. Первый вход второго элемента И 9 соединен с инверсным выходом (n+1)-го разряда реверсивного счетчика 15 и вторыми входами второго элемента И 25 первого 21, второго 22, ... и (n+1)-го 23 каналов управления. Неинверсные выходы первого, второго, ... и n-го разрядов реверсивного счетчика 15 соединены соответственно с первыми входами первого элемента И 24 первого 21, второго 22, ... и n-го 23 каналов управления. Инверсные выходы первого, второго, ... и n-го разрядов реверсивного счетчика 15 соединены соответственно с первыми входами второго элемента И 25 первого 21, второго 22, ... и n-го 23 каналов управления. В каждом канале управления выходы первого 24 и второго 25 элементов И соединены соответственно с первым и вторым входами элемента ИЛИ 26, выход которого подключен к первому входу третьего элемента И 27. Суммирующий и вычитающий входы реверсивного счетчика 15 соединены с соответствующими входами коммутатора 14, входы которого подключены к выходам первого 6 и второго 7 элементов ИЛИ.

В схеме формирователя импульсов (фиг.2) первый вход 28 соединен с С-входом третьего счетчика импульсов 42, выходы n-го, (n - 1), ... и первого разрядов которого подключены соответственно к С-входам триггера 33 первого 30, второго 31, ... n-го 32 частотных формирователей. Второй вход 29 формирователя импульсов соединен с С-входом счетчика Джонсона 36 и вторыми входами первого 37, второго 38, третьего 39, ... n-го 40 и (n+1)-го 41 элементов И, выходы которых являются выходами формирователя тактов 35. Каждый частотный формирователь содержит последовательно соединенные триггер 33 и элемент И 34. R-входы триггера 33 первого 30, второго 31, ... и n-го 32 частотных формирователей соединены соответственно с вторым, третьим, ... и (n+1)-м выходами формирователя тактов 35. Вторые входы элементов И 34 первого 30, второго 31, ... и n-го 32 частотных формирователей соединены соответственно с первым, вторым, ... и n-м выходами формирователя тактов 35. Выходы элементов И 34 первого 30, второго 31 ... и n-го 32 частотных формирователей являются первым, вторым, ... и n-м выходами формирователя импульсов.

Преобразователь работает следующим образом. Ток, поступающий на вход 12, попадает на вход интегратора 1, вызывая рост напряжения на его выходе. По достижении порогового уровня первого 2 (или второго 4) компаратора последний срабатывает и на его выходе появится высокий уровень, который поступит на вход первого 3 (или второго 5) одновибратора. В результате этого одновибратор сформирует импульс строго определенной длительности и амплитуды. Этот импульс поступит на инвертирующий (или неинвертирующий) вход интегратора 1 и уменьшит уровень напряжения на выходе последнего. Одновременно этот импульс поступит на один из выходов интегрального преобразователя, проходя через первый 6 (или второй 7) элемент ИЛИ.

При необходимости проведения компенсации сигнала смещения (изменяющегося от температуры, от включения к включению и т. д.) как самого преобразователя, так и датчика тока необходимо подать на шину управляющего сигнала 13 разрешающий уровень. Этот уровень поступит на управляющий вход коммутатора 14 и разрешит прохождение импульсов с выхода первого 6 и второго 7 элементов ИЛИ на суммирующий или вычитающий входы реверсивного счетчика 11. В исходном состоянии первый 17 и второй 20 счетчики импульсов обнулены и выходной сигнал UH на неинвертирующем выходе второго счетчика импульсов 20 имеет низкий уровень (UH=0), а на его инвертирующем выходе высокий уровень (UИ=1). В этом случае сигналы с выхода первого счетчика импульсов 17 не проходят на первый вход формирователя импульсов 11, так как четвертый элемент И 18 блокирует их прохождение. Одновременно сигналы с выхода первого счетчика импульсов 17 через третий элемент И 19 поступают на С-вход второго счетчика импульсов 20. Первый счетчик 17 осуществляет деление импульсов генератора 16 частотой fГ, преобразуя их в частоту f0. При переходе последнего разряда второго счетчика импульсов 20 в единичное состояние (выходные сигналы UH = 1, UИ =0) третий элемент И 19 блокирует прохождение сигналов с выхода первого счетчика импульсов 17 на С-вход второго счетчика импульсов 20, а четвертый элемент И 18 разрешает прохождение этих сигналов на первый вход формирователя импульсов 11.

Пусть второй счетчик импульсов 20 и реверсивный счетчик 15 имеют (n + 1) разряд. Время Т0 от момента поступления управляющего сигнала на шину 13 до появления сигнала UH = 1 будет равно 2n/f0. В течение этого времени на вход реверсивного счетчика 15 будут поступать импульсы с выхода интегрального преобразователя f+, соответствующие, например, положительному сигналу смещения. Пусть за время Т0 на вход реверсивного счетчика 15 поступило N импульсов. Для осуществления полной компенсации сигнала смещения необходимо в течение каждого интервала времени Т0 формировать на выходе интегрального преобразователя N импульсов, соответствующих отрицательному входному сигналу.

Пусть сигнал смещения таков, что частота выходного сигнала интегрального преобразователя равна fсм. За время Т0 на вход реверсивного счетчика поступит число импульсов N = fсм Т0. Если максимальное значение Тсм, соответствующее максимально возможному сигналу смещения, равно fсм max, то за время Т0 на вход реверсивного счетчика 11 поступит число импульсов Nмах = fсм.мах Т0. Выберем Т0 таким, чтобы Nмах = 2n-1. В этом случае частоту f0 первого счетчика импульсов 17 зададим как

f0=(2n)/T0. (1)

Если за время Т0 на вход реверсивного счетчика 15 поступает N импульсов, то частота fсм будет равна

fсм=N/Т0. (2)

Рассмотрим М более подробно работу интегрального преобразователя. По истечении времени Т0 на выходе реверсивного счетчика 15 формируется код, соответствующий положительному числу N, при этом (n+1)-й (знаковый) разряд этого счетчика имеет состояние: неинвертирующий выход имеет низкий уровень UPH=0, инвертирующий выход имеет высокий уровень UРИ=1. Сигнал UPH=1 разрешает прохождение выходных сигналов первого, второго, ... и n-го разрядов реверсивного счетчика 15 через первые элементы И 24 на вход элементов ИЛИ 26 первого 21, второго 22, ... и n-го 23 каналов управления. Если состояние i-го (i=1, 2, ... n) разряда реверсивного счетчика 15 единичное (Ui=1, Ui - выходной сигнал i-го разряда), то этот сигнал с выхода соответствующего элемента ИЛИ 26 разрешает прохождение выходных сигналов формирователя импульсов 11 через третий элемент И 27 на вход третьего элемента ИЛИ 10, а с его выхода на вторые входы первого 8 и второго элементов И.

Рассмотрим работу формирователя импульсов 11 (фиг.2). При поступлении на первый вход 28 импульсов частотой f0 выходные сигналы Q1, Q2, ... Qn первого, второго, ... и n-го разрядов третьего счетчика импульсов 42 будут представлять собой последовательности импульсов соответственно частотой fci, причем

fci=f0/2i. (3)

При поступлении на второй вход 28 импульсов частотой fг на выходах счетчика Джонсона 36 поочередно на каждом из (n+1) выходов формируются импульсы длительностью 1/fг. На выходах первого 37, второго 38, ... и (n+1)-го 41 элементов И формирователя тактов формируются соответственно импульсы t1, t2, ... t(n+1) согласно временной диаграмме фиг.3.

Частотный формирователь 30, 31, 32 работает следующим образом. Импульсы с выхода третьего счетчика импульсов 42, поступая на С-вход триггера 33, переводят его в единичное состояние, разрешая тем самым похождение импульсов ti с выхода формирователя тактов 35 через элемент И 34 на выход частотного формирователя. Импульс ti+1 с выхода формирователя тактов 35, поступая на R-вход триггера 33, устанавливает его в нулевое состояние. Таким образом, выходные сигналы формирователя импульсов f1, f2, ... fn представляют собой не совпадающие во времени последовательности импульсов, частота следования которых определяется частотой переключения соответственно n-го, (n-1)-го, ... и первого разрядов третьего счетчика импульсов 42.

Определим число импульсов, поступающих на входы третьего элемента ИЛИ 10 за время Т0. Пусть число n=10, а число импульсов N, поступивших на вход реверсивного счетчика 15 за время Т0, равно 515. В этом случае в реверсивном счетчике импульсов 15 будет записан код, в котором первый, второй и n-й разряды имеют единичное значение, а неинверсные выходные сигналы первого, второго и n-го разрядов реверсивного счетчика импульсов 15 будут иметь высокий уровень. Эти выходные сигналы через первый элемент И 24, элемент ИЛИ 26 поступают на вход третьего элемента И 27 первого 21, второго 22 и n-го каналов управления, разрешая прохождение импульсов f1, f2 и fn соответственно с первого, второго и n-го выходов формирователя импульсов 11 на входы элемента ИЛИ 10. Частота следования импульсов f1=f0/210, f2=f0/29, fn=f0/2. С учетом (1) за время Т0 на вход третьего элемента ИЛИ поступит (1+2+512)=515 импульсов. Так как число N положительное, то на инверсном выходе (n+1)-го разряда реверсивного счетчика 15 будет высокий потенциал, который разрешает прохождение импульсов с выхода третьего элемента ИЛИ 10 через второй элемент И 9 на второй вход второго элемента ИЛИ 7, а с его выхода на выход f- интегрального преобразователя, определяемый как алгебраическая сумма импульсов f+ и f- за некоторый промежуток времени, будет близок к нулю. Иначе говоря, с момента времени Т0 интегральным преобразователем осуществляется полная компенсация сигнала смещения. В случае отрицательного сигнала смещения на вычитающий вход реверсивного счетчика 15 в течение времени Т0 поступит N импульсов и код этого счетчика соответствует отрицательному числу. В этом случае выходной сигнал на неинверсном выходе знакового разряда реверсивного счетчика 15 U+=1 (высокий уровень), а на инверсном выходе U-=0 (низкий уровень). Сигнал U+=1 разрешает прохождение импульсов с выхода третьего элемента ИЛИ 10 через первый элемент И 8 на вход первого элемента ИЛИ 6, с выхода которого формируются импульсы f+ интегрального преобразователя. Одновременно сигнал U+=1 разрешает прохождение сигналов с инверсных выходов разрядов реверсивного счетчика 15 через вторые элементы И 25 на вторые входы элементов ИЛИ 26 первого 21, второго 22, ... и n-го 23 каналов управления. Сигналы с инверсных выходов разрядов реверсивного счетчика 15 соответствуют модулю числа N. Как и в случае положительного смещения, выходной сигнал интегрального преобразователя, определяемый как алгебраическая сумма импульсов f+ и f- за некоторый промежуток времени, будет близок к нулю.

По сравнению с известным интегральным преобразователем [2] предлагаемое обеспечивает существенно меньшее время переходного процесса. Предположим, что входной сигнал изменяется в пределах ±10 мА, а сигнал смещения составляет 1см.мах=±0,1 мА. Предположим также, что интегральный преобразователь должен скомпенсировать сигнал смещения до уровня А=0,0001 мА.

В известном устройстве в процессе проведения компенсации сигнала смещения каждый импульс, поступающий на вход реверсивного счетчика, изменяет входной сигнал на величину Δ. Определим время переходного процесса Тп в известном устройстве при проведении компенсации сигнала lсм.мах. Учитывая, что отношение lсм.мах/Δ=1000, число разрядов реверсивного счетчика n = 10. Пусть вхоя импульсов ТΔ = 100с. Время переходного процесса Тп в известном устройстведному сигналу 10 мА соответствует частота выходного сигнала 1000 Гц. В этом случае при входном сигнале Δ=0,0001 мА частота выходного сигнала будет равна 0,01 Гц, что соответствует периоду следовани можно определить в виде

Тп=ТΔ(1+1/2+1/3+1/4+...+1/1000). (4)

Это время Тп ≅ 650 с. При проведении компенсации каждый импульс на выходе интегрального преобразователя, поступающий на вход реверсивного счетчика, уменьшает сигнал на входе интегратора на величину Δ, что приводит к уменьшению времени достижения выходным сигналом интегратора 1 порога срабатывания компаратора, что и отражает равенство (4).

Выберем в предлагаемом решении Т0=ТΔ. Это время и определяет время переходного процесса Тп=100 с предлагаемого преобразователя, что непосредственно следует из описания. Таким образом, время переходного процесса предлагаемого интегрального преобразователя в несколько раз меньше времени переходного процесса известного устройства. Снижение времени переходного процесса компенсации сигнала смещения имеет существенное значение, например, при использовании интегрального преобразователя в динамических системах, например, в системах управления движением космических аппаратов в каналах преобразования сигналов акселерометров, где время компенсации (время отключения исполнительных двигателей) весьма ограничено.

Предлагаемая совокупность признаков в рассмотренных авторами решениях не встречалась для решения поставленной задачи и не следует явным образом из уровня техники, что позволяет сделать вывод о соответствии технического решения критериям "новизна" и "изобретательский уровень". В качестве элементов для реализации устройства можно использовать стандартные схемы интегратора, компаратора, генератора, одновибратора и логические элементы цифровых микросхем любых серий, например, 564 и т. д.

Источники информации

1. Авторское свидетельство СССР N 921080, кл. Н 03 К 13/20, 24.07.81. Преобразователь напряжения в частоту.

2. Патент Российской Федерации N 2138826, МПК6 G 01 R 19/252, 27.09.99.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2240569C1 |

| СПОСОБ ЧАСТОТНО-ИМПУЛЬСНОГО ПРЕОБРАЗОВАНИЯ НЕПРЕРЫВНОГО СИГНАЛА И ИНТЕГРАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2001 |

|

RU2199757C1 |

| Устройство для измерения линейных перемещений | 1981 |

|

SU1013734A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1748253A1 |

| ПРЕЦИЗИОННЫЙ ЧАСТОТНО-ИМПУЛЬСНЫЙ ИЗМЕРИТЕЛЬ | 2001 |

|

RU2208797C1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Частотный аналого-цифровой преобразователь | 1989 |

|

SU1702528A1 |

| Аналого-цифровой преобразователь с преобразованием напряжения в частоту | 1989 |

|

SU1651381A1 |

| Аналого-цифровой преобразователь с частотным преобразованием | 1988 |

|

SU1547066A1 |

Изобретение относится к электронной технике и предназначено для преобразования в частоту сигналов от датчиков тока, имеющих непостоянную нулевую составляющую, изменяющуюся от многих факторов. Преобразователь содержит интегратор, два компаратора, два одновибратора, счетчики, логические элементы, коммутатор и генератор импульсов. Работа преобразователя основана на интегрировании входного сигнала и сбросе интегратора при достижении выходным сигналом интегратора заданного уровня. Генератор импульсов, счетчики, коммутатор и логические элементы образуют схему компенсации сигнала смещения преобразователя или датчика тока. Изобретение направлено на уменьшение времени переходного процесса при компенсации сигнала смещения преобразователя или датчика тока для использования преобразователя в динамических системах. 1 з.п. ф-лы, 3 ил.

| ИНТЕГРАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1998 |

|

RU2138826C1 |

| DE 19520315 C1, 14.08.1996 | |||

| Способ установки выводных трубок и переставное приспособление для его осуществления | 1961 |

|

SU148296A1 |

| Преобразователь напряжения в частоту | 1980 |

|

SU921080A1 |

Авторы

Даты

2004-11-20—Публикация

2003-04-11—Подача