Изобретение относится к схемам защиты, в частности к схемам защиты потенциального типа, предназначено для защиты ключевого транзистора при коротком замыкании на общую шину или уменьшении сопротивления нагрузки ниже определенной величины и может быть использовано для защиты ключевого транзистора, управляющего электромагнитом или клапаном в блоке управления экономайзером принудительного холостого хода автомобиля.

Известна схема защиты мощного транзистора - аналог, основу которой составляет компаратор, выполненный на дифференциальном каскаде, на один вход которого подается опорное напряжение, на другой - напряжение с токового датчика [Патент Великобритании №2056808, кл. Н 03 К 17/08; F 02 D 11/00. Заявлено 13.08.1980. Опубликовано 18.03.1981].

Недостатком аналога являются невозможность восстановления его работоспособности после снятия режима перегрузки, а также наличие токового датчика, для включения которого требуется дополнительный вывод, и наличие трех конденсаторов, которые выполняются в виде внешних элементов при изготовлении схемы в интегральном исполнении.

Известна другая схема защиты от короткого замыкания потенциального типа - аналог, основу которой составляют два транзистора, второй из которых содержит диод Шоттки между коллектором и базой, которые параллельно формируют входной сигнал в базу переключающего транзистора и в базу выходного транзистора соответственно. При этом первый транзистор формирует сигнал в базу переключающего транзистора с задержкой относительно входного сигнала в базу выходного транзистора с целью устранения ложного срабатывания при запуске или при низком выходном напряжении во время его нарастания. Эта задержка осуществляется посредством более медленного выхода первого транзистора из режима насыщения по сравнению с транзистором, содержащем диод Шоттки [Патент США №4291357, кл. Н 02 Н 9/02. Заявлено 27.12.1979. Опубликовано 22.09.1981].

Недостатком аналога является невозможность регулировки длительности задержки, необходимой при применении ключевых транзисторов с различными параметрами.

Известна схема защиты - прототип, содержащая первый транзистор, эмиттер которого подключен к общей шине, а коллектор через второй резистор подключен к базе второго транзистора и к третьему резистору, второй вывод которого подключен к источнику питания и одновременно к эмиттеру второго транзистора, коллектор которого образует выходную шину, первый резистор, первый вывод которого соединен с базой первого транзистора и одновременно подключен к первому выводу седьмого резистора, второй вывод которого соединен с общей шиной, и через последовательно соединенные восьмой и девятый резисторы к коллектору второго транзистора и выходной шине, а второй вывод которого является точкой соединения пятого резистора, второй вывод которого подключен к общей шине, четвертого резистора, второй вывод которого одновременно подключен к базе четвертого транзистора и коллектору третьего транзистора, эмиттер которого образует входную шину, и эмиттера четвертого транзистора, коллектор которого подключен одновременно к базе третьего транзистора, к первому конденсатору, второй вывод которого соединен с общей шиной, и к шестому резистору, второй вывод которого соединен с положительным выводом источника опорного напряжения, отрицательный вывод которого соединен с общей шиной, второй конденсатор, который подключен между точкой соединения восьмого и девятого резисторов и общей шиной. В этом устройстве сигналом для срабатывания является потенциал коллектора второго транзистора. При коротком замыкании на общую шину этот ключевой транзистор входит в активный режим на время заряда первого конденсатора [Чижков Ю.П., Акимов С.В. Электрооборудование автомобилей. - М.: За рулем, 1999. -384 с. (с.219, рис.7.5 и с.221, рис.7.7)].

Недостатком прототипа является наличие двух конденсаторов, которые при его изготовлении в интегральном исполнении могут быть выполнены только в виде внешних элементов, и потребуется дополнительно два вывода. Общее число выводов будет составлять три.

Технический результат заключается в уменьшении числа выводов схемы защиты при ее изготовлении в интегральном исполнении, а также в возможности регулировки времени задержки включения схемы защиты. Общее число выводов будет составлять два.

Сущность изобретения заключается в том, что в устройство, содержащее первый транзистор, эмиттер которого подключен к общей шине, а коллектор через второй резистор подключен к базе второго транзистора и к третьему резистору, второй вывод которого подключен к источнику питания и одновременно к эмиттеру второго транзистора, коллектор которого образует выходную шину, первый резистор, первый вывод которого соединен с базой первого транзистора, введены динамический D-триггер, вход R которого подключен к первой входной шине, а инверсный выход  соединен со входом S мультиплексора, первый вход D1 которого подключен ко второй входной шине, второй вход D2 подключен через первый элемент задержки к третьей входной шине и входу С динамического D-триггера, прямой выход Q соединен со входом первого блока согласования, а инверсный выход

соединен со входом S мультиплексора, первый вход D1 которого подключен ко второй входной шине, второй вход D2 подключен через первый элемент задержки к третьей входной шине и входу С динамического D-триггера, прямой выход Q соединен со входом первого блока согласования, а инверсный выход  через второй элемент задержки соединен со входом второго блока согласования, первый источник тока, положительный вывод которого соединен с источником стабилизированного напряжения, а отрицательный вывод соединен с первым выводом первого электронного ключа, управляемый вывод которого соединен с выходом первого блока согласования, а второй вывод через четвертый резистор подключен к общей шине и является точкой соединения пятого резистора, второй вывод которого подключен к второму выводу первого резистора и одновременно к коллектору шестого транзистора, и шестого резистора, второй вывод которого подключен одновременно к выходу второго блока согласования и базе третьего транзистора, эмиттер которого соединен с общей шиной, а коллектор - с управляемым выводом второго электронного ключа, первый вывод которого соединен с отрицательным выводом второго источника тока, положительный вывод которого соединен с источником питания, а второй вывод является точкой соединения эмиттеров четвертого и пятого транзисторов, источник опорного напряжения, отрицательный вывод которого соединен с общей шиной, а положительный вывод соединен с базой четвертого транзистора, коллектор которого подключен к общей шине, седьмой транзистор, эмиттер которого подключен к общей шине, коллектор соединен с входом

через второй элемент задержки соединен со входом второго блока согласования, первый источник тока, положительный вывод которого соединен с источником стабилизированного напряжения, а отрицательный вывод соединен с первым выводом первого электронного ключа, управляемый вывод которого соединен с выходом первого блока согласования, а второй вывод через четвертый резистор подключен к общей шине и является точкой соединения пятого резистора, второй вывод которого подключен к второму выводу первого резистора и одновременно к коллектору шестого транзистора, и шестого резистора, второй вывод которого подключен одновременно к выходу второго блока согласования и базе третьего транзистора, эмиттер которого соединен с общей шиной, а коллектор - с управляемым выводом второго электронного ключа, первый вывод которого соединен с отрицательным выводом второго источника тока, положительный вывод которого соединен с источником питания, а второй вывод является точкой соединения эмиттеров четвертого и пятого транзисторов, источник опорного напряжения, отрицательный вывод которого соединен с общей шиной, а положительный вывод соединен с базой четвертого транзистора, коллектор которого подключен к общей шине, седьмой транзистор, эмиттер которого подключен к общей шине, коллектор соединен с входом  динамического D-триггера, а база подключена к девятому резистору, второй вывод которого является точкой соединения седьмого резистора, второй вывод которого подключен к общей шине, восьмого резистора, второй вывод которого подключен к базе шестого транзистора, эмиттер которого подключен к общей шине, и коллектора пятого транзистора, база которого через десятый резистор подключена к выходной шине.

динамического D-триггера, а база подключена к девятому резистору, второй вывод которого является точкой соединения седьмого резистора, второй вывод которого подключен к общей шине, восьмого резистора, второй вывод которого подключен к базе шестого транзистора, эмиттер которого подключен к общей шине, и коллектора пятого транзистора, база которого через десятый резистор подключена к выходной шине.

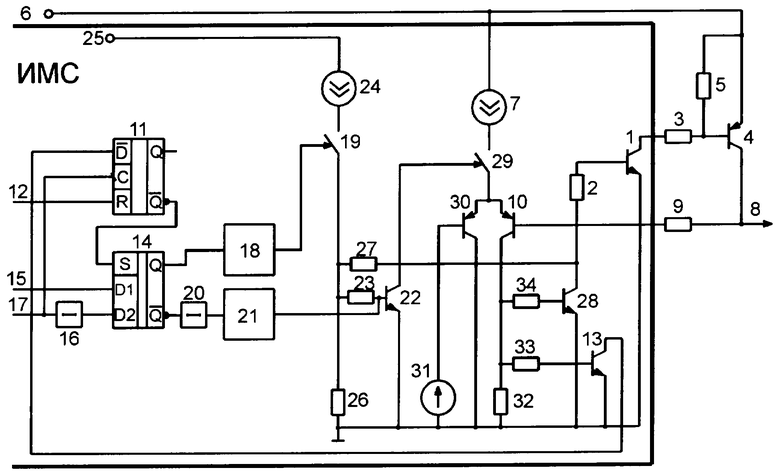

На чертеже приведена принципиальная электрическая схема предложенной схемы защиты ключевого транзистора. Устройство содержит первый транзистор 1, база которого подключена к первому выводу первого резистора 2, эмиттер которого подключен к общей шине, а коллектор через второй резистор 3 подключен к базе второго транзистора 4 и к третьему резистору 5. Второй вывод третьего резистора 5 подключен к источнику питания 6, к положительному выводу второго источника тока 7 и к эмиттеру второго транзистора 4. Коллектор второго транзистора 4 образует выходную шину 8 и через десятый резистор 9 подключен к базе пятого транзистора 10. Вход R динамического D-триггера 11 подключен к первой входной шине 12, вход  соединен с коллектором седьмого транзистора 13, а инверсный выход

соединен с коллектором седьмого транзистора 13, а инверсный выход  соединен с входом S мультиплексора 14. Первый вход D1 мультиплексора 14 подключен ко второй входной шине 15, второй вход D2 подключен через первый элемент задержки 16 к третьей входной шине 17 и к входу С динамического D-триггера 11. Прямой выход Q мультиплексора 14 через первый блок согласования 18 подключен к управляемому выводу первого электронного ключа 19, а инверсный выход

соединен с входом S мультиплексора 14. Первый вход D1 мультиплексора 14 подключен ко второй входной шине 15, второй вход D2 подключен через первый элемент задержки 16 к третьей входной шине 17 и к входу С динамического D-триггера 11. Прямой выход Q мультиплексора 14 через первый блок согласования 18 подключен к управляемому выводу первого электронного ключа 19, а инверсный выход  через второй элемент задержки 20 и второй блок согласования 21 подключен к базе третьего транзистора 22 и к первому выводу шестого резистора 23. Положительный вывод первого источника тока 24 соединен с источником стабилизированного напряжения 25, а отрицательный вывод соединен с первым выводом первого электронного ключа 19. Второй вывод первого электронного ключа 19 соединен со вторым выводом шестого резистора 23, через четвертый резистор 26 соединен с общей шиной и через пятый резистор 27 соединен со вторым выводом первого резистора 2 и коллектором шестого транзистора 28. Эмиттер третьего транзистора 22 соединен с общей шиной, а коллектор соединен с управляемым выводом второго электронного ключа 29. Первый вывод второго электронного ключа 29 соединен с отрицательным выводом второго источника тока 7, а второй вывод соединен с эмиттером четвертого транзистора 30 и эмиттером пятого транзистора 10. База четвертого транзистора 30 соединена с положительным выводом источника опорного напряжения 31, отрицательный вывод которого соединен с общей шиной, а его коллектор подключен к общей шине. Коллектор пятого транзистора 10 через седьмой резистор 32 соединен с общей шиной, через девятый резистор 33 соединен с базой седьмого транзистора 13 и через восьмой резистор 34 соединен с базой шестого транзистора 28. Эмиттеры шестого транзистора 28 и седьмого транзистора 13 подключены к общей шине.

через второй элемент задержки 20 и второй блок согласования 21 подключен к базе третьего транзистора 22 и к первому выводу шестого резистора 23. Положительный вывод первого источника тока 24 соединен с источником стабилизированного напряжения 25, а отрицательный вывод соединен с первым выводом первого электронного ключа 19. Второй вывод первого электронного ключа 19 соединен со вторым выводом шестого резистора 23, через четвертый резистор 26 соединен с общей шиной и через пятый резистор 27 соединен со вторым выводом первого резистора 2 и коллектором шестого транзистора 28. Эмиттер третьего транзистора 22 соединен с общей шиной, а коллектор соединен с управляемым выводом второго электронного ключа 29. Первый вывод второго электронного ключа 29 соединен с отрицательным выводом второго источника тока 7, а второй вывод соединен с эмиттером четвертого транзистора 30 и эмиттером пятого транзистора 10. База четвертого транзистора 30 соединена с положительным выводом источника опорного напряжения 31, отрицательный вывод которого соединен с общей шиной, а его коллектор подключен к общей шине. Коллектор пятого транзистора 10 через седьмой резистор 32 соединен с общей шиной, через девятый резистор 33 соединен с базой седьмого транзистора 13 и через восьмой резистор 34 соединен с базой шестого транзистора 28. Эмиттеры шестого транзистора 28 и седьмого транзистора 13 подключены к общей шине.

Схема защиты работает следующим образом. Основу схемы защиты составляет дифференциальный каскад на р-n-р транзисторах 30 и 10, работающий как компаратор напряжений, ток через который задается источником тока 7. На базе транзистора 30 источником опорного напряжения 31 устанавливается опорное напряжение. Это напряжение задает напряжение коллектор-эмиттер Vкэ транзистора 4, выше которого должна срабатывать схема защиты.

Выходами схемы защиты являются коллекторы транзисторов 28 и 13. Динамический D-триггер 11 анализирует сигнал на выходе схемы защиты и управляет мультиплексором 14. Мультиплексор 14 при высоком логическом уровне на входе выбора S пропускает на прямой выход Q сигнал с входной шины 15, на которую поступает входной сигнал, а при низком логическом уровне через элемент задержки 16 пропускает на прямой выход Q тактовые импульсы с входной шины 17. На вход R динамического D-триггера 11 с входной шины 12 подается сигнал начальной установки, представляющий собой высокий логический уровень с момента подачи питания в течение нескольких микросекунд и низкий логический уровень в течение остального времени до снятия питания со схемы. Если на прямом выходе Q мультиплексора 14 высокий логический уровень, то на выходе блока согласования 18 низкий потенциал. При этом на инверсном выходе  мультиплексора 14 низкий логический уровень, и на выходе блока согласования 21 высокий потенциал.

мультиплексора 14 низкий логический уровень, и на выходе блока согласования 21 высокий потенциал.

Источник тока 24 управляется электронным ключом 19 от блока согласования 18. Часть тока с источника тока 24 течет через резистор 26, часть через резисторы 27 и 2 втекает в базу транзистора 1 и открывает его. При этом открывается транзистор 4 и ток коллектора транзистора 1 ИМС ограничивается резистором 3. Ток коллектора транзистора 4 определяется сопротивлением нагрузки, подключаемой к выходной шине 8. Остальная часть тока с источника тока 24 через резистор 23 втекает в базу транзистора 22 и тем самым обеспечивает работоспособность схемы защиты.

При коротком замыкании коллектора транзистора 4 на общую шину или уменьшении сопротивления нагрузки ниже предельно допустимой величины транзистор 4, если он находился в режиме насыщения, переходит в активный режим. Напряжение коллектор-эмиттер Vкэ транзистора 4 увеличивается, и потенциал на базе транзистора 10 уменьшается. Когда потенциал на базе транзистора 10 станет меньше, чем потенциал на базе транзистора 30, транзистор 10 откроет транзисторы 28 и 13. Ток источника тока 24, который до этого втекал в базу транзистора 1, начинает протекать через транзистор 28. Транзистор 1 закрывается, что приводит к закрытию транзистора 4, предохраняя его от теплового разрушения чрезмерно большим током. После того, как откроется транзистор 13, на инверсный вход  динамического D-триггера 11 поступает низкий логический уровень. С приходом среза тактового импульса на вход С динамического D-триггера 11 на его инверсном выходе

динамического D-триггера 11 поступает низкий логический уровень. С приходом среза тактового импульса на вход С динамического D-триггера 11 на его инверсном выходе  , а следовательно, и на входе выбора S мультиплексора 14 устанавливается низкий логический уровень. Через элемент задержки 16 на прямой выход Q мультиплексора 14 проходит срез тактового импульса с входной шины 17, что приводит к тому, что транзистор 4 и схема защиты обесточиваются.

, а следовательно, и на входе выбора S мультиплексора 14 устанавливается низкий логический уровень. Через элемент задержки 16 на прямой выход Q мультиплексора 14 проходит срез тактового импульса с входной шины 17, что приводит к тому, что транзистор 4 и схема защиты обесточиваются.

С приходом фронта очередного тактового импульса с входной шины 17 на прямом выходе Q мультиплексора 14 устанавливается высокий логический уровень, и транзисторы 1 и 4 открываются. Через элемент задержки 20 открывается транзистор 22 и включает схему защиты.

Если после включения схемы защиты короткое замыкание коллектора транзистора 4 или сопротивление нагрузки ниже предельно допустимой величины сохраняется, то снова срабатывает схема защиты по выше описанному алгоритму.

Если после включения схемы защиты короткого замыкания коллектора транзистора 4 нет и сопротивление нагрузки не ниже предельно допустимой величины, то транзистор 4 успевает войти в режим насыщения. Транзисторы 10, 28 и 13 закрыты. С приходом среза тактового импульса на входе выбора S мультиплексора 14 устанавливается низкий логический уровень и на его прямой выход Q проходит входной сигнал с входной шины 15.

Таким образом, предложенное устройство осуществляет защиту транзистора 4 от короткого замыкания в нагрузке или от уменьшения сопротивления нагрузки, позволяет регулировать время задержки включения схемы защиты изменением числа инверторов в элементе задержки 20, а при его использовании в интегральном исполнении сократить число выводов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СОГЛАСОВАНИЯ НА ОСНОВЕ ОПТОЭЛЕКТРОННОГО КЛЮЧА | 2007 |

|

RU2369007C2 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ ОТ ВОЗДЕЙСТВИЯ РАДИАЦИИ | 2006 |

|

RU2322757C1 |

| Устройство для защиты нагрузки | 1979 |

|

SU904083A2 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ | 2002 |

|

RU2233022C1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ ПРИ ПОПАДАНИИ В НИХ ТЯЖЕЛЫХ ЗАРЯЖЕННЫХ ЧАСТИЦ | 2005 |

|

RU2305894C2 |

| Устройство для синхронизации воспроизведения цифровой магнитной записи | 1986 |

|

SU1337918A1 |

| Устройство электронной защиты | 1982 |

|

SU1136133A1 |

| Двухступенчатый стабилизатор напряжения постоянного тока | 1983 |

|

SU1188718A1 |

| ТРОИЧНЫЙ ТРИГГЕР | 2003 |

|

RU2237968C1 |

| Стабилизированный преобразователь постоянного напряжения в постоянное с защитой от перегрузок | 1985 |

|

SU1403042A1 |

Изобретение относится к схемам защиты интегральных схем, в частности к схемам защиты потенциального типа, предназначено для защиты ключевого транзистора при коротком замыкании на общую шину или уменьшении сопротивления нагрузки ниже определенной величины и может использоваться для защиты ключевого транзистора, управляющего электромагнитом или клапаном в блоке управления экономайзером принудительного холостого хода автомобиля. Технический результат - уменьшение числа выводов схемы защиты при ее изготовлении в интегральном исполнении и возможность регулировки времени задержки включения схемы защиты. Схема защиты ключевого транзистора содержит десять резисторов (2, 3, 5, 9, 23, 26, 27, 32-34), семь транзисторов (1, 4, 10, 13, 22, 28, 30), два электронных ключа (19, 29), два источника тока (7, 24), один источник опорного напряжения (31), один динамический D-триггер (11), один мультиплексор (14), два элемента задержки (16, 20), два блока согласования (18, 21), один источник стабилизированного напряжения (25), один источник питания (6), три входные шины: сигнал начальной установки (12), входной сигнал (15), тактовые импульсы (17) и одну выходную шину (8). 1 ил.

Схема защиты ключевого транзистора, содержащая первый транзистор, эмиттер которого подключен к общей шине, а коллектор через второй резистор подключен к базе второго транзистора и к третьему резистору, второй вывод которого подключен к источнику питания и одновременно к эмиттеру второго транзистора, коллектор которого образует выходную шину, первый резистор, первый вывод которого соединен с базой первого транзистора, отличающаяся тем, что в нее введены динамический D-триггер, вход R которого подключен к первой входной шине, а инверсный выход  соединен со входом S мультиплексора, первый вход D1 которого подключен ко второй входной шине, второй вход D2 подключен через первый элемент задержки к третьей входной шине и входу С динамического D-триггера, прямой выход Q соединен со входом первого блока согласования, а инверсный выход

соединен со входом S мультиплексора, первый вход D1 которого подключен ко второй входной шине, второй вход D2 подключен через первый элемент задержки к третьей входной шине и входу С динамического D-триггера, прямой выход Q соединен со входом первого блока согласования, а инверсный выход  через второй элемент задержки соединен со входом второго блока согласования, первый источник тока, положительный вывод которого соединен с источником стабилизированного напряжения, а отрицательный вывод соединен с первым выводом первого электронного ключа, управляемый вывод которого соединен с выходом первого блока согласования, а второй вывод через четвертый резистор подключен к общей шине и является точкой соединения пятого резистора, второй вывод которого подключен к второму выводу первого резистора и одновременно к коллектору шестого транзистора, и шестого резистора, второй вывод которого подключен одновременно к выходу второго блока согласования и базе третьего транзистора, эмиттер которого соединен с общей шиной, а коллектор с управляемым выводом второго электронного ключа, первый вывод которого соединен с отрицательным выводом второго источника тока, положительный вывод которого соединен с источником питания, а второй вывод является точкой соединения эмиттеров четвертого и пятого транзисторов, источник опорного напряжения, отрицательный вывод которого соединен с общей шиной, а положительный вывод соединен с базой четвертого транзистора, коллектор которого подключен к общей шине, седьмой транзистор, эмиттер которого подключен к общей шине, коллектор соединен с входом

через второй элемент задержки соединен со входом второго блока согласования, первый источник тока, положительный вывод которого соединен с источником стабилизированного напряжения, а отрицательный вывод соединен с первым выводом первого электронного ключа, управляемый вывод которого соединен с выходом первого блока согласования, а второй вывод через четвертый резистор подключен к общей шине и является точкой соединения пятого резистора, второй вывод которого подключен к второму выводу первого резистора и одновременно к коллектору шестого транзистора, и шестого резистора, второй вывод которого подключен одновременно к выходу второго блока согласования и базе третьего транзистора, эмиттер которого соединен с общей шиной, а коллектор с управляемым выводом второго электронного ключа, первый вывод которого соединен с отрицательным выводом второго источника тока, положительный вывод которого соединен с источником питания, а второй вывод является точкой соединения эмиттеров четвертого и пятого транзисторов, источник опорного напряжения, отрицательный вывод которого соединен с общей шиной, а положительный вывод соединен с базой четвертого транзистора, коллектор которого подключен к общей шине, седьмой транзистор, эмиттер которого подключен к общей шине, коллектор соединен с входом  динамического D-триггера, а база подключена к девятому резистору, второй вывод которого является точкой соединения седьмого резистора, второй вывод которого подключен к общей шине, восьмого резистора, второй вывод которого подключен к базе шестого транзистора, эмиттер которого подключен к общей шине, и коллектора пятого транзистора, база которого через десятый резистор подключена к выходной шине.

динамического D-триггера, а база подключена к девятому резистору, второй вывод которого является точкой соединения седьмого резистора, второй вывод которого подключен к общей шине, восьмого резистора, второй вывод которого подключен к базе шестого транзистора, эмиттер которого подключен к общей шине, и коллектора пятого транзистора, база которого через десятый резистор подключена к выходной шине.

| ЧИЖКОВ Ю.П | |||

| и др | |||

| Электрооборудование автомобилей, Москва, За рулем, 1999, с.219, рис | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Устройство контроля работы ключевого транзистора | 1989 |

|

SU1622937A1 |

| СПОСОБ ОБРАБОТКИ СПЕРМЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2056808C1 |

| US 4291357, 22.09.1981 | |||

| US 4893211, 09.01.1990. | |||

Авторы

Даты

2005-01-27—Публикация

2003-06-06—Подача