Изобретение относится к импульсной технике, а именно к транзисторным ключам, и может быть использовано для управляемого по программе подключения напряжения электропитания к биполярным полупостоянным запоминающим устройствам (ППЗУ).

Известен транзисторный ключ, обеспечивающий коммутацию активно-емкостных нагрузок и обладающий высокими коммутационными свойствами, содержащий два транзистора одной структуры, два транзистора другой структуры, логические элементы И-НЕ, И, инверторы, резисторы и нагрузку [1].

Недостатком известного транзисторного ключа является низкая его надежность при случайном подключении в цепь нагрузки встречного напряжения.

Известен транзисторный ключ, содержащий первый и второй транзисторы одной структуры, третий и четвертый транзисторы другой структуры, десять резисторов, первый и второй инверторы, первый и второй элементы И, первый и второй элементы И-НЕ, элемент задержки, дифференцирующий элемент, два элемента ИЛИ, RS-триггер, причем эмиттер первого транзистора подключен к шине источника питания и первому выводу первого резистора, второй вывод которого соединен с базой первого транзистора, коллектор которого через нагрузку подключен к общей шине, коллектор второго транзистора соединен с первым выводом второго резистора, а база подключена к первому выводу третьего резистора и через четвертый резистор к шине источника питания, второй вывод третьего резистора соединен с выходом первого элемента И-НЕ, первый вход которого подключен к первому входу второго элемента И-НЕ, выход которого через пятый резистор соединен с базой первого транзистора, эмиттер второго транзистора подключен к шине источника питания, второй вход первого элемента И-НЕ соединен с выходом первого инвертора, вход которого подключен к первому выводу шестого резистора и через седьмой резистор к общей шине, второй вход второго элемента И-НЕ соединен с коллектором первого транзистора и вторыми выводами второго и шестого резисторов, вход второго инвертора подключен к первым входам элементов И-НЕ, а выход соединен с первым входом первого элемента И и через восьмой резистор с базой третьего транзистора, коллектор которого через девятый резистор соединен с коллекторами первого и четвертого транзисторов, база четвертого транзистора через десятый резистор соединена с выходом первого элемента И, второй вход которого подключен к выходу первого инвертора, при этом эмиттеры третьего и четвертого транзисторов объединены и подключены к общей шине, первый вход второго элемента И подключен к коллектору четвертого транзистора, а второй вход через элемент задержки соединен с выходом второго инвертора, вход которого подключен к выходу первого элемента ИЛИ, первый вход которого соединен с инверсным выходом RS-триггера, R-вход которого подключен к выходу второго элемента И, а S-вход соединен с выходом второго элемента ИЛИ, первый вход которого через дифференцирующий элемент подключен к шине источника питания, а второй вход объединен со вторым входом первого элемента ИЛИ, прямой выход RS-триггера подключен к третьим входам первого и второго элементов И-НЕ. Кроме того, транзисторный ключ содержит первый и второй конденсаторы, причем первый вывод первого конденсатора подключен к коллектору первого транзистора, а второй вывод соединен с общей шиной и первым выводом второго конденсатора, второй вывод которого подключен к эмиттеру первого транзистора [2].

Известный транзисторный ключ обеспечивает коммутацию любых активно-емкостных нагрузок, обладает высокими коммутационными свойствами и имеет высокоэффективную защиту от случайного подключения в цепь нагрузки встречного напряжения.

Недостатком известного транзисторного ключа является ограниченное быстродействие, связанное со значительным временем восстановления работоспособности ключа после отключения встречного напряжения.

Указанный недостаток обусловлен тем, что в известном транзисторном ключе при аварийном подключении к нагрузке встречного напряжения (случайное попадание напряжения на отключенную от шины питания нагрузку, например, за счет наведенной ЭДС от грозовых разрядов) автоматически переходят в выключенное состояние оба разрядных транзистора, обеспечивающие разряд эквивалентной емкости нагрузки при ее отключении от шины питания. Такое отключенное состояние разрядных транзисторов сохраняется и после снятия с нагрузки аварийного встречного напряжения до тех пор, пока на входную шину не будет подан высокий уровень напряжения, устанавливающий управляющие элементы защиты ключа в исходное состояние (или пока элементы защиты ключа не установятся в исходное состояние при выключении и повторном включении напряжения питания - установка в исходное состояние через дифференцирующий элемент). Однако в ряде случаев алгоритмом управления нагрузкой может быть исключена в течение длительного времени возможность подачи на входную шину ключа высокого уровня напряжения, а также длительное время не будет коммутироваться напряжение на шине питания.

Поэтому в этих случаях, несмотря на то, что с нагрузки будет снято аварийное напряжение, нагрузка длительное время будет оставаться отключенной от шины питания и не зашунтированной разрядными транзисторами, а это, в свою очередь, может привести к недостаточно полному отключению нагрузки от источника питания и, как следствие, появлению на нагрузке некоторого напряжения за счет токов утечки коммутирующих транзисторов ключа. Это особенно опасно, если транзисторный ключ используется в качестве устройства для передачи импульсов тока в кабельную линию связи, т.к. появление такого напряжения может привести к длительному ухудшению соотношения сигнал/помеха и, как следствие, снижению достоверности передачи информации.

Перечисленные факторы приводят к увеличению времени готовности транзисторного ключа к работе после устранения аварийного подключения встречного напряжения и снижают быстродействие ключа.

Целью предлагаемого изобретения является повышение быстродействия транзисторного ключа путем сокращения времени готовности его к работе после отключения встречного напряжения.

Поставленная цель достигается тем, что в транзисторный ключ, содержащий первый и второй транзисторы одной структуры, третий и четвертый транзисторы другой структуры, десять резисторов, первый и второй инверторы, первый и второй элементы И, первый и второй элементы И-НЕ, элемент задержки, дифференцирующий элемент, два элемента ИЛИ, RS-триггер, причем эмиттер первого транзистора подключен к шине источника питания и первому выводу первого резистора, второй вывод которого соединен с базой первого транзистора, коллектор которого через нагрузку подключен к общей шине, коллектор второго транзистора соединен с первым выводом второго резистора, а база подключена к первому выводу третьего резистора и через четвертый резистор к шине источника питания, второй вывод третьего резистора соединен с выходом первого элемента И-НЕ, первый вход которого подключен к первому входу второго элемента И-НЕ, выход которого через пятый резистор соединен с базой первого транзистора, эмиттер второго транзистора подключен к шине источника питания, второй вход первого элемента И-НЕ соединен с выходом первого инвертора, вход которого подключен к первому выводу шестого резистора и через седьмой резистор к общей шине, второй вход второго элемента И-НЕ соединен с коллектором первого транзистора и вторыми выводами второго и шестого резисторов, вход второго инвертора подключен к первым входам элементов И-НЕ, а выход соединен с первым входом первого элемента И и через восьмой резистор с базой третьего транзистора, коллектор которого через девятый резистор соединен с коллекторами первого и четвертого транзисторов, база четвертого транзистора через десятый резистор соединена с выходом первого элемента И, второй вход которого подключен к выходу первого инвертора, при этом эмиттеры третьего и четвертого транзисторов объединены и подключены к общей шине, первый вход второго элемента И подключен к коллектору четвертого транзистора, а второй вход через элемент задержки соединен с выходом второго инвертора, вход которого подключен к выходу первого элемента ИЛИ, первый вход которого соединен с инверсным выходом RS-триггера, R-вход которого подключен к выходу второго элемента И, а S-вход соединен с выходом второго элемента ИЛИ, первый вход которого через дифференцирующий элемент подключен к шине источника питания, а второй вход объединен со вторым входом первого элемента ИЛИ, прямой выход RS-триггера подключен к третьим входам первого и второго элементов И-НЕ, введены пятый транзистор, одной структуры с первым и вторым транзисторами, три резистора, третий инвертор, интегрирующий элемент, третий элемент И, первый вход которого соединен с инверсным выходом RS-триггера, а выход через интегрирующий элемент подключен к третьему входу второго элемента ИЛИ, эмиттер пятого транзистора соединен с коллектором четвертого транзистора и через одиннадцатый резистор соединен с базой пятого транзистора и первым выводом двенадцатого резистора, второй вывод которого соединен с прямым выходом RS-триггера, второй вход третьего элемента И подключен к выходу третьего инвертора, вход которого соединен с коллектором пятого транзистора и первым выводом тринадцатого резистора, второй вывод которого подключен к общей шине.

Перечисленные выше существенные признаки позволяют сделать вывод о соответствии заявляемого технического решения критериям “новизна” и “изобретательский уровень”.

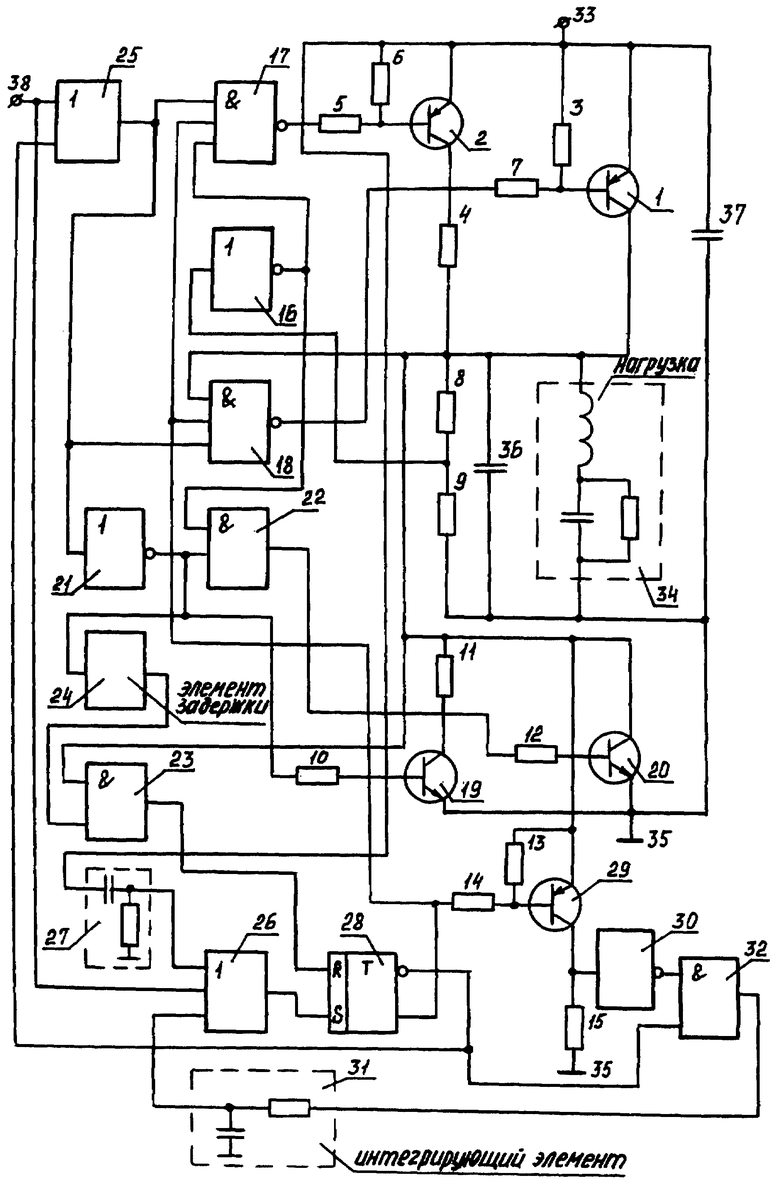

На чертеже представлена принципиальная электрическая схема транзисторного ключа.

Транзисторный ключ содержит первый 1 и второй 2 транзисторы одной структуры, тринадцать резисторов 3-15, первый инвертор 16, первый 17 и второй 18 элементы И-НЕ, третий 19 и четвертый 20 транзисторы другой структуры, второй инвертор 21, первый 22 и второй 23 элементы И, элемент задержки 24, первый 25 и второй 26 элементы ИЛИ, дифференцирующий элемент 27, RS-триггер 28, пятый транзистор 29 одной структуры с транзисторами 1 и 2, третий инвертор 30, интегрирующий элемент 31, третий элемент 32 И, причем эмиттер первого транзистора 1 подключен к шине 33 источника питания и первому выводу первого резистора 3, второй вывод которого соединен с базой первого транзистора 1, коллектор которого через нагрузку 34 подключен к общей шине 35, коллектор второго транзистора 2 соединен с первым выводом второго резистора 4, а база подключена к первому выводу третьего резистора 5 и через четвертый резистор 6 к шине 33 источника питания, второй вывод третьего резистора 5 соединен с выходом первого элемента 17 И-НЕ, первый вход которого подключен к первому входу второго элемента 18 И-НЕ, выход которого через пятый резистор 7 соединен с базой первого транзистора 1, эмиттер второго транзистора 2 подключен к шине 33 источника питания, второй вход первого элемента 17 И-НЕ соединен с выходом первого инвертора 16, вход которого подключен к первому выводу шестого резистора 8 и через седьмой резистор 9 к общей шине 35, второй вход второго элемента 18 И-НЕ соединен с коллектором первого транзистора 1 и вторыми выводами второго 4 и шестого 8 резисторов, вход второго инвертора 21 подключен к первым входам элементов 17 и 18 И-НЕ, а выход соединен с первым входом первого элемента 22 И и через восьмой резистор 10 с базой третьего транзистора 19, коллектор которого через девятый резистор 11 соединен с коллекторами первого 1 и четвертого 20 транзисторов, база четвертого транзистора 20 через десятый резистор 12 соединена с выходом первого элемента 22 И, второй вход которого подключен к выходу первого инвертора 16, эмиттеры третьего 19 и четвертого 20 транзисторов объединены и подключены к общей шине 35, первый вход второго элемента 23 И подключен к коллектору четвертого транзистора 20, а второй вход через элемент 24 задержки соединен с выходом второго инвертора 21, вход которого подключен к выходу первого элемента 25 ИЛИ, первый вход которого соединен с инверсным выходом RS-триггера 28, R-вход которого подключен к выходу второго элемента 23 И, а S-вход соединен с выходом второго элемента 26 ИЛИ, первый вход которого через дифференцирующий элемент 27 подключен к шине 33 источника питания, а второй вход объединен со вторым входом первого элемента 25 ИЛИ, при этом прямой выход RS-триггера 28 подключен к третьим входам первого 17 и второго 18 элементов И-НЕ, эмиттер пятого транзистора 29 соединен с коллектором четвертого транзистора 20 и через одиннадцатый резистор 13 соединен с базой пятого транзистора 29 и первым выводом двенадцатого резистора 14, второй вывод которого соединен с прямым выходом RS-триггера 28, первый вход третьего элемента 32 И соединен с инверсным выходом RS-триггера 28, а выход через интегрирующий элемент 31 подключен к третьему входу второго элемента 26 ИЛИ, второй вход третьего элемента 32 И подключен к выходу третьего инвертора 30, вход которого соединен с коллектором пятого транзистора 29 и первым выводом тринадцатого резистора 15, второй вывод которого подключен к общей шине 35.

Кроме того, транзисторный ключ содержит первый 36 и второй 37 конденсаторы, первый вывод первого конденсатора 36 подключен к коллектору первого транзистора 1, а второй вывод соединен с общей шиной 35 и первым выводом второго конденсатора 37, второй вывод которого подключен к эмиттеру первого транзистора 1, объединенные вторые входы элементов 25 и 26 ИЛИ соединены с клеммой 38, которая является входом транзисторного ключа.

Транзисторный ключ работает следующим образом. При включении питающего напряжения на шине 33 источника питания появляется нарастающее напряжение (передний фронт), при этом на выходе дифференцирующего элемента 27 появляется импульс короткой длительности, который через первый вход элемента 26 ИЛИ устанавливает RS-триггер 28 в единичное состояние, при котором с прямого выхода триггера 28 на третьи входы элементов 17 и 18 И-НЕ начинает поступать уровень логической единицы (“1”), а с инверсного выхода триггера 28 на первый вход элемента 25 ИЛИ - уровень логического нуля (“0”). Одновременно с прямого выхода триггера 28 уровень “1” удерживает в выключенном состоянии транзистор 29, в результате чего на входе инвертора 30 уровень “0” (через резистор 15 подан на его вход уровень общей шины), а на его выходе уровень “1”, который поступает на второй вход элемента 32 И, на первом входе которого присутствует уровень “0” с инверсного выхода триггера 28, поэтому на выходе элемента 32 И уровень “0”, который через интегрирующий элемент 31 поступает на третий вход элемента 26 ИЛИ.

В исходном состоянии на входную клемму 38 подается уровень “0”, в результате чего на выходе элемента 25 ИЛИ, а соответственно, и первых входах элементов 17 и 18 И-НЕ появляется уровень “0”, а на выходах элементов 17 и 18 И-НЕ устанавливается высокий уровень напряжения. При этом транзисторы 1 и 2 закрыты и, следовательно, нагрузка 34 отключена от шины 33 источника питания. При отсутствии напряжения на нагрузке 34 на втором входе элемента 18 И-НЕ и входе первого инвертора 16 устанавливается уровень “0”, а на выходе инвертора 16 уровень “1”, который поступает на второй вход элемента 17 И-НЕ и второй вход элемента 22 И. Кроме того, в исходном состоянии “0” с выхода элемента 25 ИЛИ подается на вход второго инвертора 21, с выхода которого уровень “1” поступает на первый вход элемента 22 И. При этом через резистор 10 в базу транзистора 19 протекает ток, открывающий транзистор 19. В это время одновременно на обоих входах элемента 22 И присутствуют уровни “1”, в результате чего на выходе элемента 22 И устанавливается уровень “1” и через резистор 12 в базу транзистора 20 протекает ток, обеспечивающий открытое состояние транзистора 20. Открытый транзистор 20 полностью шунтирует нагрузку 34 и исключает появление на ней какого-либо напряжения, так как тепловые токи закрытых транзисторов 1 и 2 протекают через открытый транзистор 20. Уровень “1” с выхода инвертора 21 через элемент 24 задержки поступает на второй вход элемента 23 И, на первом входе которого установлен уровень “0” (с отключенной нагрузки 34), поэтому на выходе элемента 23 И уровень “0”, который не влияет на состояние триггера 25 (его единичное состояние сохраняется).

При поступлении на входную клемму 38 уровня “1” на выходе элемента 25 ИЛИ появляется уровень “1”, а на выходе инвертора 21 устанавливается “0”, который выключает транзистор 19 и устанавливает на выходе элемента 22 И также уровень “0”, в результате чего ток в базу транзистора 20 прекращается и он выключается. Состояние триггера 28 при этом не изменяется (остается единичным). Наличие сигнала “0” на выходе элемента 25 ИЛИ приводит к тому, что на всех трех входах элемента 17 И-НЕ одновременно оказываются уровни “1”, в результате чего на выходе элемента 17 И-НЕ устанавливается низкий уровень напряжения, а состояние элемента 18 И-НЕ не изменяется, так как на его втором входе сохраняется уровень “0”, поступающий с нагрузки 34. Появление на выходе элемента 17 И-НЕ низкого уровня напряжения приводит к включению транзистора 2, и через резистор 4 осуществляется предварительный заряд эквивалентной емкости нагрузки 34. По мере роста напряжения на нагрузке 34 увеличивается и уровень напряжения на втором входе элемента 18 И-НЕ. Когда это напряжение достигнет уровня, равного напряжению “1”, на всех трех входах элемента 18 И-НЕ одновременно оказываются уровни “1”, в результате чего на выходе элемента 18 И-НЕ появляется низкий уровень напряжения, который открывает транзистор 1, обеспечивающий дозаряд емкости нагрузки 34 и дальнейший рост напряжения на ней.

После включения транзистора 1 напряжение в средней точке делителя напряжения, образованного резисторами 8 и 9, достигает такой величины, при которой на вход инвертора 16 начинает поступать уровень “1”, а с выхода инвертора 16 на второй вход элемента 17 И-НЕ - уровень “0”, в результате чего на выходе элемента 17 И-НЕ появляется высокий уровень напряжения, который выключает транзистор 2. При этом состояние транзистора 1 не изменяется, он остается включенным и обеспечивает подключение нагрузки 34 к шине 33 источника питания на все время, в течение которого на входной клемме 38 присутствует уровень “1”.

При поступлении на входную клемму 38 уровня “0” на выходе элемента 25 ИЛИ также появляется уровень “0”, а на выходе элемента 18 И-НЕ устанавливается высокий уровень напряжения, в результате чего транзистор 1 выключается и отключает нагрузку 34 от шины 33 источника питания (транзистор 2 остается выключенным). Поступающий с выхода элемента 25 ИЛИ на вход инвертора 21 уровень “0” приводит к появлению на выходе инвертора 16 уровня “1” и включению транзистора 19. Несмотря на то что в это время на первом входе элемента 22 И присутствует уровень “1”, элемент 22 И выключен (на его выходе уровень “1”), так как на его втором входе сохраняется уровень “0” с выхода инвертора 16, обусловленный тем, что на входе инвертора 16 присутствует высокий уровень напряжения от еще не разряженной емкости нагрузки 34. При этом транзистор 20 выключен. Включившийся транзистор 19 осуществляет предварительный разряд эквивалентной емкости нагрузки 34 через резистор 11. По мере спада напряжения на нагрузке 34 уменьшается напряжение и в средней точке делителя напряжения, образованного резисторами 8 и 9. Когда это напряжение достигнет уровня “0”, с выхода инвертора 16 на второй вход элемента 22 И начинает поступать уровень “1”. С этого момента времени на обоих входах элемента 22 И одновременно оказываются уровни “1”, в результате чего транзистор 20 переходит во включенное состояние и обеспечивает доразряд емкости нагрузки 34 и в дальнейшем полное шунтирование нагрузки (шунтирование тепловых токов и токов утечки транзисторов 1 и 2).

Таким образом, в первый момент выключения транзисторного ключа разряд эквивалентной емкости нагрузки 34 осуществляется через открытый транзистор 19 и резистор 11. Резистор 11 в ключе выбирается из условия максимально допустимого тока коллектора транзистора 19 и допустимой постоянной времени разряда эквивалентной емкости нагрузки и исключает перегрузку транзистора 19 по току при любом значении эквивалентной емкости нагрузки 34. С целью симметрирования постоянных времени заряда и разряда эквивалентной емкости нагрузки 34 номиналы резисторов 4 и 11 следует, как правило, выбирать равными. Итак, через резистор 11 осуществляется предварительный разряд емкости нагрузки до заданного напряжения, а окончательный ее разряд и полное шунтирование нагрузки осуществляется с помощью транзистора 20, в коллекторной цепи которого отсутствуют ограничительные элементы тока (так как этот транзистор должен иметь минимальное остаточное напряжение между коллектором и эмиттером для более эффективного шунтирования нагрузки 34).

Появившийся на выходе инвертора 21 уровень “1” через время задержки элемента 24 задержки поступает на второй вход элемента 23 И. Время задержки элемента 24 задержки выбирают таким, чтобы оно превышало время разряда эквивалентной емкости нагрузки 34, поэтому к моменту появления на втором входе элемента 23 И уровня “1” на его первом входе устанавливается уровень “0” в результате разряда эквивалентной емкости нагрузки 34. Поэтому через время задержки элемента 24 задержки состояние элемента 23 И не изменяется и на его выходе сохраняется уровень “0”, что сохраняет единичное состояние триггера 28.

При возникновении аварийной ситуации (например, при случайном попадании напряжения на отключенную от шины питания нагрузку) транзистор 20 автоматически переходит в выключенное состояние, так как при этом на входе инвертора 16 мгновенно оказывается уровень “1”, a на его выходе - уровень “0”, который выключает элемент 22 И по его второму входу и прекращает подачу тока в базовую цепь транзистора 20. В это же время высокий уровень напряжения с нагрузки 34 поступает на первый вход элемента 23 И, поэтому на обоих входах элемента 23 И одновременно устанавливаются уровни “1” и на его выходе, который воздействует на R-вход RS-триггера 28 (в это время на S-входе RS-триггера 28 - уровень “0”). RS-триггер 25 устанавливается в нулевое состояние, при котором на его прямом выходе уровень “0”, а с его инверсного выхода на первый вход элемента 25 ИЛИ начинает поступать уровень “1”, приводящий к появлению уровня “1” на выходе элемента 25 ИЛИ (несмотря на то, что в это время на клемме 38 - уровень “0”). При этом на выходе инвертора 21 устанавливается уровень “0”, который выключает и транзистор 19. Одновременно уровень “0” с выхода инвертора 21 подтверждает по первому входу элемента 22 И его выключенное состояние (а соответственно, подтверждается и выключенное состояние транзистора 20). С этого момента оба транзистора 19 и 20 выключены, находятся в безопасном состоянии и не потребляют тока от встречно включенного к нагрузке источника напряжения (через резистор 11 исключается протекание тока и мощность на нем не рассеивается).

В аварийном режиме уровень “1”, поступающий на первые входы элементов 17 и 18 И-НЕ с выхода элемента 25 ИЛИ, не приводит к включению этих элементов, так как переход RS-триггера 28 в нулевое состояние при аварийном подключении к нагрузке встречного напряжения обеспечивает уровень “0” на третьих входах элементов 17 и 18 И-НЕ (с прямого выхода триггера 28), при этом транзисторы 1 и 2 выключены.

Наличие уровня “0” на прямом выходе триггера 28 приводит к появлению через резистор 14 базового тока транзистора 29, и он включается, в результате чего на входе инвертора 30 - уровень “1” (от внешнего напряжения на нагрузке), а на его выходе - уровень “0”, поступающий на второй вход элемента 32 И, поэтому на выходе элемента 32 И уровень “0” сохраняется, несмотря на наличие на его первом входе уровня “1” с инверсного выхода триггера 28. Также сохраняется уровень “0” и на третьем входе элемента 26 ИЛИ (интегрирующий элемент 31 исключает даже кратковременное изменение уровня на третьем входе элемента 26 ИЛИ при переключении триггера 28).

Если теперь устранить аварийное состояние нагрузки 34 (снять случайно попавшее на нее внешнее напряжение), то ток через транзистор 29 прекратится и через резистор 15 на входе инвертора 30 окажется уровень “0”, а на его выходе уровень “1”. С этого момента времени на обоих входах элемента 32 И окажутся уровни “1”, что приведет к появлению уровня “1” на его выходе, который через время интегрирования интегрирующего элемента 31 окажется на третьем входе элемента 26 ИЛИ. На выходе элемента 26 ИЛИ появится уровень “1”, который по S-входу взведет триггер 28 в исходное состояние, при котором с его инверсного выхода уровень “0” начнет поступать на первый вход элемента 25 ИЛИ и снимет блокировку ключа (транзисторы 19 и 20 включатся по описанному выше принципу, если в это время на входной шине 38 продолжает сохраняться уровень “0”).

Следует отметить, что схема транзисторного ключа может быть взведена в исходное состояние (при устраненной аварийной ситуации) и подачей на входную шину 38 уровня “1”, так как при этом через второй вход элемента 26 ИЛИ триггер 28 может быть установлен в единичное состояние, при котором возможна работа как зарядных (включающих) транзисторов 1 и 2, так и разрядных (выключающих) транзисторов 19 и 20.

Интегрирующий элемент 31 предназначен для задержки разблокирования схемы транзисторного ключа на время коммутационных процессов, как правило, сопровождающих устранение аварийной ситуации (отключение внешнего напряжения), что повышает помехоустойчивость автоматического восстановления схемы транзисторного ключа.

Конденсаторы 36 и 37 позволяют исключить броски напряжения на нагрузке и входах логических элементов за счет компенсации индуктивности проводников, соединяющих транзисторный ключ с нагрузкой 34, шиной питания 33 и общей шиной 35.

Таким образом, предложенный транзисторный ключ по сравнению с известным обеспечивает автоматическое восстановление рабочего состояния сразу же после устранения аварийного попадания внешнего напряжения на нагрузку и при этом не обязательна подача на входную шину ключа управляющего сигнала (уровня “1”). Это обеспечивает повышение быстродействия транзисторного ключа, так как после устранения аварийного состояния нагрузки (отключения внешнего напряжения) нагрузка сразу же оказывается зашунтированной разрядными транзисторами.

Структура построения транзисторного ключа позволяет реализовать его с применением современных прогрессивных технологий в микроэлектронике (например, ПЛИС - технологий), что позволит создать высоконадежные и быстродействующие устройства для передачи импульсов тока в кабельные линии связи.

Источники информации

1. Авторское свидетельство СССР №1264332, кл. Н 03 К 17/60, опубл. 15.10.1986 г., БИ №38.

2. Авторское свидетельство СССР № 1320892, кл. Н 03 К 17/60, опубл. 30.06.1987 г., БИ №24.

| название | год | авторы | номер документа |

|---|---|---|---|

| Транзисторный ключ | 1985 |

|

SU1336223A2 |

| Транзисторный ключ | 1986 |

|

SU1320892A1 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ | 2005 |

|

RU2287219C1 |

| Транзисторный ключ | 1985 |

|

SU1265992A2 |

| Транзисторный ключ с защитой от перегрузки | 1988 |

|

SU1531203A1 |

| Импульсный понижающий стабилизатор постоянного напряжения | 1990 |

|

SU1786477A1 |

| Транзисторный ключ | 1985 |

|

SU1264332A2 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| RS-триггер | 1989 |

|

SU1626341A1 |

| УСТРОЙСТВО ДЛЯ ЗАЖИГАНИЯ И ПИТАНИЯ ГАЗОРАЗРЯДНЫХ ЛАМП НИЗКОГО ДАВЛЕНИЯ | 1992 |

|

RU2030131C1 |

Изобретение относится к импульсной технике и может использоваться для управляемого по программе подключения напряжения питания к биполярным полупостоянным запоминающим устройствам, а также в качестве формирователя импульсов тока в кабельную или воздушную линию связи с распределенными параметрами. Технический результат заключается в повышении быстродействия за счет сокращения времени готовности его к работе после отключения аварийного встречного напряжения от нагрузки. Транзисторный ключ содержит транзисторы (Т) (1, 2, 29) одной структуры, Т (19, 20) другой структуры, логические элементы управления (16-18, 21-23, 25, 30, 32), резисторы (3-15), дифференцирующий (27) и интегрирующий (31) элементы, элемент (24) задержки, RS-триггер (28). Устройство позволяет оперативно следить за состоянием нагрузки ТК и быстро восстанавливать его работоспособность после устранения аварии в нагрузке (после отключения аварийного встречного напряжения). 1 ил.

Транзисторный ключ, содержащий первый и второй транзисторы одной структуры, третий и четвертый транзисторы другой структуры, десять резисторов, первый и второй инверторы, первый и второй элементы И, первый и второй элементы И-НЕ, элемент задержки, дифференцирующий элемент, два элемента ИЛИ, RS-триггер, причем эмиттер первого транзистора подключен к шине источника питания и первому выводу первого резистора, второй вывод которого соединен с базой первого транзистора, коллектор которого через нагрузку подключен к общей шине, коллектор второго транзистора соединен с первым выводом второго резистора, а база подключена к первому выводу третьего резистора и через четвертый резистор к шине источника питания, второй вывод третьего резистора соединен с выходом первого элемента И-НЕ, первый вход которого подключен к первому входу второго элемента И-НЕ, выход которого через пятый резистор соединен с базой первого транзистора, эмиттер второго транзистора подключен к шине источника питания, второй вход первого элемента И-НЕ соединен с выходом первого инвертора, вход которого подключен к первому выводу шестого резистора и через седьмой резистор к общей шине, второй вход второго элемента И-НЕ соединен с коллектором первого транзистора и вторыми выводами второго и шестого резисторов, вход второго инвертора подключен к первым входам элементов И-НЕ, а выход соединен с первым входом первого элемента И и через восьмой резистор с базой третьего транзистора, коллектор которого через девятый резистор соединен с коллекторами первого и четвертого транзисторов, база четвертого транзистора через десятый резистор соединена с выходом первого элемента И, второй вход которого подключен к выходу первого инвертора, при этом эмиттеры третьего и четвертого транзисторов объединены и подключены к общей шине, первый вход второго элемента И подключен к коллектору четвертого транзистора, а второй вход через элемент задержки соединен с выходом второго инвертора, вход которого подключен к выходу первого элемента ИЛИ, первый вход которого соединен с инверсным выходом RS-триггера, R-вход которого подключен к выходу второго элемента И, а S-вход соединен с выходом второго элемента ИЛИ, первый вход которого через дифференцирующий элемент подключен к шине источника питания, а второй вход объединен со вторым входом первого элемента ИЛИ, прямой выход RS-триггера подключен к третьим входам первого и второго элементов И-НЕ, отличающийся тем, что дополнительно содержит пятый транзистор одной структуры с первым и вторым транзисторами, три резистора, третий инвертор, интегрирующий элемент, третий элемент И, первый вход которого соединен с инверсным выходом RS-триггера, а выход через интегрирующий элемент подключен к третьему входу второго элемента ИЛИ, эмиттер пятого транзистора соединен с коллектором четвертого транзистора и через одиннадцатый резистор соединен с базой пятого транзистора и первым выводом двенадцатого резистора, второй вывод которого соединен с прямым выходом RS-триггера, второй вход третьего элемента И подключен к выходу третьего инвертора, вход которого соединен с коллектором пятого транзистора и первым выводом тринадцатого резистора, второй вывод которого подключен к общей шине.

| Транзисторный ключ | 1986 |

|

SU1320892A1 |

Авторы

Даты

2004-07-20—Публикация

2002-11-12—Подача