113

Изобретение относится к области накопления информации, а именно к устройствам для синхронизации воспроизведения цифровой магнитной записи.

Цель изобретения - повып1ение дос- товерности воспроизведения цифровой магнитной записи.

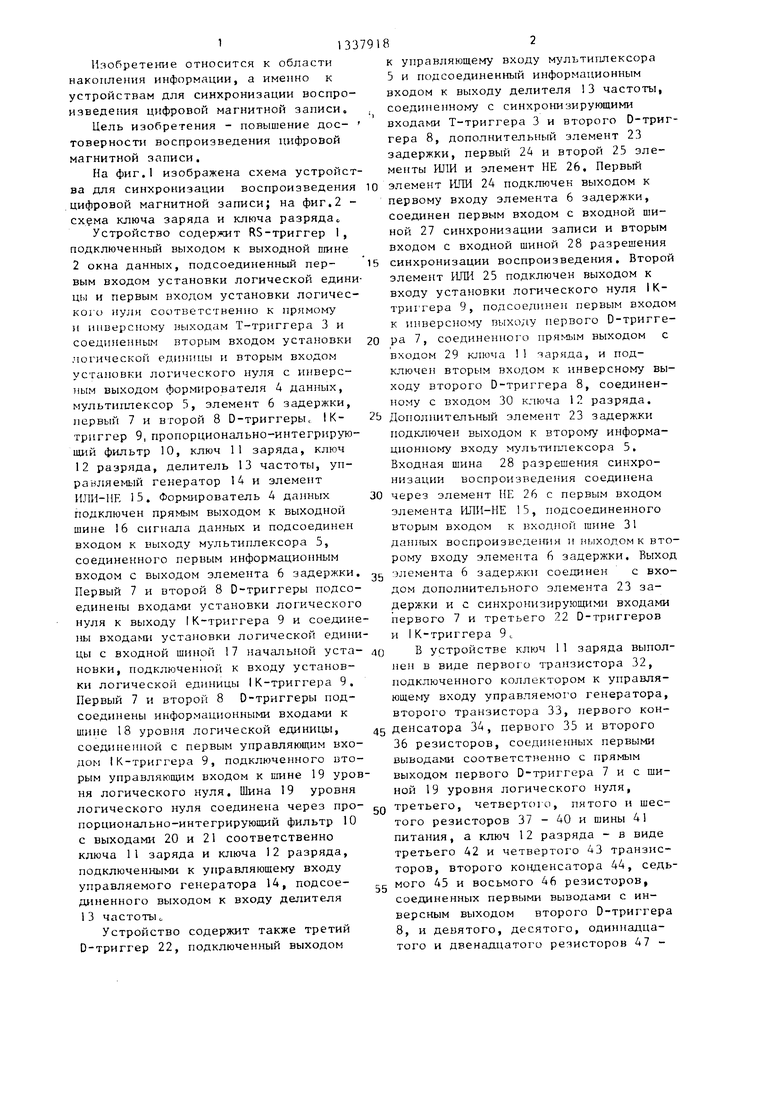

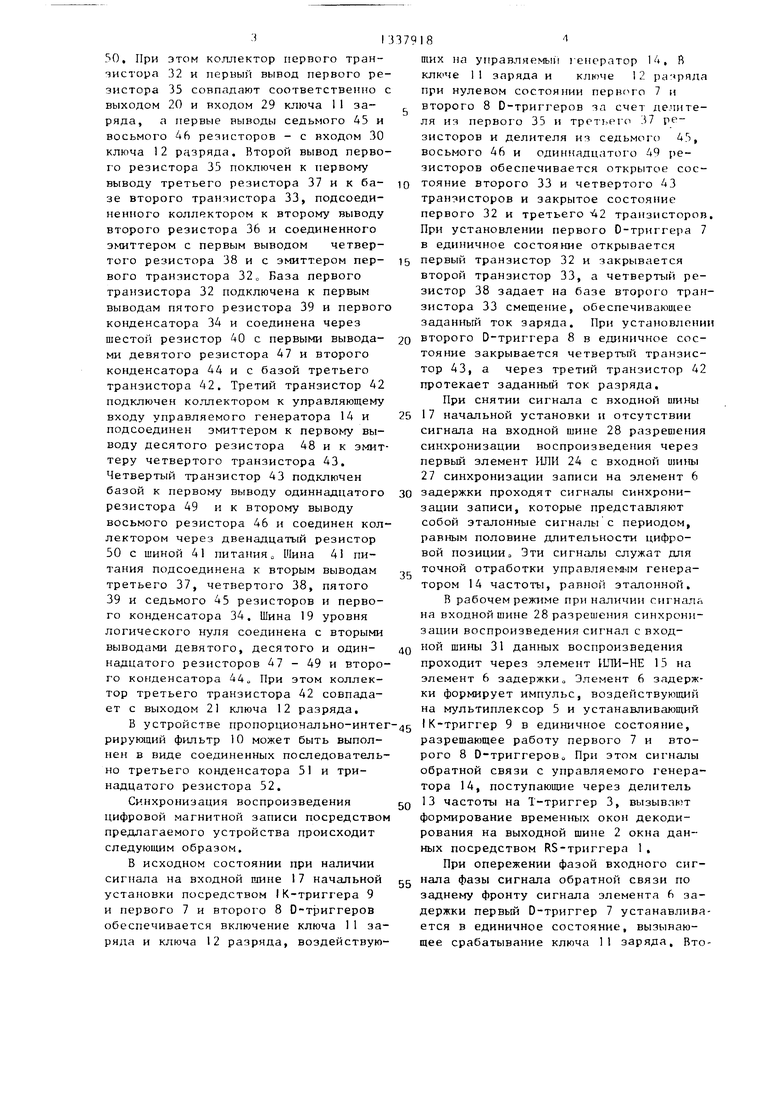

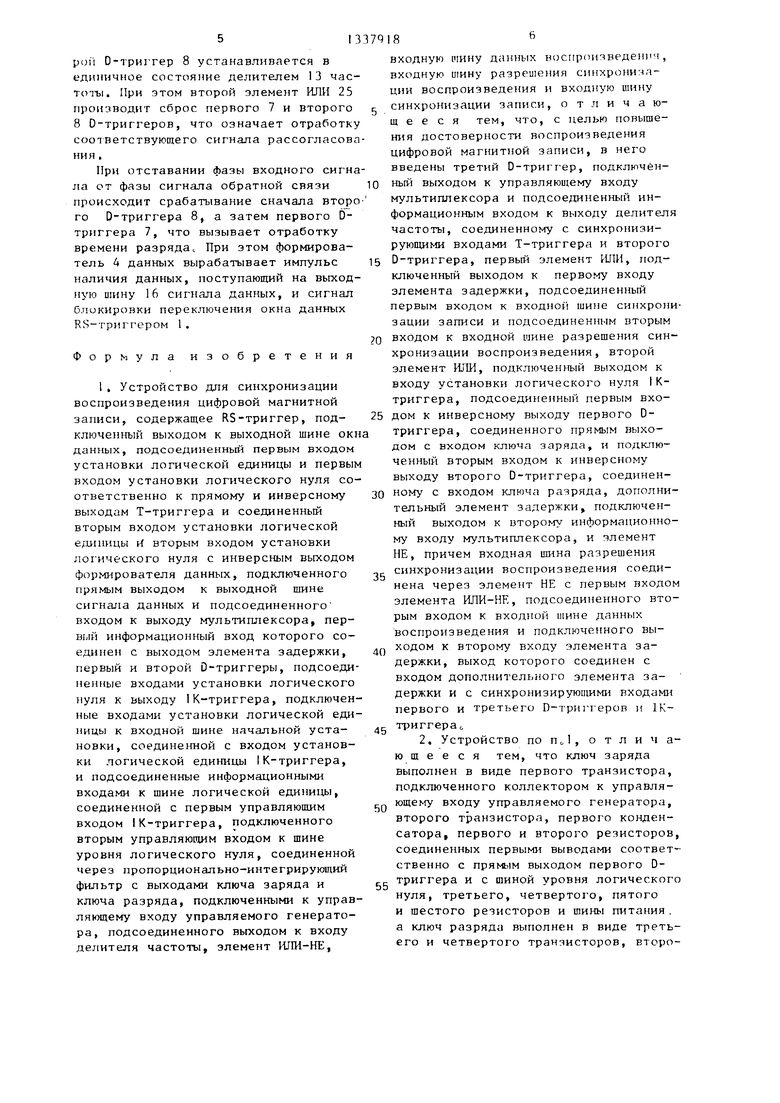

На фиг.1 изображена схема устройства для синхронизации воспроизведения цифровой магнитной записи; на фиг,2 - ключа заряда и ключа разрядво

Устройство содержит RS-триггер 1, подключенный выходом к выходной пшне 2 окна данных, подсоединенный пер- вым входом установки логической единицы и первым входам установки логического нуля соответственно к прямому и инверсному 1 ыходам Т-триггера 3 и соединенным вторым входом установки .чогической единицы и вторым входом установки логического нуля с инверсным выходом формирователя А данных, мультиплексор 5, элемент 6 задержки, первый 7 и второй 8 D-триггерЫс 1К- триггер 9, пропорционально-интегрирующий фильтр 10, ключ 11 заряда, ключ

12разряда, делитель 13 частоты, управляемый генератор 14 и элемент ИЛИ-НЕ 15. Формирователь 4 данных подключен прямым выходом к выходной шине 16 сигнала данных и подсоединен входом к выходу мультиплексора 5, соединенного первым информационным входом с выходом элемента 6 задержки. Первый 7 и второй 8 О-триггеры подсоединены входами установки логического нуля к выходу IК-триггера 9 и соединены входами установки логической единицы с входной шиной 17 начгшьной уста- новки, подключенной к входу установки логической единицы IК-триггера 9, Первый 7 и второй 8 О-триггеры подсоединены информационными входами к шине 18 уровня логической единицы, соедине1и1ой с первым управляющим входом IК-триггера 9, подключенного вторым управляюпдш входом к шине 19 уровня логического нуля. Шина 19 уровня логического нуля соединена через про- порционально-интегрирующий фильтр 10

с выходами 20 и 21 соответственно ключа 11 заряда и ключа 12 разряда, подключенными к управляющему входу управляемого генератора 14, подсое- диненного выходом к входу делителя

13частоты о

Устройство содержит также третий О-триггер 22, подключенный выходом

82

к управляющему входу мультиплексора 5 и подсоединенный информационным входом к выходу делителя 13 частоты, соединенному с синхронизирующими входами Т-триггера 3 и второго D-три гера 8, дополнительный элемент 23 задержки, первый 24 и второй 25 элементы ИЛИ и элемент НЕ 26. Первый элемент ИЛИ 24 подключен выходом к первому входу элемента 6 задержки, соединен первым входом с входной щи- ной 27 синхронизации записи и вторым входом с входной щиной 28 разрешения синхронизации воспроизведения. Второ элемент ИЛИ 25 подключен выходом к входу установки логического нуля IК- триггера 9, подсоединен первым входо к инверсному выходу первого D-тригге ра 7, соединенного прямым выходом с входом 29 ключа 11 яаряда, и подключен вторым входом к инверсному выходу второго D-триггера 8, соединенному с входом 30 ключа 12 разряда. Дополнительный элемент 23 задержки подключен выходом к BTopoNry информационному входу мультиплексора 5, Входная шина 28 разрешения синхронизации воспроизведения соединена через элемент НЕ 26 с первым входом элемента ИЛИ-НЕ 15, подсоединенного вторым входом к входной шине 31 данных воспроизведения и ныходомк второму входу элемента 6 задержки. Выход элемента 6 задержки соединен с входом дополнительного элемента 23 задержки и с синхронизирующими входами первого 7 и третьего 22 D-триггеров и IК-триггера 9 с

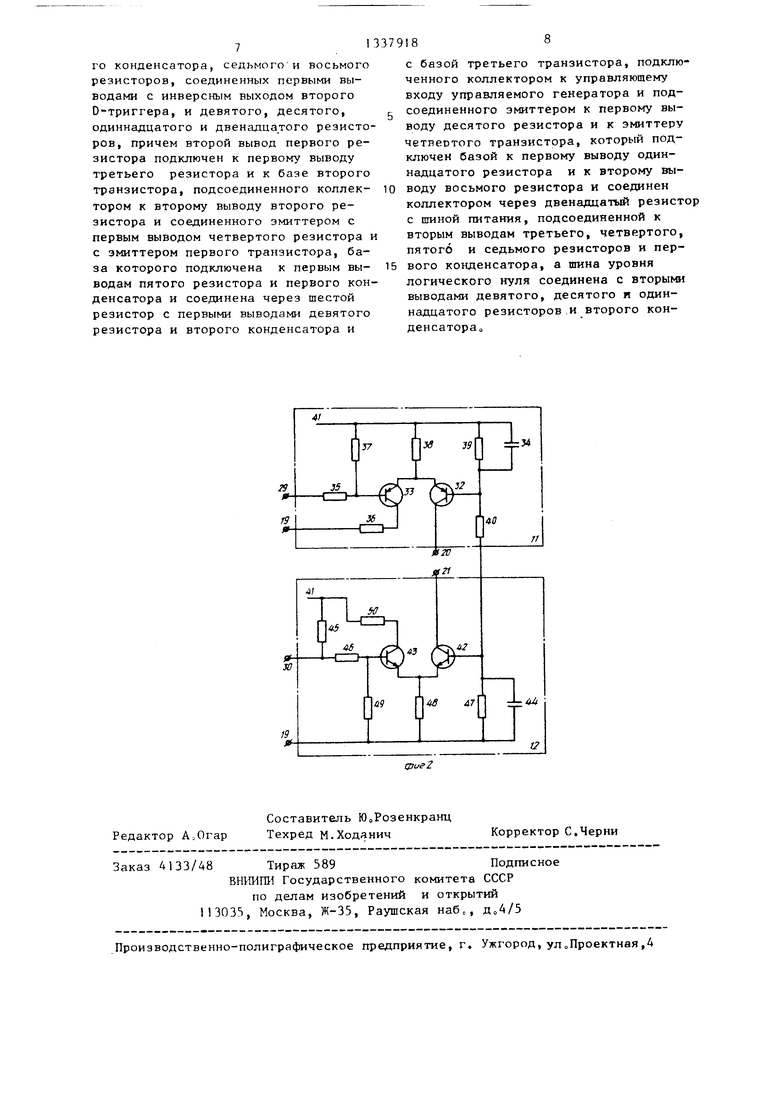

В устройстве ключ 11 заряда выполнен в виде первого транзистора 32, подключенного коллектором к управля- входу управляемого генератора, второго транзистора 33, первого конденсатора 34, первого 35 и второго 36 резисторов, соединенных первыми выводами соответственно с прямым выходом первого D-триггера 7 и с шиной 19 уровня логического нуля, третьего, четвертсп-о, пятого и шестого резисторов 37 - 40 и шины 41 питания, а ключ 12 разряда - в виде третьего 42 и четвертого 43 транзисторов, второго ковденсатора 44, седьмого 45 и восьмого 46 резисторов, соединенных первыми выводами с инверсным выходом второго D-триггера 8, и девятого, десятого, одиннадцатого и двенадцатого резисторов 47 3П

50, При этом коллектор первого транзистора 32 и первый вывод первого резистора 35 совпадают соответственно с выходом 20 и входом 29 ключа 11 за- ряда, а первые выводы седьмого 45 и восьмого 46 резисторов - с входом 30 ключа 12 разряда. Второй вывод первого резистора 35 поключен к первому выводу третьего резистора 37 и к ба- зе второго транзистора 33, подсоединенного коллектором к второму выводу второго резистора 36 и соединенного эмиттером с первым выводом четвертого резистора 38 и с эмиттером пер- вого транзистора 32„ База первого транзистора 32 подключена к первым выводам пятого резистора 39 и первого конденсатора 34 и соединена через шестой резистор 40 с первыми вывода- ми девятого резистора 47 и второго конденсатора 44 и с базой третьего транзистора 42. Третий транзистор 42 подключен коллектором к управляющему входу управляемого генератора 14 и подсоединен эмиттером к первому выводу десятого резистора 48 и к эмиттеру четвертого транзистора 43, Четвертый транзистор 43 подключен базой к первому выводу одиннадцатого резистора 49 и к второму выводу восьмого резистора 46 и соединен коллектором через двенадцатый резистор 50 с шиной 41 питания о Шина 41 питания подсоединена к вторым выводам третьего 37, четвертого 38, пятого 39 и седьмого 45 резисторов и первого конденсатора 34, Шина 19 уровня логического нуля соединена с вторыми выводами девятого, десятого и один- надцатого резисторов 47 - 49 и второго конденсатора 44 о При этом коллектор третьего транзистора 42 совпадает с выходом 21 ключа 12 разряда,

В устройстве пропорционально-интег рирующий фильтр 10 может быть выполнен в виде соединенных последовательно третьего конденсатора 51 и тринадцатого резистора 52,

Синхронизация воспроизведения цифровой магнитной записи посредством предлагаемого устройства происходит следуюш,им образом,

В исходном состоянии при наличии сигнала на входной шине 17 начальной установки посредством IК-триггера 9 и первого 7 и второго 8 О-триггеров обеспечивается включение ключа 11 заряда и ключа 12 разряда, воздействую18

щих на управляемы генератор 14, ft ключе II заряда и ключе 12 рагфлда при нулевом состоянии первс го 7 и второго 8 D-триггеров за счет делителя из первого 35 и трст1 егс1 37 резисторов и делителя из седьмого 43, восьмого 46 и одиннадцатого 49 резисторов обеспечивается открытое состояние второго 33 и четвертого 43 транзисторов и закрытое состояние первого 32 и третьего 42 транзисторов При установлении первого О-триггера 7 в единичное состояние открывается первый транзистор 32 и закрывается второй транзистор 33, а четвертый резистор 38 задает на базе второго транзистора 33 смещение, обеспечивающее заданный ток заряда. При установлени второго D-триггера 8 в единичное состояние закрывается четвертый транзистор 43, а через третий транзистор 42 протекает заданный ток разряда.

При снятии сигнала с входной пшны 17 начальнор установки и отсутствии сигнала на входной шине 28 разрешения синхронизации воспроизведения через первый элемент ИЛИ 24 с входной 27 синхронизации записи на элемент 6 задержки проходят сигналы синхронизации записи, которые представляют собой эталоннь1е сигналы с периодом, равным половине длительности цифровой позиции Эти сигналы служат для точной отработки управляемым генератором 14 частоты, равной эталонной,

В рабочем режиме при наличии сигнала на входной шине 28 разрешения синхронизации воспроизведения сигнал с входной шины 31 данных воспроизведения проходит через элемент ILTH-HE 15 на элемент 6 задержки Элемент 6 задержки формирует импульс, воздействующий на мультиплексор 5 и устанавливающий 1К-триггер 9 в единичное состояние, разрешающее работу первого 7 и второго 8 О-триггероВо При этом сигналы обратной связи с управляемого генератора 14, поступающие через делитель 13 частоты на Т-триггер 3, вызывпн)т формирование временных окон декодирования на выходной шине 2 окна данных посредством RS-триггера 1,

При опережении фазой входного сигнала фазы сигнала обратной связи по заднему фронту сигнала элемента 6 задержки первый D-триггер 7 устанавливается в единичное состояние, вызывающее срабатывание ключа 11 заряда, Вто5I

D-триггер 8 устанавливается в единичное состояние делителем 13 час- тспъи При этом второй элемент ИЛИ 25 нроизводит сброс первого 7 и второго 8 О-триггеров, что означает отработку соо1ветствующего сигнала рассогласования ,

При отставании фазы входного сигнала от фазы сигнала обратной связи происходит срабатывание сначала второ го D-триггера 8, а затем первого D- триггера 7, что вызывает отработку времени разряда При этом формирователь 4 данных вырабатывает импульс наличия данных, поступающий на выходную шину 16 сигнала данных, и сигнал блокировки переключения окна данных RS-триггером 1.

Формула изобретения

1 , Устройство для синхронизации воспроизведения цифровой магнитной записи, содержащее RS-триггер, под- ключенный выходом к выходной шине окн данных, подсоединенный первым входом установки логической единицы и первым входом установки логического нуля соответственно к прямому и инверсному выходам Т-триггера и соединенный вторым входом установки логической единицы И вторым входом установки лог ического нуля с инверсным выходом формирователя данных, подключенного прямым выходом к выходной шине сигнала данных и подсоединенного входом к выходу мультиплексора, пер- В1,гй информационный вход которого соединен с выходом элемента задержки, первый и второй D-триггеры, подсоединенные входами установки логического нуля к выходу 1К-триггера, подключенные входами установки логической единицы к входной шине начальной уста- новки, соединенной с входом установки логической единицы 1К-триггера, и подсоединенные информационными входами к шине логической единицы, соединенной с первым управляющим входом 1К-триггера, подключенного вторым управляющим входом к шине уровня логического нуля, соединенной через пропорционально-интегрирующий фильтр с выходами ключа заряда и ключа разряда, подключенными к управляющему входу управляемого генератора, подсоединенного выходом к входу делителя частоты, элемент ИЛИ-НЕ,

18

входную 1чину данных воспроизведет , входную шину разрешения синхронизации воспроизведения и входную шину синхронизации записи, отличающееся тем, что, с целью повышения достоверности воспроизведения цифровой магнитной записи, в него введены третий D-триггер, подключённый выходом к управляющему входу мультиплексора и подсоединенный информационным входом к выходу делителя частоты, соединенному с синхронизирующими входами Т-триггера и второго D-триггера, первый элемент ИЛИ, подключенный выходом к первому входу элемента задержки, подсоединенный первым входом к входной шине синхронизации записи и подсоединенным вторым входом к входной шине разрещения синхронизации воспроизведения, второй элемент ИЛИ, подключенный выходом к входу установки логического нуля IК- триггера, подсоединенный первым входом к инверсному выходу первого 0- триггера, соединенного прямым выходом с входом ключа заряда, и подключенный вторым входом к инверсному выходу второго D-триггера, соединенному с входом ключа разряда, дополнительный элемент задержки, подключенный выходом к второму информационному входу мультиплексора, и элемент НЕ, причем входная шина разрешения синхронизации воспроизведения соединена через элемент НЕ с первым входом элемента ИЛИ-НЕ, подсоединенного вторым входом к входной шине данных воспроизведения и подключенного выходом к второму входу элемента задержки, выход которого соединен с входом дополнительного элемента задержки и с синхронизирующими входами первого и третьего D-триггеров и 1К- триггера

2. Устройство по п„1, о т л и ч а- ю щ е е с я тем, что ключ заряда выполнен в виде первого транзистора, подключенного коллектором к управляющему входу управляемого генератора, второго транзистора, первого конденсатора, первого и второго резисторов соединенных первыми выводами соответственно с прямым выходом первого D- триггера и с шиной уровня логического нуля, третьего, четвертого, пятого и шестого резисторов и шины ггитания , а ключ разряда выполнен в виде третьего и четвертого транзисторов, второго конденсатора, седьмого и восьмого резисторов, соединенных первыми выводами с инверсным выходом второго О-триггера, и девятого, десятого, одиннадцатого и двенадцатого резисторов, причем второй вывод первого резистора подключен к первому выводу третьего резистора и к базе второго транзистора, подсоединенного коллектором к второму выводу второго резистора и соединенного эмиттером с первым выводом четвертого резистора и с эмиттером первого транзистора, база которого подключена к первым выводам пятого резистора и первого конденсатора и соединена через тестой резистор с первыми выводами девятого резистора и второго конденсатора и

с базой третьего транзистора, подключенного коллектором к управляющему входу управляемого генератора и подсоединенного эмиттером к первому выводу десятого резистора и к эмиттеру четпестого транзистора, который подключен базой к первому выводу одиннадцатого резистора и к второму выводу восьмого резистора и соединен

коллектором через двенадцатый резистор с шиной питания, подсоединенной к вторым выводам третьего, четвертого, пятого и седьмого резисторов и первого конденсатора, а шина уровня логического нуля соединена с вторыми выводами девятого, десятого и одиннадцатого резисторов.и второго кон- денсатора

37 ПЛУ 39l 34

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации воспроизведения цифровой магнитной записи | 1985 |

|

SU1278941A1 |

| Устройство для выделения тактовой частоты при воспроизведении цифрового сигнала | 1991 |

|

SU1770985A1 |

| СХЕМА ЗАЩИТЫ КЛЮЧЕВОГО ТРАНЗИСТОРА | 2003 |

|

RU2245602C1 |

| УСТРОЙСТВО КОДИРОВАНИЯ, ПРИЕМА И ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ ПО ДВУХПРОВОДНОЙ ЛИНИИ СВЯЗИ | 1996 |

|

RU2115240C1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Импульсный стабилизатор постоянного напряжения | 1988 |

|

SU1571561A1 |

| УСТРОЙСТВО ДЛЯ БЕСКОНТАКТНОГО ИЗМЕРЕНИЯ ИМПУЛЬСНЫХ ТОКОВ | 1990 |

|

RU2024025C1 |

| Устройство выделения данных при воспроизведении информации на подвижном магнитном носителе | 1986 |

|

SU1381589A1 |

| Устройство для управления лентопротяжным механизмом | 1987 |

|

SU1607006A1 |

| Устройство для синхронизации воспроизведения цифровой магнитной записи | 1984 |

|

SU1167647A1 |

Изобретение относится к области накопления информации. Цель изобретения - повышение достоверности воспроизведения цифровой магн.записи. При СНЯТИИ сигнала с входной шины 17 наJ/ - --- чальной установки и при отсутствии сигнала на шине 28 разрешения синхронизации воспроизведения через элемент ИЛИ 24 на элемент 6 задержки .проходят сигналы синхронизации записи, которые представляют собой эталонные сигналы с периодом, равным половине длительности цифровой позиции. Эти сигналы служат для обработки генератором 14 частоты, равной эталонной. В рабочем режиме сигнал с входной шины 31 данных воспроизведения проходит через элемент ИЛИ-НЕ 15 на элемент 6 задержки, который формирует импульс, воздействующий на мультиплексор 5 и устанавливающий IК-триггер 9 в единичное состояние, разрешающее работу D- триггеров 7 и 8. Сигналы обратной связи с генераторами 14, поступающие через делитель 13 частоты на Т-триггер 3, вызывают формирование временных окон декодирования на выходной шине 2 окна данных посредством RS-триггера 1 . 1 3 . п. ф-лы, 2 ил. (Л 00 &о сх

Редактор А.Огар

Составитель ЮоРозенкранц Техред М.Ходанич

Заказ 4133/48 Тираж 589Подписное

ВНШПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г. Ужгород, улоПроектная,4

Корректор С.Черни

| Устройство для синхронизации воспроизведения цифровой магнитной записи | 1982 |

|

SU1048512A1 |

| Flexible Disk Cont- roller Hardware Reference manual | |||

| Способ исследования моделей арочных плотин | 1958 |

|

SU121583A1 |

| Copyright, 1980, 1981 | |||

| Intel Corporation, 3065 Bowers avenul Santa Clara California 9505, p | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-09-15—Публикация

1986-03-31—Подача