Изобретение относится к области радиосвязи и может быть использовано в цифровых системах, в частности в системах спутниковой и наземной подвижной радиосвязи для создания колебаний с угловой модуляцией с компактным спектром.

Аналогами заявляемого устройства являются частотные модуляторы, использующие квадратурные схемы формирования модулированного сигнала, к которым относятся, например, модулятор π /4-DQPSK и CQPSK (Овчинников М.А., Воробьев С.В., Сергеев С.И. Открытые стандарты цифровой транкинговой радиосвязи. Серия изданий “Связь и бизнес”, М.: МЦНТИ, ООО “Мобильные коммуникации”, 2000, - 166 с. См. с.73 и 158). Эти модуляторы выполнены по одинаковым структурным схемам (рис.9.1 на с.74 и 8.10 на с.159). Блок “Таблица перекодировки”, представленный на рис. 8.10, на рис.9.1 представлен более подробно. Различаются модуляторы π /4-DQPSK и CQPSK только фильтрами и скоростью передачи информации (с.160). Эти модуляторы включат в себя устройство перекодировки, два фильтра нижних частот (фильтры Найквиста), два амплитудных модулятора и сумматор, причем два выхода устройства перекодировки соединяются, соответственно, с входами фильтров нижних частот, выходы фильтров нижних частот соединяются с первыми входами амплитудных модуляторов, на вторые входы амплитудных модуляторов подается несущее колебание с взаимным сдвигом по фазе на π /2, выходы этих модуляторов соединяются с входами сумматора, выход которого является выходом частотного модулятора. Недостатком этих частотных модуляторов является наличие сопутствующей амплитудной модуляции выходного сигнала. Вследствие этого усилитель мощности передатчика такого сигнала должен работать в линейном режиме, что исключает возможность использования высокоэффективных режимов работы передатчика с высоким КПД (с.80, с.160). Причина появления сопутствующей AM заключается в используемом методе формирования модулирующих напряжений для модуляторов в квадратурных каналах (использование реакции фильтров нижних частот, в том числе фильтров Найквиста, при действии на их входах коротких импульсов возбуждения).

Наиболее близким по технической сущности является модулятор, осуществляющий частотную модуляцию без разрыва фазы Minimum Shift Keying (MSK) или, что то же самое, модуляцию минимальным частотным сдвигом (ММС) (см. книгу: Банкет В.Л., Дорофеев В.М. Цифровые методы в спутниковой связи. - М.: Радио и связь, 1988. - 240 с., ил., с. 39-40, рис.2.1б, 2.2).

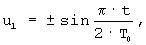

Этот модулятор содержит переключатель посылок на два квадратурных канала (четные - в один канал, нечетные - в другой), блок формирования сглаживающих напряжений, два перемножителя, генератор несущей, фазовращатель, два амплитудно-фазовых модулятора и сумматор. Поочередное переключение посылок входного модулирующего сигнала на два канала обеспечивает увеличение в два раза длительности посылок в каждом канале. Сглаживание прямоугольных посылок длительностью 2Т0 по законам

в каждом канале, соответственно, обеспечивает форму огибающих в.-ч. напряжений на выходах амплитудно-фазовых модуляторов в соответствии с напряжениями u1 и u2, вследствие чего осуществляется плавное изменение фазы в.-ч. колебаний на выходе сумматора за время Т0 на +π /2 или -π /2 в зависимости от посылки входного модулирующего сигнала (0 или 1). Такое изменение фазы соответствует индексу частотной модуляции выходного сигнала m=0,5. Выбранная форма напряжений u1 и u2 на входах квадратурных амплитудно-фазовых модуляторов обеспечивает отсутствие сопутствующей AM выходного сигнала, т.е. в данном модуляторе отсутствует основной недостаток модуляторов CQPSK и π /4-DQPSK. Кроме того, данный модулятор, благодаря увеличению в два раза длительности посылок в каналах и отсутствию скачков фазы на границах посылок, формирует на выходе модулированное по частоте напряжение с компактным спектром. В этом модуляторе нет прямого воздействия на генератор несущей, благодаря чему сохраняется высокая стабильность несущего колебания и возможность оперативной смены несущей частоты, что важно для систем со скачкообразным изменением частоты.

Недостатком модулятора ММС является возможность получения только одного значения индекса частотной модуляции (m=0,5) и невозможность осуществления двухканальной частотной модуляции с комбинационным уплотнением каналов. Причинами этого являются, во-первых, использование в модуляторе сглаживающих напряжений указанного выше вида, которые не позволяют получать модулированные сигналы с другими индексами модуляции, и, во-вторых, структура модулятора, не позволяющая осуществлять комбинационное уплотнение каналов.

В заявляемом изобретении решается задача формирования фазовращающих напряжений для амплитудно-фазовых модуляторов квадратурных каналов частотного модулятора, обеспечивающих 4-частотную модуляцию без разрыва фазы с управлением двумя сигналами на входах модулятора. Это позволяет получить основной технический результат - возможность работы частотного модулятора в одноканальном режиме с выбором индекса модуляции m=0,5 или m=1,5 или в двухканальном режиме с частотной модуляцией при минимальном частотном сдвиге и без разрыва фазы. Такой технический результат расширяет функциональные возможности частотного модулятора и позволяет применять его в адаптивных системах связи, в том числе в сотовых.

Решение этой задачи достигается тем, что в частотный модулятор, содержащий генератор несущей, фазовращатель, два амплитудно-фазовых модулятора и сумматор, причем выход генератора несущей соединяется с первым входом первого амплитудно-фазового модулятора и с входом фазовращателя, выход фазовращателя соединяется с первым входом второго амплитудно-фазового модулятора, выходы амплитудно-фазовых модуляторов соединяются, соответственно, с первым и вторым входами сумматора, выход которого является выходом двухвходового частотного модулятора, включаются анализатор состояния фазовращающих напряжений, блок формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов, логический блок формирования управляющих напряжений для блока ключей и блок ключей, причем первые два входа логического блока формирования управляющих напряжений для блока ключей, на которые подаются двоичные модулирующие сигналы, являются входами двухвходового частотного модулятора, 4 других входа логического блока формирования управляющих напряжений для блока ключей соединяются, соответственно, с 4 выходами анализатора состояния фазовращающих напряжений, 8 выходов логического блока формирования управляющих напряжений для блока ключей соединяются с первыми 8 входами блока ключей, вторые 8 входов блока ключей соединяются с 8 выходами блока формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов, первый выход блока ключей соединяется со вторым входом первого амплитудно-фазового модулятора и с первым входом анализатора состояния фазовращающих напряжений, второй выход блока ключей соединяется со вторым входом второго амплитудно-фазового модулятора и со вторым входом анализатора состояния фазовращающих напряжений, а 3-й и 4-й входы анализатора состояния фазовращающих напряжений соединяются, соответственно, с двумя другими выходами блока формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов.

Анализатор состояния фазовращающих напряжений включает в себя два компаратора, два элемента НЕ, 4 элемента И, один элемент ИЛИ и 4 расширителя импульсов, причем входы компараторов являются, соответственно, первым и вторым входами анализатора состояний, выход первого компаратора соединяется со входом первого элемента НЕ и с первым входом первого элемента И, выход второго компаратора соединяется со входом второго элемента НЕ и с первым входом третьего элемента И, вторые входы 1 и 2-го элементов И соединяются с первым входом элемента ИЛИ, который является третьим входом анализатора состояний, вторые входы 3 и 4-го элементов И соединяются со вторым входом элемента ИЛИ, который является четвертым входом анализатора состояния фазовращающих напряжений, выход первого элемента НЕ соединяется с первым входом второго элемента И, выход второго элемента НЕ соединяется с первым входом четвертого элемента И, выходы всех элементов И соединяются, соответственно, с первыми входами расширителей импульсов, выход элемента ИЛИ соединяется со вторыми входами всех расширителей импульсов, а выходы расширителей импульсов являются выходами анализатора состояния фазовращающих напряжений.

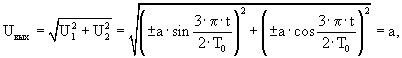

Блок формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов содержит задающий генератор, 5 делителей частоты на два, делитель частоты на 6, блок предустановки триггеров делителей частоты, две дифференцирующие цепи с ограничением по минимуму, два элемента Исключающее ИЛИ, 4 формирователя напряжения пилообразной формы и 4 формирователя напряжения синусоидальной формы, причем выход задающего генератора соединяется с первыми входами первого делителя частоты на два и делителя частоты на 6, выходы первою делителя частоты на два соединяются, соответственно, с первыми входами второго и третьего делителей частоты на два, выходы которых соединяются, соответственно, с первыми входами элементов Исключающее ИЛИ, первый выход делителя частоты на 6 соединяется с входами первой дифференцирующей цепи с ограничением по минимуму, второго формирователя напряжения пилообразной формы и четвертого делителя частоты на два, второй выход делителя частоты на 6 соединяется с входами второй дифференцирующей цепи с ограничением по минимуму, третьего формирователя напряжения пилообразной формы и пятого делителя частоты на два, первый выход блока предустановки триггеров делителей частоты соединяется со вторым входом первого делителя частоты на два, второй выход блока предустановки триггеров делителей частоты соединяется со вторыми входами второго, третьего, четвертого и пятого делителей частоты на два и со вторым входом делителя частоты на 6, выходы дифференцирующих цепей с ограничением по минимуму являются первыми двумя выходами блока формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов, а выход четвертого делителя частоты на два соединяется со вторым входом первого элемента Исключающее ИЛИ, выход пятого делителя частоты на два соединяется со вторым входом второго элемента Исключающее ИЛИ, выход первого элемента Исключающее ИЛИ соединяется со входом первого формирователя напряжения пилообразной формы, выход второго элемента Исключающее ИЛИ соединяется со входом четвертого формирователя напряжения пилообразной формы, выходы формирователей напряжения пилообразной формы соединяются, соответственно, с входами формирователей напряжения синусоидальной формы, прямой и инверсный выходы которых являются выходами блока формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов.

Логический блок формирования управляющих напряжений для блока ключей выполнен на двух элементах НЕ, 20 элементах И и восьми элементах ИЛИ, причем первый вход логического блока формирования управляющих напряжений для блока ключей соединяется со входом первого элемента НЕ и с первыми входами 3 и 4-го элементов И, второй вход логического блока формирования управляющих напряжений для блока ключей соединяется со входом второго элемента НЕ и со вторыми входами 2 и 4-го элементов И, выход первого элемента НЕ соединяется с первыми входами 1 и 2-го элементов И, выход второго элемента НЕ соединяется со вторыми входами 1 и 3-го элементов И, выход первого элемента И соединяется с первыми входами 5, 7, 9 и 11-го элементов И, выход второго элемента И соединяется с первыми входами 6, 8, 10 и 12-го элементов И, выход третьего элемента И соединяется с первыми входами 13, 15, 17 и 19-го элементов И, выход четвертого элемента И соединяется с первыми входами 14, 16, 18 и 20-го элементов И, третий вход логического блока формирования управляющих напряжений для блока ключей соединяется со вторыми входами 5, 6, 13 и 14-го элементов И, четвертый вход логического блока формирования управляющих напряжений для блока ключей соединяется со вторыми входами 7, 8, 15 и 16-го элементов И, пятый вход логического блока формирования управляющих напряжений для блока ключей соединяется со вторыми входами 9, 10, 17 и 18-го элементов И, шестой вход логического блока формирования управляющих напряжений для блока ключей соединяется со вторыми входами 11, 12, 19 и 20-го элементов И, выход 5-го элемента И соединяется с первыми входами 1 и 4-го элементов ИЛИ, выход 6-го элемента И соединяется с третьими входами 1 и 2-го элементов ИЛИ, выход 7-го элемента И соединяется с первыми входами 2 и 3-го элементов ИЛИ, выход 8-го элемента И соединяется с третьими входами 3 и 4-го элементов ИЛИ, выход 9-го элемента И соединяется со вторыми входами 1 и 2-го элементов ИЛИ, выход 10-го элемента И соединяется с четвертыми входами 2 и 3-го элементов ИЛИ, выход 11-го элемента И соединяется со вторыми входами 3 и 4-го элементов ИЛИ, выход 12-го элемента И соединяется с четвертыми входами 1 и 4-го элементов ИЛИ, выход 13-го элемента И соединяется с первыми входами 6 и 7-го элементов ИЛИ, выход 14-го элемента И соединяется со вторыми входами 7 и 8-го элементов ИЛИ, выход 15-го элемента И соединяется с четвертыми входами 5 и 8-го элементов ИЛИ, выход 16-го элемента И соединяется с вторыми входами 5 и 6-го элементов ИЛИ, выход 17-го элемента И соединяется с третьими входами 5 и 6-го элементов ИЛИ, выход 18-го элемента И соединяется с четвертыми входами 6 и 7-го элементов ИЛИ, выход 19-го элемента И соединяется с третьими входами 7 и 8-го элементов ИЛИ, выход 20-го элемента И соединяется с первыми входами 5 и 8-го элементов ИЛИ, а выходы элементов ИЛИ являются выходами анализатора состояний.

Блок ключей состоит из 8 аналоговых ключей, причем каждый из 8 управляющих входов блока ключей подключается к управляющему входу соответствующего аналогового ключа, каждый из 8 сигнальных входов блока ключей подключается к сигнальному входу соответствующего аналогового ключа, выходы аналоговых ключей 1, 3, 5 и 7-го соединяются между собой и образуют первый выход блока ключей, выходы аналоговых ключей 2, 4, 6 и 8-го также соединяются между собой и образуют второй выход блока ключей.

Совокупность признаков, характеризующих двухвходовой частотный модулятор в целом, обеспечивает получение технического результата во всех случаях, на которые испрашивается объем правовой защиты, а признаки, относящиеся к анализатору состояния фазовращающих напряжений, блоку формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов, логическому блоку формирования управляющих напряжений для блока ключей и блоку ключей, характеризуют его лишь в конкретной форме выполнения.

Все существенные признаки заявляемого изобретения находятся в причинно-следственной связи с достигаемым техническим результатом. Анализатор состояния фазовращающих напряжений определяет состояние фазовращающих напряжений на входах амплитудно-фазовых модуляторов в квадратурных каналах в каждый тактовый момент времени, логический блок формирования управляющих напряжений для блока ключей на основе результатов этого анализа и входных модулирующих сигналов определяет форму фазовращающих напряжений, которые должны поступать в каждый квадратурный канал в течение последующего тактового интервала, чтобы посылка выходного напряжения имела соответствующую частоту, и открывает необходимую пару ключей в блоке ключей (по одному для каждого квадратурного канала). Через открытые ключи необходимые фазовращающие напряжения с выходов блока формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсова поступают на амплитудно-фазовые модуляторы квадратурных каналов. При этом на выходе двухканального частотного модулятора формируются либо 2-частотные модулированные сигналы без разрыва фазы с индексом модуляции 0,5 или 1,5, либо 4-частотный (двухканальный) сигнал, также без разрыва фазы.

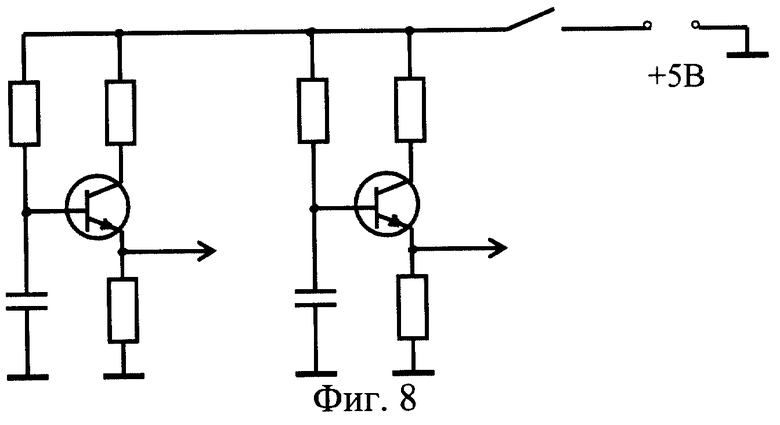

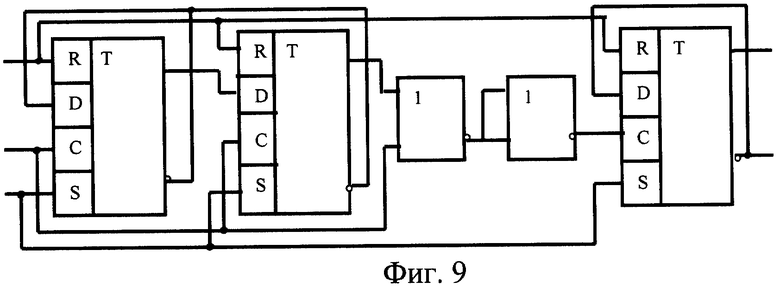

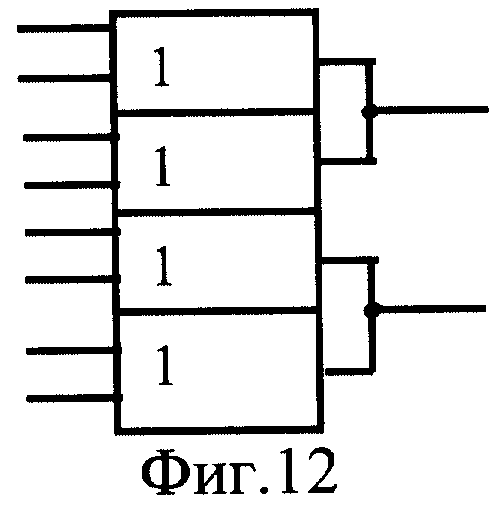

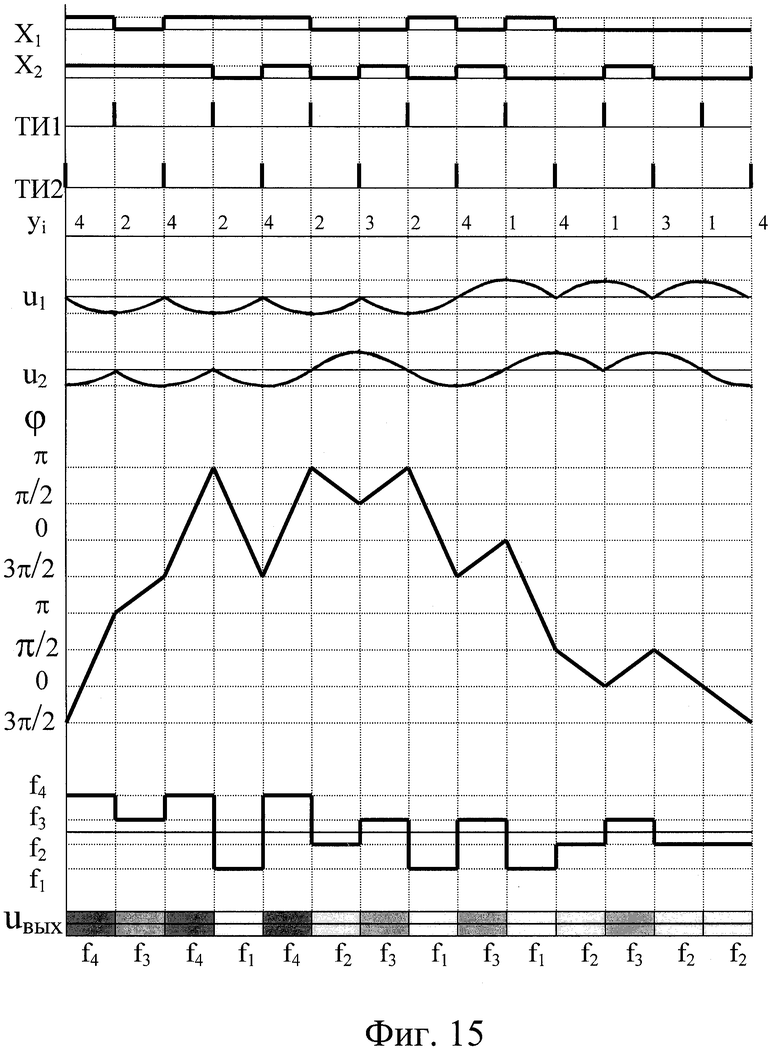

На фиг.1 представлена структурная схема двухвходового частотного модулятора, на фиг.2 - структурная схема анализатора состояния фазовращающих напряжений, на фиг.3 - структурная схема блока формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов, на фиг.4 - структурная схема логического блока формирования управляющих напряжений для блока ключей, на фиг.5 - структурная схема блока ключей, на фиг.6 - схема расширителя импульсов, ни фиг.7 - схема задающего генератора, на фиг.8 - схема блока предустановки триггеров делителей частоты, на фиг.9 - схема делителя частоты на 6, на фиг.10 - схема формирователя напряжения пилообразной формы и формирователя напряжения синусоидальной формы, на фиг.11 - схема дифференцирующей цепи с ограничением по минимуму, на фиг.12 - схема элементов 4ИЛИ, на фиг.13 - осциллограммы напряжений на выходах блока формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов, на фиг.14 - осциллограммы напряжений в блоке формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов, на фиг.15 - осциллограммы напряжений в двухвходовом частотном модуляторе.

Двухвходовой частотный модулятор содержит анализатор 1 состояния фазовращающих напряжений, блок 2 формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов, логический блок 3 формирования управляющих напряжений для блока ключей, блок 4 ключей, первый амплитудно-фазовый модулятор 5, второй амплитудно-фазовый модулятор 6, фазовращатель 7, генератор 8 несущей и сумматор 9. Анализатор 1 состояния фазовращающих напряжений содержит компараторы 10 и 11, элементы 12 и 13 НЕ, элементы 14-17 И, элемент 18 ИЛИ и расширители 19-22 импульсов. Блок 2 формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов содержит задающий генератор 23, блок 24 предустановки триггеров делителей частоты, делители 25, 26, 28, 29 и 33 частоты на два, делитель 27 частоты на 6, дифференцирующие цепи 31 и 32 с ограничением по минимуму, элементы 30 и 34 Исключающее ИЛИ, формирователи 35, 37, 39 и 41 напряжения пилообразной формы и формирователи 36, 38, 40 и 42 напряжения синусоидальной формы. Логический блок 3 формирования управляющих напряжений для блока ключей содержит элементы 43 и 44 НЕ, элементы 45-64 И и элементы 65-72 ИЛИ. Блок 4 ключей содержит аналоговые ключи 73-80.

Первый и второй входы логического блока 3 формирования управляющих напряжений для блока ключей (см. фиг.4, входы элементов 43 и 44 НЕ), на которые подаются двоичные модулирующие сигналы, являются входами частотного модулятора. Четыре других входа логического блока формирования управляющих напряжений для блока ключей соединяются с 4 выходами анализатора 1 состояний, при этом выход расширителя 19 импульсов соединяется (см. фиг.2 и 4) со вторыми входами элементов 49, 50, 57 и 58 И, выход расширителя 20 импульсов соединяется со вторыми входами элементов 51, 52, 59 и 60 И, выход расширителя 21 импульсов соединяется со вторыми входами элементов 53, 54, 61 и 62 И, выход расширителя 22 импульсов соединяется со вторыми входами элементов 55, 56, 63 и 64 И. 8 выходов логического блока 3 формирования управляющих напряжений для блока ключей соединяются с 8 управляющими входами блока 4 ключей, при этом выходы элементов 65-72 ИЛИ соединяются, соответственно, с управляющими входами аналоговых ключей 73-80. Первый выход блока 4 ключей соединяется со вторым входом амплитудно-фазового модулятора 5 и с первым входом анализатора 1 состояния фазовращающих напряжений, при этом выходы ключей 73, 75, 77 и 79 соединяются с входом компаратора 10 и со вторым входом амплитудно-фазового модулятора 5. Второй выход блока 4 ключей соединяется со вторым входом амплитудно-фазового модулятора 6 и со вторым входом анализатора 1 состояния фазовращающих напряжений, при этом выходы ключей 74, 76, 78 и 80 соединяются с входом компаратора 11 и со вторым входом амплитудно-фазового модулятора 6. Входы 3 и 4 анализатора 1 состояния фазовращающих напряжений соединяются с двумя выходами блока 2 формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов, при этом первый вход элемента 18 ИЛИ соединяется с выходом дифференцирующей цепи 32 с ограничением по минимуму, а второй вход элемента 18 ИЛИ соединяется с выходом дифференцирующей цепи 31 с ограничением по минимуму. Восемь других выходов блока формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов 2 соединяются с восемью входами блока 4 ключей, при этом первый выход формирователя 38 соединяется с сигнальным входом аналогового ключа 73, первый выход формирователя 40 соединяется с сигнальным входом аналогового ключа 74, второй выход формирователя 38 соединяется с сигнальным входом аналогового ключа 75, второй выход формирователя 40 соединяется с сигнальным входом аналогового ключа 76, первый выход формирователя 36 соединяется с сигнальным входом аналогового ключа 77, второй выход формирователя 42 соединяется с сигнальным входом аналоговою ключа 78, второй выход формирователя 36 соединяется с сигнальным входом аналогового ключа 79, первый выход формирователя 42 соединяется с сигнальным входом аналогового ключа 80.

Первый вход анализатора 1 состояния фазовращающих напряжений соединяется (см. фиг.2) с входом компаратора 10, второй вход анализатора 1 состояния фазовращающих напряжений соединяется с входом компаратора 11, выход компаратора 10 соединяется с входом элемента 12 НЕ и с первым входом элемента 14 И, выход компаратора 11 соединяется с входом элемента 13 НЕ и с первым входом элемента 16 И, вторые входы элементов 14 и 15 И соединяются с первым входом элемента 18 ИЛИ, который является третьим входом анализатора 1 состояния фазовращающих напряжений, вторые входы элементов 16 и 17 И соединяются со вторым входом элемента 18 ИЛИ, который является четвертым входом анализатора состояния фазовращающих напряжений, выход элемента 12 НЕ соединяется с первым входом элемента 15 И, выход элемента 13 НЕ соединяется с первым входом элемента 17 И, выходы элементов 14-17 И соединяются, соответственно, с первыми входами расширителей 19-22 импульсов, выход элемента 18 ИЛИ соединяется со вторыми входами всех расширителей импульсов, а выходы расширителей импульсов являются выходами анализатора состояния фазовращающих напряжений.

В блоке 2 формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов выход задающего генератора 23 (см. фиг.3) соединяется с входом делителя 25 частоты на два и с входом делителя 27 частоты на 6, выходы делителя 25 частоты на два соединяются, соответственно, с входами делителей 26 и 28 частоты на два, выходы которых соединяются, соответственно, с первыми входами элементов 30 и 34 Исключающее ИЛИ, первый выход делителя 27 частоты на 6 соединяется с входами дифференцирующей цепи 31 с ограничением по минимуму, формирователя 37 напряжения пилообразной формы и с первым входом делителя 29 частоты на два, второй выход делителя 27 частоты на 6 соединяется с входами дифференцирующей цепи 32 с ограничением по минимуму, формирователя 39 напряжения пилообразной формы и с первым входом делителя 33 частоты на два, первый выход блока 24 предустановки триггеров делителей частоты соединяется со вторым входом делителя 25 частоты на два, второй выход блока предустановки триггеров делителей частоты соединяется со вторыми входами делителей 26, 28, 29 и 33 частоты на два и вторым входом делителя 27 частоты на 6, выходы дифференцирующих цепей 31 и 32 с ограничением по минимуму являются первыми двумя выходами блока формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов, выход делителя 29 частоты на два соединяется со вторым входом элемента 30 Исключающее ИЛИ, выход делителя 33 частоты на два соединяется со вторым входом элемента 34 Исключающее ИЛИ, выход элемента 30 Исключающее ИЛИ соединяется со входом формирователя 35 напряжения пилообразной формы, выход элемента 34 Исключающее ИЛИ соединяется с входом формирователя 41 напряжения пилообразной формы, выходы формирователей 35,37,39 и 41 напряжения пилообразной формы соединяются, соответственно, с входами формирователей 36, 38, 40 и 42 напряжения синусоидальной формы, прямой и инверсный выходы которых являются выходами блока формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов.

Первый вход логического блока 3 формирования управляющих напряжений для блока ключей соединяется (см. фиг.4) с входом элемента 43 НЕ и с первыми входами элементов 47 и 48 И, второй вход логического блока 3 формирования управляющих напряжений для блока ключей соединяется с входом элемента 44 НЕ и с вторыми входами элементов 46 и 48 И, выход элемента 43 НЕ соединяется с первыми входами элементов 45 и 46 И, выход элемента 44 НЕ соединяется с вторыми входами элементов 45 и 47 И, выход элемента 45 И соединяется с первыми входами элементов 49, 51, 53 и 55 И, выход элемента 46 И соединяется с первыми входами элементов 50, 52, 54 и 56 И, выход элемента 47 И соединяется с первыми входами элементов 57, 59, 61 и 63 И, выход элемента 48 И соединяется с первыми входами элементов 58, 60, 62 и 64 И, вторые входы элементов 49, 50, 57 и 58 И соединяются между собой и являются третьим входом логического блока 3 формирования управляющих напряжений для блока ключей, вторые входы элементов 51, 52, 59 и 60 И соединяются между собой и являются четвертым входом логического блока 3 формирования управляющих напряжений для блока ключей, вторые входы элементов 53, 54, 61 и 62 И соединяются между собой и являются пятым входом логического блока 3 формирования управляющих напряжений для блока ключей, вторые входы элементов 55, 56, 63 и 64 И соединяются между собой и являются шестым входом логического блока 3 формирования управляющих напряжений для блока ключей, выход элемента 49 И соединяется с первыми входами элементов 65 и 68 ИЛИ, выход элемента 50 И соединяется с третьими входами элементов 65 и 66 ИЛИ, выход элемента 51 И соединяется с первыми входами элементов 66 и 67 ИЛИ, выход элемента 52 И соединяется с третьими входами элементов 67 и 68 ИЛИ, выход элемента 53 И соединяется со вторыми входами элементов 65 и 66 ИЛИ, выход элемента 54 И соединяется с четвертыми входами элементов 66 и 67 ИЛИ, выход элемента 55 И соединяется со вторыми входами элементов 67 и 68 ИЛИ, выход элемента 56 И соединяется с четвертыми входами элементов 65 и 68 ИЛИ, выход элемента 57 И соединяется с первыми входами элементов 70 и 71 ИЛИ, выход элемента 58 И соединяется со вторыми входами элементов 71 и 72 ИЛИ, выход элемента 59 И соединяется с четвертыми входами элементов 69 и 72 ИЛИ, выход элемента 60 И соединяется со вторыми входами элементов 69 и 70 ИЛИ, выход элемента 61 И соединяется с третьими входами элементов 69 и 70 ИЛИ, выход элемента 62 И соединяется с четвертыми входами элементов 70 и 71 ИЛИ, выход элемента 63 И соединяется с третьими входами элементов 71 и 72 ИЛИ, выход элемента 64 И соединяется с первыми входами элементов 69 и 72 ИЛИ, а выходы элементов ИЛИ являются выходами логического блока 3 формирования управляющих напряжений для блока ключей.

Восемь управляющих входов блока 4 ключей (фиг.5) соединяются, соответственно, с управляющими входами аналоговых ключей 73-80, 8 сигнальных входов блока 4 ключей соединяются, соответственно, с сигнальными входами аналоговых ключей 73-80, выходы аналоговых ключей 73, 75, 77 и 79 соединяются между собой и образуют первый выход блока 4 ключей, выходы аналоговых ключей 74, 76, 78 и 80 также соединяются между собой и образуют второй выход блока 4 ключей.

Большинство функциональных узлов частотного модулятора выполняется на ИМС: 2-входовые элементы 14-17, 45-64 И - К1533ЛИ1; 2-входовой элемент 18 ИЛИ - КР1533ЛЛ1; расширители 19-22 импульсов - на RSD-триггерах типа КР1533ТМ2 и инверторах КР1533ЛН1 по схеме фиг.6, задающий генератор 23 может быть выполнен на ИМС КР531ГГ1 по схеме фиг.7, блок 24 предустановки триггеров делителей частоты может быть выполнен по схеме фиг.8 на транзисторах КТ3102Г, делители 25, 26, 28, 29 и 33 частоты на два могут быть выполнены на RSD-триггерах К1533ТМ2; делитель 27 частоты на 6 для получения меандра на выходе выполняется в виде последовательного включения делителей на 3 и на 2 по схеме фиг.9 с использованием перед выходным делителем на два формирующих элементов 2ИЛИ-НЕ КР1533ЛЕ1; формирователь напряжения пилообразной формы (ФНП) выполняется на интегрирующей RC-цепи (с буферным усилителем на операционном усилителе, например, КР140УД8). Формирователь напряжения синусоидальной формы (ФНС) выполняется по схеме, представленной в книге: Граф Р. Электронные схемы: 1300 примеров: Пер. с англ. - М.: Мир, 1989, 688 с., ил., с.618; схема функционального узла, включающего в себя ФНП с буферным усилителем и ФНС, представлена на фиг.10; дифференцирующие цепи 31 и 32 с ограничением по минимуму можно выполнить на RC-цепях с элементами И К1533ЛИ1 в качестве ограничителей по минимуму, устраняющих отрицательные импульсы на выходах дифференцирующих цепей (фиг.11), 4-входовые элементы 65-72 ИЛИ - К155ЛЛ1 (объединяя выходы у двух элементов 2ИЛИ по схеме фиг.12), элементы 12, 13, 43 и 44 НЕ - КР1533ЛН1, элементы 30 и 34 Исключающее ИЛИ - К155ЛП5, аналоговые ключи 73-80 выполняются на ИМС КР590КН6, компараторы 10, 11 - К554САЗ.

Работа частотного модулятора осуществляется следующим образом.

Блок формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов 2 создает 8 непрерывных периодических последовательностей S1...S8, из элементов которых формируются фазовращающие напряжения u1 и u2, и две последовательности тактовых импульсов ТИ1 и ТИ2, следующих с периодом 2Т0 и взаимно смещенных на время T0. Форма сигналов, формируемых блоком формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов, показана на фиг.13. Сигналы S1-S4 имеют частоту Ω 1=π /(2· T0), а сигналы S5-S8 имеют частоту Ω 2=3π /(2· Т0). С тактовыми импульсами последовательности ТИ1 совпадают максимумы положительных и отрицательных значений сигналов S1, S3, S5 и S7, а с тактовыми импульсами последовательности ТИ2 совпадают максимумы положительных и отрицательных значений сигналов S2, S4, S6 и S8. Такое взаимное фазирование сигналов и тактовых импульсов, показанное на фиг.13, обеспечивается структурой построения блока 2 формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов (фиг.3) и использованием предварительной установки триггеров делителей частоты с помощью блока 24 предустановки триггеров делителей частоты. Форма сигналов в блоке 2 формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов представлена на временных диаграммах фиг.14. Задающий генератор 23 формирует меандр с длительностью элементов Т0/12, где Т0 - длительность посылок двоичного сигнала на входе модулятора (осциллограмма u23). Форма напряжений на выходах делителей частоты показана на фиг.14: u25-1 и u25-2 - напряжения на прямом и инверсном выходах делителя 25 частоты на два, u27-1 и u27-2 - напряжения на прямом и инверсном выходах делителя 27 частоты на 6; u26, u28, u29 и u33 - напряжения на выходах соответствующих делителей частоты на два. Дифференцирование с ограничением по минимуму напряжения u27-1 дает последовательность тактовых импульсов ТИ2, а дифференцирование с ограничением по минимуму напряжения u27-2 дает последовательность тактовых импульсов ТИ1. Осциллограммы u30 и u34 на фиг.14 показывают форму напряжений на выходах элементов 30 и 34 Исключающее ИЛИ. Формирователи напряжений пилообразной формы (ФНП) из прямоугольных посылок на их входах образуют напряжения, форма которых показана на осциллограммах u35, u37,u39 и u41. Из этих напряжений формирователи напряжений синусоидальной формы (ФНС) создают выходные напряжения блока формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов: на прямом и инверсном выходах ФНС 36 (u36-1 и u36-2) - сигналы S5 и S7, на прямом и инверсном выходах ФНС 38 (u38-1 и u38-2) - сигналы S1 и S3, на прямом и инверсном выходах ФНС 40 (u40-1 и u40-2) - сигналы S2 и S4, на прямом и инверсном выходах ФНС 42 (u42-1 и u42-2) - сигналы S8 и S6.

Блок предустановки триггеров делителей частоты, схема которого показана на фиг.8, вместе с делителем 25 частоты на два обеспечивает синхронизацию первоначального срабатывания делителей 26, 28, 29 и 33 частоты на 2 и делителя 27 частоты на 6 и необходимое взаимное расположение выходных сигналов на оси времени в процессе работы. Это обеспечивается следующим образом. При включении питания заряжаются конденсаторы в базовых цепях транзисторов (фиг.8). Постоянная времени цепи заряда второго конденсатора меньше, чем первого, и заданный уровень положительного напряжения на выходе второго транзистора появляется раньше, чем первого. Напряжение с выхода второго транзистора поступает на входы R триггеров в делителях 26, 28, 29 и 33 частоты на 2 и в делителе 27 частоты на 6 и устанавливает эти триггеры в одинаковое (нулевое) исходное состояние. После этого заданный уровень выходного напряжения появляется на выходе первого транзистора, это напряжение подается на вход R делителя 25 частоты на два и обеспечивает его рабочий режим (режим деления частоты). Первые же положительные перепады напряжения на выходах этого делителя обеспечат переключение триггеров в остальных делителях частоты, т.е. синхронизм работы этих делителей.

Анализатор 1 состояния фазовращающих напряжений определяет напряжения u1 и u2 на выходах блока 4 ключей в тактовые моменты и по их значениям выносит решение о состоянии этих выходов. Выделяются 4 различающихся состояния, в том числе 2 состояния для тактового момента, когда действует импульс ТИ1, и 2 состояния для момента, когда действует ТИ2:

1. ТИ1, u1=+a, u2=0; 2. ТИ1, u1=-а, u2=0;

3. ТИ2, u1=0, u2=+a; 4. ТИ2, u1=0, u2=-а.

При этом учитывается, что если в некоторый тактовый момент одно из напряжений u1 или u2 равно +a или -а, то второе напряжение обязательно равно нулю. В анализаторе 1 состояния фазовращающих напряжений (фиг.2) компараторы 10 и 11 преобразуют двухполярные сигналы u1 и u2 в однополярные импульсы с логическими уровнями. Порог срабатывания компараторов устанавливается на уровне логического нуля (0,2-0,4 В). Элементы 12 и 13 НЕ инвертируют сигналы на выходах компараторов; при этом на первые входы пары элементов 14 и 15 И и пары элементов 16 и 17 И поступают взаимно инверсные напряжения. Если в данный тактовый момент времени действует импульс тактовой последовательности ТИ1, а эта последовательность подается на верхний по схеме фиг.2 элемент 18 ИЛИ, то этот импульс поступает на выход одного из первой пары элементов И - 14 или 15. Если же в данный тактовый момент действует тактовый импульс последовательности ТИ2, то этот импульс выделится на выходе одного из элементов другой пары элементов И - 16 или 17. Таким образом, в каждый тактовый момент появляется короткий импульс на выходе одного из четырех (14-17) элементов И, определяющий одно из указанных выше 4 состояний напряжений u1 и u2 на выходах блока ключей. Последующие расширители 19-22 импульсов формируют из коротких импульсов единичные посылки длительностью Т0. Появление единичной посылки на выходе расширителя 19 импульсов свидетельствует о первом состоянии напряжений u1 и u2, появление единичной посылки на выходе расширителя 20 свидетельствует о втором состоянии напряжений u1 и u2, на выходе расширителя 21 - о третьем состоянии, на выходе расширителя 22 - о четвертом состоянии. В элементе 18 ИЛИ объединяются последовательности ТИ1 и ТИ2 и создается последовательность коротких тактовых импульсов, следующих с периодом Т0.

Непосредственное управление работой ключей блока 4 осуществляет логический блок 3 формирования управляющих напряжений для блока ключей. Исходя из значений напряжений u1 и u2 в заданный тактовый момент, определяющих значение фазы выходного напряжения модулятора в этот момент (это определяет анализатор состояния фазовращающих напряжений), и действующих модулирующих сигналов в последующий тактовый интервал времени, логический блок формирования управляющих напряжений для блока ключей 2 формирует управляющие напряжения, поступающие на управляющие входы аналоговых ключей 73-80, и обеспечивает открывание необходимой пары аналоговых ключей в блоке 4 ключей. При этом учитывается задаваемый манипуляционный код, определяющий соответствие между комбинацией посылок входных сигналов uc1 и uc2, передаваемых в заданный тактовый интервал, и частотой выходного напряжения модулятора. В частотном модуляторе принят следующий манипуляционный код:

Здесь принято:

f1=f0-3· fд=f0-3/(4· Т0), f2=f0-fд=f0-1/(4· Т0),

f3=f0+fд=f0+1/(4· T0), f4=f0+3· fд=f0+3/(4· T0),

f0 - несущая частота, обеспечиваемая генератором 8 несущей.

Достоинством этого манипуляционного кода является то, что при подаче на первый вход модулятора уровня логического нуля манипуляция по второму входу обеспечит использование только частот f2 и f3, т.е. одноканальную передачу с индексом модуляции m=0,5, а при подаче на первый вход уровня логической единицы и манипуляции по второму входу используются частоты f1 и f4, что обеспечивает одноканальную передачу с индексом m=1,5. При подаче на оба входа модулирующих сигналов обеспечится двухканальная передача с комбинационным уплотнением каналов.

Для обеспечения своих функций при выбранном манипуляционном коде логический блок 3 формирования управляющих напряжений для блока ключей должен иметь следующую таблицу состояний.

Таблица состояний логического блока 3 формирования управляющих напряжений для блока ключей

В этой таблице X1 и Х2 - значения входных модулирующих посылок uc1 и uc2 на входах 1 и 2 логического блока 3 формирования управляющих напряжений для блока ключей, являющихся входами модулятора; Y1 - Y4 - логические уровни на выходах анализатора 1 состояния; Z1, Z3, Z5, Z7 - логические уровни на выходах элементов, соответственно, 65, 67, 69, 71 ИЛИ; Z2, Z4, Z6, Z8 - логические уровни на выходах элементов, соответственно, 66, 68, 70, 72 ИЛИ логического блока 3 формирования управляющих напряжений для блока ключей. Структура построения логического блока 3 формирования управляющих напряжений для блока ключей (фиг.4) обеспечивает реализацию этой таблицы состояний.

Работа двухвходового частотного модулятора основана на плавном повороте вектора выходного напряжения без разрыва фазы на границах посылок в соответствии с двоичными сигналами на входе модулятора. За время одной посылки вектор выходного напряжения поворачивается на угол ±π /2, что соответствует девиации частоты fд=1/(4· Т0) и индексу частотной модуляции m=0,5 (минимальный сдвиг частоты, как в сигнале ММС), или на угол ±3π /2, что соответствует девиации частоты fд=3/(4-Т0) и индексу частотной модуляции m=1,5. Частоты посылок при этом принимают значения f0±1/(4· Т0) и f0±3/(4· Т0).

Необходимый поворот вектора осуществляется подбором формы фазовращающих напряжений u1 и u2 на входах амплитудно-фазовых модуляторов 5 и 6 (фиг.1). Если фазовращающие напряжения за время одной посылки изменяются с частотой π /(2· Т0) и имеют взаимный фазовый сдвиг на ±π /2, т.е., например,

u1=±a· sin(π · t/2· T0), u2=±a· cos(π · t/2· T0)

или

u1=±a· cos(π · t/2· T0), u2=±a· sin(π · t/2· T0),

то за время одной посылки фаза выходного напряжения модулятора изменится на +π /2 или -π /2 (так же, как в модуляторе ММС). Если же фазовращающие напряжения изменяются с частотой 3π /(2· Т0) и также имеют взаимный фазовый сдвиг на ±π /2, то за время посылки Т0 фаза выходного напряжения изменится на +3π /2 или - 3π /2. Таким образом, выбором формы (частоты и фазы) пары фазовращающих напряжений u1 и u2 на входах амплитудно-фазовых модуляторов 5 и 6 осуществляется необходимый поворот фазы выходного напряжения за время каждой посылки и формируется посылка на выходе модулятора с необходимой частотой.

Принцип работы двухвходового частотного модулятора поясняется временными диаграммами фиг.15. При включении двухвходового частотного модулятора блок 2 формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов формирует 8 последовательностей сигналов Si и две последовательности тактовых импульсов (фиг.14). Каждый из сигналов Si поступает на сигнальный вход соответствующего ключа в блоке 4 ключей. Первоначально все ключи закрыты, напряжения на их выходах u1 и u2 равны нулю. На выходах компараторов 10 и 11 напряжения также равны нулю, а на выходах инверторов 12 и 13 будут напряжения с уровнем логической единицы. При поступлении тактового импульса на вход 3 или 4 анализатора 1 состояния фазовращающих напряжений (входы элемента 18 ИЛИ) появится тактовый импульс на выходе одного из элементов И - 15 или 17, в зависимости от того, какой импульс (ТИ1 или ТИ2) поступит первым. Допустим, что первым пришел импульс последовательности ТИ2, и тактовый импульс появился на выходе элемента 17 И. При этом появится единичная посылка длительностью Т0 на выходе расширителя 22 импульсов, что соответствует, как указывалось выше, 4-му состоянию напряжений u1 и u2. Номера состояний в каждый тактовый момент указаны на фиг.15 (строка уi). С выхода расширителя 22 импульсов единичная посылка поступает на вторые входы элементов 55, 56, 63 и 64 И логического блока 3 формирования управляющих напряжений для блока ключей, и только эти четыре элемента активизированы в данный тактовый интервал. Предположим, что данный тактовый интервал соответствует первым посылкам модулирующих сигналов. В этот тактовый интервал на модулирующих входах Х1 и X2 (uc1 и uc2) действуют единичные посылки (см. фиг.15). Единичная посылка X1 через первый вход логического блока 3 формирования управляющих напряжений для блока ключей (вход элемента 43 НЕ) поступает на первые входы элементов 47 и 48 И, а единичная посылка Х2 через второй вход логического блока 3 формирования управляющих напряжений для блока ключей поступает на вторые входы элементов 46 и 48 И. Таким образом, единичные посылки окажутся на обоих входах элемента 48 И, и на выходе этого элемента появится единичная посылка, которая поступит на первые входы элементов 58, 60, 62 и 64 И. При этом единичные посылки окажутся на обоих входах элемента 64 И, поэтому с выхода этого элемента единичная посылка через элементы 69 и 72 ИЛИ поступит на 5-й и 8-й (по схеме) выходы логического блока 3 формирования управляющих напряжений для блока ключей. Далее эта посылка поступит на управляющие входы аналоговых ключей 77 и 80 в блоке 4 ключей; эти ключи откроются, и через них пройдут сигналы, соответственно, S5 и S8 в определенных фазах. Эти фазы определяются по временным диаграммам сигналов на фиг.13. Соответствующие сигналы отображены на диаграммах, соответственно, u1 и u2 (фиг.15) в первом тактовом интервале.

В конце первого тактового интервала, т.е. во второй тактовый момент, состояние напряжений u1 и u2 вновь оценивается в анализаторе 1 состояния фазовращающих напряжений. На входе 1 анализатора 1 состояния фазовращающих напряжений, куда подается напряжение u1, напряжение равно -а, поэтому на выходе компаратора 10 появится нулевое напряжение, на выходе элемента 12 НЕ появится единичное напряжение, которое активизирует элемент 15 И. В этот тактовый момент появляется тактовый импульс последовательности ТИ1, который через третий вход анализатора 1 состояния фазовращающих напряжений поступает на вторые входы элементов 14 и 15 И. На элементе 15 И окажется совпадение единичных напряжений, и тактовый импульс поступит на выход элемента 15 И. На выходе расширителя 20 импульсов при этом сформируется единичный импульс длительностью Т0 (второе состояние напряжений u1 и u2). Этот импульс поступает на 4-й вход логического блока 3 формирования управляющих напряжений для блока ключей и далее на вторые входы элементов 51, 52, 59 и 60 И этого блока. На 1-й и 2-й входы логического блока 3 формирования управляющих напряжений для блока ключей в этот тактовый интервал действуют входные модулирующие сигналы: нулевое напряжение X1 (uc1) действует на 1-й вход и единичное напряжение Х2 (uс2) - на 2-й вход. Нулевая посылка X1 через элемент 43 НЕ поступает на первые входы элементов 45 и 46 И. Единичная посылка Х2 воздействует на вторые входы элементов 46 и 48 И. На входах элемента 46 И окажется совпадение единичных напряжений, вследствие чего тактовый импульс с выхода этого элемента поступает на первые входы элементов 50, 52, 54 и 56 И. На входах элемента 52 И обеспечивается совпадение единичных напряжений, и на выходе этого элемента появится единичный импульс длительностью Т0; такие же импульсы появятся на выходах элементов 67 и 68 ИЛИ, т.е. на 3-м и 4-м (по схеме) выходах логического блока 3 формирования управляющих напряжений для блока ключей. Эти импульсы поступают на управляющие входы ключей 75 и 76 (3-го и 4-го по счету) и открывают эти ключи. Через ключ 75 пройдет элемент сигнала S3, а через ключ 76 - элемент сигнала S4. Форма этих сигналов, определенная согласно фиг.13 для тактового интервала, действующего после тактового момента ТИ1, показана на фиг.15 (u1 и u2, тактовый интервал 2).

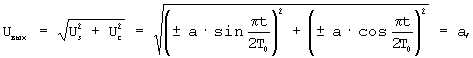

Продолжая аналогичные рассуждения для последующих тактовых интервалов, получим временные диаграммы фазовращающих напряжений u1 и u2, поступающих на входы амплитудно-фазовых модуляторов 5 и 6 двухвходового частотного модулятора. Далее обычным образом работают элементы 5-9 двухвходового частотного модулятора, входящие в ограничительную часть формулы изобретения. При этом напряжение u1, воздействуя на модулирующий вход первого амплитудно-фазового модулятора 5, изменяет амплитуду и фазу в.ч. напряжения на его выходе; в зависимости от полярности u1 фаза выходного напряжения амплитудно-фазового модулятора 5 может принимать значения 0 или π , а амплитуда изменяется по закону модулирующего напряжения. Напряжение u2 воздействует на модулирующий вход второго амплитудно-фазового модулятора 6 и также изменяет его амплитуду и фазу; фаза, в зависимости от полярности u2, может принимать значения π /2 или 3 π /2. Сложение выходных напряжений амплитудно-фазовых модуляторов в сумматоре 9 дает выходное напряжение модулятора. Амплитуда этого напряжения постоянна, т.к. определяется соотношениями:

- на частоте фазовращающего напряжения Ω 1=π /2T0

- на частоте фазовращающего напряжения Ω 2=3π /2Т0

а фаза линейно изменяется во времени за время действия каждой посылки:

- на частоте фазовращающего напряжения Ω 1=π /2T0

на частоте фазовращающего напряжения Ω 2=3π /2Т0

В зависимости от частоты напряжений u1 и u2 на данном тактовом интервале фаза выходного напряжения за время одной посылки может измениться на угол π /2 или 3π /2, что соответствует смещению частоты посылки от значения f0 на 1/(4Т0) или, соответственно, на 3/(4Т0). Значения частот посылок выходного напряжения модулятора указаны на временной диаграмме uвых фиг.15. Сопоставление комбинации передаваемых символов с частотой выходного напряжения модулятора на каждом тактовом интервале Т0 показывает, что между ними существует однозначное соответствие, определяемое вышеприведенным манипуляционным кодом. Таким образом, предлагаемый двухвходовой частотный модулятор обеспечивает 4-частотную ЧМ без разрыва фазы при одновременной передаче двух двоичных цифровых сигналов на основе комбинационного уплотнения с заданным манипуляционным кодом. Кроме того, двухвходовой частотный модулятор обеспечивает работу и в одноканальном режиме. При установке на модуляционном входе X1 уровня логического нуля модулятор работает по второму входу (X2), используя фазовращающие напряжения только с низкими частотами Ω 1 и формируя при этом на выходе 2-частотное ЧМ колебание без разрыва фазы с индексом модуляции 0,5. Если на входе X1 установить уровень логической единицы, то модулятор работает по второму входу и использует фазовращающие напряжения с частотами Ω 2; на выходе модулятора при этом формируется 2-частотное ЧМ колебание без разрыва фазы с индексом модуляции 1,5. Во всех режимах двухвходовой частотный модулятор обеспечивает компактный спектр выходного сигнала. Расчеты показывают, что при работе в двухканальном режиме реальная ширина спектра (по уровню мощности 99%), приходящаяся на один канал, составляет 1,27-V (незначительное увеличение по сравнению с ММС). Работа с индексом модуляции 1,5 дает реальную ширину спектра 2,92-V, т.е. трехкратное увеличение индекса модуляции потребовало увеличения полосы менее чем в 2,5 раза. Предлагаемый частотный модулятор обладает и другими достоинствами модулятора ММС, которые указаны выше.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРЕХЧАСТОТНЫЙ МОДУЛЯТОР | 2003 |

|

RU2239939C1 |

| ЧАСТОТНЫЙ МОДУЛЯТОР С РАЗДЕЛЕНИЕМ СПЕКТРА | 2003 |

|

RU2255415C1 |

| ЧАСТОТНЫЙ МОДУЛЯТОР С ЦЕЛОЧИСЛЕННЫМ ИНДЕКСОМ МОДУЛЯЦИИ | 2003 |

|

RU2255414C1 |

| Частотный модулятор | 1980 |

|

SU951641A1 |

| Когерентный демодулятор | 1979 |

|

SU855987A1 |

| МАЛОГАБАРИТНЫЙ РАДИОЛОКАТОР ТРАНСПОРТНОГО СРЕДСТВА | 1997 |

|

RU2117964C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ЧАСТОТЫ, ВИДА МОДУЛЯЦИИ И МАНИПУЛЯЦИИ ПРИНИМАЕМЫХ СИГНАЛОВ | 2006 |

|

RU2310870C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЧАСТОТЫ, ВИДА МОДУЛЯЦИИ И МАНИПУЛЯЦИИ ПРИНИМАЕМЫХ СИГНАЛОВ | 2012 |

|

RU2514160C2 |

| Демодулятор телеграфных сигналов | 1971 |

|

SU448588A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЧАСТОТЫ, ВИДА МОДУЛЯЦИИ И МАНИПУЛЯЦИИ ПРИНИМАЕМЫХ СИГНАЛОВ | 2007 |

|

RU2361225C1 |

Изобретение относится к технике радиосвязи и может применяться в системах подвижной наземной и спутниковой связи. Технический результат заключается в обеспечении возможности работы модулятора в одноканальном режиме с выбором индекса частотной модуляции m=0,5 или m=1,5 или в двухканальном режиме при минимальном частотном сдвиге и без разрыва фазы. Устройство содержит анализатор состояния фазовращающих напряжений (1), блок формирования непрерывных периодических последовательностей сигналов и последовательностей тактовых импульсов (2), логический блок формирования управляющих напряжений для блока ключей (3), блок ключей (4), два амплитудно-фазовых модулятора (5), (6), фазовращатель (7), генератор несущей (8), сумматор (9). 4 з.п. ф-лы, 1 табл., 15 ил.

| БАНКЕТ В.Л., и др., Цифровые методы в спутниковой связи, Москва, Радио и связь, 1988, с.39-40, рис.2.1б, 2.2 | |||

| ЧАСТОТНЫЙ МОДУЛЯТОР | 1989 |

|

RU2012150C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННОГО СИГНАЛА | 1996 |

|

RU2110145C1 |

| УСТРОЙСТВО ДЛЯ ФОРМОВАНИЯ ЧАСТОТНО-МОДУЛИРОВАННОГО СИГНАЛА | 1992 |

|

RU2039414C1 |

| US 2001016017, 23.08.2001. | |||

Авторы

Даты

2005-03-10—Публикация

2003-04-21—Подача