Изобретение относится к электросвязи, преимущественно к передаче данных с помощью частотно-модулированных сигналов.

Известно устройство формирования ЧМ сигнала [1] состоящее из эталонного генератора, смесителя, усилителя, ЧМ дискриминатора, блока выборки и хранения, сумматора, ключа и генератора. Принцип действия таких систем основан на перестройке характеристик генератора при воздействии входного манипулированного сигнала.

Наиболее близкой по технической сущности к предложенному объекту является устройство для формирования частотно-манипулированных сигналов [2]

Недостатки работы прототипа приводят к низкой достоверности принимаемых ЧМ сигналов.

Целью настоящего изобретения является увеличение помехоустойчивости принимаемых сигналов.

В устройство для формирования частотно-модулированного сигнала, содержащее генератор, первый выход которого соединен с первым входом первого делителя частоты с переменным коэффициентом деления, дешифратор, делитель частоты, выход которого соединен с входом полосового фильтра, выход которого является выходом устройства, введены второй, третий, делители частоты с переменным коэффициентом деления, первый, второй, третий постоянно-запоминающие устройства, реверсивный счетчик, первый, второй элементы И-НЕ и инвертор, причем второй и третий выход генератора соединен с первыми входами элементов И-НЕ, выходы которых соединены с входами реверсивного счетчика, выход которого соединен с входами дешифратора и всех постоянно-запоминающих устройств, первый, второй выходы первого постоянно-запоминающего устройства соединены с вторым и третьим выходами первого делителя частоты с переменным коэффициентом деления, выход которого соединен с первым входом второго делителя частоты с переменным коэффициентом деления, выход которого соединен с первым входом третьего делителя частоты с переменным коэффициентом деления, второй и третий входы которого и второй и третий входы второго делителя частот с переменными коэффициентами деления соединены соответственно с первым и вторым выходами третьего и второго постоянно-запоминающих устройств, выход третьего делителя частоты с переменным коэффициентом деления соединен с входом делителя частоты, второй вход первого элемента И-НЕ и вход инвертора являются информационным входом устройства, выход инвертора соединен с вторым входом второго элемента И-НЕ, первый, второй выходы дешифратора соединены с третьими входами первого и второго элементов И-НЕ.

На фиг. 1 изображено предлагаемое устройство, которое содержит генератор 1; делитель частоты 4; дешифратор 7; первый 8-1, второй 8-2, третий 8-3 делители частот с переменным коэффициентом деления; полосовой фильтр 9; первую 10-1, вторую 10-2 схемы И-НЕ; первое 11-1, второе 11-2, третье 11-3 постоянно запоминающее устройство; реверсивный счетчик 12, инвертор 10-3; первый 8-1 и второй 8-2 делители частот с переменным коэффициентом деления содержат каждый сумматор 13; первый 14 и второй 16 триггеры; счетчик 15; схему И-НЕ 17.

На фиг. 2 изображен третий 8-3 делитель частоты с переменным коэффициентом деления, содержащий счетчик 18; сумматор 19, первый 20, второй 21 триггеры.

Предлагаемое устройство работает следующим образом.

В данном устройстве протекает одновременно четыре процесса.

Первый процесс процесс формирования управляющих сигналов для плановой перестройки с одной частоты на другую. Он осуществляется с помощью первой 10-1, второй 10-2 схем И-НЕ, инвертора 10-3, реверсивного счетчика 12, дешифратора 7, трех 11-1, 11-2, 11-3 постоянных запоминающих устройств.

Второй и третий процессы идентичны друг другу. Они предполагают исключение одного тактового периода на заданном интервале. Эти процессы осуществляются в первом 8-1 и втором 8-2 делителях частот с переменным коэффициентом деления.

Наконец, четвертый процесс процесс деления входной частоты на переменный коэффициент деления. Он осуществляется с помощью 8-3 делителя частот с переменным коэффициентом деления.

Рассмотрим эти процессы более подробно.

Процесс формирования управляющих сигналов.

Сразу после включения устройства на информационный вход поступает информационный сигнал аi ∈0,1} Сигнал аi в инверторе 10-3 инвертируется. Сигналы со входа и выхода инвертора 10-3 соответственно подготавливают к работе первую 10-1 схему И-НЕ и закрывают схему 10-2 И-НЕ.

Тактовые импульсы со второго выхода генератора 1 одновременно поступают на первую 10-1 и вторую 10-2 схемы И-НЕ. При этом в любой момент времени открыта может быть только одна из них, либо могут быть закрыты обе схемы.

Как было показано выше, режимом открывания либо запирания первой 10-1 и второй 10-2 схем И-НЕ осуществляют информационный сигнал ai. Помимо этого, аналогичную операцию осуществляет дешифратор 7. Если реверсивный счетчик 12 достигнет максимально-возможного значения, то его состояние дешифруется дешифратором 7 и на его первом выходе формируется логический 0. Если же реверсивный счетчик достигнет минимально-возможного состояния, то на втором выходе дешифратора 7 формируется логический 0. Во всех остальных случаях на первом и втором выходах дешифратора 7 логическая 1.

Покажем, что будет при поступлении информационного сигнала на i-ом тактовом интервале при ai=1. Пусть в этот момент времени состояние реверсивного счетчика 7 минимально-возможное. Тогда вторая схема 10-2 И-НЕ закрыта сразу по двум входам: с выхода инвертора 10-3, и со второго выхода дешифратора 7. Первая 10-1 схема И-НЕ, в свою очередь, открыта информационным сигналом ai и сигналом с выхода дешифратора 7. Тактовые импульсы со второго выхода генератора начинают проходить через первую 10-1 схему И-НЕ и поступают на вход (+) реверсивного счетчика 12. Реверсивный счетчик 12 начинает увеличивать свое состояние от минимально-возможного до максимально-возможного. Как только реверсивный счетчик 12 достигнет максимально-возможного состояния, то его состояние дешифрируется дешифратором 7 и на его первом выходе появляется логический ⊘ который принудительно закрывает первую 10-1 схему И-НЕ. Таким образом, спустя определенный промежуток времени, который называется временем перестройки модулятора и первая 10-1, и вторая схемы 10-2 И-НЕ оказываются закрытыми. По-иному будет обстоять дело при поступлении на (i+1) тактовом интервале логического 0 (аi+1=0). Тактовые импульсы с выхода генератора 1 начинают проходить через вторую 10-2 схему И-НЕ на (-) вход реверсивного счетчика 12. Последний начинает уменьшать свое состояние. При достижении реверсивным счетчиком 12 минимально возможного состояния на втором выходе дешифратора 7 появится логический ⊘ который закрывает вторую схему 10-2 схему И-НЕ. Аналогично будут протекать процессы и при других информационных сигналах аi. Код состояния реверсивного счетчика 12 подается одновременно на адресные входы первого 11-1, второго 11-2 и третьего 11-3 постоянных запоминающих устройств и выдает код для управления трех делителей 8-1, 8-2, 8-3.

Покажем, как работает первый 8-1 делитель частот с переменным коэффициентом деления. Выходная частота на выходе ДПКД1 (блок 8-1) определяется выражением

f =f

=f =f

=f (1) Здесь fзг частота задающего генератора;

(1) Здесь fзг частота задающего генератора;

N определяет интервал входной последовательности, на длительности которого исключается один период;

К-код, формируемый первым 11-1 постоянным запоминающим устройством.

Пусть для приема требуется исключить один период входной последовательности из десяти. Тогда N 1010, а К=810; здесь и далее подстрочный индекс означает систему счисления.

В первом 11-1 ПЗУ для управления первым 8-1 делителем частот с переменным коэффициентом деления величина "К" выдается в обратном коде. Так как в прямом коде К 01002, то в обратном коде К 10112. Данный код подается на вход "В" сумматора 13. На вход "А" этого же сумматора 13 подается сигнал с выхода счетчика 15. Пусть счетчик 15 находится в исходном нулевом состоянии. Первый 14 триггер находится также в исходном состоянии, т.е. на выходе логический 0, а на  выходе логическая 1. Покажем как работает ДПКД1 (8-1) в случае, если второй 16 триггер находится принудительно в единичном состоянии, и когда принудительной установки нет. Принудительная установка осуществляется со второго выхода первого 11-1 ПЗУ подачей на установочный "S" вход второго 16 триггера единичного установочного потенциала. В этом случае на выходе второго 16 триггера постоянно будет логическая 1. Тактовые импульсы с выхода задающего генератора 1 поступают на вход счетчика 15 и изменяют его состояние. Как только состояние счетчика 15 достигнет величины К 01002, то на выходе переноса Р4 сумматора 13 появляется логическая 1.

выходе логическая 1. Покажем как работает ДПКД1 (8-1) в случае, если второй 16 триггер находится принудительно в единичном состоянии, и когда принудительной установки нет. Принудительная установка осуществляется со второго выхода первого 11-1 ПЗУ подачей на установочный "S" вход второго 16 триггера единичного установочного потенциала. В этом случае на выходе второго 16 триггера постоянно будет логическая 1. Тактовые импульсы с выхода задающего генератора 1 поступают на вход счетчика 15 и изменяют его состояние. Как только состояние счетчика 15 достигнет величины К 01002, то на выходе переноса Р4 сумматора 13 появляется логическая 1.

Сигнал переноса Р4 записывается в первый 14 триггер той же тактовой частотой fзг, что поступает и на вход счетчика 15. Причем, обязательным условием правильной работы делителей частот с переменным коэффициентом деления является то, что и счетчик 15, и первый 14 триггер должны работать по заднему фронту импульсной последовательности. Итак, счетчик 15 достигнет состояния 01002, когда на его тактовый вход поступит 8 тактовых импульсов. При поступлении 9 тактового импульса сигнал переноса Р4 записывается в первый 14 триггер. Так как сигнал Р4 поступает на информационный Д вход первого триггера 14, то, следовательно, на выходе формируется импульс логической 1. Сигнал с выхода первого 14 триггера принудительно обнуляет счетчик 15.

Кроме того, сигнал с Q выхода 14 триггера, который соответственно равен логическому 0, поступает на схему 17 И-НЕ, запрещая одному периоду прохождение тактовой частоты fзг на выход ДПКД1 (блок 8-1). При обнулении счетчика 15, его состояние становится равным 00002. Следовательно, на выходе переноса сумматора 13 сигнал логической 1 исчезает.Но данный сигнал будет записан в первый 14 триггер только 10 тактовым импульсом частоты fзг. После прихода 10 тактового импульса в первый 14 триггер записывается логический ⊘ и разблокируется работа счетчика 15. Таким образом, на 9 и 10 тактовые интервалы счетчик 15 не реагирует, так как находится в нуле. Начиная с 11 тактового интервала схема начинает свою работу вновь. Таким образом, на временном интервале, который задает код, подаваемый с первого 11-1 ПЗУ, делитель с переменным коэффициентом деления запрещает прохождение одному периоду входной частоты, и, следовательно, выходная частота определяется выражением (1).

В нашем конкретном случае на 10 тактовых интервалах входной частоты fзг запрещено прохождение одного периода. Помимо этого режима, первый 8-1 делитель частоты с переменным коэффициентом деления позволяет осуществить деление на половинный коэффициент деления, к примеру 10,510. В этом режиме со второго выхода первого 11-1 ПЗУ не поступает обнуляющий потенциал на "S" вход второго 16 триггера. Второй 16 триггер начинает работать в счетном режиме. Для этого на тактовый вход второго 16 триггера поступает сигнал с Q выхода первого 14 триггера. Таким образом, на Ро сумматора 13 поступает сигнал либо логического 0, либо логической 1. Если в j-том цикле работы на Ро идет логический 0 с выхода второго 16 триггера, то в (j+1) цикле работы на Ро поступает логическая 1. В (j+2) цикле вновь на Ро идет логический 0. Режим с дробным коэффициентом деления аналогичен предыдущему режиму, описанному выше. Разница лишь в том, что для рассмотренного случая, когда с Q выхода второго 16 триггера идет логическая 1 на Ро сумматора 13, то ДПКД 1 (8-1) исключает один тактовый интервал на длительности 10 периодов входной частоты. В случае, если на Ро поступает логический 0, то один тактовый интервал исключается на 11 тактовых периодах. В среднем получается, что исключается один период на 10,5 тактовых интервалах.

Второй 8-2 делитель частоты с переменным коэффициентом деления работает аналогично первому 8-1 делителю частоты с переменным коэффициентом деления. Интервал, на длительности которого исключается один период входной частоты второго 8-2 ДПКД задается во втором 11-2 постоянном запоминающем устройстве величиной К2; тогда на выходе второго 8-2 ДПКД частота определяется как

f =f

=f (2)

(2)

Второй делитель частоты 8-2 с переменным коэффициентом деления может работать в тех же режимах, что и первый 8-1, а именно: исключается один период их целого значения N2 и из половинного значения N2(N2=K2+2). Процесс исключения одного периода при N2 равных половинному значению задается сигналом второго выхода второго 11-2 ПЗУ на аналогичный второй 16 триггер второго 8-2 делителя.

Процесс деления на дробный коэффициент аналогичен.

Сигнал с выхода второго 8-2 ДПКД поступает на вход третьего 8-3 ДПКД. Отличие третьего 8-3 ДПКД от рассмотренных ранее 8-1 и 8-2 заключается лишь в том, что в отсутствии схемы И-НЕ выходной сигнал третьего ДПКД снимается с выхода триггера.

Выходная частота третьего 8-3 делителя частоты с переменным коэффициентом деления определяется выражением

f = f

= f (3) Здесь К3 коэффициент деления третьего 8-3 делителя.

(3) Здесь К3 коэффициент деления третьего 8-3 делителя.

Для уменьшения краевых искажений модуляции частотно-манипулированных сигналов в первом 8-1, втором 8-2 и третьем 8-3 делителях частот с переменным коэффициентом деления осуществляется в высокочастотной области, как минимум в 64 раза выше характеристической частоты передачи логического 0 или 1. Для того, чтобы согласовать работу перечисленных выше делителей с параметрами канала связи служит делитель частоты 4. Таким образом, на выходе делителя частоты 4 получена частота, величина которой определяется из выражения

fхар=f (4)

(4)

Здесь К1 и К2 интервалы, на которых исключается один период частоты;

К3 коэффициент деления третьего 8-3 ДПКД;

К4 коэффициент деления делителя частоты (К4 ≥ 64).

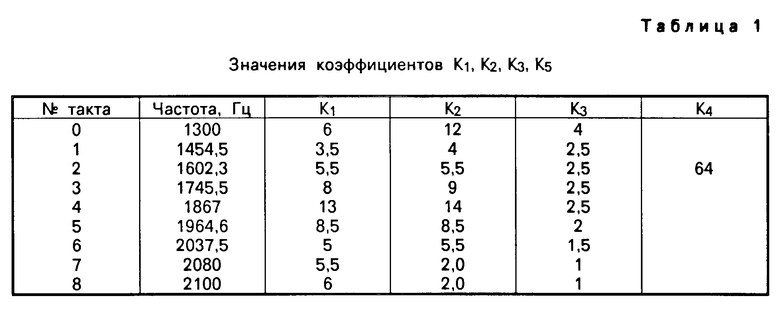

Как видно из описания, для правильной работы формирователя ЧМ сигнала, необходимо знать значения коэффициентов К1, К2, К3, К4. В табл. 1 приведены значения этих коэффициентов для скорости передачи В 1200 бит/с согласно ГОСТ 20855-83 и рекомендации МККТТ V21. Как видно из описания принципа работы формирователя ЧМ сигнала, производится плавный переход с одной частоты на другую без разрыва фазы. Это, в конечном счете, сужает спектр передаваемого ЧМ сигнала и повышает достоверность сигнала на приемной стороне.

Величины Кi должны храниться в первом 11-1, втором 11-2 и третьем 11-3 постоянных запоминающих устройствах. Их значения должны храниться в инверсном коде к примеру для выходной частоты 1454,5 Гц требуется согласно табл. 1 взять К13,510; К2 410; К 2,510. Целые части этих коэффициентов в двоичной системе счисления будут соответственно равны К1 00112; К2 01002; К3 00102. В первом 11-1 постоянном запоминающем устройстве запишется цифровая комбинация, равная 011002. Четыре младших разряда являются инверсным кодом величины К1. Старший разряд (логический 0) указывает на то, что К1 величина кратная 0,5. Аналогично во втором 11-2 ПЗУ запишется комбинация 010012. В качестве примера в табл. 2 приведены значения кодов, которые записаны в постоянных запоминающих устройствах.

Выходной сигнал делителя частоты 4 далее поступает через полосовой фильтр 9 в канал связи. Фильтр 9 фильтрует цифровой сигнал (меандр) и преобразует его в гармонический ЧМ сигнал.

Достоверность положительного эффекта доказывается вышеизложенным текстом, и результатами эксперимента.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ НАПРАВЛЕНИЙ ПЕРЕДАЧИ И ПРИЕМА В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 1992 |

|

RU2038702C1 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ НАПРАВЛЕНИЙ ПЕРЕДАЧИ И ПРИЕМА В ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 1993 |

|

RU2039415C1 |

| Цифровой частотный демодулятор | 1991 |

|

SU1817249A1 |

| Преобразователь частоты следования импульсов в код | 1991 |

|

SU1780037A1 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1829115A1 |

| Устройство синхронизации с фазовой автоподстройкой частоты | 1988 |

|

SU1700751A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННОГО СИГНАЛА | 1996 |

|

RU2110145C1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1363458A1 |

| Фазовый модулятор | 1986 |

|

SU1388974A2 |

| Формирователь сигналов с угловой модуляцией | 1985 |

|

SU1241411A1 |

Использование: в электросвязи при передаче частотно-манипулированных сигналов. Сущность изобретения: устройство содержит генератор 1, делитель частоты 4, дешифратор 7, делители частот 8.1, 8.2, 8.3 с переменным коэффициентом деления, полосовой фильтр 9, элементы И-НЕ 10.1, 10.2, 17, постоянные запоминающие устройства 11.1, 11.2, 11.3, реверсивный счетчик 12, сумматор 13, триггеры 14, 16, счетчик 15, инвертор 10.3. Цель изобретения увеличение помехоустойчивости принимаемых сигналов. 2 з.п. ф-лы, 2 ил. 2 табл.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для формирования частотно-манипулированного сигнала | 1987 |

|

SU1467783A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1995-07-09—Публикация

1992-07-08—Подача