Изобретение относится к технике радиосвязи и может быть использовано в радиопередающих и радиоприемных устройствах для формирования линейно-частотно-модулированного (ЛЧМ) сигнала.

Известны устройства формирования линейно-частотномодулированного сигнала (авт. св. СССР N 1677845, кл. H 03 C 3/08, 1991, авт.св. СССР N 1674345, кл. H 03 C 3/08, 1991, авт.св. СССР N 1631598, кл. H 03 C 3/08, 1991, в которых используются управляемые генераторы с различными системами подстройки частоты формируемого сигнала. Однако, использование в предлагаемых устройствах аналоговых элементов (управляемых генераторов, генераторов пилообразного напряжения, полосовых фильтров и т.п.) делает их чувствительными к внешним воздействиям (температуре окружающей среды, напряжению источников питания и пр.).

Наиболее близким к предлагаемому устройству является устройство формирования ЛЧМ сигнала по авт.св. N 1617621, кл. H 03 C 3/08, 1991. Данное устройство состоит из двух накапливающих сумматоров НС, комбинированного сумматора, двух блоков памяти, цифро-аналогового преобразователя ЦАП, переключателя, коммутатора, блока фильтров, делителя частоты на М, счетчика, генератора импульсов запуска, генератора импульсов, делителя частоты с переменным коэффициентом деления ДПКД, причем выход первого НС соединен с первым входом комбинационного сумматора, выход которого соединен со входом второго НС. Выход второго НС соединен со входом первого блока памяти, выход которого соединен со входом ЦАП. Выход ЦАП соединен с первым входом переключателя, а выход последнего соединен со входом коммутатора. Выход коммутатора соединен с входом блока фильтров, вход которого является выходом устройства. Выход генератора импульсов запуска соединен со вторыми входами первого НС, комбинационного сумматора, со входами счетчика и генератора импульсов. Выход генератора импульсов соединен со входами ДПКД и делителя частоты на М. Выход делителя частоты на М соединен с третьим входом первого НС и комбинационного сумматора. Выход счетчика соединен со вторым входом второго блока памяти. Первый, второй, третий и четвертый выходы первого блока памяти соединены с первым входом первого НС, вторым входом коммутатора, вторым входом ДПКД и четвертым входом комбинационного сумматора соответственно.

Выход ДПКД соединен со вторым входом переключателя. В данном устройстве коды фазы формируемого сигнала считываются из второго блока памяти, накапливаются в первом НС, преобразуются к квадратичному виду во втором НС и используются в качестве адреса для считывания кодов мгновенных значений формируемого ЛЧМ сигнала из первого блока памяти. Считываемые из первого блока памяти коды мгновенных значений преобразовываются в аналоговый сигнал с помощью ЦАП, и через схему фильтрации поступают на выход устройства. Расширение диапазона частот формируемых сигналов осуществляется путем фильтрации высших гармоник с помощью полосовых фильтров управляемых коммутаторов.

Недостатком прототипа является искажения спектральных характеристик формируемого ЛЧМ сигнала в широкой полосе частот, нестабильность амплитуды сигнала на выходе устройства, а также необходимость хранения достаточно большого количества кодов мгновенных значений формируемого сигнала в первом блоке памяти.

Целью изобретения является разработка устройства, обеспечивающего неискаженное формирование ЛЧМ сигнал в широкой полосе частот и постоянство амплитуды сигнала на его выходе, а также упрощение схемы устройства.

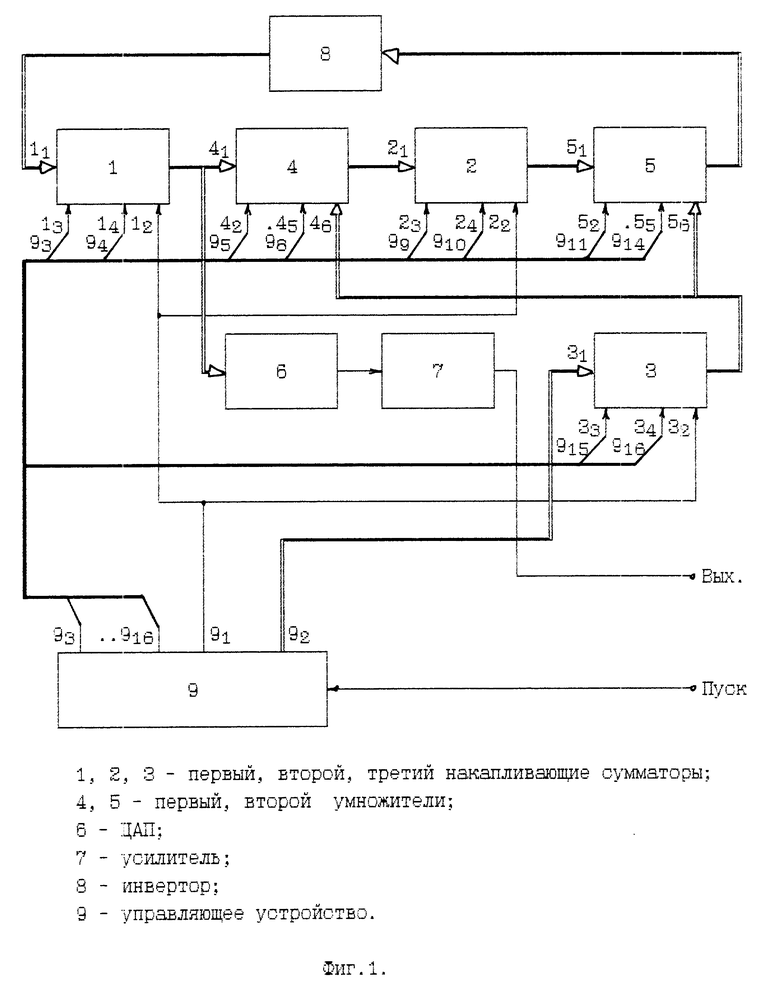

Поставленная цель достигается тем, что в известное устройство, содержащее первый и второй НС, ЦАП, дополнительно введены первый и второй умножители Ум, усилитель Ус, третий НС, инвертор, управляющее устройство УУ, Вход УУ является пусковым входом устройства. Первый вход первого НС подключен к выходу инвертора, вход которого подключен к выходу второго Ум. Первый НС, первый Ум, второй НС и второй Ум включены каскадно, причем выход первого НС дополнительно связан со входом ЦАП. Выход ЦАП подключен ко входу Ус, а выход последнего является выходом устройства. Первый выход УУ одновременно подключен ко вторым входам первого, второго и третьего НС, а первый вход последнего подключен ко второму выходу УУ. С третьего по шестнадцатый выходы УУ подключены соответственно к третьему, четвертому входам первого НС, второму-пятому входам первого Ум, третьему, четвертому входам второго НС, второму-пятому входам второго Ум и к третьему и четвертому входу третьего НС. Выход третьего НС подключен к шестым входам первого и второго Ум. Кольцевое включение первого НС, первого Ум, второго НС, второго Ум и инвертора позволяет осуществлять рекурентное вычисление мгновенных значений формируемого сигнала в широкой полосе частот, а применение многоразрядного ЦАП и усилителя с глубокой отрицательной обратной связью дает возможность получить сигнал с постоянной амплитудой с высокими спектральными характеристиками.

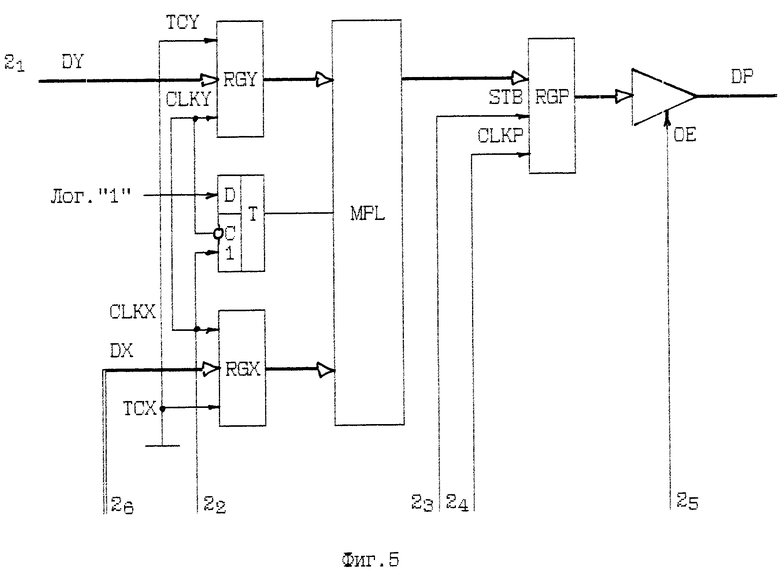

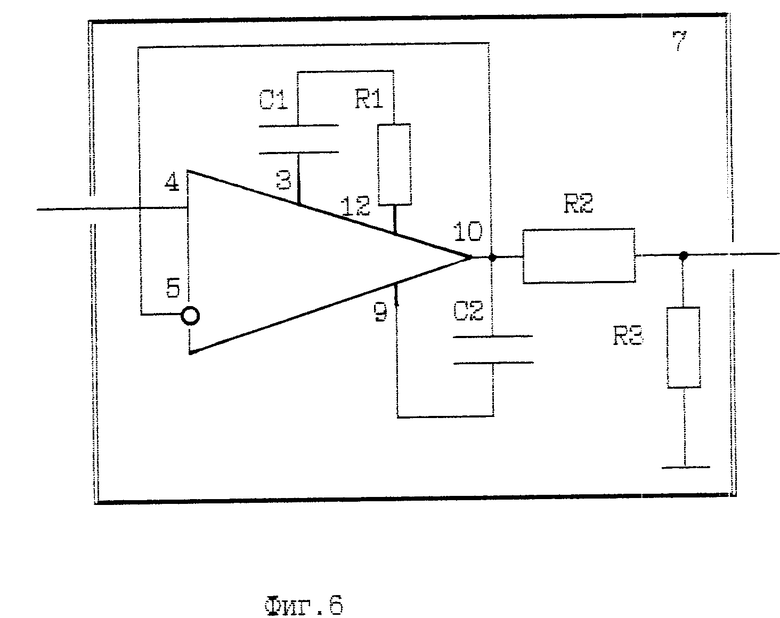

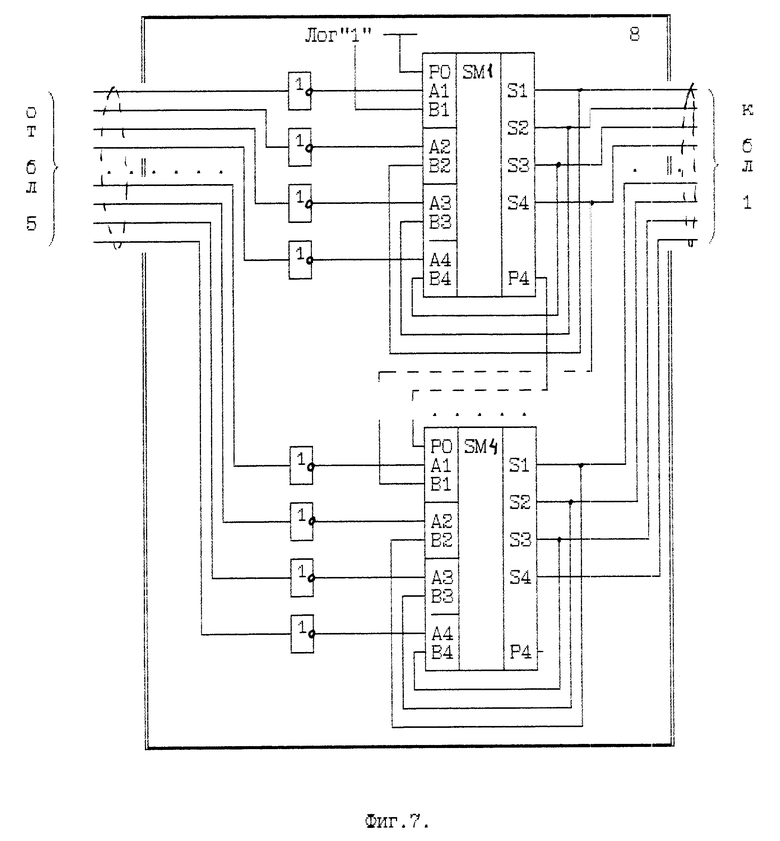

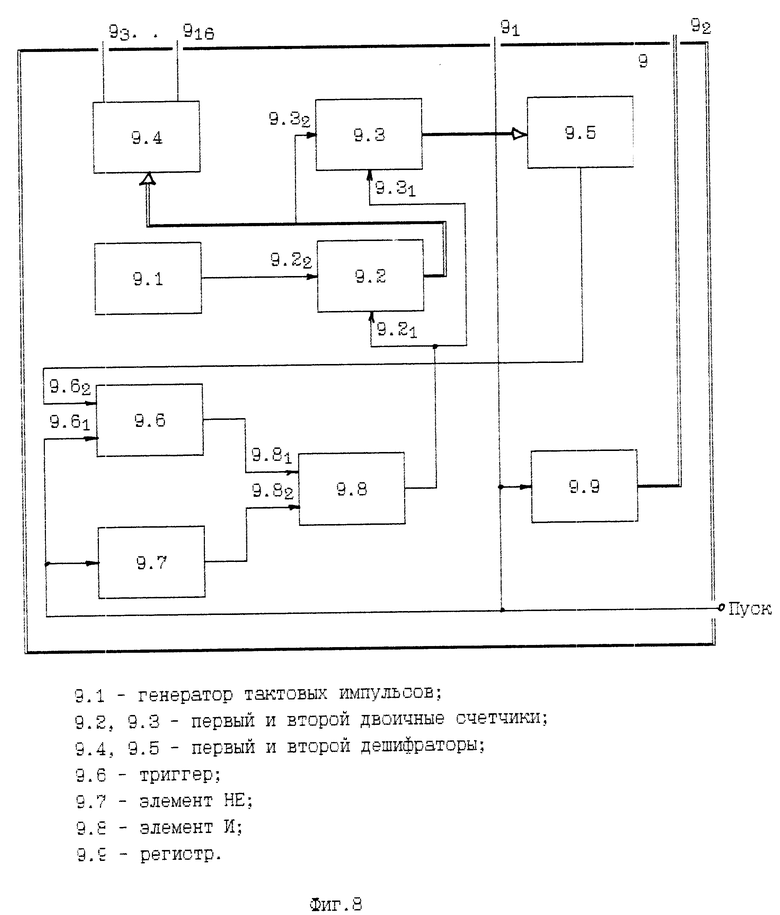

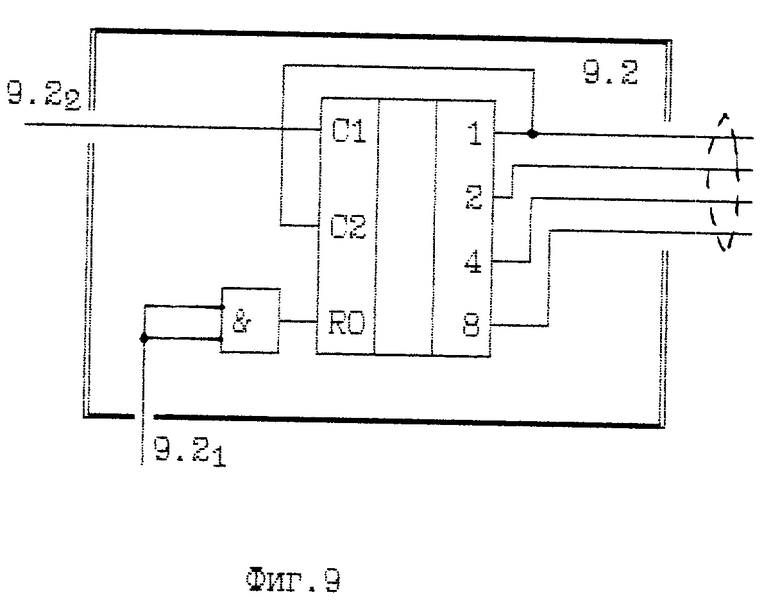

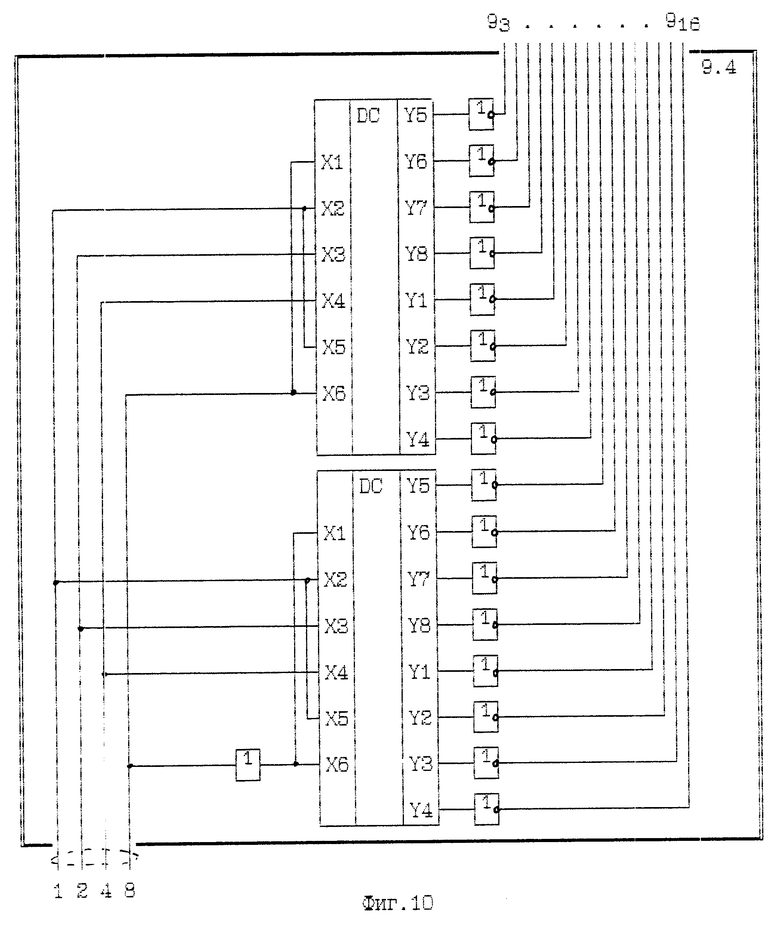

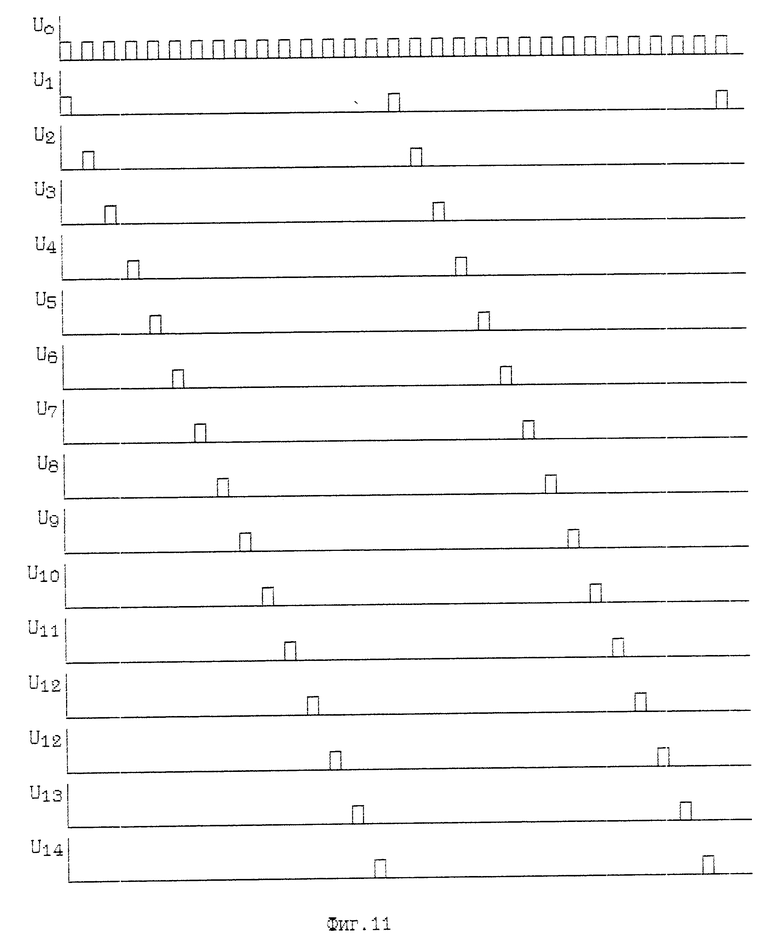

На фиг. 1 показана структурная схема устройства формирования линейно-частотно-модулируемого сигнала; на фиг. 2 - структурная схема накапливающегося сумматора; на фиг. 3 - структурная схема комбинационного сумматора; на фиг. 4 - структурная схема регистра; на фиг. 5 - схема включения умножителя; на фиг. 6 - структурная схема усилителя; на фиг. 7 - структурная схема инвертора; на фиг. 8 - структурная схема управляющего устройства; на фиг. 9 - структурная схема двоичного счетчика; на фиг. 10 - структурная схема дешифратора; на фиг. 11 - временные диаграммы, поясняющие работу устройства.

Устройство, показанное на фиг. 1, состоит из первого 1, второго 2 и третьего 3 НС, первого 4 и второго 5 Ум, ЦАП 6, Ум 7, инвертора 8 и УУ 9. Вход УУ 9 является пусковым входом устройства, а первый вход первого НС 1 подключен к выходу инвертора 8, вход которого подключен к выходу второго Ум 5. Первый НС 1, первый Ум 4, второй НС 2 и второй Ум 5 включены каскадно, причем выход первого НС 1 дополнительно связан со входом ЦАП 6. Выход ЦАП 6 подключен ко входу Ус 7, а выход последнего является выходом устройства. Первый выходы УУ 9 одновременно подключен ко вторым входам первого 1, второго 2 и третьего 3 НС, а первый вход последнего подключен ко второму выходу УУ 9. С третьего по шестнадцатый выходу УУ 9 подключены соответственно к третьему, четвертому входам первого НС 1, второму-пятому входам первого Ум 4, третьему, четвертому входам второго НС 2, второму-пятому входам второго Ум 5, третьему и четвертому входам третьего НС 3. Выход третьего НС 3 подключен к шестым входам первого 4 и второго 5 Ум.

Входящие в общую структурную схему блоки могут быть реализованы следующим образом.

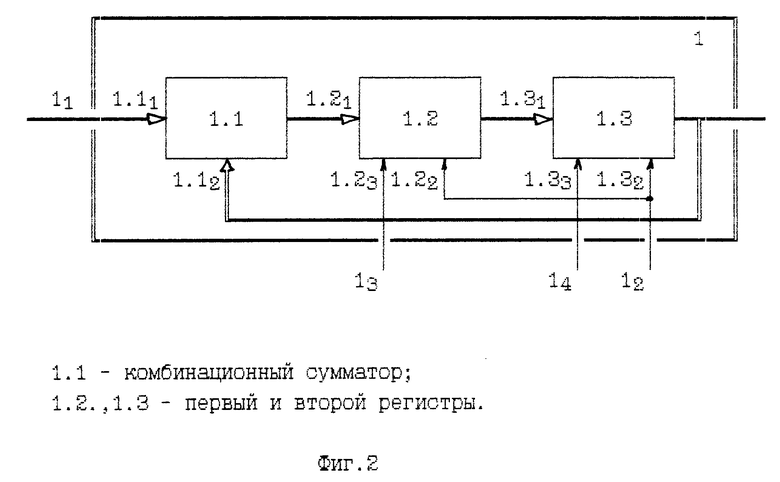

Первый 1, второй 2 и третий 3 НС идентичны. На фиг. 2 представлена схема первого НС 1, который в своем составе имеет комбинационный сумматор КС 1.1, первый 1.2 и второй 1.3 регистры, причем первый вход сумматора 1.1 является первым входом НС 1. КС 1.1, регистры 1.2 и 1.3 включены каскадно, причем выход регистра 1.3, являющийся выходом первого НС 1, подключен ко второму входу КС 1.1. Вторые входы регистров 1.2 и 1.3 являются третьим и четвертым входами первого НС 1, а третьим входы этих же регистров объединены и являются вторым входом первого НС 1.

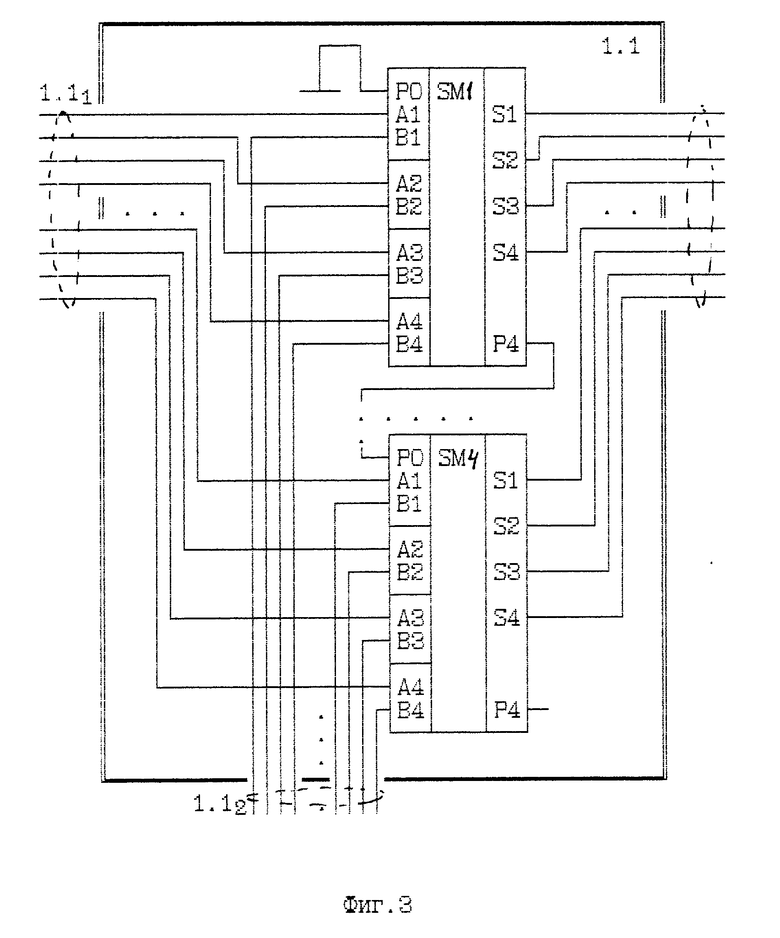

Примером реализации КС 1.1 может служить функциональный узел на микросхеме К155ИМЗ (Интегральные микросхемы. Справочник. Под ред. Б.В.Тарабрина. М. : Энергоатомиздат, 1985, с. 64). При организации суммирования шестнадцатибитовых чисел, схема КС 1.1 представляет собой параллельное соединение предлагаемых микросхем, которое показано на фиг. 3. При этом входы A1, A2, A3 и A4 соответствующих ИМС являются соответствующими разрядами первого входа КС, а входы B1, B2, B3 и B4 этих же ИМС являются соответствующими разрядами второго входа ИМС. Кроме того, вход P0 первой ИМС заземляется, а ее выход P4 соединен с входом P0 второй ИМС. Аналогично выходы P4 второй и третий ИМС соединены с входами P0 третьей и четвертой ИМС. Выход P4 четвертой ИМС не задействуется. Выходы S1, S2, S3, S4 являются соответствующими разрядами выхода КС.

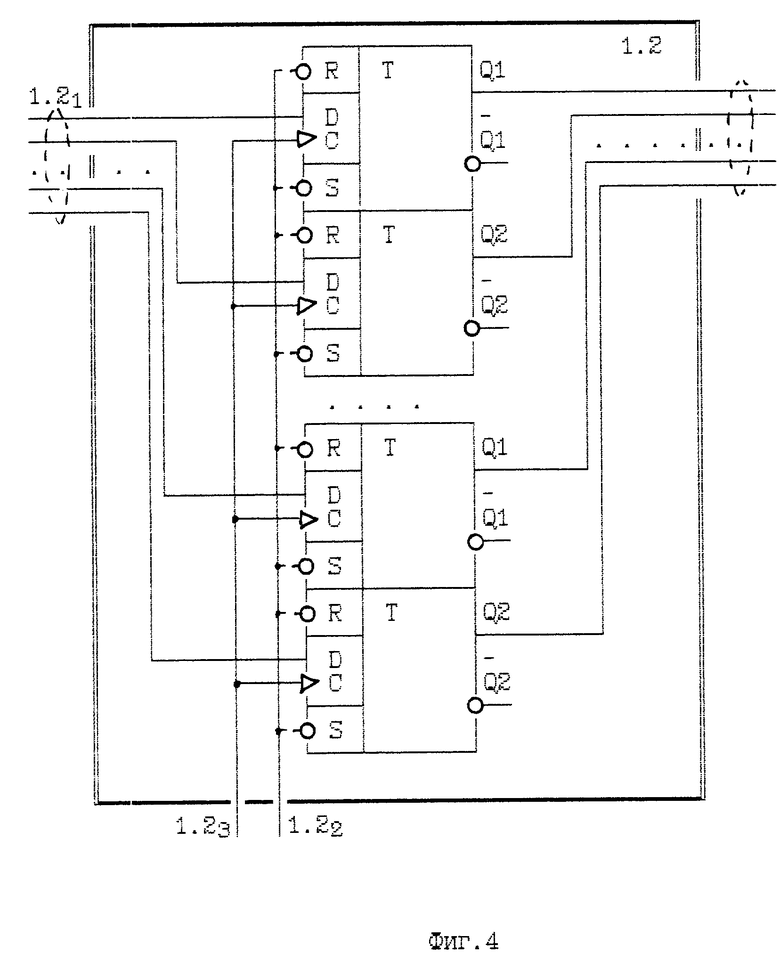

Регистры 1.2 и 1.3 аналогичны и могут быть реализованы на параллельно включенных триггерах, например, на восьми микросхемах К155ТМ2, каждая из которых содержит два триггера (Интегральные микросхемы. Справочник. Под ред. Б. В.Тарабрина. М.: Энергоатомиздат, 1985, с. 67). Схема регистра 1. на фиг. 4. При этом входы D триггеров являются соответствующими разрядами первого входа регистра 1.2, а их прямые выходы Q являются соответствующими разрядами выхода регистра. Инверсные выходы триггеров  остаются незадействованными. C-взоды триггеров являются соответствующими разрядами второго входа регистров. Третий вход регистра является установочным, и в зависимости от требуемой начальной установки, соединяется либо с R, либо с S-входами триггеров, причем, соединение с R-входом триггера соответствует записи при начальной установке логической единицы в соответствующий разряд устанавливаемого числа, а соединение с S-входом - логическому нулю.

остаются незадействованными. C-взоды триггеров являются соответствующими разрядами второго входа регистров. Третий вход регистра является установочным, и в зависимости от требуемой начальной установки, соединяется либо с R, либо с S-входами триггеров, причем, соединение с R-входом триггера соответствует записи при начальной установке логической единицы в соответствующий разряд устанавливаемого числа, а соединение с S-входом - логическому нулю.

Вторые регистры всех НС, а также первый регистр второго НС требуют начальной установки соответствующей числу ноль (соединяются S-входы триггеров со вторым входом регистра). Первый регистр НС 1 требует начальной установки числа один со вторым входом регистра R-входы триггеров). Первый регистр НС 3 требует установки числа, соответствующего начальной частоте ЛЧМ сигнала на каждом такте, в зависимости от которого со вторым входом регистра соединяются либо S, либо R-входы соответствующих триггеров.

Первый и второй Ум 2 и 3 соответственно идентичны и могут быть реализованы, например, на ИМС КР1802ВР3 (микропроцессоры и микроэвм в системах автоматического управления. Справочник. Под ред. С.Т.Хвоща. Л.:Машиностроение, 1987, с. 339, рис. 10, 9a). Схема включения Ум на предлагаемой ИМС представлена на фиг. 5. Вход DY данной ИМС является первым входом Ум, а вход DX ИМС - его шестым входом. Входы TCY и TCX закорочены на корпус, а входы CLRE и CLKX соединены и являются вторым входом Ум. Входы STB, CLKP, и OE ИМС являются третьим, четвертым и пятым входами Ум, а выход DP ИМС является выходом Ум. Увеличение разрядности обрабатываемых Ум чисел до шестнадцати возможно путем объединения нескольких ИМС при использовании дополнительных сумматоров. Схема такого объединения приведена в литературе (Микропроцессоры и микроэвм в системах автоматического управления. Справочник. Под ред. С.Т. Хвоща. Л.:Машиностроение, 187, с. 339, рис. 10, 9б). При этом в качестве выхода Ум используются шестнадцать старших разрядов выхода DP приведенной на рисунке схемы.

ЦАП 5 может быть реализован на ИМС с диодными ключами и описан в литературе (Г.Д.Бахтиаров, В.В.Малинин, В.П.Школин. Аналого-цифровые преобразователи. Под ред. Г.Д.Бахтиарова. М.:Советское радио, 1980, с. 68). В качестве входа предлагаемого ЦАП используется двенадцать старших разрядов выхода НС 1.

Ус 6 может быть реализован на ИМС К553УД1. Данная ИМС описана в литературе (Интегральные микросхемы. Справочник. Под ред. Б.В.Тарабрина. М.: Энергоатомиздат, 1985, с. 462). Здесь же приведена схема включения ИМС. При использовании предлагаемой ИМС в предлагаемом устройстве необходимо соединить выход 10 ИМС с инверсным входом 5. На фиг. 6 показана схема усилителя для предлагаемого устройства с учетом указанных изменений.

Инвертор 8 может быть реализован с использованием сумматоров на ИМС КМ155ИМЗ и элементов НЕ на ИМС К155ЛН1, которые описаны в литературе (интегральные микросхемы. Справочник. Под ред. Б.В.Тарабрина. М.: Энергоатомиздат, 1985, с. 64, 67). На фиг. 7 изображен один из вариантов построения инвертора. Соответствующие разряды входа инвертора через элементы НЕ соединены с входами A1...A4 сумматоров SM1...SM4 Входы S1 сумматоров соединены с входами B2, входы S2 сумматоров соединены с входами B3, входы S3 сумматоров соединены с входами B4. Выход S4 первого сумматора соединен с входом второго сумматора, выход S4 второго сумматора соединен с входом B1 третьего сумматора, а выход S4 третьего сумматора соединен с входами B1 четвертого сумматора. На вход B1 первого сумматора подается напряжение, соответствующее логической единице. Кроме того, выходы P4 первого, второго и третьего сумматоров соответственно соединены с входами P0 второго, третьего и четвертого сумматоров. Выход P4 четвертого сумматора остается незадействованным. Выходы первого, второго, третьего и четвертого сумматоров являются выходами инвертора 8.

УУ 9, представленное на фиг. 8, включает генератор тактовых импульсов (ГТИ) 9.1, первый и второй двоичные счетчики 9.2 и 9.3, первый и второй дешифраторы 9.4 и 9.5, триггер 9.6, элемент 9.7 НЕ, элемент 9.8 И и регистр 9.9, причем вход УУ 9 является первым входом триггера 9.6 и первым выходом УУ 9, а также входами элемента 9.7 НЕ и регистра 9.9, причем выход последнего является вторым выходом УУ 9. Выходы триггера 9.6 и элемента 9.7 НЕ являются первым и вторым входами элемента 9.8 И, а выход последнего является первыми входами двоичных счетчиков 9.2 и 9.3. Второй вход двоичного счетчика 9.2 соединен с выходом ГТИ 9.1, а его выход является входами первого дешифратора 9.4. Кроме того, верхний разряд выхода первого двоичного счетчика 9.2 является вторым входом второго двоичного счетчика 9.3, а выход последнего является входом второго дешифратора 9.5. Выход второго дешифратора 9.5 является вторым входом триггера 9.3. С первого по четырнадцатый выходы первого дешифратора 9.4 являются 3-16 выходами УУ 9.

ГТИ 9.1 может быть реализован как описано в литературе (И.С.Потемкин. Функциональные узлы цифровой автоматики. М. Энергоатомиздат, 1988, с. 240, рис. 7, 9в).

Первый и второй двоичные счетчики 9.2 и 9.3 идентичны и могут быть реализованы на ИМС К155ИЕ5, описанной в литературе (Интегральные микросхемы. Справочник. Под ред. Б.В.Тарабрина. М.:Энергоатомиздат, 1985, с.63) Схема включения предлагаемого счетчика представлена на фиг. 9. Входы элемента И счетчика соединены и являются первым входом первого двоичного счетчика 9.2, а вход C1 является его вторым входом. Вход C2 счетчика соединен с выходом 1 счетчика, а выходы 1, 2, 4, 8 ИМС являются выходами двоичного счетчика.

Триггер 9.6 является законченным функциональным узлом и описан в литературе (Микросхемы и их применение. Справочное пособие). М.: Радио и связь, 1983, с. 118), причем его первый вход является R входом, а второй вход - S входом.

Элемент 9.7 НЕ является функционально законченным узлом и может быть реализован на ИМС К155ЛН1, описанной в литературе (Интегральные микросхемы. Справочник. Под ред. Б.В.Тарабрина. М.:Энергоатомиздат. 1985, с. 67).

Элемент 9.8 И также является законченным функциональным узлом и может быть реализован на ИМС К155ЛИ1, описанной в литературе (Интегральные микросхемы. Справочник. Под ред. Б.В.Тарабрина. М.: Энергоатомиздат, 1985. с. 67).

Регистр 9.9 может быть реализован аналогично регистрам 1.2, 1.2 (фиг. 4). Особенностью является то, что в качестве его входа используется только третий вход регистра 1.2, а остальные входы остаются незадействованными. Соединение входа осуществляется с R и S входами триггеров в соответствии с записываемым в него числом характеризующим приращение частоты сигнала согласно правила описанного выше.

Первый дешифратор 9.3 может быть реализован на ИМС К155ИД4 и К155ЛН1, описанными в известной литературе (Микросхемы и их применение. Справочное пособие. М. : Радио и связь, 1983, с. 70, 67). На фиг. 10 изображена схема такого дешифратора. Провода 2 и 3 входа дешифратора соединены с входами X2 и X3 ИМС. Входы X2 и X5 обеих ИМС дешифратора соединены и являются проводом 1 входа дешифратора, а соединенные входы X1 и X6 являются проводами 8 входа дешифратора, причем эти входы второй ИМС соединены с проводом 8 через элемент НЕ. Выходы Y1-Y8 обеих ИМС соединены с входами элементов НЕ, выходы последних являются 3-16 выходами УУ 9.

Второй дешифратор 9.5 является дешифратором команды окончания работы устройства и может быть реализован аналогично первому дешифратору 9.4 за исключением того, что его выходом является последний выход предлагаемого первого дешифратора 9.4.

Предлагаемые второй счетчик 9.3 и второй дешифратор 9.5 позволяют сформировать ЛЧМ сигнал длительностью шестнадцать периодов. При необходимости формирования сигнала с большей длительностью необходимо использовать двоичный счетчик и дешифратор с большим количеством разрядов.

Предлагаемое устройство формирования ЛЧМ сигнала реализует принцип решения дифференциального уравнения второго порядка вида

u''(t) + w(t) u'(t) = 0.

Решение такого уравнения осуществляется приближенным методом, при котором дифференциалы заменяются конечными приращениями значений переменных. При этом функции интегрирования выполняют первый 1 и второй 2 НС. Таким образом решение уравнения (1) сводится к решению эквивалентного интегрального уравнения вида

u(t) = - w(t) ∫∫ u(t),

причем остальные элементы, а именно первый 4 и второй 5 Ум, инвертор 8, замыкают цепь обратной связи и обеспечивают рекурентные вычисления кодов мгновенных значений формируемого ЛЧМ сигнала.

Для получения кодов значений выходного напряжения используется начальная установка значений в первом 1, втором 2, третьем 3 НС и УУ 9, причем в первый 1 НС записывается значение "1", во второй 2 НС - значение "0", третий 3 НС - число соответствующее начальной (нижней) частоте формируемого ЛЧМ сигнала, а УУ 9 - число, соответствующее приращению частоты на каждом цикле расчета мгновенного значения. Последующие числа, соответствующие напряжению формируемого ЛЧМ сигнала, складываются из последовательных накоплений этих чисел в НС по кольцу: первый НС 1, первый Ум 4, второй НС 2, второй Ум 5 и инвертор 8.

Предложенное устройство работает следующим образом. При поступлении импульса "Пуск" на УУ 9 на его первом выходе формируется импульс начальной установки, который поступает на вторые входы первого 1, второго 2 и третьего 3 НС. При этом осуществляется запись: в первый НС 1 числа "1"; во второй НС 2 числа "0"; в третий НС 3 числа, определяющего начальную частоту формируемого ЛЧМ сигнала.

Кроме того, УУ 9 на втором выходе формирует число, определяющее приращение частоты формируемого сигнала при расчете очередного значения его напряжения.

Далее, УУ 9 начинает формировать на выходах (с третьего по шестнадцатый) управляющие импульсы, которые поступают на соответствующие входы блоков предложенного устройства и обеспечивают его работу. На фиг. 11 представлены временные диаграммы формируемых управляющих импульсов, причем U0 напряжение на выходе генератора тактовых импульсов, U1-U14 - напряжения соответственно на третьем-шестнадцатом выходах УУ 9.

На первом и втором тактах работы устройства за счет управляющих импульсов, поступающих на УУ 9 на третий и четвертый вход первого НС 1, последний осуществляет считывание записанного при начальной установке числа, которое поступает на первый вход Ум 4 и ЦАП 6. На третьем, четвертом, пятом и шестом тактах, за счет управляющих импульсов поступающих с пятого-восьмого выходов УУ 9 на второй-пятый входы Ум 4, последний производит умножение поступающего на его первый вход числа и числа, соответствующего текущей частоте формируемого сигнала, которое подается с выхода третьего НС 3 на его второй вход. Результат умножения с выхода Ум 4 поступает на первый вход второго НС 2.

На очередных двух тактах за счет управляющих импульсов поступающих с девятого и десятого выхода УУ 9 на третий и четвертый входы второго НС 2, последний осуществляет сложение поступившего на первый вход и хранящегося в нем чисел. Полученный результат сложения сохраняется в НС и поступает на первый вход второго Ум 5.

На последующих четырех тактах с помощью управляющих импульсов поступающих с одиннадцатого-четырнадцатого выходов УУ 9 на второй-пятый входы второго Ум 5, последний производит умножение числа поступившего с выхода НС 2 на его первый вход на число, соответствующее коду начальной частоты и поступившее с выхода НС 3 на его шестой вход. Результат умножения через инвертор 8 поступает на первый вход первого НС 1.

На очередных двух тактах за счет управляющих импульсов поступающих с пятнадцатого и шестнадцатого выходов УУ 9 на третий и четвертый входы третьего НС 3, последний осуществляет сложение хранящегося в нем числа, соответствующего коду начальной частоты формируемого сигнала и числа, соответствующего коду приращения этой частоты, поступающего на первый его вход с второго выхода УУ 9. Результат сложения сохраняется в НС 3 и поступает на его выход.

На последующих тактах первый НС 1 осуществляет сложение хранящегося в нем числа и числа поступающего с выхода инвертора 8. Процесс рекурентного вычисления повторяется согласно выше описанной последовательности.

Формируемые на выходе первого НС 1 числа поступает на вход ЦАП 6, который преобразовывает коды чисел в аналоговый сигнал соответствующий генератору ЛЧМ сигналу. Сигнал с выхода ЦАП 6 поступает на вход Ус 7, который его усиливает и за счет стопроцентной отрицательной обратной связи обеспечивает постоянство амплитуды ЛЧМ сигнала на выходе устройства.

Разрядность чисел, циркулирующих по цепи первый НС 1, первый Ум 4, второй НС 2, второй Ум 5, инвертор 8 выбрана достаточной (в данном случае количества разрядов шестнадцать) для обеспечения точности вычисления чисел, соответствующих напряжению формируемого ЛЧМ сигнала.

Поскольку на выходах первого 4 и второго 5 Ум результат перемножения двух шестнадцатиразрядных чисел представляется тридцатидвухразрядным числом, то на вход НС 2 и инвертора 8 подается только шестнадцать старших разрядов, а младшие разряды отбрасываются.

Поскольку разрядность ЦАП 6 ( в данном случае двенадцать) меньше разрядности чисел циркулирующих по кольцу первый НС 1, первый Ум 4, второй НС 2, второй Ум 5, инвертор 8, то на его вход подается только двенадцать старших разрядов с выхода первого НС 1, а младшие разряды отбрасываются. Использование большего числа разрядов при расчетах, чем используется ЦАП 6 позволяет снизить погрешность вычислений за счет накопления ошибок.

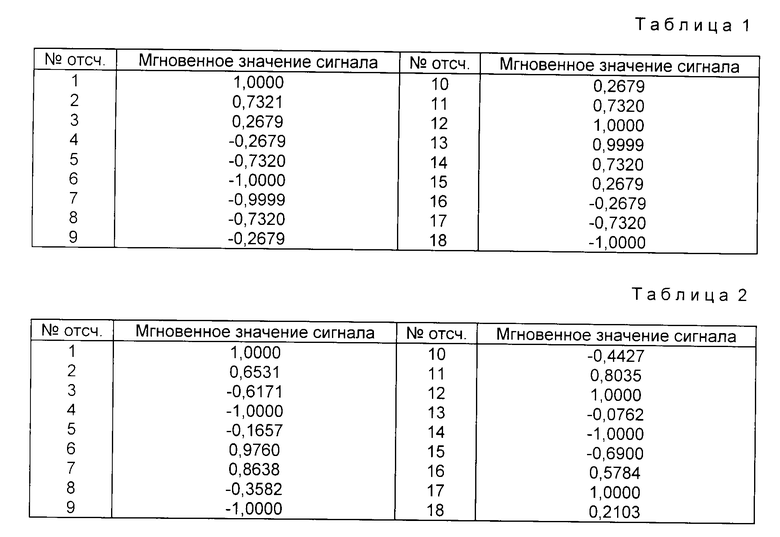

В качестве примера произведены расчеты мгновенных значений формируемого ЛЧМ сигнала при расчете омега = 0,5176 и приращении частоты Δω = ω/324000000 . Результаты расчете приведены в табл. 1 и 2, причем в табл. 1 приведены результаты отсчетов формируемого сигнала на начальном отрезке времени работы устройства, а в табл. 2 - в середине времени работы устройства.

Анализ результатов работы предложенного устройства требует отметить, что вводимые при начальной установке в третий НС 3 код начальной частоты и в УУ 9 код приращения частоты на каждом такте должны обеспечивать не менее шести - семи отсчетов напряжения формируемого сигнала на один его период на самой высшей частоте. В этом случае уровень высших гармоник сигналов не будет превышать - 60 дБ.

Начальная частота формируемого ЛМЧ сигнала определяется частотой генератора тактовых импульсов и начальной установкой в третьем НС 3. Верхняя частота формируемого сигнала будет также определяться частотой генератора тактовых импульсов и, кроме того, приращением частоты на каждом такте и разрядность второго счетчика 9.2 и второго дешифратора 9.5 УУ 9.

Все НС работают аналогично. В качестве примера рассмотрим работу первого НС 1 (фиг. 2).

При поступлении на второй вход первого НС 1 импульса начальной установки он поступает одновременно на вторые входы первого 1.2 и второго 1.3 регистра. В соответствии с их конструкцией осуществляется в первой регистр 1.2 числа "один", а во второй регистр числа "ноль". При этом хранящимся в нем числом является число "один" .

На первом такте работы устройства на третий вход первого НС 1 поступает управляющий импульс, который, поступая на третий вход регистра 1.2, обеспечивает на его выходе число "один". Это число с выхода первого регистра 1.2 поступает на вход второго регистра 1.3. На втором такте работы устройства управляющий импульс, приходящий на четвертый вход первого НС 1, поступает на третий вход второго регистра 1.3 и обеспечивает формирование на его выходе числа, поступившего на его вход. Сформированное на выходе второго регистра 1.3 число поступает одновременно на выход первого НС 1 и второй вход комбинационного сумматора. Приходящее на первый вход первого НС 1 число поступает на первый вход комбинационного сумматора, который осуществляет сложение его с числом, которое присутствует на его втором входе и пересылает результат на первый вход первого регистра 1.2. Далее устройство работает в выше изложенном порядке. Хранение накапливаемого числа осуществляется в регистрах 1.2 и 1.3, а каскадное включение этих регистров предотвращает повторное сложение на одном такте работы НС.

Регистры 1.2 и 1.3, входящие в состав первого НС 1 идентичны, поэтому рассмотрим их работу на примере первого регистра 1.2.

При начальной установке импульс начальной установки, поступающий на второй вход регистра 1.2 поступает на R или S -входы триггеров в зависимости от записываемого числа. В процессе работы устройства, при поступлении управляющего импульса на третий вход регистра 1.2, он одновременно открывает триггеры всех разрядов и обеспечивает формирование на их Q-выходах логической единицы (если импульс начальной установки подавался на R вход) или логического нуля (если при начальной установке импульс подавался на S-вход). Поскольку Q-выходы триггеров являются выходом регистра, то записанное при начальной установке число будет передано на выход регистра. В процессе работы, на первом входе регистра 1.2 поступает число, которое поступает на D-входы триггеров соответствующих разрядов. На очередном такте работы регистра, управляющий импульс, поступающий на третий вход регистра, своим передним фронтом открывает триггеры и обеспечивает формирование на Q-выходах триггеров формирование напряжения логической единицы или нуля в зависимости от напряжения на их D-входах.

Инвертор 8 работает следующим образом. Поступающее на его вход число, в виде напряжений, соответствующих значению логической единицы или нуля для соответствующего разряда, подается на входы элементов НЕ, которые его инвертируют и подают на A-входы комбинационного сумматора. К полученному в результате инверсии числу прибавляется логическая единица, которая подается на первый B-вход комбинационного сумматора. Описанная схема соединения соответствующих входов и выходов обеспечивает логическое сложение. Получаемые на S-выходах комбинационного сумматора напряжения подаются на соответствующие разряды выхода инвертора. Формируемое инвертором 8 таким образом число является противоположным по отношению к числу, подающему на его вход.

УУ 9 обеспечивает функционирование всего устройства и работает следующим образом. При поступлении на вход устройства импульса запуска прямоугольной формы, он одновременно подается на вход регистра 9.9, вход элемента 9.7 НЕ, R-триггера 9.6 и на первый выход УУ 9, обеспечивающий начальную установку первого 1, второго 2, и третьего 3 НС. При этом своим передним фронтом импульс запуска осуществляет запись числа, соответствующего увеличению частоты на очередном такте работы устройства в регистр 9.9, формирует на выходе триггера 9.6 напряжение, соответствующее логической единице, а на выходе элемента НЕ 9.7 сигнал, соответствующий нулю. Таким образом на первый вход элемента 9.8 И поступает напряжение соответствующее логической единице, а на второй его вход - логическому нулю. На своем выходе элемент 9.8 И формирует напряжение логического нуля, которое, поступая на первые входы первого 9.2 и второго 9.3 счетчиков, дает "запрет" на счет поступающих на их вторые входы импульсов.

По окончании импульса запуска, он своим задним фронтом формирует на входе элемента 9.7 НЕ напряжение логического нуля, который, в свою очередь, формирует на своем выходе напряжение логической единицы и подает на его второй вход элемента 9.8 И. Поскольку на первом и втором входах элемента 9.8 И присутствует напряжение, соответствующее логической единице, он формирует на своем выходе, также напряжение логической единицы, которые, поступая на первые входы первого 9.2 и второго 9.3 двоичных счетчиков, является разрешающим для начала работы последних.

Генератор 9.1 тактовых импульсов формирует последовательность импульсов прямоугольной формы, которые с его выхода поступают на второй вход первого двоичного счетчика 9.2. При наличии разрешающего напряжения на его первом входе, он начинает считать поступающие на его второй вход импульсы, формируя на своем выходе четырехразрядное число, соответствующее количеству сосчитанных импульсов. Сформированное первым двоичным счетчиком 9.2 число с его выхода поступает на вход первого дешифратора 9.4, который, в зависимости от поступившего на его вход числа, формирует управляющий импульс на одном из своих выходов. Временные диаграммы последовательности тактовых импульсов и управляющих импульсов на выходах первого дешифратора представлены на фиг. 11.

Импульсы старшего разряда числа, формируемого первым двоичным счетчиком 9.2, поступают на второй вход второго двоичного счетчика 9.3, который, при наличии разрешающего напряжения на его первом входе, осуществляет их счет и формирует на своем выходе число, соответствующее количеству поступивших на его вход импульсов. Сформированное вторым двоичным счетчиком 9.3 число поступает на вход второго дешифратора 9.5. При заполнении второго двоичного счетчика 9.3, второй дешифратор 9.5 формирует на своем выходе импульс окончания работы, который поступает на S-вход триггера 9.6. Триггер 9.6 формирует на своем выходе напряжение, соответствующее логическому нулю, которое, поступив на первый вход элементе 9.8 И, обеспечивает формирование последним сигнала "запрет" для первого 9.2 и второго 9.3 двоичных счетчиков. На этом устройство заканчивает формирование ЛЧМ сигнала.

Таким образом, новая совокупность существенных признаков предложенного устройства обеспечивает формирование ЛЧМ сигнала в широкой полосе частот с постоянной амплитудой.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК | 1998 |

|

RU2127943C1 |

| СПОСОБ И УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПАКЕТОВ ДАННЫХ В КАНАЛЕ СВЯЗИ ОБЩЕГО ПОЛЬЗОВАНИЯ | 1997 |

|

RU2115246C1 |

| МАЛОШУМЯЩИЙ УСИЛИТЕЛЬ СВЕРХВЫСОКИХ ЧАСТОТ | 1995 |

|

RU2108658C1 |

| УСТРОЙСТВО ОБУЧЕНИЯ ОПЕРАТОРОВ | 1997 |

|

RU2129734C1 |

| ГЕНЕРАТОР БЕЛОГО ШУМА (ВАРИАНТЫ) | 1997 |

|

RU2120179C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ ПОМЕХ | 1994 |

|

RU2097921C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1995 |

|

RU2099889C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2115165C1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

Использование: изобретение относится к технике радиосвязи и может быть использовано в радиопередающих и радиоприемных устройствах для формирования линейно-частотно-модулированного (ЛЧМ) сигнала. Целью изобретения является разработка устройства, формирующего ЛЧМ сигнал в широкой полосе частот и обеспечивающего постоянство амплитуды сигнала на его выходе. Цель изобретения достигается построением устройства формирования ЛУЧ сигнала, содержащего три накапливающих сумматора 1, 2 и 3, два умножителя 4 и 5, цифроаналоговый преобразователь (ЦАП) 6, усилитель 7, инвертор 8 и управляющее устройство 9. Кольцевое включение блоков 1, 4, 2, 5 и 8 обеспечивает рекурентное вычисление мгновенных значений формируемого сигнала в широкой полосе частот, а применение многоразрядного ЦАП и усилителя с глубокой отрицательной обратной связью дает возможность получить сигнал с постоянной амплитудой и высокими спектральными характеристиками. 1 з.п.ф-лы, 11 ил.

| SU, авторское свидетельство, 1677845, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| SU, авторское свидетельство 1617621, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1998-04-27—Публикация

1996-02-19—Подача