Изобретение относится к области радиосвязи и может быть использовано в цифровых системах, в частности в системах спутниковой и наземной подвижной радиосвязи для создания колебаний с угловой модуляцией с компактным спектром.

Аналогами заявляемого устройства являются частотные модуляторы, использующие квадратурные схемы формирования модулированного сигнала, к которым относятся, например, модуляторы π /4-DQPSK и CQPSK (Овчинников М.А., Воробьев С.П., Сергеев С.И. Открытые стандарты цифровой транкинговой радиосвязи. Серия изданий “Связь и бизнес”. М.: МЦНТИ, ООО “Мобильные коммуникации”, 2000, 166 с. См. с.73 и 158). Эти модуляторы выполнены по одинаковым структурным схемам (рис. 9.1 и 8.10). Различаются они только фильтрами и скоростью передачи информации (с.160). Эти модуляторы включат в себя устройство перекодировки, два фильтра нижних частот (фильтры Найквиста), два амплитудных модулятора и сумматор, причем два выхода устройства перекодировки соединяются соответственно с входами фильтров нижних частот, выходы ФНЧ соединяются с входами амплитудных модуляторов, выходы этих модуляторов соединяются с входами сумматора, выход которого является выходом частотного модулятора. Недостатком этих частотных модуляторов является наличие сопутствующей амплитудной модуляции выходного сигнала. При таком сигнале усилитель мощности передатчика должен работать в линейном режиме, что исключает возможность использования высокоэффективных режимов работы передатчика с высоким кпд (с.80). Причина появления сопутствующей AM заключается в используемом методе формирования модулирующих напряжений для модуляторов в квадратурных каналах (использование реакции фильтров Найквиста при действии на их входах коротких импульсов возбуждения).

Наиболее близким по технической сущности является модулятор, осуществляющий частотную модуляцию без разрыва фазы Minimum Shift Keying (MSK) или, что то же самое, модуляцию минимальным частотным сдвигом (ММС) (см. книгу: Банкет В Л., Дорофеев В.М. Цифровые методы в спутниковой связи. - М.: Радио и связь. 1988. - 240 с., ил., с. 39-40, рис. 2.1б, 2.2).

Этот модулятор содержит переключатель посылок на два канала (четные - в один канал, нечетные - в другой), генератор сглаживающих напряжений, два перемножителя, генератор несущей, фазовращатель, два амплитудно-фазовых модулятора и сумматор. Поочередное переключение посылок входного модулирующего сигнала на два канала обеспечивает увеличение в два раза длительности посылок в каждом канале. Сглаживание прямоугольных посылок длительностью 2Т0 по законам

в каждом канале, соответственно, обеспечивает форму огибающих ВЧ-напряжений на выходах амплитудно-фазовых модуляторов в соответствии с напряжениями u1 и u2, вследствие чего осуществляется плавное изменение фазы ВЧ-колебаний на выходе сумматора за время Т0 на +π /2 или -π /2 в зависимости от посылки входного модулирующего сигнала (0 или 1). Такое изменение фазы соответствует индексу частотной модуляции выходного сигнала m=0,5. Выбранная форма напряжений u1 и u2 на входах квадратурных амплитудно-фазовых модуляторов обеспечивает отсутствие сопутствующей AM выходного сигнала, т.е. в данном модуляторе отсутствует основной недостаток модуляторов CQPSK и π /4-DQPSK. Кроме того, данный модулятор, благодаря линейному изменению фазы за время посылки, отсутствию скачков фазы на границах посылок, формирует на выходе модулированное по частоте напряжение с компактным спектром. Реальная ширина спектра модулированного таким образом сигнала составляет 1,18 V, где V - скорость передачи, бит/с. Применение в модуляторе ММС фильтра Гаусса дает дополнительные возможности уменьшения занимаемой полосы частот (модуляция GMSK, см., например, книгу: Ратынский М.В. Основы сотовой связи/ Под ред. Д.Б.Зимина. - М.: Радио и связь, 1998. - 248 с., ил., с.121-126). Кроме того, в данном модуляторе нет прямого воздействия на генератор несущей, благодаря чему обеспечивается высокая стабильность несущего колебания и возможность оперативной смены несущей частоты, что важно для систем со скачкообразным изменением частоты.

Вместе с тем, требования к уменьшению реальной ширины спектра постоянно растут, а возможности модулятора ММС не соответствуют этим требованиям. Таким образом, сравнительно широкая реальная ширина спектра формируемого сигнала является недостатком модулятора ММС. Причиной этого является использование в модуляторе двухчастотной модуляции, и соответственно, двоичного цифрового сигнала, обладающего информационной избыточностью, которая не используется для уменьшения реальной ширины спектра.

Заявляемое изобретение направлено на решение задачи использования трех частот манипуляции для создания частотно-манипулированного сигнала без разрыва фазы. Это позволяет использовать информационную избыточность двоичного цифрового сигнала. а также уменьшение необходимой девиации частоты и перераспределение энергии в спектре сигнала для получения основного технического результата - уменьшения реальной ширины спектра при сохранении индекса частотной модуляции m=0,5.

Решение этой задачи достигается тем, что в частотный модулятор, содержащий генератор несущей, фазовращатель, два амплитудно-фазовых модулятора и сумматор, причем выход генератора несущей соединяется с первым входом первого амплитудно-фазового модулятора и с входом фазовращателя, выход фазовращателя соединяется с первым входом второго амплитудно-фазового модулятора, выходы амплитудно-фазовых модуляторов соединяются, соответственно, с первым и вторым входами сумматора, выход которого является выходом трехчастотного модулятора, дополнительно включаются анализатор состояния фазовращающих напряжений, блок формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов, логический блок формирования управляющих напряжений для блока ключей, блок ключей и преобразователь кода, причем один вход преобразователя кода является входом трехчастотного модулятора, три других входа соединяются с тремя соответствующими выходами блока формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов, три выхода преобразователя кода соединяются с тремя соответствующими входами логического блока формирования управляющих напряжений для блока ключей, восемь других входов логического блока формирования управляющих напряжений для блока ключей соединяются с восемью соответствующими выходами анализатора состояний фазовращающих напряжений, восемь выходов логического блока формирования управляющих напряжений для блока ключей соединяются с восемью управляющими входами блока ключей, четыре сигнальных входа блока ключей соединяются с четырьмя соответствующими выходами блока формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов, первый выход блока ключей соединяется с вторым входом первого амплитудно-фазового модулятора и с первым входом анализатора состояний фазовращающих напряжений, второй выход блока ключей соединяется с вторым входом второго амплитудно-фазового модулятора и с вторым входом анализатора состояния фазовращающих напряжений, а два выхода блока формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов, соединенные с входами преобразователя кода, соединяются с третьим и четвертым входами анализатора состояния фазовращающих напряжений.

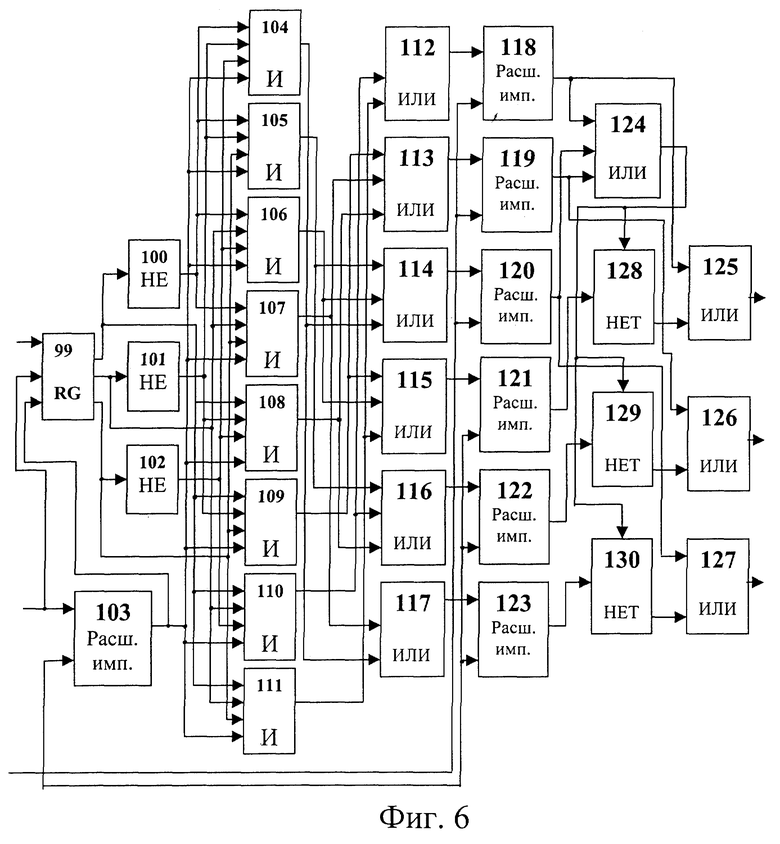

Анализатор состояния фазовращающих напряжений включает в себя два инвертора, 8 элементов И, один элемент НЕТ, три элемента ИЛИ и 8 расширителей импульсов, причем вход первого инвертора соединяется с первыми входами первого и второго элементов И и является первым входом анализатора состояния фазовращающих напряжений, вход второго инвертора соединяется с первыми входами пятого и шестого элементов И и является вторым входом анализатора состояния фазовращающих напряжении, выход первого инвертора соединяется с первыми входами 3-го и 4-го элементов И, выход второго инвертора соединяется с первыми входами 7-го и 8-го элементов И, первый вход первого элемента ИЛИ соединяется с вторыми входами 1-, 3-, 5- и 7-го элементов И и является третьим входом анализатора состояния фазовращающих напряжений, второй вход первого элемента ИЛИ соединяется с вторыми входами 2-, 4-, 6- и 8-го элементов И и является четвертым входом анализатора состояния фазовращающих напряжений, выход каждого из элементов И соединяется с соответствующим входом второго элемента ИЛИ и, кроме того, выход первого элемента И соединяется с вторым входом третьего элемента ИЛИ, выходы элементов И с второго по восьмой соединяются с первыми входами расширителей импульсов, соответственно, с второго по восьмой, выход первого элемента ИЛИ соединяется с первым входом элемента НЕТ и с вторыми входами всех расширителей импульсов, выход второго элемента ИЛИ соединяется с вторым входом элемента НЕТ, выход элемента НЕТ соединяется с первым входом третьего элемента ИЛИ, выход которого соединяется с первым входом первого расширителя импульсов, а выходы расширителей импульсов являются выходами анализатора состояния фазовращающих напряжений.

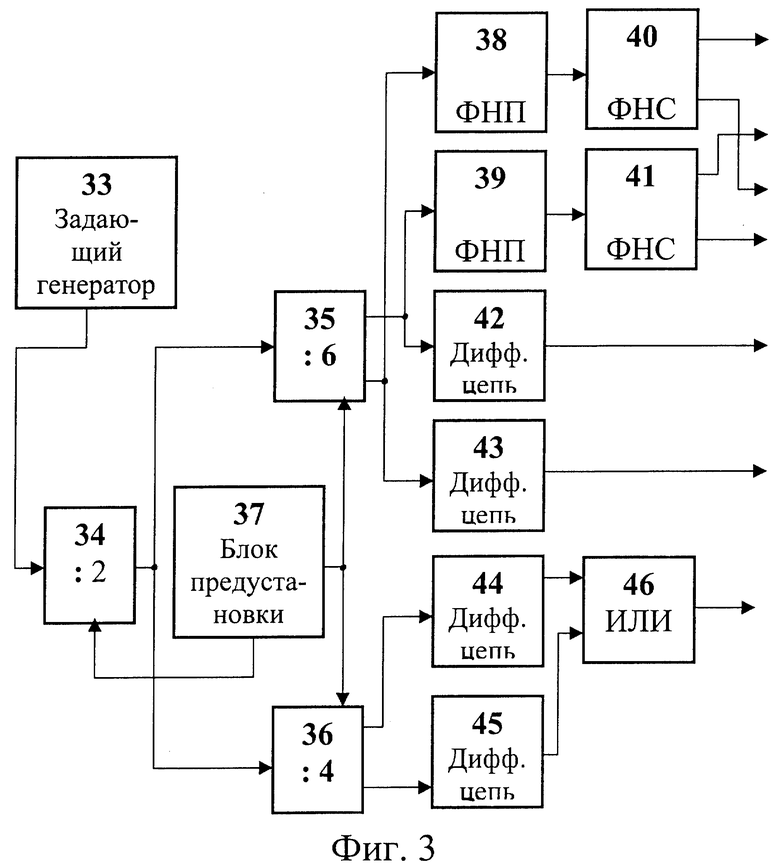

Блок формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов содержит задающий генератор, делители частоты на два, на 4 и на 6, блок предустановки триггеров делителей частоты, четыре дифференцирующие цепи с ограничением по минимуму, два формирователя напряжения пилообразной формы, два формирователя напряжения синусоидальной формы и один элемент ИЛИ, причем выход задающего генератора соединяется с первым входом делителя частоты на два, выход делителя частоты на два соединяется с первыми входами делителей частоты на 4 и на 6, второй вход делителя частоты на два соединяется с первым выходом блока предустановки триггеров делителей частоты, вторые входы делителей частоты на 4 и на 6 соединяются с вторым выходом блока предустановки триггеров делителей частоты, первый выход делителя частоты на 6 соединяется с входом второго формирователя напряжения пилообразной формы и с входом первой дифференцирующей цепи с ограничением по минимуму, выход которой является выходом блока формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов, второй выход делителя частоты на 6 соединяется с входом первого формирователя напряжения пилообразной формы и входом второй дифференцирующей цепи с ограничением по минимуму, выход которой является выходом блока формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов, первый выход делителя частоты на 4 соединяется с входом третьей дифференцирующей цепи с ограничением по минимуму, второй выход делителя частоты на 4 соединяется с входом четвертой дифференцирующей цепи с ограничением по минимуму, выход первого формирователя напряжения пилообразной формы соединяется с входом первого формирователя напряжения синусоидальной формы, два выхода которого являются выходами блока формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов, выход второго формирователя напряжения пилообразной формы соединяется с входом второго формирователя напряжения синусоидальной формы, два выхода которого являются выходами блока формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов, выход третьей дифференцирующей цепи соединяется с первым входом элемента ИЛИ, выход четвертой дифференцирующей цепи соединяется со вторым входом элемента ИЛИ, а выход элемента ИЛИ является выходом блока формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов.

Логический блок формирования управляющих напряжений для блока ключей выполнен на 24-х элементах И и 14-ти элементах ИЛИ, причем первые входы элементов И с первого по восьмой соединяются между собой и являются первым входом логического блока формирования управляющих напряжений для блока ключей, первые входы элементов И с 9-го по 16-й соединяются между собой и являются вторым входом логического блока формирования управляющих напряжений для блока ключей, первые входы элементов И с 17-го по 24-й соединяются между собой и являются третьим входом логического блока формирования управляющих напряжений для блока ключей, вторые входы 1-, 9- и 17-го элементов И соединяются между собой и являются четвертым входом логического блока формирования управляющих напряжений для блока ключей, вторые входы 2-, 10- и 18-го элементов И соединяются между собой и являются пятым входом логического блока формирования управляющих напряжений для блока ключей, вторые входы 3-, 11- и 19-го элементов И соединяются между собой и являются шестым входом логического блока формирования управляющих напряжений для блока ключей, вторые входы 4-, 12- и 20-го элементов И соединяются между собой и являются седьмым входом логического блока формирования управляющих напряжений для блока ключей, вторые входы 5-, 13- и 21-го элементов И соединяются между собой и являются восьмым входом логического блока формирования управляющих напряжений для блока ключей, вторые входы 6-, 14- и 22-го элементов И соединяются между собой и являются девятым входом логического блока формирования управляющих напряжений для блока ключей, вторые входы 7-, 15- и 23-го элементов И соединяются между собой и являются десятым входом логического блока формирования управляющих напряжений для блока ключей, вторые входы 8-, 16- и 24-го элементов И соединяются между собой и являются одиннадцатым входом логического блока формирования управляющих напряжений для блока ключей, выход первого элемента И соединяется с входами 1-го и 8-го элементов ИЛИ, выход второго элемента И соединяется с входами 2-го и 9-го элементов ИЛИ, выход третьего элемента И соединяется с входами 3-го и 10-го элементов ИЛИ, выход четвертого элемента И соединяется с входами 4-го и 11-го элементов ИЛИ, выход пятою элемент 11 соединяется с входами 4-го и 9-го элементов ИЛИ, выход шестого элемента И соединяется с входами 3-го и 8-го элементов ИЛИ, выход седьмого элемента И соединяется с входами 2-го и 11-го элементов ИЛИ, выход восьмого элемента И соединяется с входами 1-го и 10-го элементов ИЛИ, выход девятого элемента И соединяется с входами 5-го и 14-го элементов ИЛИ, выход десятого элемента И соединяется с входами 5-го и 14-го элементов ИЛИ, выход одиннадцатого элемента И соединяется с входами 6-го и 14-го элементов ИЛИ, выход двенадцатого элемента И соединяется с входами 6-го и 14-го элементов ИЛИ, выход тринадцатого элемента И соединяется с входами 7-го и 13-го элементов ИЛИ, выход четырнадцатого элемента И соединяется с входами 7-го и 13-го элементов ИЛИ, выход пятнадцатого элемента И соединяется с входами 7-го и 12-го элементов ИЛИ, выход шестнадцатого элемента И соединяется с входами 7-го и 12-го элементов ИЛИ, выход семнадцатого элемента И соединяется с входами 1-го и 10-го элементов ИЛИ, выход восемнадцатого элемента И соединяется с входами 2-го и 11-го элементов ИЛИ, выход девятнадцатого элемента И соединяется с входами 3-го и 8-го элементов ИЛИ, выход двадцатого элемента И соединяется с входами 4-го и 9-го элементов ИЛИ, выход двадцать первого элемента И соединяется с входами 2-го и 9-го элементов ИЛИ, выход двадцать второго элемента И соединяется с входами 1-го и 8-го элементов ИЛИ, выход двадцать третьего элемента И соединяется с входами 4-го и 11-го элементов ИЛИ, выход двадцать четвертого элемента И соединяется с входами 3-го и 10-го элементов ИЛИ, а выходы всех элементов ИЛИ являются выходами логического блока формирования управляющих напряжений для блока ключей.

Блок ключей состоит из 14 аналоговых ключей, причем первые входы попарно 1- и 8-го, 2- и 9-го, 3- и 10-го, 4- и 11-го, 5- и 12-го, 6- и 13-го, 7- и 14-го аналоговых ключей соединены между собой и являются входами блока ключей, вторые входы всех ключей также являются входами блока ключей, выходы аналоговых ключей с 1-го по 7-й соединяются между собой и являются первым выходом блока ключей, выходы аналоговых ключей с 8-го по 14-й также соединяются между собой и являются вторым выходом блока ключей.

Преобразователь кода содержит регистр сдвига, 3 элемента НЕ, 8 элементов И, 10 элементов ИЛИ, 7 расширителей импульсов и три элемента НЕТ, причем первый вход регистра сдвига является первым входом преобразователя кода, второй вход регистра сдвига соединяется с первым входом первого расширителя импульсов и является вторым входом преобразователя кодов, второй вход первого расширителя импульсов соединяется с вторыми входами 5-, 6- и 7-го расширителей импульсов и является третьим входом преобразователя кода, выход первого расширителя импульсов соединяется с третьим входом регистра сдвига и с четвертыми входами элементов И, первый выход регистра сдвига соединяется с входом первого элемента НЕ и с входами 5-, 6-, 7- и 8-го элементов И, второй выход регистра сдвига соединяется с входом второго элемента НЕ и с входами 3-, 4-, 7- и 8-го элементов И, третий выход регистра сдвига соединяется с входом третьего элемента НЕ и с входами 2-, 4-, 6- и 8-го элементов И, выход первого элемента НЕ соединяется с входами 1-, 2-, 3- и 4-го элементов И, выход второго элемента НЕ соединяется с входами 1-, 2-, 5- и 6-го элементов И, выход третьего элемента НЕ соединяется с входами 1-, 3-, 5- и 7-го элементов И, выход первого элемента И соединяется с входами 3- и 6-го элементов ИЛИ, выход второго элемента И соединяется с входами 3- и 5-го элементов ИЛИ, выход третьего элемента И соединяется с входами 3- и 4-го элементов ИЛИ, выход четвертого элемента И соединяется с входами 2- и 6-го элементов ИЛИ, выход пятого элемента И соединяется с входами 2- и 5-го элементов ИЛИ, выход шестого элемента И соединяется с входами 2- и 4-го элементов ИЛИ, выход седьмого элемента И соединяется с входами 1- и 5-го элементов ИЛИ, выход восьмого элемента И соединяется с входами 1- и 4-го элементов ИЛИ, выходы элементов ИЛИ с 1- по 6-й соединяются с первыми входами расширителей импульсов, соответственно, с второго по седьмой, вторые входы второго третьего и четвертого расширителей импульсов соединяются между собой и являются четвертым входом преобразователя кода, выход второго расширителя импульсов соединяется с входами 7- и 8-го элементов ИЛИ, выход третьего расширителя импульсов соединяется с входами 7- и 9-го элементов ИЛИ, выход четвертого расширителя импульсов соединяется с входами 7- и 10-го элементов ИЛИ, выход пятою расширителя импульсов соединяется с первым входом первого элемента НЕТ, выход шестого расширителя импульсов соединяется с первым входом второго элемента НЕТ, выход седьмого расширителя импульсов соединяется с первым входом третьего элемента НЕТ, выход 7-го элемента ИЛИ соединяется с вторыми входами элементов НЕТ, выходы первого, второго и третьего элементов НЕТ соединяются с входами, соответственно, восьмого, девятого и десятого элементов ИЛИ, выходы которых являются выходами преобразователя кода.

Совокупность признаков, характеризующих в целом трехчастотный модулятор, обеспечивает получение технического результата во всех случаях, на которые испрашивается объем правовой защиты, а признаки, относящиеся к анализатору состояния фазовращающих напряжений, блоку формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов, логическому блоку формирования управляющих напряжений для блока ключей, блоку ключей и преобразователю кода, характеризуют его лишь в конкретной форме выполнения.

Все существенные признаки заявляемого изобретения находятся в причинно-следственной связи с достигаемым техническим результатом. Преобразователь кода из входного модулирующего двоичного сигнала, имеющего длительность элементов Т0, формирует троичный сигнал в позиционном коде, имеющий длительность посылок 3Т0/2. Для осуществления модуляции несущей этим троичным сигналом используется трехчастотная модуляция без разрыва фазы. Частота посылок ВЧ-сигнала изменяется с помощью элементов, используемых в устройстве-прототипе: амплитудно-фазовых модуляторов, генератора несущей, фазовращателя и сумматора. Однако для того, чтобы модуляция была трехчастотной, на входы фазовых модуляторов необходимо подавать модулирующие (фазовращающие) напряжения специальной формы. Эти напряжения формируются функциональными узлами, которых нет в прототипе: анализатором состояния фазовращающих напряжений, блоком формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов, логическим блоком формирований управляющих напряжений для блока ключей и блоком ключей. Анализатор состояния фазовращающих напряжений определяет состояние фазовращающих напряжений на входах амплитудно-фазовых модуляторов в каждый тактовый момент времени, логический блок формирования управляющих напряжений для блока ключей на основе результатов этого анализа и выходных сигналов преобразователя кода определяет форму фазовращающих напряжений, которые должны поступать на каждый амплитудно-фазовый модулятор в течение последующего тактового интервала, чтобы посылка выходного напряжения имела соответствующую частоту, и открывает необходимую пару ключей в блоке ключей (по одному для каждого амплитудно-фазового модулятора). Через открытые ключи необходимые фазовращающие напряжения с выходов блока формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов поступают на амплитудно-фазовые модуляторы. При этом на выходе частотного модулятора формируется трехчастотный модулированный сигнал без разрыва фазы с индексом модуляции 0,5. Длительность посылок этого сигнала в 1,5 раза больше длительности посылок двоичного цифрового сигнала, поступающего на вход модулятора и, соответственно, в 1,5 раза больше длительности посылок сигнала ММС. Увеличение длительности посылок приводит к уменьшению реальной ширины спектра сигнала, что и определяет технический результат заявляемого изобретения. Кроме того, в сформированном 3-частотном сигнале девиация частоты в 1,5 раза меньше, чем в сигнале ММС, а третья частота манипуляции расположена на частоте несущей, т.е. посередине между двумя первыми частотами, и эти два фактора также уменьшают ширину спектра сигнала.

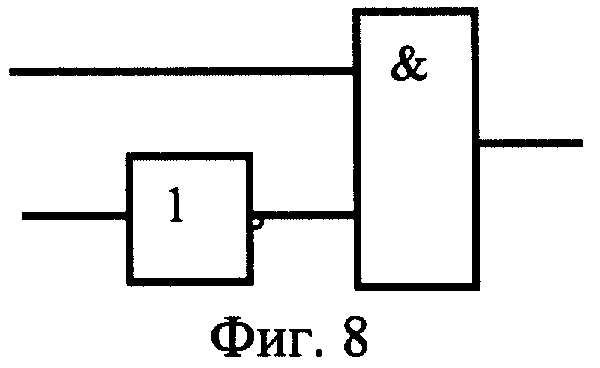

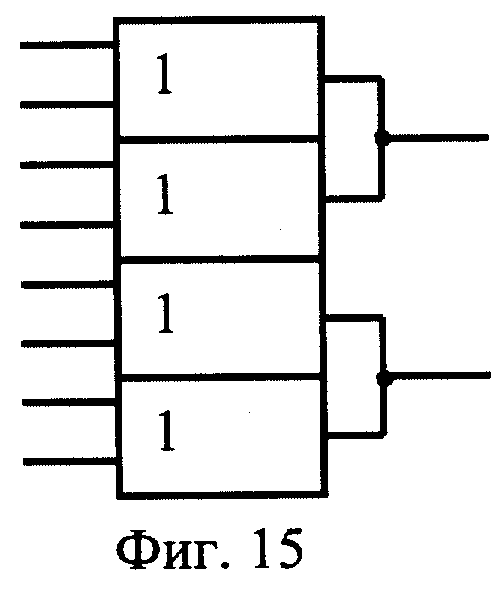

На фиг.1 представлена структурная схема частотного модулятора, на фиг.2 - структурная схема анализатора состояния фазовращающих напряжений, на фиг.3 структурная схема блока формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов, на фиг.4 - структурная схема логического блока формирования управляющих напряжений для блока ключей, на фиг.5 - структурная схема блока ключей, на фиг.6 - структурная схема преобразователя кода, на фиг.7 - схема элемента 8 ИЛИ, на фиг.8 - схема элемента НЕТ, на фиг.9 - схема расширителя импульсов, на фиг.10 - схема задающего генератора, на фиг.11 - схема блока предустановки триггеров делителей частоты, на фиг.12 - схема делителя частоты на шесть, на фиг.13 - схема формирователей напряжения прямоугольной формы и формирователя напряжения синусоидальной формы, на фиг.14 - схема дифференцирующей цепи с ограничением по минимуму, на фиг.15 - схема элемента 4 ИЛИ, на фиг.16 - временные диаграммы сигналов в блоке формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов, на фиг.17 - временные диаграммы сигналов в преобразователе кода, на фиг.18 - временные диаграммы, поясняющие принцип работы трехчастотного модулятора.

Трехчастотный модулятор содержит анализатор 1 состояния фазовращающих напряжений, блок 2 формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов, логический блок 3 формирования управляющих напряжений для блока ключей, блок 4 ключей, преобразователь 5 кода, первый амплитудно-фазовый модулятор 6, второй амплитудно-фазовый модулятор 7, фазовращатель 8, генератор 9 несущей и сумматор 10. Анализатор 1 состояния фазовращающих напряжений содержит инверторы 11 и 12, элементы 14-21 И, элементы 13, 22, 23 ИЛИ, элемент 24 НЕТ и расширители 25-32 импульсов. Блок 2 формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов содержит задающий генератор 33, делитель 34 частоты на два, делитель 35 частоты на 6, делитель 36 частоты на 4, блок 37 предустановки, формирователи 38 и 39 напряжения пилообразной формы, формирователи 40 и 41 напряжения синусоидальной формы, дифференцирующие цепи 42-45 с ограничением по минимуму и элемент 46 ИЛИ. Логический блок формирования управляющих напряжений для блока ключей содержит элементы 47-70 И и элементы 71-84 ИЛИ. Блок ключей содержит аналоговые ключи 85-98. Преобразователь 5 кода содержит регистр 99 сдвига, элементы 100-102 НЕ, элементы 104-111 И, элементы 112-117, 124-127 ИЛИ, расширители 118-123 импульсов и элементы 128-130 НЕТ.

Первый вход преобразователя 5 кода (на фиг.6 это первый вход регистра 99 сдвига) является входом трехчастотного модулятора, на который подается входной двоичный модулирующий сигнал. Второй вход преобразователя 5 кода соединяется с выходом элемента 46 ИЛИ блока 2 формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов (тактовые импульсы ТИ0, см. фиг.16). Третий вход преобразователя кода, соединенный с входом расширителя 103 импульсов, соединяется с выходом дифференцирующей цепи 42 (импульсы ТИ1, фиг.16). Четвертый вход преобразователя 5 кода соединяется с выходом дифференцирующей цепи 43 блока 2 формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов (импульсы ТИ2, фиг.16). Три выхода преобразователя 5 кода соединяются с тремя входами логического блока 3 формирования управляющих напряжений для блока ключей, при этом выход элемента 125 ИЛИ соединяется с первыми входами элементов 47-54 И, выход элемента 126 ИЛИ соединяется с первыми входами элементов 55-62 И и выход элемента 127 ИЛИ соединяется с первыми входами элементов 63-70 И. 14 выходов логического блока 3 формирования управляющих напряжений для блока ключей соединяются с 14-ю входами блока ключей, при этом выход элемента 71 ИЛИ соединяется с управляющим входом ключа 85, выход элемента 72 ИЛИ соединяется с управляющим входом ключа 86, выход элемента 73 ИЛИ соединяется с управляющим входом ключа 87, выход элемента 74 ИЛИ соединяется с управляющим входом ключа 88, выход элемента 75 ИЛИ соединяется с управляющим входом ключа 89, выход элемента 76 ИЛИ соединяется с управляющим входом ключа 90, выход элемента 77 ИЛИ соединяется с управляющим входом ключа 91, выход элемента 78 ИЛИ соединяется с управляющим входом ключа 93, выход элемента 79 ИЛИ соединяется с управляющим входом ключа 92, выход элемента 80 ИЛИ соединяется с управляющим входом ключа 95, выход элемента 81 ИЛИ соединяется с управляющим входом ключа 94, выход элемента 82 ИЛИ соединяется с управляющим входом ключа 97, выход элемента 83 ИЛИ соединяется с управляющим входом ключа 96, выход элемента 84 ИЛИ соединяется с управляющим входом ключа 98. Восемь выходов анализатора 1 состояния фазовращающих напряжений соединяются с восемью входами логического блока 3 формирования управляющих напряжений для блока ключей, при этом выход расширителя 25 импульсов соединяется с вторыми входами элементов 47, 55, 63 И, выход расширителя 26 импульсов соединяется с вторыми входами элементов 48, 56 и 64 И, выход расширителя 27 импульсов соединяется с вторыми входами элементов 49, 57 и 65 И, выход расширителя 28 импульсов соединяется с вторыми входами элементов 50, 58, 66 И, выход расширителя 29 импульсов соединяется с вторыми входами элементов 51, 59 и 67 И, выход расширителя 30 импульсов соединяется с вторыми входами элементов 52, 60 и 68 И, выход расширителя 31 импульсов соединяется с вторыми входами элементов 53, 61 и 69 И, выход расширителя 32 импульсов соединяется с вторыми входами элементов 54, 62 и 70 И. Четыре выхода блока 2 формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов соединяются с четырьмя входами блока 4 ключей, при этом первый выход формирователя 40 напряжения синусоидальной формы соединяется с сигнальными входами ключей 85 и 92, первый выход формирователя 41 напряжения синусоидальной формы соединяется с сигнальными входами ключей 86 и 93, второй выход формирователя 40 напряжения синусоидальной формы соединяется с сигнальными входами ключей 87 и 94, второй выход формирователя 41 напряжения синусоидальной формы соединяется с сигнальными входами ключей 88 и 95. На сигнальные входы ключей 89 и 96 подается постоянное напряжение уровнем +а, на сигнальные входы ключей 90 и 97 подается постоянное напряжение -а, на сигнальные входы ключей 91 и 98 подается нулевое напряжение. Первый выход блока 4 ключей соединяется с первым входом анализатора 1 состояния фазовращающих напряжений, при этом точка соединения ключей 85-91 соединяется со входами инвертора 11 и элементов 14 и 15 И, и эта точка соединяется с вторым входом амплитудно-фазового модулятора 6. Второй выход блока 4 ключей соединяется с вторым входом анализатора 1 состояния фазовращающих напряжений, при этом точка соединения ключей 92-98 соединяется с входами инвертора 12 и элементов 18 и 19 И, и эта точка соединяется с вторым входом амплитудно-фазового модулятора 7. Два выхода блока 2 формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов соединяются с двумя соответствующими входами анализатора 1 состояния фазовращающих напряжений, при этом выходы дифференцирующих цепей 42 и 43 соединяются, соответственно, с входами элемента 22 ИЛИ.

В анализаторе 1 состояния фазовращающих напряжений вход инвертора 11 соединяется с первыми входами элементов 14 и 15 И, вход инвертора 12 соединяется с первыми входами элементов 18 и 19 И, выход инвертора 11 соединяется с первыми входами элементов 16 и 17 И, выход инвертора 12 соединяется с первыми входами элементов 20 и 21 И, первый вход элемента 22 ИЛИ соединяется с вторыми входами элементов 14, 16, 18 и 20 И, второй вход элемента 22 ИЛИ соединяется с вторыми входами элементов 15, 17, 19 и 21 И, выход каждого из элементов И соединяется с соответствующим входом элемента 13 ИЛИ и, кроме того, выход элемента 14 И соединяется с вторым входом элемента 23 ИЛИ, выходы элементов 15-21 И соединяются с первыми входами расширителей 26-32 импульсов, выход элемента 22 ИЛИ соединяется с первым входом элемента 24 НЕТ и с вторыми входами всех расширителей импульсов, выход элемента 13 ИЛИ соединяется с вторым входом элемента 24 НЕТ, выход элемента 24 НЕТ соединяется с первым входом элемента 23 ИЛИ, выход которого соединяется с первым входом расширителя 25 импульсов, а выходы расширителей импульсов являются выходами анализатора 1 состояния фазовращаюших напряжений.

В блоке 2 формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов выход задающего генератора 33 (см. фиг.3) соединяется с первым входом делителя 34 частоты на два, выход делителя 34 частоты на два соединяется с первыми входами делителя 35 частоты на 6 и делителя 36 частоты на 4, второй вход делителя частоты на два соединяется с первым выходом блока 37 предустановки, вторые входы делителей 35 и 36 частоты на 4 и на 6 соединяются с вторым выходом блока 37 предустановки триггеров делителей частоты, первый выход делителя 35 частоты на 6 соединяется с входом формирователя 39 напряжения пилообразной формы и с входом дифференцирующей цепи 42 с ограничением по минимуму, выход которой является выходом блока 2 формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов, второй выход делителя 35 частоты на 6 соединяется с входом формирователя 38 напряжения пилообразной формы и с входом дифференцирующей цепи 43 с ограничением по минимуму, выход которой является выходом блока 2 формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов, первый выход делителя 36 частоты на 4 соединяется с входом дифференцирующей цепи 44 с ограничением по минимуму, второй выход делителя 36 частоты на 4 соединяется с входом дифференцирующей цепи 45 с ограничением по минимуму, выход формирователя 38 напряжения пилообразной формы соединяется с входом формирователя 40 напряжения синусоидальной формы, два выхода которого являются выходами блока 2 формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов, выход формирователя 39 напряжения пилообразной формы соединяется с входом формирователя 41 напряжения синусоидальной формы, два выхода которого являются выходами блока 2 формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов, выход дифференцирующей цепи 44 соединяется с первым входом элемента 46 ИЛИ, выход дифференцирующей цепи 45 соединяется с вторым входом элемента 46 ИЛИ, а выход элемента 46 ИЛИ является выходом блока 2 формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов.

В логическом блоке 3 формирования управляющих напряжений для блока ключей первые входы элементов 47-54 И соединяются между собой и являются первым входом логического блока 3 формирования управляющих напряжений для блока ключей, первые входы элементов 55-62 И соединяются между собой и являются вторым входом логического блока 3 формирования управляющих напряжений для блока ключей, первые входы элементов 63-70 И соединяются между собой и являются третьим входом логического блока 3 формирования управляющих напряжений для блока ключей, вторые входы элементов 47, 55 и 63 И соединяются между собой и являются четвертым входом логического блока 3 формирования управляющих напряжений для блока ключей, вторые входы элементов 48, 56 и 64 И соединяются между собой и являются пятым входом логического блока 3 формирования управляющих напряжений для блока ключей, вторые входы элементов 49, 57 и 65 И соединяются между собой и являются шестым входом логического блока 3 формирования управляющих напряжений для блока ключей, вторые входы элементов 50, 58 и 66 И соединяются между собой и являются седьмым входом логического блока 3 формирования управляющих напряжений для блока ключей.

Вторые входы элементов 51, 59 и 67 И соединяются между собой и являются восьмым входом логического блока 3 формирования управляющих напряжений для блока ключей, вторые входы элементов 52, 60 и 68 И соединяются между собой и являются девятым входом логического блока 3 формирования управляющих напряжений для блока ключей, вторые входы элементов 53, 61 и 69 И соединяются между собой и являются десятым входом логического блока 3 формирования управляющих напряжений для блока ключей, вторые входы элементов 54, 62 и 70 И соединяются между собой и являются одиннадцатым входом логического блока 3 формирования управляющих напряжений для блока ключей, выход элемента 47 И соединяется с входами элементов 71 и 78 ИЛИ, выход элемента 48 И соединяется с входами элементов 72 и 78 ИЛИ, выход элемента 49 И соединяется с входами элементов 73 и 80 ИЛИ, выход элемента 50 И соединяется с входами элементов 74 и 81 ИЛИ, выход элемента 51 И соединяется с входами элементов 74 и 79 ИЛИ, выход элемента 52 И соединяется с входами элементов 73 и 78 ИЛИ, выход элемента 53 И соединяется с входами элементов 72 и 81 ИЛИ, выход элемента 54 И соединяется с входами элементов 71 и 80 ИЛИ, выход элемента 55 И соединяется с входами элементов 75 и 84 ИЛИ, выход элемента 56 И соединяется с входами элементов 75 и 84 ИЛИ, выход элемента 57 И соединяется с входами элементов 76 и 84 ИЛИ, выход элемента 58 И соединяется с входами элементов 76 и 84 ИЛИ, выход элемента 59 И соединяется с входами элементов 77 и 83 ИЛИ, выход элемента 60 И соединяется с входами элементов 77 и 83 ИЛИ, выход элемента 61 И соединяется с входами элементов 77 и 84 ИЛИ, выход элемента 62 И соединяется с входами элементов 77 и 84 ИЛИ, выход элемента 63 И соединяется с входами элементов 71 и 80 ИЛИ, выход элемента 64 И соединяется с входами элементов 72 и 81 ИЛИ, выход элемента 65 И соединяется с входами элементов 73 и 78 ИЛИ, выход элемента 66 И соединяется с входами элементов 74 и 79 ИЛИ, выход элемента 67 И соединяется с входами элементов 72 и 79 ИЛИ, выход элемента 68 И соединяется с входами элементов 71 и 78 ИЛИ, выход элемента 69 И соединяется с входами элементов 74 и 81 ИЛИ, выход элемента 70 И соединяется с входами элементов 73 и 80 ИЛИ, а выходы всех элементов ИЛИ являются выходами логического блока 3 формирования управляющих напряжений для блока ключей.

В блоке 4 ключей первые входы аналоговых ключей попарно 85 и 92, 86 и 93, 87 и 94, 88 и 95, 89 и 96, 90 и 97, 91 и 98 соединяются между собой и являются сигнальными входами блока 4 ключей, вторые входы всех аналоговых ключей являются управляющими входами блока 4 ключей, выходы аналоговых ключей с 85 по 91-й соединяются между собой и являются первым выходом блока 4 ключей, выходы аналоговых ключей с 92 по 98 также соединяются между собой и являются вторым выходом блока 4 ключей.

В преобразователе 5 кода первый вход регистра 99 сдвига является первым входом преобразователя 5 кода, второй вход регистра 99 сдвига соединяется с первым входом расширителя 103 импульсов и является вторым входом преобразователя 5 кода, второй вход расширителя 103 импульсов соединяется с вторыми входами расширителей 121-123 импульсов и является третьим входом преобразователя 5 кода, выход расширителя 103 импульсов соединяется с третьим входом регистра 99 сдвига и с четвертыми входами элементов 104-111 И, первый выход регистра 99 сдвига соединяется с входом элемента 100 НЕ и с входами элементов 108-111 И, второй выход регистра 99 сдвига соединяется с входом элемента 101 НЕ и с входами элементов 106, 107, 110 и 111 И, третий выход регистра 99 сдвига соединяется с входом элемента 102 НЕ и с входами элементов 105, 107, 109 и 111 И, выход элемента 100 НЕ соединяется с входами элементов 104-107, И, выход элемента 101 НЕ соединяется с входами элементов 104, 105, 108 и 109 И, выход элемента 102 НЕ соединяется с входами элементов 104, 106, 108 и 110 И, выход элемента 104 И соединяется с входами элементов 114 и 117 ИЛИ, выход элемента 105 И соединяется с входами элементов 114 и 116 ИЛИ, выход элемента 106 И соединяется с входами элементов 114 и 115 ИЛИ, выход элемента 107 И соединяется с входами элементов 113 и 117 ИЛИ, выход элемента 108 И соединяется с входами элементов 113 и 116 ИЛИ, выход элемента 109 И соединяется с входами элементов 113 и 115 ИЛИ, выход элемента 110 И соединяется с входами элементов 112 и 116 ИЛИ, выход элемента 111 И соединяется с входами элементов 112 и 115 ИЛИ, выходы элементов 112-117 ИЛИ соединяются, соответственно, с первыми входами расширителей 118-123 импульсов, вторые входы расширителей 118-120 импульсов соединяются между собой и являются четвертым входом преобразователя 5 кода, выход расширителя 118 импульсов соединяется с первыми входами элементов 124 и 125 ИЛИ, выход расширителя 119 импульсов соединяется с входами элементов 124 и 126 ИЛИ, выход расширителя 120 импульсов соединяется с входами элементов 124 и 127 ИЛИ, выход расширителя 121 импульсов соединяется с входом элемента 128 НЕТ, выход расширителя 122 импульсов соединяется с входом элемента 129 НЕТ, выход расширителя 123 импульсов соединяется с входом элемента 130 НЕТ, выход элемента 124 ИЛИ соединяется с входами элементов 128, 129 и 130 НЕТ, выходы элементов 128, 129 и 130 НЕТ соединяются с входами, соответственно, элементов 125, 126 и 127 ИЛИ, выходы которых являются выходами преобразователя 5 кода.

Большинство функциональных узлов трехчастотного модулятора выполняются на ИМС: 2-входовые элементы 14-21, 47-70 И - К1533ЛИ1; 4-входовые элементы 104-111 И-КР1533ЛИ6; 2-входовые элементы 22, 23, 46, 75, 76, 82, 83, 112, 117, 125-127 ИЛИ - КР1533ЛЛ1; 3-входовые элементы 113-116, 124 ИЛИ - КР1533ЛЕ4 (это 3ИЛИ-НЕ) и КР1533ЛН1 (это элемент НЕ); восьмивходовой элемент 13 ИЛИ выполняется на двух элементах 4ИЛИ-НЕ (К176ЛП6) и одном элементе 2И-НЕ (КР1533ЛАЗ) по схеме фиг.7, элементы 24, 128-130 НЕТ выполняются на одном элементе НЕ (КР1533ЛН1) и одном элементе 2И-НЕ по схеме фиг.8, расширители 25-32, 103, 118-123 импульсов - на RSD-триггерах типа КР1533ТМ2 и инверторах КР1533ЛН1 по схеме фиг.9, задающий генератор 33 может быть выполнен на ИМС КР531ГГ1 по схеме фиг.10, блок 37 предустановки может быть выполнен по схеме фиг.11 на транзисторах КТ3102Г, делители 34-36 частоты могут быть выполнены на RSD-триггерах К1533ТМ2, при этом делитель частоты на 6 для получения меандра на выходе выполняется в виде последовательного включения делителей на 3 и на 2 по схеме фиг.12 с использованием перед выходным делителем на два формирующих элементов 2ИЛИ-НЕ КР1533ЛЕ1.

Формирователь напряжения пилообразной формы (ФНП) выполняется на интегрирующей RC-цепи (с буферным усилителем на операционном усилителе, например, КР140УД8). Формирователь напряжения синусоидальной формы (ФНС) выполняется по схеме, представленной в книге: Граф Р. Электронные схемы: 1300 примеров: Пер. с англ. - М.: Мир. 1989, 688 с., ил., с.618.

Схема функционального узла, включающего в себя ФНП с буферным усилителем и ФНС, представлена на фиг.13. Дифференцирующие цепи 42, 43 с ограничением по минимуму можно выполнить на RC-цепях с элементами И К1533ЛИ1 в качестве ограничителей по минимуму, устраняющих отрицательные импульсы на выходах дифференцирующих цепей (фиг.14), 4-входовые элементы 71-74, 77-81, 84 ИЛИ - К155ЛЛ1 (объединяя выходы у двух элементов 2ИЛИ по схеме фиг.15), элементы 100-102 НЕ - КР1533ЛН1, дифференцирующие цепи 42, 43 выполняются в виде RC-цепи, аналоговые ключи 85-98 выполняются на ИМС КР590КН6, регистр 99 сдвига выполняется на ИМС К555ИР16.

Работа трехчастотного модулятора осуществляется следующим образом. Блок 2 формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов формирует четыре последовательности сигналов заданной формы S1-S4 и три последовательности тактовых импульсов ТИ0, ТИ1 и ТИ2. Форма этих последовательностей, а также форма сигналов в генераторе представлены на временных диаграммах фиг.16. Задающий генератор 33 формирует меандр с длительностью элементов Т0/8, где Т0 - длительность посылок двоичного сигнала на входе модулятора (осциллограмма uзг). Делитель 34 частоты на два и блок предустановки триггеров делителей частоты обеспечивают взаимную синхронизацию выходных напряжений генератора 2: сигналы S1...S4 имеют частоту Ω =π /(3· Т0), причем с тактовыми импульсами последовательности ТИ1 совпадают максимумы положительных и отрицательных значений сигналов S1 и S3, а с тактовыми импульсами последовательности ТИ2 совпадают максимумы положительных и отрицательных значений сигналов S2 и S4. С выхода делителя частоты на два напряжение (осциллограмма u:2) подается на делители частоты на 6 и на 4. С прямого выхода делителя частоты на 6 напряжение u:6 поступает на формирователь 39 и дифференцирующую цепь 42. Формирователь напряжения пилообразной формы представляет собой интегратор (элементы R и С на входе схемы фиг.13). Форма пилообразного напряжения на выходе формирователя 39 показана на осциллограмме uфнп39 (фиг.16). Напряжение такой формы подается на формирователь 41 напряжения синусоидальной формы (ФНС). На выходах формирователя 41 получаем два взаимно инверсных напряжения в виде последовательностей полуволн синусоид частотой Ω =π /3Т0 (S2 и S4 на фиг.16).

Дифференцирующая цепь 42 с ограничением по минимуму, выполненная по схеме фиг.14, выделяет короткие импульсы ТИ1, соответствующие положительным фронтам напряжения u:6 (осциллограмма ТИ1 на фиг.16). Дифференцирование импульсов с выхода делителя 36 частоты на 4 и объединение положительных импульсов в элементе 46 ИЛИ дает тактовые импульсы ТИ0 на выходе генератора (осциллограммы u:4 и ТИ0 на фиг.16). Аналогичным образом формируются напряжения S1 и S3 на выходе формирователя 40 и последовательность ТИ2 на выходе дифференцирующей цепи 43; осциллограммы этих сигналов представлены на фиг.16.

Блок предустановки триггеров делителей частоты, схема которого показана на фиг.11, вместе с делителем 34 частоты на два обеспечивает одновременное первоначальное срабатывание делителей частоты на 4 и на 6 от одного фронта входного сигнала и необходимое взаимное расположение выходных сигналов на оси времени в процессе работы. Это обеспечивается следующим образом. При включении питания заряжаются конденсаторы в базовых цепях транзисторов (фиг.11). Постоянная времени цепи заряда второго конденсатора меньше, чем первого, и заданный уровень положительного напряжения на выходе второго транзистора появляется раньше, чем первого. Напряжение с выхода второго транзистора поступает на входы R триггеров в делителях частоты на 4 и на 6 и устанавливает эти триггеры в одинаковое исходное состояние. После этого заданный уровень выходного напряжения появляется на выходе первого транзистора, это напряжение подается на вход R делителя 34 частоты на два и обеспечивает его рабочий режим (режим деления частоты). Первый же перепад напряжения на выходе этого делителя обеспечит одновременное переключение триггеров в делителях на 4 и на 6, т.е. синхронизм работы этих делителей. Полученные сигналы S1-S4 поступают на входы аналоговых ключей, тактовые импульсы ТИ1 и ТИ2 - на анализатор состояния, а ТИ1, ТИ2 и ТИ0 - на преобразователь кода.

Преобразователь кода (фиг.6) решает задачу преобразования двоичного кода с длительностью посылок Т0 в троичный позиционный код с длительностью посылок Tт=1,5· Т0. Принцип работы его поясняется осциллограммами фиг.17. Входной модулирующий двоичный сигнал (осциллограмма uс) поступает на первый вход (S1) регистра 99 сдвига (К555ИР16). Принцип работы этого регистра и режимы его работы описаны в книге: Шило В.Л. Популярные цифровые схемы: Справочник. 2-е изд., испр. - Челябинск: Металлургия. Челябинское отд., 1989. - 352 с.: ил. - (Массовая радиобиблиотека, вып. 1111) на с.111. Вход РЕ регистра для обеспечения режима последовательного ввода двоичного сигнала в регистр соединяется с нулевым потенциалом схемы. На вход С регистра подаются тактирующие импульсы ТИ0. Считывание сигнала осуществляется одновременно с первых трех разрядов регистра подачей на его вход Е0 импульсов ТИ3 (осциллограмма ТИ3). Эти импульсы формируются с помощью расширителя 103 импульсов при действии на входе инвертора (см. фиг.9) тактовых импульсов ТИ1, а на входе С триггера - тактовых импульсов Т0. При действии единичного напряжения ТИ3 регистр выходит из режима Z (режим размыкания), и на его выходах Q0, Q1 и Q2 появляются, соответственно, посылки 1, 2 и 3 из каждой группы последовательно следующих посылок, которые на фиг.17 обозначены стрелками над сигналом uc. Таким образом, посылки каждой группы из трех элементов представляются на выходах регистра в параллельном коде (осциллограммы RG1, RG2 и RG3). Следующая группа элементов преобразователя кода - восемь элементов И (104-111) совместно с инверторами 100-102 НЕ обеспечивает идентификацию кодовой комбинации посылок, полученных на выходах регистра. Если принимается кодовая комбинация 000, то появляется единичная посылка длительностью То на выходе первого элемента И (104), если принимается кодовая комбинация 001, то появляется единичное напряжение на выходе второго элемента И (105) и т.д. Порядковый номер элемента И соответствует числу, определяемому в двоичном коде комбинацией символов на выходах регистра (осциллограммы И104-И111).

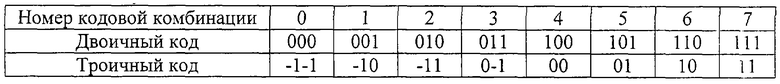

Элементы 112-117 ИЛИ представляют идентифицированную кодовую комбинацию в троичном позиционном коде. Принятое соответствие двоичного и троичного кодов имеет следующий вид:

Первые символы троичного кода представляются в позиционном коде на выходах первых трех элементов ИЛИ (112-114), а вторые символы - на выходах вторых трех элементах ИЛИ (115-117). Единичная посылка на выходе элемента 112 ИЛИ и нули на выходах элементов 113 и 114 ИЛИ означают, что первый символ троичного кода - +1. Единичная посылка на выходе элемента 113 ИЛИ и нули на выходах элементов 112 и 114 ИЛИ означают, что первый символ троичного кода - 0. Единичная посылка на выходе элемента 114 ИЛИ и нули на выходах элементов 112 и 113 ИЛИ означают, что первый символ троичного кода - -1. Точно так же выходы элементов 115-117 ИЛИ определяют второй символ троичного кода. Например, если появляется единичный элемент на выходе элемента 104 И, то это значит, что на входе действует кодовая группа 000, троичная кодовая комбинация согласно вышеприведенной таблице должна иметь вид -1-1 и, следовательно, должны выделиться единичные посылки длительностью То на выходах элементов 114 и 117 ИЛИ. Это обеспечивается соединением выхода элемента 104 И со входами элементов 114 и 117 ИЛИ. По этому принципу соединяются выходы элементов 104-111 И со входами элементов 112-117 ИЛИ.

Расширители 118-123 импульсов (фиг.9) увеличивают длительность единичных посылок. При поступлении на вход S положительного напряжения, которое получается на выходе инвертора после окончания входного импульса, триггер устанавливается в единичное состояние. Тактовые импульсы на входе С переводят триггер в нулевое состояние. Таким образом, передний фронт выходных посылок определяется задним фронтом импульсов на входе инвертора, а задний фронт - передними фронтами импульсов на входе С. Особенность расширителей импульсов в преобразователе кода состоит в различном расширении импульсов: импульсы с выходов элементов 112-114 ИЛИ расширяются до необходимого значения Тт=3Т0/2, а импульсы с выходов элементов 115-117 ИЛИ расширяются до значения 3Т0. Это связано с тем, что единичные импульсы на выходах каждой пары элементов 112-117 ИЛИ появляются одновременно, а поскольку элементы 115-117 ИЛИ определяют второй символ троичного кода, следующий за первым, то соответствующие посылки на выходе преобразователя кода должны появиться позднее тех посылок, которые формируются на выходе из посылок на выходах элементов 112-114 ИЛИ. Задержка посылок осуществляется в два приема: сначала длительность посылок на выходах расширителей 121-123 импульсов устанавливается равной 3Т0, а затем первая половина этих импульсов длительностью 3Т0/2 устраняется в элементах 128-130 НЕТ. Различие в расширении импульсов обеспечивается подачей на расширители импульсов (входы С триггеров КР1533ТМ2) различных тактовых импульсов: на расширители 118-120 импульсов подается последовательность ТИ2, а на расширители 121-123 импульсов - последовательность ТИ1. На временных диаграммах фиг.17 РИ118-РИ123 (РИ - расширители импульсов) показана форма сигналов на выходах расширителей импульсов. Видно, в частности, что окончание импульсов на выходе расширителей 118-120 импульсов определяется импульсами ТИ2, а окончание импульсов на выходах расширителей 121-123 импульсов задается импульсами ТИ1.

Устранение первой половины посылок с выходов расширителей 121-123 импульсов осуществляется в элементах 128-130 НЕТ. Для этого на входы этих элементов подаются, соответственно, сигналы с выходов расширителей 121-123 импульсов, а на запрещающие входы элементов НЕТ подаются сигналы с выходов расширителей 118-120 импульсов, объединенные в элементе 124 ИЛИ. Форма сигналов на выходах элементов 124 ИЛИ и 128-130 НЕТ представлена на фиг.17. Объединение по ИЛИ (элементы 125-127) сигналов с выходов элементов попарно 118 и 128, 119 и 129, 120 и 130 дает выходной сигнал в позиционном троичном коде. Осциллограммы напряжений на выходах элементов 125-127 ИЛИ показаны на фиг.17 (Вых.1, Вых.2 и Вых.3, соответственно).

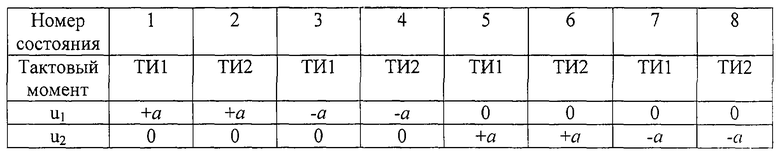

Анализатор 1 состояния фазовращающих напряжений определяет состояние напряжений u1 и u2 на выходах блока ключей в тактовые моменты. Выделяются 8 различающихся состояний, в том числе 4 состояния для тактовых моментов, когда действует импульс ТИ1, и 4 состояния для моментов, когда действует ТИ2. Эти состояния и их номера представлены в таблице:

Из таблицы видно, что состояние 1 имеет место, если в тактовый момент, когда действует тактовый импульс ТИ1, напряжение u1 равно +a, а напряжение u2=0. Состояние 2 имеет место, если в тактовый момент, когда действует тактовый импульс TИ2, выполняются равенства u1=+а, u2=0. И т.д. При этом учитывается, что если в тактовый момент одно из напряжений u1 или u2 равно +а или -а, то второе напряжение обязательно равно нулю.

Анализатор 1 состояния фазовращающих напряжений (фиг.2) имеет 8 выходов. Каждый выход соответствует определенному номеру состояния согласно вышеприведенной таблице. Если анализатор выявляет состояние 1, то появляется единичная посылка длительностью Тт=3Т0/2 на выходе расширителя 25 импульсов. Если выявляется состояние 2, то единичная посылка появляется на выходе расширителя 26 импульсов и т.д. Непосредственный анализ выполняют инверторы 11 и 12 и логические элементы 14-21 И. Из схемы видно, что если имеет место состояние 1, то на выходе элемента 14 И появляется короткий импульс, сформированный из входного импульса ТИ1, действующего на входе анализатора 1 состояния фазовращающих напряжений. В состоянии 2 появляется короткий импульс на выходе элемента 15 И и т.д. Длительность этих импульсов увеличивается до значения Тт в расширителях импульсов, включенных на выходе каждого элемента И. Элементы 13 ИЛИ, 24 НЕТ и 23 ИЛИ образуют схему запуска. В исходном состоянии, при включении модулятора, все аналоговые ключи 85-98 закрыты, следовательно, u1=0 и u2=0. В рабочем режиме такого состояния не бывает, и анализатор 1 состояния фазовращающих напряжений не сформирует единичного напряжения ни на одном из своих выходов. Соответственно, логический блок 3 формирования управляющих напряжений для блока 4 ключей не сработает и не обеспечит открывания ни одного аналогового ключа; весь модулятор останется в нерабочем состоянии. Чтобы осуществить перевод модулятора в рабочий режим, первая единичная посылка на выходе анализатора 1 состояния фазовращающих напряжений формируется принудительно, для чего и служит схема запуска. Она работает следующим образом. Если модулятор включен и блок 2 формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов дает тактовые импульсы ТИ1 и ТИ2, но ни на одном из элементов 14-21 И не появился импульс, то не появится импульс на выходе элемента 13 ИЛИ. А этот импульс является запрещающим для элемента 24 НЕТ. Поэтому элемент 24 НЕТ окажется открытым, и первый же тактовый импульс с выхода элемента 22 ИЛИ через элемент 24 НЕТ и элемент 23 ИЛИ поступит на вход расширителя 25 импульса. Выходной импульс расширителя 25 импульсов обеспечит нормальный режим работы логического блока 3 формирования управляющих напряжений для блока ключей и вхождение модулятора в рабочий режим.

Логический блок 3 формирования управляющих напряжений для блока ключей формирует управляющие напряжения для блока ключей. Основой для формирования управляющих напряжений являются:

- значения напряжений u1 и u2 на выходах блока ключей в каждый тактовый момент и, следовательно, исходное значение фазы выходного напряжения модулятора в этот момент времени;

- необходимые направление и угол поворота вектора выходного напряжения модулятора, начиная от данного тактового момента, за время действия посылки, следующей за этим моментом времени; эти параметры определяются комбинацией посылок, действующих в каждый тактовый интервал Тт на выходах преобразователя кода (Вых.1, Вых.2 и Вых.3 на фиг.17).

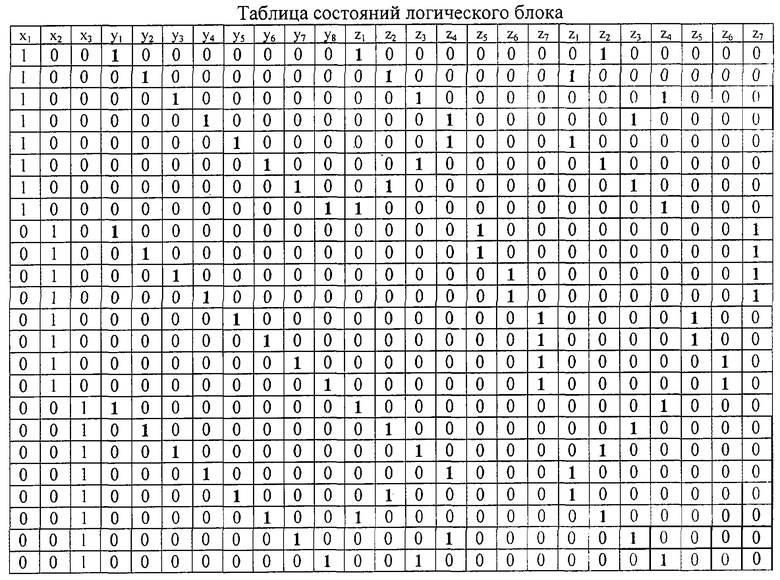

Исходя из состояния модулятора в заданный тактовый момент и действующих модулирующих сигналов в последующий тактовый интервал времени, логический блок 3 формирования управляющих напряжений для блока ключей обеспечивает открывание необходимой пары ключей в блоке 4 ключей. При этом учитывается задаваемый манипуляционный код, определяющий соответствие между передаваемым троичным символом и частотой посылки на выходе модулятора. Выберем, например, следующий манипуляционный код: передаче элемента -1 соответствует частота посылки f1, передаче элемента 0 соответствует частота f2 и передаче элемента +1 соответствует частота f3. При этом для обеспечения своих функций логический блок формирования управляющих напряжений для блока ключей 3 должен иметь следующую таблицу состояний:

В этой таблице x1, x2 и х3 - значения входных модулирующих посылок на входах 1, 2 и 3 логического блока 3 формирования управляющих напряжений для блока ключей, поступающих с выходов преобразователя кода; y1-y8- логические уровни на выходах анализатора 1 состояния фазовращающих напряжений; z1-z7 - логические уровни на выходах элементов, соответственно, 71-77 ИЛИ; z1-z7 - логические уровни на выходах элементов, соответственно, 78-84 ИЛИ логического блока 3 формирования управляющих напряжений для блока ключей. При этом согласно схеме фиг.4 выделяются две группы выходов логического блока 3 формирования управляющих напряжений для блока ключей: выходы элементов 71-77 ИЛИ образуют первую группу, а выходы элементов 78-84 - вторую группу. В первой группе принято: z1 - выход элемента 71 ИЛИ, z2 - выход элемента 72 ИЛИ и т.д. Во второй группе принято: z1- выход элемента 79 ИЛИ, z2 - выход элемента 78 ИЛИ, z3 - выход элемента 81 ИЛИ и т.д. по схеме фиг.4. Структурная схема логического блока 3 формирования управляющих напряжений для блока ключей (фиг.4) составлена согласно вышеприведенной таблице. Сигнал x1 поступает на 1-й (верхний по схеме) вход логического блока 3 формирования управляющих напряжении для блока ключей, сигнал x2 - на 2-й вход, х3 - на 3-й, y1- на 4-й, у2 - на 5-й вход и т.д. Например, если в некоторый тактовой момент анализатор состояния определил 4-е состояние, то это соответствует единицам в столбце у4 таблицы. Предположим, что после этого тактового момента действует единичная посылка на первом входе логического блока 3 формирования управляющих напряжений для блока ключей. Эта ситуация соответствует 4-й строке таблицы. В этой строке таблицы единичное состояние указано для выходов z4 в первой группе выходов и z3 - во второй группе выходов. Это значит, что единичное напряжение в данный тактовый интервал появится на выходах элементов 74 и 81 ИЛИ. Это обеспечивается схемой логического блока: в указанной ситуации откроется элемент 50 И, и с его выхода единичное напряжение поступает на выходы элементов 74 и 81 И (см. схему фиг.4).

Поскольку информация о модулирующем сигнале представляется на трех выходах преобразователя кода, то в модуляторе используются три частоты манипуляции: f1, f2 и f3. Средняя из этих частот равна частоте несущего колебания, формируемого генератором 9 несущей, а две другие симметрично расположены около средней частоты. Для получения на выходе модулятора посылок с частотами f1 и f3 используется плавный поворот вектора несущего колебания, как это делается при двухчастотной модуляции без разрыва фазы в устройстве-прототипе (ММС). Однако частота сглаживающего напряжения в трехчастотном модуляторе выбирается по-другому: если в модуляторе ММС эта частота равна π /2Т0, то в данном случае она равна π /3Т0. Поворот вектора несущего колебания осуществляется функциональными узлами, входящими в ограничительную часть изобретения. Фазовращающие напряжения u1 и u2, действующие на входах амплитудно-фазовых модуляторов 6 и 7 (фиг.9), в этом случае изменяются в течение каждой посылки по гармоническому закону и имеют взаимный фазовый сдвиг на π /2, т.е., например,

или

Эти напряжения определяют амплитуду и фазу напряжений на выходах амплитудно-фазовых модуляторов 6 и 7. Учитывая фазовый сдвиг на π /2, который вносит фазовращатель 8 в несущее колебание, напряжения на выходах амплитудно-фазовых модуляторов определятся, соответственно:

Эти колебания суммируются в сумматоре 10 и дают выходной трехчастотный сигнал

Амплитуда U0 выходного напряжения определится:

Из этого равенства видно, что амплитуда U0 не зависит от времени. Это значит, что в выходном сигнале нет амплитудной модуляции. Фаза выходного напряжения:

Из этой формулы видно, что при модуляции фаза выходного напряжения изменяется в сторону увеличения (знак +) или уменьшения (знак -), и за время одной посылки (t=3Т0/2) набег фазы соствляет π /2.

Такое изменение фазы соответствует смещению частоты на величину

При такой девиации индекс частотной модуляции составляет:

Если же фазовращающие напряжения сделать постоянными на время посылки, например, u1=±a, u2=0 или u1=0, u2=±а, то дополнительного вращения вектора несущего колебания не будет, и частота выходной посылки останется равной несущей частоте, задаваемой генератором 9, т.е. получим f2=f0.

Таким образом, в данном модуляторе осуществляется трехчастотная модуляция с частотами манипуляции

f1=f0-fд=f0-1/(6· T0), f2=f0, f3=f0+fд=f0+1/(6· T0).

Фаза ВЧ-посылок при этом линейно изменяется или остается неизменной в тактовые интервалы времени и не имеет скачков на их границах.

Работа трехчастотного модулятора в целом поясняется осциллограммами фиг.18. При включении трехчастотного модулятора блок 2 формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов формирует три последовательности тактовых импульсов ТИ0, ТИ1 и ТИ2, показанные на соответствующих осциллограммах фиг.18. Предположим, что на вход модулятора подается двоичный модулирующий сигнал uс (см. фиг, 18) с длительностью элементов Т0 (этот сигнал принят таким же, как на фиг.17). Тогда на трех выходах преобразователя кода сформируются три последовательности X1, X2 и Х3 (см. фиг.18) с длительностью элементов 3Т0/2 (они совпадают с сигналами, показанными на осциллограммах “Вых.1”. “Вых.2” и “Вых.3” на фиг.17). В строке уi указаны номера состояний выходов блока 4 ключей, которые определяет анализатор 1 состояния. В первый тактовый момент, когда действует передний фронт сигналов Xi, сработает устройство запуска в анализаторе 1 состояния фазовращающих напряжений и сформирует импульс длительностью 3Т0/2 на выходе расширителя 25 импульсов, что соответствует первому состоянию выходов блока ключей. Этот импульс поступит на вторые входы элементов 47, 55 и 63 И в логическом блоке 3 формирования управляющих напряжений для блока ключей. Поскольку в первый тактовый интервал сигналы Xi имеют значения 0-1-0, то единичное напряжение Х2, которое действует на втором сверху (по схеме фиг.4) входе логического блока 3 формирования управляющих напряжений для блока ключей подается на первые входы элементов 55-62 И. В результате единичные напряжения окажутся на обоих входах элемента 55 И. На выходе этого элемента появится единичное напряжение длительностью 3Т0/2, которое через элемент 75 ИЛИ воздействует на ключ 89, а через элемент 84 ИЛИ воздействует на ключ 98. Эти ключи открываются, и на вход амплитудно-фазового модулятора 6 подается постоянное напряжение с уровнем а, а на вход амплитудно-фазового модулятора 7 - напряжение с нулевым уровнем. Эти напряжения показаны, соответственно, на осциллограммах u1 и u2 на фиг.18.

Во второй тактовый момент, т.е. в момент окончания первых посылок X1, X2 и Х3 действует импульс ТИ2. В анализаторе 1 состояния фазовращающих напряжений этот импульс воздействует на 4-й сверху (по схеме фиг.2) вход и подается на входы элементов 15, 17, 19 и 21 И, а также на элемент 22 ИЛИ. Одновременно напряжение u1 с уровнем +а поступает на верхний (по схеме фиг.2) вход анализатора 1 состояния фазовращающих напряжений и подается на первые входы элементов 14 и 15 И. На обоих входах элемента 15 И оказывается положительное напряжение, на выходе его появляется тактовый импульс, который подается на вход расширителя 26 импульсов, на выходе которого формируется импульс длительностью 3Т0/2. Появление импульса на выходе расширителя 26 импульсов свидетельствует о втором состояния выходов блока ключей, что и отмечено в строке уi фиг.18 (второй тактовый момент). Этот импульс поступает на вторые входы элементов 48, 56 и 64 И в логическом блоке 3 формирования управляющих напряжений для блока ключей. В этот тактовый момент на выходах преобразователя кода формируется кодовая комбинация 1-0-0 (фиг.18). Единичное напряжение X1 подается на первый (по схеме фиг.4) вход логического блока 3 формирования управляющих напряжений для блока ключей и воздействует на первые входы элементов 47-54 И. В результате единичное напряжение окажется на обоих входах элемента 48 И, на выходе его появится единичное напряжение, которое через элементы 72 и 79 ИЛИ откроет ключи 86 и 92. Через ключ 86 на вход амплитудно-фазового модулятора 6 поступит сигнал S2, а через ключ 92 на вход амплитудно-фазового модулятора 7 поступит сигнал S1. Форма этих напряжений в тактовый интервал, начинающийся с момента ТИ2, показана на фиг.16. Эта же форма показана на осциллограммах u1 и u2 во второй тактовый интервал. Продолжая аналогичные рассуждения для последующих тактовых интервалов, получим временные диаграммы фазовращающих напряжений u1 и u2, поступающих на входы амплитудно-фазовых модуляторов 6 и 7 трехчастотного модулятора. Далее обычным образом работают элементы 6-10 частотного модулятора, входящие в ограничительную часть формулы изобретения. При этом напряжение u1, воздействуя на модулирующий вход первого амплитудно-фазового модулятора 6, изменяет (или оставляет неизменными) амплитуду и фазу ВЧ-напряжения на его выходе; в зависимости от полярности u1 фаза выходного напряжения модулятора 6 может принимать значения 0 или π , а амплитуда изменяется по закону модулирующего напряжения. Напряжение u1 воздействует на модулирующий вход второго амплитудно-фазового модулятора 7 и также изменяет его амплитуду и фазу; фаза, в зависимости от полярности u2, может принимать значения π /2 или 3π /2. Сложение выходных напряжений амплитудно-фазовых модуляторов в сумматоре 10 дает трехчастотное напряжение на выходе модулятора. На последующих осциллограммах фиг.18 показаны изменение фазы ϕ и частоты fi выходного напряжения модулятора. Выходное напряжение в течение каждой посылки изменяется по гармоническому закону.

В данном модуляторе используются три взаимосвязанных фактора, обеспечивающие уменьшение реальной ширины спектра модулированного сигнала и достижение технического результата изобретения. Во-первых, уменьшение тактовой частоты модулированного сигнала в 1,5 раза при сохранении скорости передачи информации. Поскольку реальная ширина спектра пропорциональна тактовой частоте или обратно пропорциональна длительности посылок, то уменьшение тактовой частоты соответственно уменьшит занимаемую сигналом полосу частот. Во-вторых, уменьшение в 1,5 раза девиации частоты. В-третьих, использование трех частот манипуляции; третья частота располагается посередине между двумя другими, которые используются в двухчастотных модуляторах, и ее использование концентрирует спектр модулированного сигнала. Трехчастотная манипуляция обеспечивает передачу трехпозиционного модулирующего сигнала, который образуется в модуляторе при понижении тактовой частоты.

Возможность уменьшения тактовой частоты модулированного сигнала при сохранении скорости передачи информации определяется различием информационной емкости С сигналов с различным основанием кода М:

C=log2M (бит).

Для двоичного кода (М=2) получаем С=1, т.е. одна информационная посылка содержит 1 бит информации. Для троичного кода (М=3) из представленной формулы получаем С=1,585, т.е. одна троичная посылка содержит 1,585 бит информации. Следовательно, при передаче информации троичным кодом можно в 1,585 раза уменьшить скорость передачи посылок или в 1,585 раза увеличить длительность посылок. Скорость передачи информации при этом остается без изменений.

Расчеты показывают, что реальная ширина спектра трехчастотного сигнала, определенная при относительной мощности сигнала 99%, составляет 0,7· V (при ММС - 1,18· V); при этом выигрыш по пропускной способности канала связи составляет 1,5 раза. Если реальную ширину спектра сигнала определять при относительной мощности сигнала 90%, то выигрыш составит 2 раза, т.к. в этом случае реальная ширина спектра трехчастотного сигнала в два раза меньше по сравнению с сигналом ММС.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХВХОДОВОЙ ЧАСТОТНЫЙ МОДУЛЯТОР | 2003 |

|

RU2248090C2 |

| ЧАСТОТНЫЙ МОДУЛЯТОР С ЦЕЛОЧИСЛЕННЫМ ИНДЕКСОМ МОДУЛЯЦИИ | 2003 |

|

RU2255414C1 |

| ЧАСТОТНЫЙ МОДУЛЯТОР С РАЗДЕЛЕНИЕМ СПЕКТРА | 2003 |

|

RU2255415C1 |

| Устройство для передачи телеизмерительной информации | 1982 |

|

SU1070593A2 |

| Частотный модулятор | 1980 |

|

SU951641A1 |

| АКУСТООПТИЧЕСКИЙ АНАЛИЗАТОР СПЕКТРА | 1992 |

|

RU2024026C1 |

| Демодулятор телеграфных сигналов | 1971 |

|

SU448588A1 |

| Устройство для управления трехфазным мостовым инвертором | 1984 |

|

SU1297194A1 |

| МАЛОГАБАРИТНЫЙ РАДИОЛОКАТОР ТРАНСПОРТНОГО СРЕДСТВА | 1997 |

|

RU2117964C1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1254589A1 |

Изобретение относится к технике радиосвязи и может применяться в системах подвижной наземной и спутниковой связи. Технический результат заключается в уменьшении реальной ширины спектра модулированного сигнала при сохранении индекса частотной манипуляции m=0,5. Устройство содержит анализатор состояния фазовращающих напряжений 1, блок формирования последовательностей сигналов заданной формы и последовательностей тактовых импульсов 2, логический блок формирования управляющих напряжений для блока ключей 3, блок ключей 4, преобразователь кода 5, два амплитудно-фазовых модулятора 6, 7, фазовращатель 8, генератор несущей 9, сумматор 10. В изобретении решается задача использования трех частот манипуляции для создания частотно-манипулированного сигнала без разрыва фазы. 18 ил., 3 табл.

| ЧАСТОТНЫЙ МОДУЛЯТОР | 1989 |

|

RU2012150C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННОГО СИГНАЛА | 1996 |

|

RU2110145C1 |

| УСТРОЙСТВО ДЛЯ ФОРМОВАНИЯ ЧАСТОТНО-МОДУЛИРОВАННОГО СИГНАЛА | 1992 |

|

RU2039414C1 |

| US 2001016017, 23.08.2001. | |||

Авторы

Даты

2004-11-10—Публикация

2003-04-21—Подача