Изобретение относится к микропроцессорному устройству с микропроцессором и периферийным блоком, которые связаны между собой шиной данных. На концах шины предусмотрены криптографические блоки.

Микропроцессорные устройства, в случае которых поток данных, передаваемый по шинам данных, криптографически зашифровывается, используются в приложениях, критичных с точки зрения обеспечения защиты. Например, такие микропроцессорные устройства служат в качестве схем управления для мобильных карт носителей данных, так называемых чип-карт. В памяти данных микропроцессорных устройств сохраняются персонализированные данные, значения денежных средств или данные предоставления права доступа, которые считываются устройством считывания, которое затем обеспечивает свободный доступ к функциональному блоку, защищенному от несанкционированного доступа.

Так как в процессе обмена данными в микропроцессорном устройстве используются конфиденциальные данные, в отношении которых должна быть обеспечена невозможность несанкционированного доступа, требуются соответствующие меры защиты. Несанкционированное считывание памяти данных устройства или перехват внутреннего для устройства обмена данными мог бы реализовываться с помощью зондирования, при котором тонкие щупы устанавливаются в соответствующих частях схемы и проводников, чтобы создать тем самым ответвление обрабатываемого потока сигнала в рабочем режиме. Использование шин требует, вследствие относительно высоких паразитных емкостей, повышенного потребления тока схем. Доступ к шине извне наблюдается по характерному профилю тока. Отсюда можно сделать выводы о внутренних рабочих этапах схемы; в определенных обстоятельствах было бы даже возможно определить ключ криптографического блока.

Защитные меры от несанкционированного считывания содержимого памяти данных в микроконтроллере для чип-карты описаны в DE 19642560 А1. В памяти данных в зашифрованном виде хранятся принципиально важные для обеспечения защиты данные. В шине данных между памятью и центральным процессорным блоком (ЦПБ) включено устройство дешифрирования, чтобы в ЦПБ можно было обрабатывать дешифрированные исходные данные. При записи вновь данных в память данные вновь зашифровываются. В возможном варианте осуществления способы шифрования и дешифрирования реализуются двухэтапным образом. В соответствии с этим по одному устройству шифрования и дешифрирования включено на стороне памяти и соответствующих периферийных блоков, а также на стороне ЦПБ.

Проблематичным является обеспечение того, чтобы обмен данными по шине зависимости от варианта осуществления, был либо полностью, либо частично зашифрован. За счет зондирования можно было бы информационный обмен, который осуществляется по шине, перехватить относительно простыми средствами. Потребовались бы дополнительные, например, механические меры, чтобы обеспечить эффективную защиту от несанкционированного доступа.

Задача настоящего изобретения состоит в том, чтобы создать микропроцессорное устройство, защищенность которого по отношению к несанкционированному прослушиванию зашифрованных процессов была бы повышена.

В соответствии с изобретением эта задача решается микропроцессорным устройством, которое содержит центральный блок обработки и по меньшей мере один периферийный блок, которые связаны между собой шиной данных; первый криптографический блок, который находится в упомянутом периферийном блоке и подключен к шине данных; второй криптографический блок, который находится в упомянутом центральном блоке обработки и подключен к шине данных, и генератор случайного сигнала для выработки последовательности значений данных, который связан с первым и с вторым криптографическим блоком для подачи на них упомянутых значений данных, причем криптографический режим первого и второго криптографических блоков может управляться в зависимости от значений данных, выработанных генератором случайного сигнала.

В соответствии с изобретением, информационный поток, выдаваемый функциональным блоком микропроцессорного устройства в шину данных, зашифровывается и на входе приемного блока вновь дешифрируется. Режим шифрования и дешифрирования управляется от генератора случайного сигнала, так что какое-либо рабочее состояние в способе шифрования/дешифрирования невозможно предсказать детерминированным образом. Тем самым повышается защищенность информационного обмена, осуществляемого посредством шины данных. Вследствие этого отпадает необходимость в использовании механических средств защиты, предохраняющих шину данных от несанкционированного доступа с использованием щупов. За счет управления случайным образом процессом шифрования/дешифрирования обеспечивается создание соответствующего случайного профиля тока, благодаря чему прослушивание информационного обмена в шине данных становится невозможным.

В принципе, изобретение может быть использовано в любой микропроцессорной системе, в которой центральный блок обработки (центральный процессорный блок) обменивается по шине данными и адресами с периферийными блоками, включая блок памяти. Устройство может быть реализовано как с дискретными элементами, так и по монолитной интегральной технологии на одном полупроводниковом кристалле, в виде так называемого микроконтроллера.

Предпочтительным образом, случайные числа для управления шифрованием и дешифрированием подаются с тактовой синхронизацией на соответствующие блоки. Для этого предусмотрен проводник тактового сигнала, соединяющий между собой все блоки шифрования/дешифрирования. Кроме того, эти блоки соединены между собой проводником, по которому случайные числа передаются дальше. Для повышения надежности защиты целесообразно оба названных проводника защитить посредством механического экранирования от перехвата с использованием щупов. Однако при этом не необходимости в соответствующей защите множества остальных проводников шин данных.

Также возможно случайные значения для ключа передать в криптографические блоки посредством шины и проводника управления. Отдельный проводник 5 в этом случае не нужен. Тем самым можно не только данные шины, но и управляющие сигналы, так называемые состояния шины, передавать в зашифрованном виде.

Блок шифрования/дешифрирования содержит предпочтительным образом регистр сдвига с обратной связью, который управляется общим тактовым сигналом и последовательно подаваемым случайным числом. Выдаваемое с выхода регистра сдвига слово данных логически связывается с выдаваемым в шину или принимаемым из шины словом данных, например за счет использования логической схемы “исключающее ИЛИ”. Обратная связь, используемая в регистре сдвига, предпочтительно является линейной.

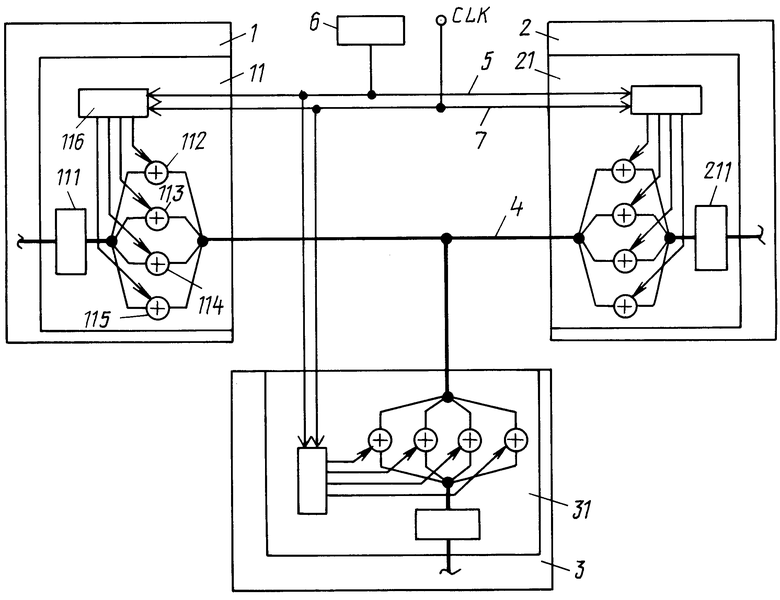

Ниже изобретение описано на примере осуществления со ссылками на чертеж, на котором показано схематичное представление центрального блока обработки (центрального процессорного блока - ЦПБ), блока памяти и дополнительного периферийного блока, которые выполнены в виде монолитной интегральной схемы микроконтроллера.

Показанный на чертеже микроконтроллер содержит центральный блок обработки или ЦПБ 1, блок 2 памяти и периферийный блок 3. Периферийный блок 3 может представлять собой, например, блок ввода/вывода. Все компоненты микроконтроллера выполнены в виде одной кремниевой интегральной схемы. ЦПБ 1 имеет функции управления данными и вычислений, блок 2 памяти содержит данные, сохраненные в энергозависимой памяти и в энергонезависимой памяти, а периферийный блок 3 служит для выполнения предписанной ему функции. В общем случае микроконтроллер содержит и другие функциональные блоки. Обмен данными между указанными блоками производится по шине 4 данных. Шина данных включает в себя множество проводников, по которым параллельно передаются данные. Кроме того, шина содержит соответствующие проводники управления, предназначенные для управления передачей данных. На обращенных к шине данных входе и выходе блоков 1, 2, 3 подключен соответствующий криптографический блок 11, 21, 31. Передаваемый по проводникам шины данных поток данных, вводимый в соответствующий блок или соответственно или выводимый из этого блока, расшифровывается или соответственно зашифровывается с помощью соответствующего криптографического блока.

Например, ЦПБ запрашивает слово данных из блока 2 памяти. Слово данных считывается из соответствующей ячейки памяти блока 2 памяти и сохраняется промежуточным образом в регистре 211. С помощью внутренних схем криптографического блока 21 слово данных зашифровывается и выдается в шину 4. Криптографический блок 11 ЦПБ 1 принимает это слово данных, чтобы расшифровать его и сохранить промежуточным образом в регистре 111. Во время передачи слова данных по шине 4 от блока 2 памяти к ЦПБ 1 это слово данных существует только в зашифрованной форме. Шифрование и дешифрирование в блоках 21 или 11 выполняется в зависимости от случайного числа, которое обеспечивается от генератора 6 случайных чисел, выход которого посредством проводника 5 соединен с блоками 21, 11. Ввод случайного числа в оба блока 21, 11 производится синхронизированным образом с помощью тактового сигнала CLK, вводимого по проводнику 7 в оба устройства 21, 11. Генератор 6 случайных чисел вырабатывает (псевдо)случайную последовательность битов, которая синхронно, с помощью тактового сигнала CLK, подается на криптографические блоки 21, 11.

За счет управления с использованием случайных чисел шифрованием и дешифрированием данных обеспечивается повышение эффективности защиты передаваемых по шине 4 значений данных. Синхронное управление обеспечивает то, что этапы шифрования и дешифрирования в передающем и соответственно принимающем блоках в одном и том же временном интервале являются взаимодополняющими процессами. Вследствие случайного характера шифрования, несмотря на повторяющиеся в конечном счете передаваемые данные, в шине формируются различающиеся битовые комбинации. Профиль тока в интегральной схеме, который, вследствие относительно высоких перезаряжаемых емкостных нагрузок шины, относительно просто мог бы быть измерен извне, представляется некоррелированным во времени и случайным. Поэтому профиль тока при попытках считывания не может быть использован, чтобы распознать какие-либо характеристические состояния переключений микроконтроллера.

Чтобы еще больше повысить эффективность защиты, достаточно защитить от попыток зондирования или использования щупов для ответвления тока только проводники 5 и 7, предназначенные для подачи случайных чисел и тактового сигнала шифрования/дешифрирования. Для этого могут быть использованы обычные известные меры. Например, проводники могут быть покрыты дополнительным слоем, при удалении которого проводники разрушаются и становятся непригодными для применения.

Все три показанные на чертеже блока шифрования/дешифрирования 11, 21, 31 построены одинаковым образом. Поэтому для примера ниже более подробно рассматривается блок 11. На стороне ЦПБ 1 регистр 111 служит для промежуточного сохранения слова данных, принятого от ЦПБ или выдаваемого к нему. На стороне подключения к шине данных для каждого из проводников данных шины используется логическая схема. В представленном примере используются логические схемы “исключающее ИЛИ” 112, 113, 114, 115. Каждая из логических схем “исключающее ИЛИ” одним своим входом и своим выходом включена в один из проводников шины данных, а другой ее вход соединен с соответствующим выходом регистра 116 сдвига, который выполнен, например, с линейной обратной связью. Регистр 116 сдвига со стороны входов соединен с проводником 7 тактового сигнала и с проводником 5 для подачи случайных чисел. Случайное число, вырабатываемое генератором 6 случайных чисел, подается последовательно по проводнику 5 на регистр 116 сдвига с обратной связью, причем тактовое управление осуществляется с помощью тактового сигнала CLK. Обратная связь регистра 116 сдвига обеспечивает то, что на его выходных выводах в каждом временном такте имеется отличающееся слово данных, которое посредством логических схем “исключающее ИЛИ” 112,..., 115 логически связывается со словом данных, выдаваемым в шину 4 или принимаемым из шины 4. При запуске регистры сдвига инициализируются одним и тем же значением. Так как другие криптографические блоки выполнены и подключены аналогичным образом, то слова данных, передаваемые по шине 4 данных, зашифровываются в месте передачи и расшифровываются в месте приема взаимодополняющим образом. Шифрование и дешифрирование симметричны по отношению друг к другу. В принципе достаточно, чтобы регистр 116 сдвига не имел обратной связи. Однако использование обратной связи повышает эффективность защиты. Для реализации обратной связи достаточно использовать линейную обратную связь на основе примитивного полинома. В соответствии с параллельностью, зашифровывается соответствующее количество битов из регистра сдвига. На стороне передачи и приема производится синхронное шифрование и соответственно дешифрирование с использованием одного и того же случайного числа. Вследствие симметричности шифрования передача, не играет никакой роли.

Схемотехнические затраты на выработку случайных чисел и тактового сигнала, а также схемотехнические затраты на регистр сдвига с линейной обратной связью, регистр ввода/вывода и логические схемы “исключающее ИЛИ” являются оправданными. В то же время защита от несанкционированного прослушивания передаваемых по шине данных и несанкционированного измерения профиля тока, с учетом дополнительных затрат, существенно повышается.

Изобретение относится к микропроцессорному устройству с микропроцессором и периферийным блоком. Техническим результатом является повышенная защищенность этого устройства от несанкционированного доступа. Устройство содержит центральное устройство обработки, включающее в себя первый криптографический блок, по меньшей мере, периферийный блок, включающий в себя второй криптографический блок, устройство также содержит шину данных, генератор случайных чисел, проводник для подачи тактового сигнала, проводник для подачи сигнала случайных чисел, совокупность логических элементов связи, причем каждый криптографический блок содержит регистр сдвига с обратной связью. 6 з.п. ф-лы, 1 ил.

| МЕХАНИЗМ ВЗАИМОАУТЕНТИФИКАЦИИ В РАСПРЕДЕЛЕННЫХ ИНФОРМАЦИОННО-УПРАВЛЯЮЩИХ СИСТЕМАХ | 1998 |

|

RU2126170C1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА К ИНФОРМАЦИИ, ХРАНИМОЙ В ПЕРСОНАЛЬНОЙ ЭВМ | 1995 |

|

RU2067313C1 |

| EP 0790547 A1, 20.08.1997 | |||

| СПОСОБ ГЕРМЕТИЗАЦИИ РЕЗЬБОВЫХ СОЕДИНЕНИЙ ТРУБ НЕФТЯНОГО СОРТАМЕНТА | 1995 |

|

RU2099616C1 |

| БОЛЬШАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 1990 |

|

RU2068602C1 |

| US 5943421 А, 24.08.1999. | |||

Авторы

Даты

2005-05-10—Публикация

2000-11-30—Подача