Изобретение относится к устройству с интегральной схемой и к интегральной схеме с функциональными модулями, причем функциональные модули включают в себя центральный блок обработки, посредством которого обрабатываются данные и выполняются программы, и кэш-память.

Устройства с интегральными схемами вышеописанного типа находят в настоящее время широкое применение во всех предметах повседневного спроса с встроенной электроникой. Приборы для электронной обработки данных, связи или записи данных содержат, в зависимости от типа обрабатываемых данных, средства, которые ограничивают считывание, запись данных или доступ к данным для их изменения. Тем самым данные должны быть защищены от неограниченного доступа или манипуляций. В частности, в области будущего поколения бортовых самописцев, цифровых тахографов, защита регистрируемых данных от манипулирования имеет очень большое значение.

Нынешние защищенные от манипулирования системы с высокими требованиями по обеспечению защиты состоят обычно из нескольких дискретных конструктивных узлов, с которыми связаны различные функции, например центральный блок обработки, блок шифрования и различные блоки памяти обычно образуют, соответственно, отдельный блок, который соединяется с остальными блоками. Требование наличия нескольких конструктивных узлов и их компоновка, а также согласование друг с другом приводят к высоким затратам при серийном производстве.

Исходя из проблем и недостатков уровня техники, задача настоящего изобретения заключается в том, чтобы создать устройство вышеназванного типа, которое удовлетворяет самым высоким требованиям по обеспечению защиты от манипулирования, при одновременной пригодности для серийного производства при более низких затратах.

Соответствующая изобретению задача решается посредством интегральной схемы вышеуказанного типа, которая содержит блок шифрования в качестве функционального модуля, посредством которого данные или программные коды могут зашифровываться и расшифровываться.

За счет того, что блок шифрования в качестве функционального модуля интегральной схемы представляет собой элемент этого конструктивного узла, при изготовлении и дальнейшем совершенствовании устройства с соответствующей изобретению интегральной схемой, можно сэкономить на дополнительной подготовке, монтаже и настройке для согласования со смежными конструктивными элементами. На основе синэргического эффекта, обеспечивается дополнительное существенное преимущество, заключающееся в том, что блок шифрования лишь с большим трудом можно было бы отделить от интегральной схемы, в связи с чем, все попытки манипулирования будут обречены на неудачу.

Манипулирование соответствующей изобретению интегральной схемой, в частности, отделение отдельных функциональных модулей, оказывается особенно проблематичным, если интегральная схема выполнена как полупроводниковый чип, в частности, если отдельные функциональные модули сопряжены друг с другом подобно элементам головоломки таким образом, что отдельные функциональные модули невозможно распознать по отдельности. Для этого могут применяться, например, особенно сложные геометрические переплетения, так что перемешанные друг с другом полупроводниковые структуры уже невозможно будет распознать по отдельности как таковые, посредством анализа в целях манипулирования.

Дополнительная защита от манипулирования обеспечивается в том случае, если функциональные модули включают в себя первую память, в которой сохранены криптографические ключи. Интеграция подобной первой памяти затрудняет целенаправленный доступ и целенаправленное считывание криптографических ключей.

Затраты на обращение с криптографическими ключами изготовителем прибора полностью перекрываются за счет дополнительного выигрыша от защищенности, если функциональные модули включают в себя генератор случайных чисел, который автономным образом вырабатывает криптографические ключи. Эти ключи могут предпочтительным образом сохраняться в первой памяти.

Предпочтительным образом, в качестве еще одного функционального модуля в интегральную схему могут быть включены часы реального времени, корректное функционирование которых также имеет большую важность для защиты от манипулирования.

Для того чтобы не только затруднить манипулирование, но сделать его невозможным, предпочтительным образом, сенсорные средства защиты могут интегрироваться в интегральную схему в качестве функционального модуля, посредством которого может контролироваться, по меньшей мере, один рабочий параметр интегральной схемы. Подходящими параметрами для контроля являются, например, тактовая частота часов реального времени, системная тактовая частота или тактовая частота центрального процессора, или рабочая температура, или рабочее напряжение интегральной схемы, или состояние защитного слоя на интегральной схеме, или комбинация названных рабочих параметров. Если интегральная схема выполнена как полупроводниковый конструктивный элемент, то контроль состояния защитного слоя на интегральной схеме является особенно эффективным, так как защитный слой должен быть разрушен, чтобы механически получить доступ к структуре полупроводникового чипа. При этом предпочтительно, если защитный слой выполнен в качестве активного защитного слоя и непосредственно нанесен на кристалл полупроводникового чипа. Предпочтительный вариант осуществления предусматривает, что активный защитный слой состоит из, по меньшей мере, одного удлиненного электрического проводника, который проходит вдоль поверхности кристалла, в частности, на участках в виде параллельных друг другу дорожек. Контроль может заключаться в контроле омического сопротивления электрического проводника, причем предпочтительным образом, изменение значения сопротивления, которое может быть обусловлено разрушением электрического проводника, вызывает стирание подлежащих защите данных. Предпочтительным образом, микроконтроллер переводится в защищенное состояние, например, устанавливается в исходное состояние. Таким способом система «интегральной схемы», соответствующая изобретению, обеспечивает самозащиту.

Предпочтительным образом, контроль рабочего параметра реализуется таким образом, что, по меньшей мере, задается граничное значение для контролируемого рабочего параметра, рабочий параметр измеряется и сравнивается с граничным значением, и, при превышении граничного значения или уменьшении ниже граничного значения, содержание первой памяти стирается. Предпочтительным образом, граничное значение выбирается таким образом, чтобы заданные величины нормального режима не приводили к прерыванию функционирования устройства, например, для применения на автомобилях, чтобы при температуре -40оС еще не происходило стирания данных.

Удобство в обращении и защищенность соответствующей изобретению интегральной схемы повышаются дополнительно в том случае, если она размещается в корпусе и имеет выведенные из корпуса соединительные контакты. В соответствии с этим для механического манипулирования следовало бы сначала открыть корпус.

Высокая степень интеграции соответствующей изобретению интегральной схемы может достигаться в том случае, если отдельные функциональные модули имеют, по существу, плоскую протяженность и в направлении нормали к плоскости размещены рядом друг с другом. Так, например, центральный блок управления может размещаться как уложенный в стопку вместе с различными блоками памяти и другими функциональными модулями.

Предпочтительным образом, попытки взлома для получения сведений о функциональном состоянии из режима тока питания интегральной схемы могут предотвращаться в том случае, если функциональные модули содержат встроенный регулятор напряжения, который регулирует рабочее напряжение и таким способом обеспечивает относительное маскирование рабочих параметров для постороннего наблюдателя.

Особые преимущества обеспечиваются соответствующей изобретению интегральной схемой в устройстве со вторым блоком памяти, который посредством шины данных связан с соответствующей изобретению интегральной схемой, в этом втором блоке памяти сохранены в зашифрованном виде данные или программный код, причем второй блок памяти содержит ячейки памяти, которые имеют, соответственно, адрес памяти, и каждая ячейка памяти обеспечивает прямое обращение к ней для считывания или записи. Чтобы все устройство защитить от отказа внешнего источника питания, целесообразно соединить его с батареей питания, так что питающее напряжение поддерживается и при отсутствии другого энергопитания. Можно также сэкономить затраты, если второй блок памяти экономичным образом выполнить как энергозависимый и обеспечить его поддержку посредством батареи питания.

В качестве альтернативы или в дополнение ко второму блоку памяти может оказаться целесообразным использование третьего блока питания, который соединяется с интегральной схемой посредством шины данных и выполнен как энергонезависимый блок, в частности, как флэш-память или ПЗУ, причем в третьем блоке памяти сохранены, предпочтительно в зашифрованном виде, данные или программный код.

Особенно предпочтительной является буферизация сенсорных средств защиты с помощью батареи питания. В качестве альтернативы, или в дополнение к этому, в корпусе может быть предусмотрен встроенный вспомогательный источник энергии, например, конденсатор, который, в случае зафиксированной попытки манипулирования, обеспечивает энергию для стирания содержимого блока памяти, в частности, первого блока памяти.

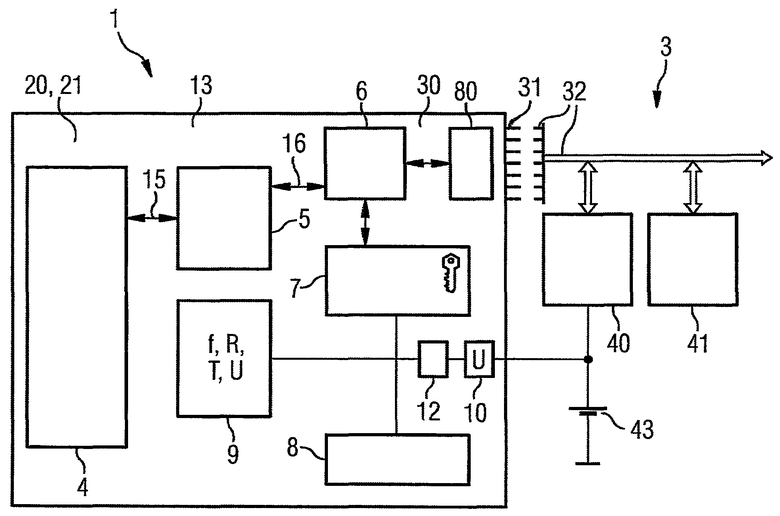

Далее изобретение описано более подробно на конкретном примере выполнения. Наряду с данным примером выполнения, из представленного описания изобретения для специалиста в данной области техники были бы очевидны многочисленные другие возможности выполнения. В частности, изобретение также включает в себя комбинации признаков, которые вытекают из комбинаций пунктов формулы изобретения, если даже на это не дается ссылка в явном виде. На чертеже показано схематичное представление соответствующего изобретению устройства.

На чертеже показана интегральная схема 1 с различными функциональными модулями 2, которая соединена с внешними конструктивными элементами 3. Интегральная схема содержит, наряду с центральным блоком 4 обработки, еще другие функциональные модули 2, а именно, кэш-память 5, блок 6 шифрования, первый блок 7 памяти, часы 8 реального времени, генератор 80 случайных чисел, сенсорное средство 9 защиты. Кроме того, регулятор 10 напряжения и вспомогательный источник 12 энергии являются встроенными конструктивными элементами интегральной схемы 1, выполненной в виде полупроводникового чипа 13. Центральный блок 4 обработки обрабатывает данные или исполняет программу, которую он считывает посредством шины 15 данных из кэш-памяти 5.

Кэш-память 5 соединена с блоком 6 шифрования посредством второй шины 16 данных. Блок 6 шифрования считывает из второго или третьего блока 40, 41 памяти посредством адресной шины 32 данных зашифрованные данные или код, расшифровывает их с помощью сохраненного в первом блоке 7 памяти криптографического ключа 18 и записывает их в кэш-память или в другой внутренний регистр центрального блока 4 обработки. Криптографические ключи 18 перед этим были выработаны генератором 80 случайных чисел. Генератор 80 случайных чисел применяет для выработки криптографических ключей 18, которые сохранены в первом блоке 7 памяти, например начальные значения из статистических колебаний (шумов) внутренних физических измеренных величин, таких как температура чипа, напряжение питания, тактовая частота.

Сенсорное средство 9 защиты контролирует, наряду с рабочей температурой Т, рабочим напряжением U, тактовой частотой f, также омическое сопротивление R защитного слоя 20, который состоит из, по существу, параллельных друг другу дорожек электрического проводника 21, которые нанесены непосредственно на кристалл полупроводникового чипа 13. Измеренное сопротивление R постоянно сравнивается с граничным значением, превышение граничного значения вызывает стирание центральным блоком 4 обработки содержимого первого блока 7 памяти, причем интегральная схема 1 затем переводится в защищенное состояние, например, путем установки в исходное состояние.

Интегральная схема 1 помещена в корпус 30, который имеет соединительные контакты 31, которые, по меньшей мере, частично соединены с адресной шиной 32 данных. Посредством адресной шины 32 данных интегральная схема 1 обменивается данными со вторым блоком 40 памяти и третьим блоком 41 памяти. Второй блок 40 памяти выполнен как энергозависимое ОЗУ и посредством батареи 43 защищается от пропадания напряжения питания, так же, как и интегральная схема 1. Третий блок 41 памяти выполнен как энергонезависимый блок, в виде флэш-памяти или ПЗУ. Данные, сохраненные во втором блоке 40 памяти и в третьем блоке 41 памяти, зашифровываются с помощью криптографических ключей 18 и при каждом доступе зашифровываются и расшифровываются с помощью блока 6 шифрования.

Изобретение относится к интегральной схеме с функциональными модулями, причем функциональные модули включают в себя центральный блок обработки, посредством которого могут обрабатываться данные и выполняться программы, и кэш-память. Техническим результатом является обеспечение защиты от несанкционированного доступа и манипуляций. Интегральная схема для обработки данных с функциональными модулями, включающими в себя центральный блок обработки, посредством которого могут обрабатываться данные и выполняться программы, кэш-память, блок шифрования, посредством которого данные могут зашифровываться и расшифровываться, датчик безопасности, посредством которого может контролироваться, по меньшей мере, один рабочий параметр (f, Т, U) интегральной схемы, причем в качестве рабочего параметра (f, Т, U) контролируется состояние защитного слоя на интегральной схеме, первый блок памяти, причем для контролируемого рабочего параметра (f, Т, U) задается граничное значение, рабочий параметр (f, Т, U) измеряется и сравнивается с граничным значением, и при превышении граничного значения или уменьшении ниже граничного значения содержание первого блока памяти стирается. 6 н. и 11 з.п. ф-лы, 1 ил.

1. Интегральная схема (1) для обработки данных с функциональными модулями (2), причем функциональные модули (2) включают в себя центральный блок (4) обработки, посредством которого могут обрабатываться данные и выполняться программы, и кэш-память (5), причем функциональные модули (2) включают в себя блок (6) шифрования, посредством которого данные могут зашифровываться и расшифровываться, и функциональные модули (2) включают в себя датчик (9) безопасности, посредством которого может контролироваться, по меньшей мере, один рабочий параметр (f, Т, U) интегральной схемы (1), отличающаяся тем, что в качестве рабочего параметра (f, Т, U) контролируется состояние защитного слоя (20) на интегральной схеме (1), при этом функциональные модули (2) включают в себя первый блок (7) памяти, причем для контролируемого рабочего параметра (f, Т, U) задается граничное значение, рабочий параметр (f, Т, U) измеряется и сравнивается с граничным значением, и при превышении граничного значения или уменьшении ниже граничного значения содержание первого блока (7) памяти стирается.

2. Интегральная схема (1) по п.1, отличающаяся тем, что функциональные модули (2) включают в себя генератор (80) случайных чисел.

3. Интегральная схема (1) по п.1, отличающаяся тем, что функциональные модули (2) включают в себя первый блок (7) памяти, в котором сохранены криптографические ключи (18).

4. Интегральная схема (1) по пп.2 и 3, отличающаяся тем, что криптографические ключи (18), которые сохранены в первом блоке (7) памяти, вырабатываются генератором (80) случайных чисел.

5. Интегральная схема (1) по п.1, отличающаяся тем, что функциональные модули (2) включают в себя часы (8) реального времени.

6. Интегральная схема (1) по п.1, отличающаяся тем, что контролируемый рабочий параметр (f, Т, U) дополнительно представляет собой тактовую частоту (f) часов (8) реального времени, и/или рабочую температуру (Т) в любой конкретной точке интегральной схемы (1), и/или рабочее напряжение (U) интегральной схемы (1).

7. Интегральная схема (1) по п.1, отличающаяся тем, что она размещена в корпусе (30) и имеет выведенные из корпуса (30) соединительные контакты (31).

8. Интегральная схема (1) по п.1, отличающаяся тем, что отдельные функциональные модули (2) имеют, по существу, плоскую протяженность и в направлении нормали к плоскости размещены рядом друг с другом.

9. Интегральная схема (1) по п.1, отличающаяся тем, что функциональные модули (2) содержат встроенный регулятор напряжения, который регулирует рабочее напряжение (U).

10. Интегральная схема (1) по п.1, отличающаяся тем, что она выполнена как полупроводниковый чип (13).

11. Интегральная схема (1) по п.10, отличающаяся тем, что полупроводниковые структуры отдельных функциональных модулей (2) сопряжены друг с другом в форме особенно сложных геометрических переплетений для предотвращения возможности распознавания отдельных функциональных модулей.

12. Интегральная схема (1) по п.10, отличающаяся тем, что на кристалл полупроводникового чипа (13) непосредственно нанесен активный защитный слой (20), который состоит из, по меньшей мере, одного удлиненного электрического проводника (21), который проходит вдоль поверхности кристалла, в частности на участках в виде параллельных друг другу дорожек.

13. Устройство для обработки данных с интегральной схемой (1) по любому из пп.1-12, отличающееся тем, что интегральная схема (1) посредством шины (32) данных соединена со вторым блоком (40) памяти (ПЗУ), в котором сохранены в зашифрованном виде данные, причем второй блок (40) памяти содержит ячейки памяти, которые имеют, соответственно, адрес памяти, и каждая ячейка памяти обеспечивает прямое обращение к ней для считывания или записи.

14. Устройство для обработки данных с интегральной схемой (1) по любому из пп.1-12, отличающееся тем, что второй блок (40) памяти является энергозависимым и соединен с батареей (43), так что питающее напряжение поддерживается при отсутствии другого энергопитания.

15. Устройство для обработки данных с интегральной схемой (1) по любому из пп.1-12, отличающееся тем, что интегральная схема (1) посредством шины (32) данных соединена с энергонезависимым третьим блоком (41) памяти, в частности флэш-памятью или ПЗУ, в котором сохранены в зашифрованном виде данные или программный код.

16. Устройство для обработки данных с интегральной схемой (1) по п.1, отличающееся тем, что датчик (9) безопасности соединен с батареей (43), так что питающее напряжение поддерживается при отсутствии другого энергопитания.

17. Устройство для обработки данных с интегральной схемой (1) по п.1, отличающееся тем, что датчик (9) безопасности соединен с встроенным в корпус (30) вспомогательным источником (12) питания, который обеспечивает энергию для стирания содержимого первого блока (7) памяти.

| US 5943421 А, 24.08.1999 | |||

| RU 95103311 A1, 27.11.1996 | |||

| US 5828753 А, 27.10.1998 | |||

| RU 94036200 A1, 07.10.1996 | |||

| ПЕРВИЧНАЯ БАТАРЕЯ, ИМЕЮЩАЯ ВСТРОЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ | 1999 |

|

RU2214655C2 |

| ЗАЩИЩЕННАЯ ОТ МАНИПУЛИРОВАНИЯ ИНТЕГРАЛЬНАЯ СХЕМА | 2000 |

|

RU2216779C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПРОВОДЯЩЕЙ СХЕМЫ НА ПОДЛОЖКЕ, ПРОВОДЯЩАЯ СХЕМА НА ПОДЛОЖКЕ И УСТРОЙСТВО ДЛЯ ИЗГОТОВЛЕНИЯ ГИБКОЙ ПРОВОДЯЩЕЙ СХЕМЫ | 1993 |

|

RU2138930C1 |

Авторы

Даты

2011-02-20—Публикация

2005-03-10—Подача