Изобретение относится к области техники электрической связи и может быть использовано в радиоприемных устройствах сверхвысоких частот повышенной надежности.

Известны малошумящие усилители сверхвысоких частот, например:

Малошумящие усилители СВЧ (Шутенко М.С. Малошумящие усилители СВЧ. М.: Военное издательство МО СССР. 1966; Полупроводниковые приборы в технике электросвязи. Сб. статей, вып.6, 1970; вып.14, 1974. М.: Связь. Полупроводниковые приборы и их применение. Сб. статей, вып.25. М.: Советское радио, 1971; Сравнительное исследование шумовых свойств IМРАТТ-диодов. "ТИИЭР", №6, 1972; Савельев B.C. Транзисторные усилители СВЧ диапазона. М.: ЦНИИ "Электроника", 1979), содержащие мост деления, два усилителя, мост сложения и две согласованные нагрузки.

Общим недостатком аналогов является низкая надежность в работе, так как при выходе из строя одного из усилителей отказывает весь усилительный тракт в целом.

Известен также малошумящий усилитель сверхвысоких частот, описанный в книге "Полупроводниковые приборы и устройства СВЧ". Киев: КВВИД-КУС, 1976, с.118-119, рис. 4.4.1. Он содержит два гибридных соединения (мосты, трехдецибельные направленные ответвители и т.д.) и два усилителя, включенные между этими соединениями.

Недостатком данного устройства является его низкая надежность. Это обусловлено тем, что при отказе одного из усилительных элементов снижается коэффициент усиления и, следовательно, повышается коэффициент шума приемного тракта.

Наиболее близким по своей технической сущности к заявленному устройству является малошумящий усилитель сверхвысоких частот (патент РФ №2108658, кл. Н 03 F 3/60, Н 03 G 3/20, 1998). Малошумящий усилитель СВЧ содержит три усилителя, регулируемый усилитель, мост сложения, две согласованные нагрузки, три блока коммутации, три ключа, блок управления и детектор, при этом сигнальный вход первого блока коммутации является входом малошумящего усилителя сверхвысоких частот, а второй вход подключен к первой согласованной нагрузке, первые выходы первого, второго и третьего блоков коммутации соединены с сигнальными входами соответственно первого, второго и третьего усилителей, второй выход первого блока коммутации подключен к второму входу второго блока коммутации, второй выход которого подключен к второму входу третьего блока коммутации, выходы первого, второго и третьего усилителей подключены к первым входам соответственно второго, третьего блоков коммутации и моста сложения, второй вход которого подключен к второму выходу третьего блока коммутации, первый и второй выходы моста сложения подключены соответственно к сигнальному входу регулируемого усилителя и к второй согласованной нагрузке, выход регулируемого усилителя соединен с входом детектора и является выходом малошумящего усилителя сверхвысоких частот, выход детектора соединен с логическими входами блока управления и регулируемого усилителя, первый, второй и третий управляющие выходы блока управления соединены с управляющими входами соответственно первого, второго и третьего блоков коммутации, а четвертый, пятый и шестой управляющие выходы блока управления соединены с управляющими входами соответственно первого, второго и третьего ключей, выходы которых подключены к питающим входам соответственно первого, второго и третьего усилителей.

Устройство-прототип по сравнению с описанными аналогами обладает более высокими надежностными характеристиками при одновременном снижении коэффициента шума радиоприемного тракта за счет его построения по схеме со скользящим резервированием и имеющего возможность работы в квазирезервированном режиме при равномерном расходовании ресурса усилителей.

Однако устройство-прототип имеет недостаток - относительно низкую надежность, обусловленную высокой вероятностью выхода из строя элементов схемы при возникновении коротких замыканий в системе питания.

Целью изобретения является разработка устройства, обеспечивающего повышение надежности малошумящего усилителя (МШУ) сверхвысоких частот (СВЧ) при возникновении коротких замыканий в системе питания.

Поставленная цель достигается тем, что в известный малошумящий усилитель сверхвысоких частот, содержащий первый, второй и третий усилители, регулируемый усилитель (РУ), мост сложения (МС), первую и вторую согласованные нагрузки (СН), первый, второй и третий блоки коммутации (БК), первый, второй и третий ключи, блок управления (БУ) и детектор, при этом сигнальный вход первого БК является входом МШУ СВЧ, а второй вход подключен к первой СН, первые выходы первого, второго и третьего БК соединены с сигнальными входами соответственно первого, второго и третьего усилителей, второй выход первого БК подключен к второму входу второго БК, второй выход которого подключен к второму входу третьего БК, выходы первого, второго и третьего усилителей подключены к первым входам соответственно второго, третьего БК и МС, второй вход которого подключен к второму выходу третьего БК, первый и второй выходы МС подключены соответственно к сигнальному входу РУ и к второй СН, выход РУ соединен с входом детектора и является выходом МШУ СВЧ, выход детектора соединен с логическими входами БУ и РУ, первый, второй и третий управляющие выходы БУ соединены с управляющими входами соответственно первого, второго и третьего БК, а четвертый, пятый и шестой управляющие выходы БУ соединены с управляющими входами соответственно первого, второго и третьего ключей, выходы которых подключены к питающим входам соответственно первого, второго и третьего усилителей, дополнительно введен многоканальный блок питания (МБП), первый, второй и третий питающие выходы МБП соединены с питающими входами соответственно первого, второго и третьего ключей, а четвертый питающий выход МБП соединен с питающим входом РУ. Первый, второй и третий управляющие выходы МБП соединены соответственно с первым, вторым и третьим управляющими входами БУ.

МБП состоит из первичного источника питания (ПИП), анализатора, формирователя управляющего напряжения (ФУН) и индикатора. Первый, второй, третий и четвертый коммутационные выходы ПИП соединены соответственно с первым, вторым, третьим и четвертым коммутационными входами ФУН. Первый и второй токовые выходы ПИП соединены с первым и вторым токовыми входами анализатора, выход которого соединен с управляющим входом ФУН. Первый, второй, третий и четвертый управляющие выходы ФУН соединены соответственно с первым, вторым, третьим и четвертым входами индикатора, причем второй, третий и четвертый управляющие выходы ФУН являются соответственно первым, вторым и третьим управляющими выходами МБП, а первый, второй, третий и четвертый питающие выходы ПИП являются соответственно первым, вторым, третьим и четвертым питающими выходами МБП.

БУ состоит из элемента сравнения (ЭС), вход которого является логическим входом БУ, реверсивного счетчика (РСч), первого и второго генераторов импульсов (ГИ), элемента сравнения кодов (ЭСК), элемента развязки (ЭР), первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого, девятого, десятого, одиннадцатого и двенадцатого двухвходовых элементов И, трехвходового элемента И, первого, второго и третьего двухвходовых элементов ИЛИ, первого и второго трехвходовых элементов ИЛИ, первого, второго, третьего, четвертого и пятого элементов НЕ, счетчика (Сч), блока определения (БО), дешифратора (Дш), регистра (Рг), триггера и дешифратора состояний (ДшС). Первый выход "больше" ЭС подключен к первому "вычитающему" входу РСч, выходу ЭР и первому дополнительному входу второго ГИ, выход которого соединен с третьим информационным входом трехвходового элемента И и третьим входом счетных импульсов РСч. Второй вход "сложения" РСч подключен к второму выходу, "меньше" ЭС, второму дополнительному входу второго ГИ, второму входу второго элемента И, второму входу трехвходового элемента И и входу первого элемента НЕ. Выход первого элемента НЕ соединен с вторым входом третьего элемента И, первый вход которого подключен к первому входу второго элемента И и первому выходу "сигнал превышения" ЭСК. Выход третьего элемента И соединен с входом ЭР. Первый вход трехвходового элемента И соединен с вторым выходом "равно" ЭСК, третий выход "сигнал понижения" которого соединен с первым входом первого трехвходового элемента ИЛИ, второй и третий входы которого подключены к выходам соответственно второго элемента И и трехвходового элемента И. Выход первого трехвходового элемента ИЛИ подключен к входу второго элемента НЕ и первому входу первого элемента И, второй вход которого подключен к выходу первого ГИ и соединен с пятым тактовым входом Рг. Выход первого элемента И подключен к входу Сч, первый, второй и третий выходы которого соединены с соответствующими входами БО и первым, вторым и третьим входами Рг, четвертый стробирующий вход которого соединен с выходом второго элемента НЕ и первым информационным входом триггера. Выход БО соединен с вторым входом ЭСК, первый вход которого подключен к выходу РСч. Первый, второй и третий выходы Рг подключены к соответствующим входам Дш и ДшС, а также подключены к первым входам соответственно десятого, одиннадцатого и двенадцатого элементов И. Первый, второй и третий выходы Дш подключены к вторым входам соответственно четвертого, пятого и шестого элементов И. Первый, второй и третий управляющие входы БУ подключены к соответствующим входам второго трехвходового элемента ИЛИ и к входам соответственно третьего, четвертого и пятого элементов НЕ. Первый, второй и третий выходы ДшС подключены к вторым входам соответственно седьмого, восьмого и девятого элементов И. Выход второго трехвходового элемента ИЛИ подключен к первым входам седьмого, восьмого и девятого элементов И, управляющему входу ДшС и к второму информационному входу триггера, выход которого подключен к первым входам четвертого, пятого и шестого элементов И, выходы которых подключены к первым входам соответственно первого, второго и третьего элементов ИЛИ. Выходы седьмого, восьмого и девятого элементов И подключены к вторым входам соответственно первого, второго и третьего элементов ИЛИ, выходы которых являются первым, вторым и третьим выходами БУ. Выходы третьего, четвертого, и пятого элементов НЕ подключены ко вторым входам соответственно десятого, одиннадцатого и двенадцатого элементов И, выходы которых являются соответственно четвертым, пятым и шестым выходами БУ.

Благодаря введению МБП и новых связей появилась возможность повысить надежность работы первого, второго, третьего и регулируемого усилителей за счет индивидуального подбора источника электропитания усилителей, что предотвращает выход из строя транзисторов усилителей, вследствие возникновения импульсного тока, возникающего при коротких замыканиях в усилительных элементах, и обеспечивается контроль их состояния.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественными всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности "новизна".

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

Заявленное устройство поясняется чертежами, на которых показаны:

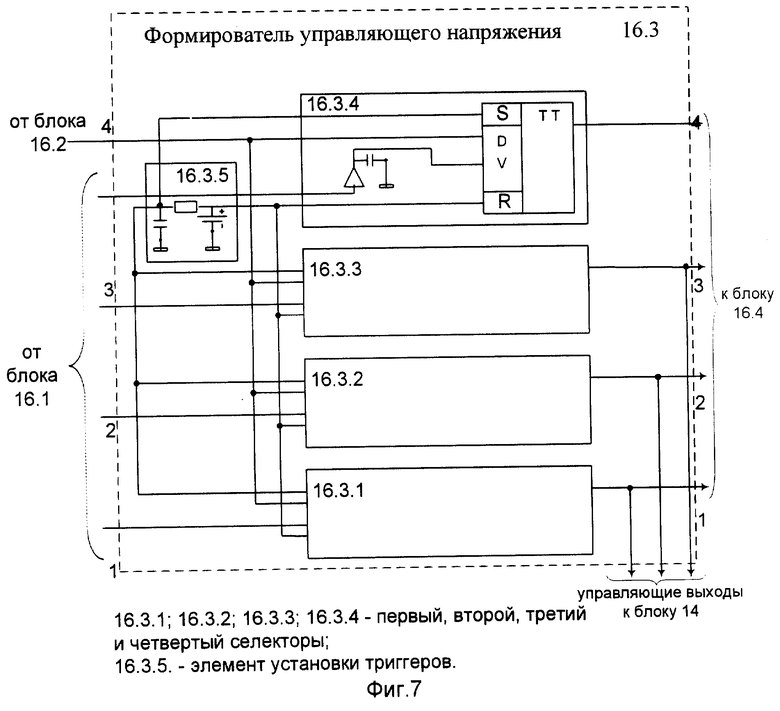

фиг.1 - структурная схема малошумящего усилителя сверхвысоких частот;

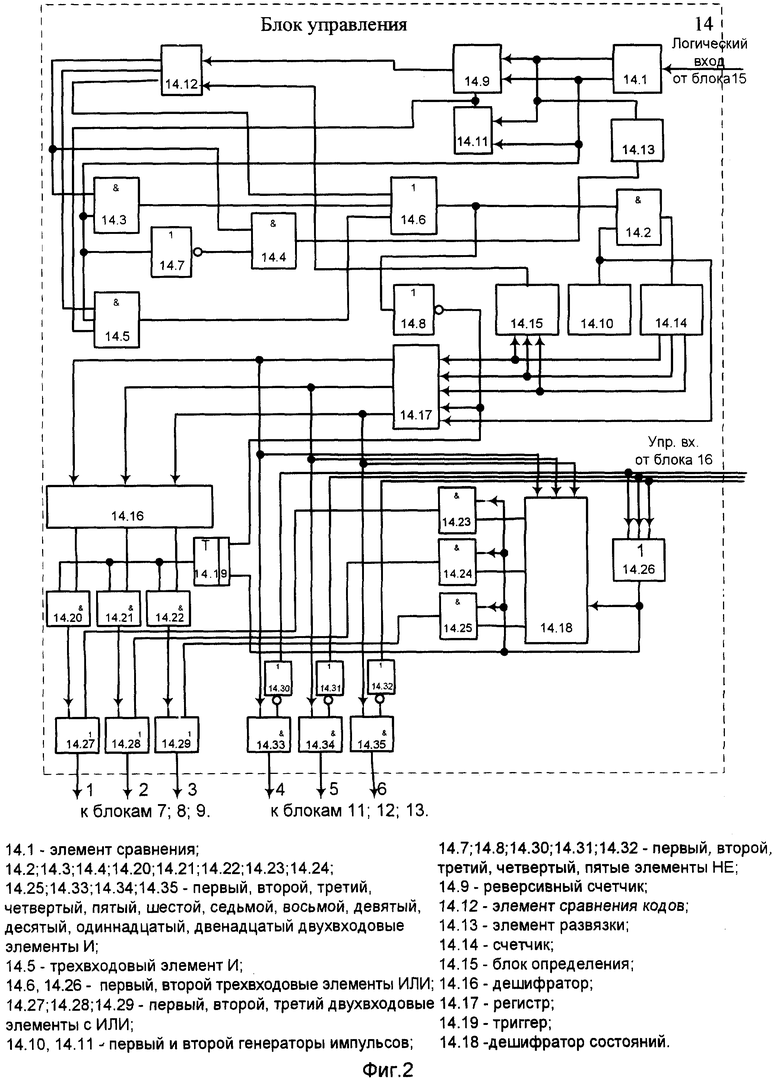

фиг.2 - блок управления 14;

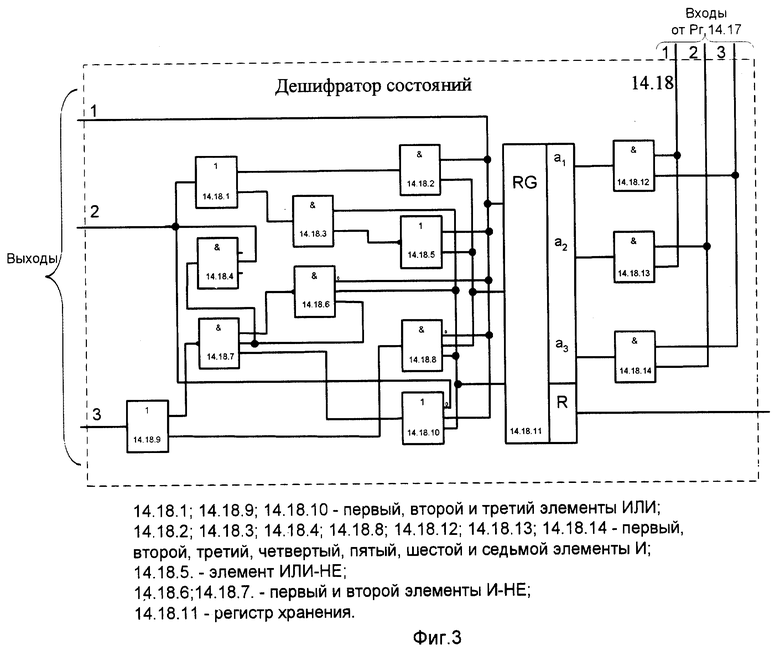

фиг.3 - вариант структурной схемы дешифратора состояний 14.18;

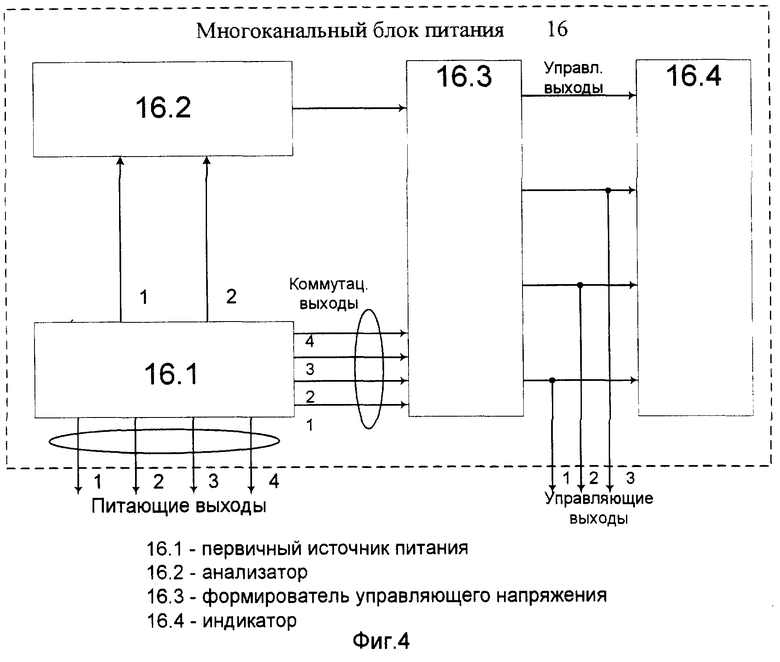

фиг.4 - структурная схема многоканального блока питания 16;

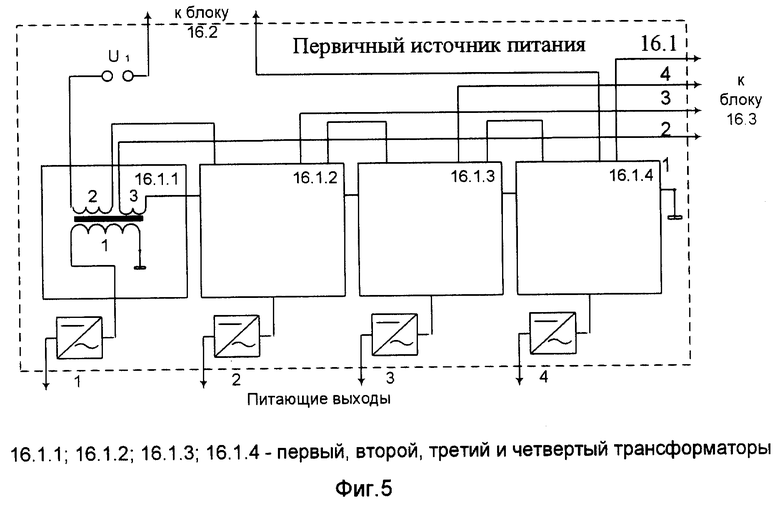

фиг.5 - схема первичного источника питания 16.1;

фиг.6 - схема анализатора 16.2;

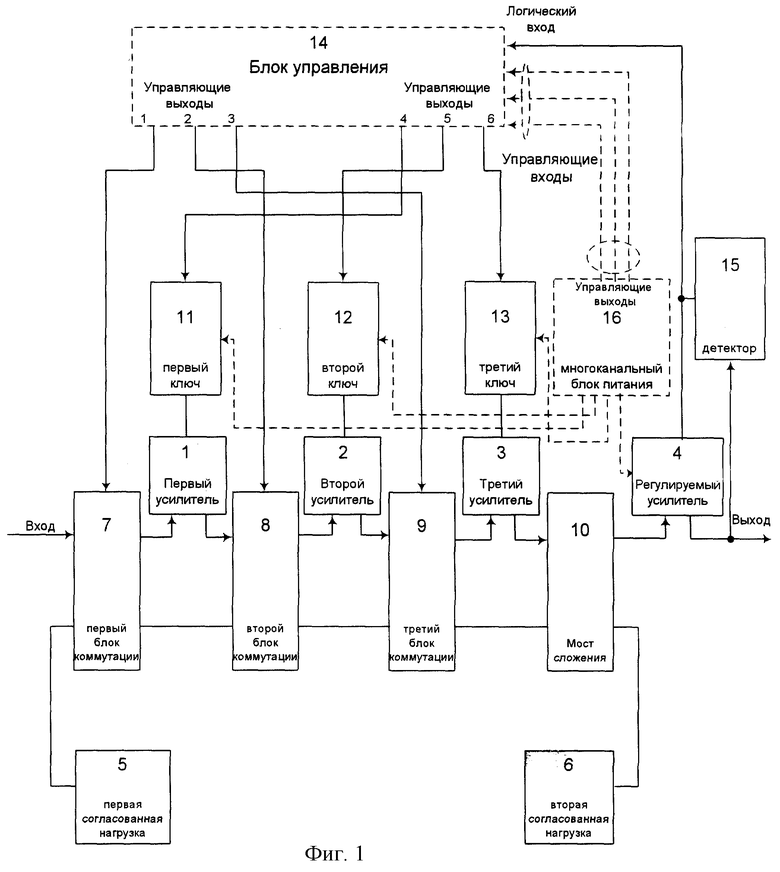

фиг.7 - схема формирователя управляющего напряжения 16.3.

Малошумящий усилитель сверхвысоких частот, показанный на Фиг.1, состоит из первого 1, второго 2 и третьего 3 усилителей, регулируемого усилителя 4 (РУ), первой 5 и второй 6 согласованных нагрузок (СН), первого 7, второго 8 и третьего 9 блоков коммутации (БК), моста сложения 10 (МС), первого 11, второго 12 и третьего 13 ключей, блока управления 14 (БУ), детектора 15, многоканального блока питания 16 (МБП).

Сигнальный вход первого 7 БК является входом МШУ СВЧ, а второй вход подключен к первой 5 СН. Первые выходы первого 7, второго 8 и третьего 9 БК соединены с сигнальными входами соответственно первого 1, второго 2 и третьего 3 усилителей. Второй выход первого 7 БК подключен к второму входу второго 8 БК, второй выход которого подключен к второму входу третьего 9 БК. Выходы первого 1, второго 2 и третьего 3 усилителей подключены к первым входам соответственно второго 8, третьего 9 БК и 10 МС, второй вход которого подключен к второму выходу третьего 9 БК. Первый и второй выходы 10 МС подключены соответственно к сигнальному входу 4 РУ и к второй 6 СН. Выход 4 РУ соединен с входом детектора 15 и является выходом МШУ СВЧ. Выход детектора 15 соединен с логическими входами 14 БУ и 4 РУ. Первый, второй и третий управляющие выходы 14 БУ соединены с управляющими входами соответственно первого 7, второго 8 и третьего 9 БК. Четвертый, пятый и шестой управляющие выходы 14 БУ соединены с управляющими входами соответственно первого 11, второго 12 и третьего 13 ключей, выходы которых подключены к питающим входам соответственно первого 1, второго 2 и третьего 3 усилителей. Первый, второй и третий питающие выходы 16 МБП соединены с питающими входами соответственно первого 11, второго 12 и третьего 13 ключей, а четвертый питающий выход МБП 16 соединен с питающим входом РУ 4. Первый, второй и третий управляющие выходы 16 МБП соединены соответственно с первым, вторым и третьим управляющими входами БУ 14.

Блок управления 14, схема которого показана на Фиг.2, предназначен для разработки вариантов использования усилителей, на основе анализа радиоприемного тракта, а также формирования управляющих сигналов разрешающих или запрещающих включать первый 1, второй 2 и третий 3 усилители.

Блок управления 14, состоит из элемента сравнения 14.1 (ЭС), первого 14.2, второго 14.3, третьего 14.4, четвертого 14.20, пятого 14.21, шестого 14.22, седьмого 14.23, восьмого 14.24, девятого 14.25, десятого 14.33, одиннадцатого 14.34 и двенадцатого 14.35 двухвходовых элементов И, трехвходового элемента 14.5 И, первого 14.6 и второго 14.26 трехвходовых элементов ИЛИ, первого 14.27, второго 14.28 и третьего 14.29 двухвходовых элементов ИЛИ, первого 14.7, второго 14.8, третьего 14.30, четвертого 14.31 и пятого 14.32 элементов НЕ, реверсивного счетчика 14.9, первого 14.10 и второго 14.11 генераторов импульсов, элемента сравнения кодов 14.12, элемента развязки 14.13, счетчика 14.14, блока определения 14.15 предназначенного для определения кода счетчика 14.14, дешифратора 14.16, регистра 14.17, триггера 14.19 и дешифратора состояний 14.18. Блок определения 14.15 может быть реализован по известной схеме, приведенной в патенте РФ №2108658, Фиг.4.

Первый выход "больше" 14.1 ЭС подключен к первому "вычитающему" входу 14.9 РСч, выходу 14.13 ЭР и первому дополнительному входу второго 14.11 ГИ. Выход второго 14.11 ГИ, соединен с третьим информационным входом трехвходового элемента 14.5 И и третьим входом счетных импульсов 14.9 РСч. Второй вход "сложения" 14.9 РСч подключен к второму выходу "меньше" 14.1 ЭС, второму дополнительному входу второго 14.11 ГИ, второму входу второго 14.3 элемента И, второму входу трехвходового элемента 14.5 И и входу первого 14.7 элемента НЕ. Выход первого 14.7 элемента НЕ соединен с вторым входом третьего 14.4 элемента И, первый вход которого подключен к первому входу второго 14.3 элемента И и первому выходу "сигнал превышения" 14.12 ЭСК. Выход третьего 14.4 элемента И соединен с входом 14.13 ЭР. Первый вход трехвходового элемента 14.5 И соединен с вторым выходом "равно" 14.12 ЭСК, третий выход "сигнал понижения" которого соединен с первым входом первого 14.6 трехвходового элемента ИЛИ. Второй и третий входы первого 14,6 элемента ИЛИ подключены к выходам соответственно второго 14.3 элемента И и трехвходового элемента 14.5 И. Выход первого 14.6 трехвходового элемента ИЛИ подключен к входу второго 14.8 элемента НЕ и первому входу первого 14.2 элемента И. Второй вход первого 14.2 элемента И подключен к выходу первого 14.10 ГИ и соединен с пятым тактовым входом 14.17 Рг. Выход первого 14.2 элемента И подключен к входу 14.14 Сч, первый, второй и третий выходы которого соединены с соответствующими входами 14.15 БО и первым, вторым и третьим входами 14.17 Рг. Четвертый стробирующий вход регистра 14.17 соединен с выходом второго 14.8 элемента НЕ и первым информационным входом триггера 14.19. Выход 14.15 БО соединен с вторым входом 14.12 ЭСК, первый вход которого подключен к выходу 14.9 РСч. Первый, второй и третий выходы 14.17 Рг подключены к соответствующим входам 14.16 Дш и 14.18 ДшС, а также подключены к первым входам соответственно десятого 14.33, одиннадцатого 14.34 и двенадцатого 14.35 элементов И. Первый, второй и третий выходы 14.16 Дш подключены к вторым входам соответственно четвертого 14.20, пятого 14.21 и шестого 14.22 элементов И. Первый, второй и третий управляющие входы 14 БУ подключены к соответствующим входам второго 14.26 трехвходового элемента ИЛИ и к входам соответственно третьего 14.30, четвертого 14.31 и пятого 14.32 элементов НЕ. Первый, второй и третий выходы 14.18 ДшС подключены к вторым входам соответственно седьмого 14.23, восьмого 14.24 и девятого 14.25 элементов И. Выход второго 14.26 элемента ИЛИ с тремя входами подключен к первым входам седьмого 14.23, восьмого 14.24 и девятого 14.25 элементов И, управляющему входу ДшС 14.18 и к второму информационному входу триггера 14.19. Выход триггера 14.19 подключен к первым входам четвертого 14.20, пятого 14.21 и шестого 14.22 элементов И, выходы которых подключены к первым входам соответственно первого 14.27, второго 14.28 и третьего 14.29 элементов ИЛИ. Выходы седьмого 14.23, восьмого 14.24 и девятого 14.25 элементов И подключены к вторым входам соответственно первого 14.27, второго 14.28 и третьего 14.29 элементов ИЛИ, выходы которых являются первым, вторым и третьим выходами БУ 14. Выходы третьего 14.30, четвертого 14.31 и пятого 14.32 элементов НЕ подключены ко вторым входам соответственно десятого 14.33, одиннадцатого 14.34 и двенадцатого 14.35 элементов И, выходы которых являются соответственно четвертым, пятым и шестым выходами 14 БУ.

Элементы 14.2, 14.3, 14.4, 14.5, 14.20, 14.21, 14.22, 14.23, 14.24, 14.25, 14.33, 14.34, 14.35 И могут быть реализованы на ИМС (Шило В.Л. Популярные цифровые микросхемы: Справочник. 1987. М.: Радио и связь, с.40, табл. 1.11).

Элементы 14.6, 14.26, 14.27, 14.28, 14.29 ИЛИ могут быть реализованы на ИМС (Вениаминов В.Н., Лебедев О.Н., Мирошниченко А.И. Микросхемы и их применение. Справочное пособие. 3-е издание, переработанное и дополненное. М.: Радио и связь, 1989, с.20, табл. 1.2).

Элементы 14.7, 14.8, 14.30, 14.31, 14.32 НЕ могут быть реализованы на ИМС (Шило В.Л. Популярные цифровые микросхемы: Справочник. 1987 М.: Радио и связь, с.27).

Дешифратор состояний 14.18 предназначен для анализа аварийной ситуации и поиска верной комбинации позволяющей использовать только исправные усилители. Вариант построения дешифратора состояний представлен на Фиг.3. Он состоит из первого 14.18.1, второго 14.18.9 и третьего 14.18.10 элементов ИЛИ, первого 14.18.2, второго 14.18.3, третьего 14.18.7, четвертого 14.18.8, пятого 14.18.12, шестого 14.18.13 и седьмого 14.18.14 элементов И, элемента 14.18.5 ИЛИ-НЕ, первого 14.18.4 и второго 14.18.6 элементов И-НЕ регистра хранения РгХ 14.18.11.

Первый, второй и третий входы ДшС 14.18 являются первыми входами соответственно пятого 14.18.12, шестого 14.18.13 и седьмого 14.18.14 элементов И. Вторые входы пятого 14.18.12, шестого 14.18.13 и седьмого 14.18.14 элементов И подключены соответственно к третьему, первому и второму входам ДшС 14.18. Выходы пятого 14.18.12, шестого 14.18.13 и седьмого 14.18.14 элементов И подключены соответственно к первому, второму и третьему информационному входам РгХ 14.18.11. Первый выход которого подключен к первым входам элемента 14.18.5 ИЛИ-НЕ, первого 14.18.6 элемента И-НЕ, первого 14.18.2 и четвертого 14.18.8 элементов И, а также ко второму входу третьего 14.18.10 элемента ИЛИ, и этот же выход является первым выходом ДшС 14.18. Второй выход РгХ 14.18.11 подключен ко вторым входам элемента 14.18.5 ИЛИ-НЕ, первого 14.18.2 и четвертого 14.18.8 элемента И. Третий выход РгХ 14.18.11 подключен к первому входу второго 14.18.3 элемента И, второму входу первого 14.18.6 элемента И-НЕ, и третьим входам четвертого 14.18.8 элемента И и третьего 14.18.10 элемента ИЛИ. Выход первого 14.18.2 элемента И подключен к первому входу первого 14.18.1 элемента ИЛИ, второй вход которого подключен к выходу второго 14.18.3 элемента И, а его второй вход подключен к выходу элемента 14.18.5 ИЛИ-НЕ. Выход первого элемента 14.18.6 И-НЕ подключен к первому входу второго 14.18.7 элемента И, второй вход которого подключен к третьему входу первого элемента 14.18.6 И-НЕ и выходу третьего элемента 14.18.4 И. Третий вход второго элемента 14.18.7 И подключен к выходу третьего элемента 14.18.10 ИЛИ, первый вход которого подключен к выходу первого элемента 14.18.1 ИЛИ, входу третьего элемента 14.18.4 И и является вторым выходом ДшС 14.18. Выход второго элемента 14.18.7 И-НЕ подключен к первому входу второго элемента 14.18.9 ИЛИ, второй вход которого подключен к выходу четвертого элемента 14.18.8 И, а третий выход ДшС 14.18 является выходом второго элемента 14.18.9 ИЛИ. Аварийный вход ДшС 14.18 является управляющим входом РгХ 14.18.11.

Элементы 14.18.2, 14.18.3, 14.18.7, 14.18.8. 14.18.12, 14.18.13, 14.18.14 И могут быть реализованы на ИМС (Шило В.Л. Популярные цифровые микросхемы: Справочник. 1987. М.: Радио и связь, с.40, табл. 1.11).

Элементы 14.18.1, 14.18.9, 14.18.10 ИЛИ могут быть реализованы на ИМС (Вениаминов В.Н., Лебедев О.Н., Мирошниченко А.И. Микросхемы и их применение. Справочное пособие. 3-е издание, переработанное и дополненное. М.: Радио и связь, 1989, С.20, табл. 1.2).

Элементы 14.18.5 ИЛИ-НЕ и 14.18.4, 14.18.6 И-НЕ могут быть реализованы на ИМС серии К176. (Тарабрин Б.В., Лунин Л.Ф., Смирнов Ю.Н. и др.; Под ред. Тарабрина Б.В. Интегральные микросхемы: Справочник. - М.: Радио и связь, 1983. - с.139).

Регистр хранения 14.18.11 может быть реализован на ИМС (Вениаминов В.Н., Лебедев О.Н., Мирошниченко А.И. Микросхемы и их применение. Справочное пособие. 2-е издание., переработанное и дополненное. М.: Радио и связь, 1983, с.134).

Многоканальный блок питания 16, схема которого показана на Фиг.4, предназначен для индивидуального подбора источника электропитания первого 1, второго 2 и третьего 3 усилителей, формирования управляющих сигналов и индикации состояния элементов МБП 16. Он состоит из первичного источника питания 16.1, анализатора 16.2, формирователя управляющего напряжения 16.3, индикатора 16.4. Первый, второй, третий и четвертый коммутационные выходы 16.1 ПИП соединены соответственно с первым, вторым, третьим и четвертым коммутационными входами 16.3 ФУН. Первый и второй токовые выходы 16.1 ПИП соединены с первым и вторым токовыми входами анализатора 16.2, выход которого соединен с управляющим входом 16.3 ФУН. Первый, второй, третий и четвертый управляющие выходы 16.3 ФУН соединены соответственно с первым, вторым, третьим и четвертым входами индикатора 16.4, причем второй, третий и четвертый управляющие выходы 16.3 ФУН являются соответственно первым, вторым и третьим управляющими выходами 16 МБП. Первый, второй, третий и четвертый питающие выходы 16.1 ПИП являются соответственно первым, вторым, третьим и четвертым питающими выходами 16 МБП.

Первичный источник питания 16.1 предназначен для индивидуального формирования питающего напряжения первого 1, второго 2, третьего 3 усилителей и регулируемого усилителя 4. Схема ПИП 16.1 показана на Фиг.5, который состоит из источника рабочего напряжения U1 и первого 16.1.1. второго 16.1.2, третьего 16.1.3 и четвертого 16.1.4 трансформаторов. Обмотки 2 первого 16.1.1, второго 16.1.2, третьего 16.1.3 и четвертого 16.1.4 трансформаторов соединены последовательно с источником рабочего напряжения U1. Выход источника рабочего напряжения U1 является первым токовым выходом 16.1 ПИП. Первые выводы обмоток 3 первого 16.1.1, второго 16.1.2, третьего 16.1.3 и четвертого 16.1.4 трансформаторов являются соответственно первым, вторым, третьим и четвертым коммутационными выходами 16.1 ПИП, а вторые выводы обмоток 3 первого 16.1.1, второго 16.1.2. третьего 16.1.3 и четвертого 16.1.4 трансформаторов соединены с общей шиной. Первые выводы обмоток 1 первого 16.1.1, второго 16.1.2, третьего 16.1.3 и четвертого 16.1.4 трансформаторов соединены с общей шиной, а вторые выводы являются соответственно первым, вторым, третьим и четвертым питающими выходами 16.1 ПИП, они же питающие выходы МБП 16.

Анализатор 16.2 предназначен для сравнения напряжения подаваемого на усилители с параметрами источника опорного напряжением. Схема анализатора 16.2 показана на Фиг.6, который состоит из датчика тока 16.2.1, компаратора 16.2.2 и источника опорного напряжения U2. Входы датчика тока 16.2.1 являются первым и вторым токовыми входами 16.2 анализатора.

Выход 16.2.1 датчика тока подключен к второму входу 16.2.2 компаратора, вход опорного напряжения которого соединен с выходом источника опорного напряжения U2. Управляющий выход 16.2.2 компаратора является управляющим выходом анализатора 16.2.

Формирователь управляющего напряжения 16.3 предназначен для формирования сигнала авария при возникновении короткого замыкания в конкретном усилителе. Схема ФУН 16.3 показана на Фиг.7, который состоит из первого 16.3.1, второго 16.3.2, третьего 16.3.3 и четвертого 16.3.4 селекторов, а также элемента установки триггеров 16.3.5, состоящего из конденсатора С, резистора R и источника питания Е. Выходы первого 16.3.1, второго 16.3.2 и третьего 16.3.3 селекторов являются соответственно первым, вторым и третьим информационными входами 16.4 индикатора, а также первым, вторым и третьим управляющими выходами ФУН 16.3. Выход четвертого 16.3.4 селектора является четвертым информационным входом 16.4 индикатора.

Первый, второй, третий и четвертый коммутационные входы 16.3 ФУН являются соответственно коммутационными входами первого 16.3.1, второго 16.3.2, третьего 16.3.3 и четвертого 16.3.4 селекторов. Первый вход конденсатора С и отрицательный полюс источника питания Е соединены с общей шиной. Второй вход конденсатора С подключен к первому входу резистора R и к установочным входам S первого 16.3.1, второго 16.3.2, третьего 16.3.3 и четвертого 16.3.4 селекторов. Положительный полюс источника питания Е подключен ко второму входу резистора R и к установочным входам R первого 16.3.1, второго 16.3.2, третьего 16.3.3 и четвертого 16.3.4 селекторов.

Селектор состоит из RS-триггера и выпрямителя, состоящего из диода Dn и конденсатора Cn. Коммутационные входы первого 16.3.1, второго 16.3.2, третьего 16.3.3 и четвертого 16.3.4 селекторов подключены ко входу соответствующего Dn диода. Выход каждого Dn диода соединяется с разрешающим V входом RS-триггера и первым входом конденсатора Cn, второй вход которого соединяется с общей шиной. Управляющий вход 16.3 ФУН является информационным входом первого 16.3.1, второго 16.3.2, третьего 16.3.3 и четвертого 16.3.4 селекторов и соответственно информационным входом D RS-триггера.

RS-триггеры в селекторах могут быть реализованы на ИМС серии К561 (Тарабрин Б.В., Лунин Л.Ф., Смирнов Ю.Н. и др.; Под ред. Тарабрина Б.В. Интегральные микросхемы: Справочник. - М.: Радио и связь, 1983. - С.319).

Блок индикации 16.4 предназначен для индикации состояния элементов 16 МБП и может быть реализован различными способами, одним из которых является диодная матрица, схема которой выполнена на светодиодах и описана в справочнике по полупроводниковым приборам (Лавриненко В.Ю. Справочник по полупроводниковым приборам. Киев.: Техника, 1980, с.464).

МШУ работает следующим образом. В рабочем режиме при исправном состоянии всех усилителей (1, 2, 3) БУ 14 формирует команды на включение любых двух усилителей, а третий усилитель остается в резерве. Причем, поскольку команда на выходе Сч. 14.14 случайна, то вероятность включения двух усилителей из трех равна. Следовательно, в процессе эксплуатации будет обеспечен равномерный расход ресурса усилителей. МШУ работает в режимах скользящего резервирования и квазирезервирования.

В рабочем состоянии, в режиме резервирования в результате случайной комбинации, поступаемой от Сч. 14.14, на управляемых выходах БУ 14 формируется команда на включение любых двух усилителей из трех 1, 2, 3. Пусть для определенности от Сч. 14.14 на вход регистра Рг. 14.17 поступила комбинация 011. В этом случае на выходе Рг.14.17 будет комбинация 001, а на выходе Дш. 14.16 сформируется комбинация 001. Так как усилители исправны, то на управляемых выходах многоканального блока питания 16 команда “авария” (1) не формируется и на управляемые входы БУ 14 поступает комбинация 000. Двухвходовые элементы И 14.20; 14.21; 14.22; 14.23; 14.24; 14.25; 14.33; 14.34; 14.35, двухвходовые элементы ИЛИ 14.27; 14.28; 14.29, трехвходовые элементы ИЛИ 14.26, НЕ 14.30; 14.31; 14.32, триггер 14.19 выполняют роль ключей и комбинация 001, поступающая от Дш 14.16, а также 011, поступающая от Рг.14.17, формирует команды на управляющих выходах БУ 14, разрешающие использовать второй 2 и третий 3 усилители.

СВЧ сигнал поступает на первый вход первого БК 7, в котором происходит его проключение на один из его выходов, в зависимости от команды, поступающей с 1-го и 4-го управляющих выходов БУ 14. В рассматриваемом случае с 1-го и 4-го управляемых выходов БУ 14 подаются сигналы логического 0. Сигнал логического 0, поступаемый с 1-го управляющего выхода БУ 14 на управляющий вход первого БК 7, обеспечивает фазовый сдвиг 0 град, в результате чего СВЧ сигнал проключается на второй выход первого БК 7. Сигнал логического 0, поступаемый с 4-го управляющего выхода БУ 14 на управляющий вход первого ключа 11, исключает возможность подачи питающего напряжения на первый усилитель 1. В результате чего он выключен, а СВЧ сигнал обходит его.

С второго выхода первого БК 7 СВЧ сигнал поступает на 2-й вход второго БК 8 и должен поступить на его вход второго усилителя 2. В этом случае с 2-го и 5-го управляемых выходов БУ 14 подаются сигналы логического 0 и логической 1 соответственно. Сигнал логического 0, поступаемый с 2-го управляющего выхода БУ 14 на управляющий вход второго БК 8 обеспечивает фазовый сдвиг 0 град, в результате чего СВЧ сигнал проключается на первый выход второго БК 8. Сигнал логической 1, поступаемый с 5-го управляющего выхода БУ 14 на управляющий вход второго ключа 12, обеспечивает подачу питающего напряжения от МБП 16 на второй усилитель 2, в результате чего он включен.

Усиленный СВЧ сигнал с выхода второго усилителя 2 подается на первый вход третьего БК 9 и должен поступить на вход третьего усилителя 3.

В этом случае с 3-го и 6-го управляемых выходов БУ 14 подаются сигналы логической 1. Сигнал логической 1, поступаемый с 3-го управляющего выхода БУ 14 на управляющий вход третьего БК 9, обеспечивает фазовый сдвиг 180 град, в результате чего усиленный СВЧ сигнал проключается на первый выход третьего БК 9. Сигнал логической 1, поступаемый с 6-го управляющего выхода БУ 14 на управляющий вход третьего ключа 13 обеспечивает подачу питающего напряжения от МБП 16 на третий усилитель 3, в результате чего он включен. Усиленный СВЧ сигнал с выхода третьего усилителя 3 через МС 10 поступает на вход РУ 4, который поддерживает постоянным требуемый уровень сигнала на выходе МШУ СВЧ. Таким образом, включение усилителей и управление работой БК 7, 8 и 9 осуществляется разными цифровыми комбинациями (табл. 1).

При работе МШУ СВЧ на линиях связи с улучшенными энергетическими характеристиками он переходит в режим квазирезервирования (т.е. возникает дополнительная избыточность усилителей), когда в работу включается один усилитель, а два других находятся в резерве. В этом случае управление включением усилителей и работой БК осуществляется следующими цифровыми комбинациями (табл.2).

Управление работой МШУ СВЧ осуществляет БУ 14 на основе сигнала, поступающего с выхода РУ через детектор 15 на вход ЭС 14.1. Число состояний Сч 14.14 равно 6, так как комбинации 111 и 000 являются запрещенными, что соответствует двум возможным режимам работы МШУ СВЧ: 1) включено два усилителя (режим скользящего резервирования); 2) включен один усилитель (режим квазирезервирования). Число состояний PC 14.9 соответствует числу режимов работы МШУ СВЧ: 01 и 10, где 01 - включение одного усилителя, 10 - включение двух усилителей. Состояние PC 14.9 совпадает с числом включенных усилителей в двоичном коде. Для устранения кольцевых эффектов и сокращения времени управления состояния 11 и 00 в PC 14.9 блокируются. Устойчивость работы БУ 14 обеспечивается выбором периода следования импульсов ГИ 14.11 и постоянной времени регулировки усиления РУ 4. Они должны быть равны, а период следования импульсов ГИ 14.10 выбирается значительно меньше периода следования импульсов ГИ 14.11, при этом время полного цикла Сч. 14.14 будет значительно меньше периода следования ГИ 14.10. Это обеспечивает возможность с помощью элементов И 14.5 и ИЛИ 14.6 распознавать наличие неисправного усилителя в схеме. В нормальном режиме работы в исходном состоянии PC 14.9 находится в состоянии 10, что соответствует включению двух усилителей. Если после включения Сч.14.14 находится в одном из состояний 011, 110, 101, то на выходе ЭС 14.1 сигналы отсутствует, на втором выходе ЭСК 14.12 сигнал 1, который поступает на пятый вход Рг 14.17 и по сигналу ГИ 14.11 на выходе Рг 14.17 будет комбинация, соответствующая состоянию Сч 14.14, обеспечивающая включение (выключение) ключей 11, 12, 13 (в соответствии с табл.1), а на выходе Дш 14.16 сформируется соответствующая комбинация для управления БК 001, 110, или 100, что обеспечивает подключение требуемого количества усилителей.

Если устройство работает на линиях связи с улучшенными характеристиками, то МШУ СВЧ перейдет в режим квазирезервирования. В этом случае после включения на первом выходе ЭС 14.1 появится сигнал логической 1, который запустит ГИ 14.11 и поступит на первый вход PC 14.9. В результате PC 14.9 перейдет в состояние 01, что соответствует включению одного усилителя. На втором входе ЭСК 14.12 будет сигнал в двоичном коде меньше, чем на первом входе. Следовательно, на третьем выходе ЭСК 14,12 появится логическая 1, которая через элемент ИЛИ 14.6 разрешит подачу импульсов управления на вход Сч. 14.14 и через элемент НЕ 14.8 подачей логического 0 на четвертый вход Рг 14.17 запретит изменение структуры цифровой комбинации МШУ СВЧ до момента, когда на втором выходе ЭСК 14.12 не появится логическая 1, что будет соответствовать переходу Сч 14.14 в одно из состояний 100, 010, 001, тогда на выходе элемента ИЛИ 14.6 будет 0, а на выходе элемента НЕ 14.8 логический 0. На выходе Рг 14.17 будет одна из комбинаций включения-выключения ключей 11, 12, 13 (табл. 2), соответствующая состоянию Сч 14.14, а на выходе Дш 14.16 будет 101, 000 или 010 в зависимости от комбинации на выходе Рг 14.17 (табл. 2), что обеспечит включение только одного усилителя. В этом случае МШУ СВЧ будет работать в режиме квазирезервирования. Если в момент включения Сч 14.14 оказался в одном из состояний 100, 010, 001 соответствующих включению одного усилителя, то это приведет к тому, что на первом выходе ЭСК 14.12 появится логическая 1, которая поступит на первые входы элементов И 14.3 и 14.4 и на второй выход ЭС 14.1, так как включен только один усилитель. Тогда на выходе элемента И 14.3 будет 1, которая обеспечит появление 1 на выходе элемента ИЛИ 14.6 и подключит ГИ 14.11, который переведет Сч 14.14 в одно из состояний 011, 110 или 101. Тогда на втором выходе ЭСК 14.12 будет логическая 1, а на выходе элемента ИЛИ 14.6 логический 0, следовательно Рг 14.17 и Дш 14.16 обеспечат включение двух усилителей. Для повышения устойчивости работы БУ 14 используются элементы НЕ 14.8, И 14.4 и развязки 14.13. В момент включения PC 14.9 может оказаться в состоянии 10, а на выходах ЭС 14.1 сигнала нет, тогда PC 14.9 переводится из состояния 10 в 01 подачей импульса с выхода элемента развязки 14.13. Переход МШУ СВЧ (при ухудшении характеристик линий связи) из режима квазирезервирования в режим скользящего резервирования по сигналу МЕНЬШЕ на выходе ЭС 14.1, который поступает на второй вход PC 14.9 и запускает ГИ 14.11. Тогда PC 14.9 переходит из состояния 01 в состояние 10, что обеспечивает включение двух усилителей.

В МШУ СВЧ предусмотрены режимы работы в случаях выхода из строя одного из усилителей и возникновения перегрузок по напряжению, возникающие при коротких замыканиях в усилителях.

При выходе из строя одного из усилителей при работе МШУ СВЧ в режиме скользящего резервирования PC 14.9 находится в состоянии 10 и не изменит его по сигналу МЕНЬШЕ со второго выхода ЭС 14.1, поступающего на второй вход PC 14.9. На всех входах элемента И 14.5 логическая 1 и Сч 14.14 изменит свое состояние, и максимум за два цикла работы Сч 14.14 восстановит работоспособность МШУ СВЧ. Например, если были включены второй 2 и третий 3 усилители, на выходе Сч 14.14 комбинация 011. В случае, если произошел отказ второго 2 усилителя, то Сч 14.14 перейдет в состояние 101 на первом цикле. При отказе третьего 3 усилителя Сч 14.14 перейдет в состояние 110 на втором цикле, что будет соответствовать восстановлению работоспособности МШУ СВЧ. При работе МШУ СВЧ в режиме квазирезервирования и отказе усилителя восстановление работоспособности будет осуществляться через режим скользящего резервирования.

При возникновении короткого замыкания в усилителях МШУ СВЧ работает следующим образом. Пусть МШУ СВЧ работает в режиме скользящего резервирования при включенных втором и третьем У 2, 3. При включении источника рабочего напряжения U1, первичного источника питания в МБП 16, напряжение поступает на обмотки 2 и через индуктивную связь - на питающие выходы МБП 16. В случае возникновения короткого замыкания во втором 2 усилителе в первичной обмотке второго трансформатора 16.1.2. напряжение на его второй обмотке уменьшается, а на остальных обмотках 2 первого 16.1.1, третьего 16.1.3 и четвертого 16.1.4 трансформаторов возрастает, что приводит к увеличению тока через датчик тока 16.2.1, срабатыванию компаратора 16.2.2 и подаче питания на первый 16.3.1, второй 16.3.2, третий 16.3.3. и четвертый 16.3.4 селекторы. Напряжение с обмоток 3 первого 16.1.1, второго 16.1.2, третьего 16.1.3 и четвертого 16.1.4 трансформаторов поступает на входы первого 16.3.1, второго 16.3.2, третьего 16.3.3 и четвертого 16.3.4 селектора соответственно, где осуществляется поиск минимального напряжения. В результате срабатывает индикатор, соответствующий номеру неисправного усилителя и сигнал логической 1 подается на управляющий вход БУ 14. Сигнал логической 1, поступаемый через элемент ИЛИ 14.26, выполняет следующие функции: 1) блокирует прохождение комбинации 011 с выхода Дш 14.16; 2) разрешает прохождение комбинации 010 с выхода ДшС 14.18 на 1-й, 2-й и 3-й управляющие выходы БУ 14; 3) разрешает формирование ДшС 14.18 комбинацию 010. В рассматриваемой аварийной ситуации на 1-ом, 2-ом и 3-ем управляющих выходах БУ 14 формируется такая комбинация (010) управляющая БК 7, 8 и 9, при которой МШУ кратковременно на время работы Сч. 14.14 переходит в режим квазирезервирования при включенном третьем 3 усилителе. Сигналы об аварии, поступающие с МБП 16 (010) на управляющие входы БУ 14, формируют команду (001) с 4-го, 5-го и 6-го выходов БУ 14 прерывающую подачу напряжения на второй 2 усилитель до момента полного восстановления его работоспособности. В случае аварии по короткому замыканию одного из усилителей управление работой первого 7, второго 8 и третьего 9 БК осуществляется разными цифровыми комбинациями вырабатываемыми ДшС 14.18 (табл. 3).

Сигнал логической 1, поступающий на вход элемента ИЛИ 14.6, разрешит подачу импульсов от ГИ 14.10 на вход Сч 14.14, а через первый элемент НЕ 14.8 подачей логического 0 на четвертый вход Рг 14.17 запретит изменение его структуры, пока счетчик не перейдет к комбинации 101, использующей только первый 1 и третий 3 усилители. Тогда на выходе элемента ИЛИ 14.6 будет логический 0, запрещающий прохождение импульсов от ГИ 14.10 на вход Сч14.14, а также снимет запрещающий сигнал с четвертого входа Рг 14.17 и первого информационного входа триггера 14.19. В результате этого на выходе Рг 14.17 будет комбинация включения-выключения ключей 11, 12, 13 (табл. 2), соответствующая состоянию Сч 14.14 (101), а на выходе Дш 14.16 комбинация (100), обеспечивающая проключение первого 1 и третьего 3 усилителей (табл. 2). Сигналы с выходов Дш 14.16 и Рг 14.17 через цепь логических элементов поступают на 1-й, 2-й, 3-й, 4-й, 5-й и 6-й управляющие выходы БУ 14, в результате чего работают первый 1 и третий 3 усилители, а второй 2 усилитель принудительно отключен подачей сигнала логической 1 на управляемый вход БУ 14. Сигнал авария второго 2 усилителя подается до момента его перехода в исправное состояние. Учитывая, что предлагаемое устройство позволяет автоматически определять и выводить индикацию об отказавшем усилителе, то это снижает коэффициент простоя МШУ СВЧ, а следовательно, и всего приемного тракта по причине отказов усилителей.

Таким образом, новая совокупность существующих признаков заявляемого устройства обеспечивает повышение надежности функционирования радиоприемного тракта при возникновении коротких замыканий в системе питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| МАЛОШУМЯЩИЙ УСИЛИТЕЛЬ СВЕРХВЫСОКИХ ЧАСТОТ | 1995 |

|

RU2108658C1 |

| РАДИОПЕРЕХОДНОЕ УСТРОЙСТВО | 2000 |

|

RU2187213C2 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| СПОСОБ ПРИЕМА ДВОИЧНЫХ ФАЗОМАНИПУЛИРОВАННЫХ НА 0, 90, 180, 270 СИГНАЛОВ С ФАЗОРАЗНОСТНОЙ МОДУЛЯЦИЕЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2141731C1 |

| ЦИФРОВОЙ ИНТЕЛЛЕКТУАЛЬНЫЙ РЕКУРСИВНЫЙ ФИЛЬТР | 2007 |

|

RU2357357C2 |

| ЦИФРОВОЙ ИНТЕЛЛЕКТУАЛЬНЫЙ ИТЕРАТИВНЫЙ ФИЛЬТР | 2007 |

|

RU2362265C1 |

| Устройство для двусторонней электрохимической обработки | 1990 |

|

SU1743739A1 |

| ПЕЛЕНГАЦИОННОЕ УСТРОЙСТВО (ВАРИАНТЫ) | 2010 |

|

RU2504796C2 |

| ПРИЕМНО-ПЕРЕДАЮЩИЙ МОДУЛЬ АКТИВНОЙ ФАЗИРОВАННОЙ АНТЕННОЙ РЕШЕТКИ | 2002 |

|

RU2206155C1 |

| Система записи и воспроизведения видеосигнала | 1990 |

|

SU1783635A1 |

Изобретение относится к технике электрической связи и может использоваться в радиоприемных устройствах сверхвысоких частот. Технический результат заключается в повышении надежности при возникновении коротких замыканий в системе питания. Малошумящий усилитель содержит усилители (У) (1-3), регулируемый У (4), согласованные нагрузки (5, 6), блоки коммутации (7-9), мост сложения (10), ключи (11-13), блок управления (14), детектор (15), многоканальный блок питания (МБП) (16). Благодаря введению МБП (16) повысилась надежность работы У (1-4) за счет индивидуального подбора электропиания У (1-4), что предотвращает выход из строя транзисторов этих У, из-за возникновения импульсного тока при коротких замыканиях в усилительных элементах, и обеспечивается контроль их состояния. 2 з.п. ф-лы. 7 ил., 3 табл.

четвертый, пятый и шестой управляющие выходы блока управления соединены с управляющими входами соответственно первого, второго и третьего ключей, выходы которых подключены к питающим входам соответственно первого, второго и третьего усилителей, отличающийся тем, что дополнительно введен многоканальный блок питания, первый, второй и третий питающие выходы многоканального блока питания соединены с питающими входами соответственно первого, второго и третьего ключей, а четвертый питающий выход многоканального блока питания соединен с питающим входом регулируемого усилителя, а первый, второй и третий управляющие выходы многоканального блока питания соединены соответственно с первым, вторым и третьим управляющими входами блока управления.

| МАЛОШУМЯЩИЙ УСИЛИТЕЛЬ СВЕРХВЫСОКИХ ЧАСТОТ | 1995 |

|

RU2108658C1 |

| Устройство для выпрямления многофазного тока | 1923 |

|

SU50A1 |

| РЕЗЕРВИРОВАННЫЙ УСИЛИТЕЛЬ | 1996 |

|

RU2115275C1 |

| Усилитель мощности | 1986 |

|

SU1483597A1 |

| Усилитель мощности | 1983 |

|

SU1205251A1 |

Авторы

Даты

2005-06-10—Публикация

2003-10-29—Подача